I

Изобретение относится к цифровой вычислительной технике и может Сыть использовано при построении специализированных вычислительных систем.

Известно устройство для выполнения операций над матрицами и векторами, которое содержит регистры для занесения слагаемых и сомножителей, а также ряд логических схем, связаннь1х с этими регистрами цепями прямой и обратной связи тЗ .

Однако в таком устройстве низкий уровень распараллеливания вычислений, обусловленный тем, что алгоритм умножения чисел в этих устройствах основан на последовательном поступлении разрядов одного из со-. множителей. Зто приводит к тому,что на входы устройств новую пару сомножителей можно принимать не на каждом такте, а только через некоторое множество тактов, необходимое для обработки предыдущей пары сомножителей.

Известны устройства для вычисления сумм произведений, содержащие матричное множительное устройство. Устройства содержат два регистра, накапливающий сумматор, шину тактовых импульсов, шину установки в О и матрицу одноразрядных элементов. На входы устройства оба сомножителя принимаются параллельным кодом, причем на каждом следующем такте осуществляется прием новой пары сомножителей 2 и 31.

Недостатком этих устройств является то, что после подачи на входы устройств последней пары сомножителей, подлежащей суммированию, пары сомножителей новой суммы могут приниматься только по истечении некоторого множества М холостых тактов. Холостые такты необходимы для приема на входы устройств М.пар нулевых значений множимого и множителя, в результате чего значения поразрядных сумм и переносов выходят из матричного множительного устройства состоящего из одноразрядных модулей и суммируются Б накапливающем сумматоре. Так для первого и второго устройств количество холостых тактов М Зп + fog, - 1 , где п - раз рядность операндов, (N-1) - количество пар сомножителей, подлежащих сложению, в третьем же устройстве в связи с применением специальной схемы анализа достигается некоторое уменьшение этой составляющей. Кроме того, к недостаткам первого и треть его устройств следует отнести также ограниченные функциональные возможности, а именно то, что сомножители могут представлять собой только коды положительных чисел, это существенно снижает область применения таких устройств. Наиболее близким по техническому решению к изобретению является устройство для вычисления сумм произведений . Устройство для вычисления сумм произведений содержит матрицу вычислительных элементов,которая содержит п+1 строк, первые три строки имеют (2п+1). Вычислительных элемен тов, каждая последующая строь Ра матрицы имеет на один вычислительный элемент меньше, последняя строка со держит (п+3) вычислительных элементов, (п+1}-разрядные первый и второй регистры операнда (где п - разрядность операндов), первую и вторую группу элементов И-НЕ, накапливающи сумматор, причем первая входная шина соединена с информационными входами первого регистра операнда, вто рая -входная шина соединена с информ ционными входами второго регистра операнда, выходы значащих разрядов пер.вого регистра операнда и второго регистра операнда соответственно Соединены с первыми входами элементов И-НЕ первой и второй групп, вто рые входы элементов И-НЕ первой группы соединены с выходом знакового разряда второго регистра операнда, вторые входы элементов И-НЕ второй группы соединены с выходом знакового разряда первого регист.ра операнда, первые и вторые информационные входы накапливающего сумматора соответственно соединены с (п+2) младшими выходами и с Сп+2) старшими выходами вычислительных элементов последней строки матрицы, первый управляющий вход накапливающего сумматора подключен к шине установки в ноль,выходы накапливающего сумматора соединены с выходной шиной устройства, шина тактовых импульсов соединена со вторым управляющим входом накапливающего сумматора, с управляющим входом каждого вычислительного элемен1а матрицы, с управляющими входами первого и второго регистров операнда J. С помощью этого устройства возможно вычисление сумм произведений операндов, представленных дополнительным двоичным кодом. На каждом такте на входы устройства осуществляется прием параллельных кодов двух очередных сомножителей. После приема последней пары сомножителей на входы устройства в течение (3 + EognN - 1) тактов необходимо подать нулевые сомножители. Таким образом, количество холостых тактов для этого устройства является довольно значительнь1м, что существенно снижает производительность устройства. Цель изобретения - увелимение производительности устройства. Поставленная цель достигается тем, что в устройство введены первый, второй, третий триггеры, причем первый и второй выходы каждого i,j)-ro вычислительного элемента (i 1, 2,п; j 2, 3,-.-,2п) соединены соответственно с первым входом (i+l,j-1)-ro вычислительного элемента и вторым входом (1+1, j+l)-ro вычислительного элемента, а выходы поразрядной суммы и переноса соответственно со входом поразрядной суммы (i+1,jj-ro вычислительного элемента и входом переноса (i+1, -1)-го вычислительного элемента, первый выход каждого (i,j)-ro Еьчислительного элемента (i 1, 2, ) соединен со вторым входом (i+1,j)-ro вычислительного элемента, а выход поразрядной суммы - со входом поразрядной суммы (i+l,j)-ro вычислительного элемента, выход переноса (i,j)-ro вычислительного элемента (,2; j 2п+1) соединен с входом переноса (i-;-l,J)-ro вычислительного элемента, вход переноса (2п+1)-го вычислительного элемента второй строки матрицы соединен с выходом.первого триггера, вход переноса (2n+1J-ro вычислительного элемента третьей строки матрицы соединен с выходом второго триггера, информационный вход которого соединен с выходом третьего триггера, управляющие входы первого,второго и третьего триггеров объединены и подключены к шине тактовых импульсов , первые и вторые входы вычислительных элементов нечетных столбцов первой строки матрицы поразрядно связаны соответственно с выходами второго и первого регистров операнда первые и вторые входы вычислительных элементов четных столбцов первой строки матрицы поразрядно связаны ;оответственно с младшими выходами первого регистра операнда и с п старшими выходами второго регистра операнда, входы поразрядной суммы и переноса вычислительных элементов с г .ервого по п-й столбец первой строки матрицы поразрядно соединены соответственно с выходами элементов И-НЕ второй группы и с выходами элементов И-НЕ первой группы, а входы поразрядной суммы и переноса вычислительных элементов остальных столбцов первой строки матрицы соответственно с выходом знакового разряда первого регистра операнда и с выходом знакового разряда второго регистра операнда, которые соответственно соединены со входами первого и третьего триггеров.

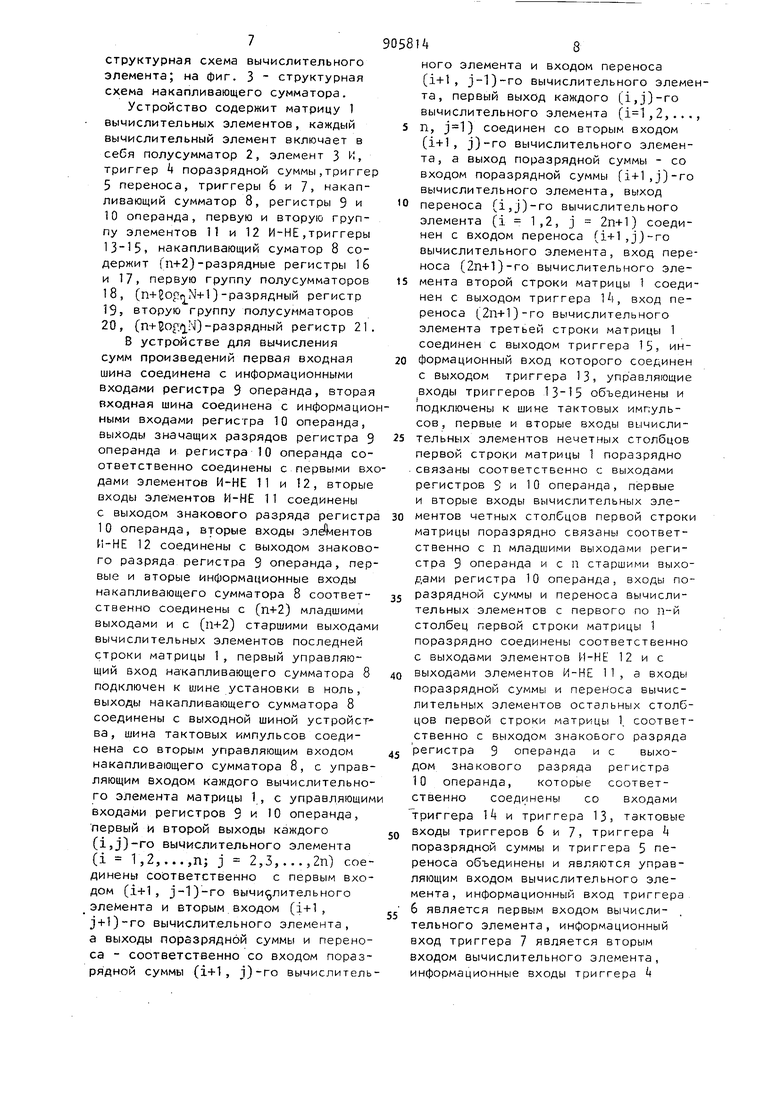

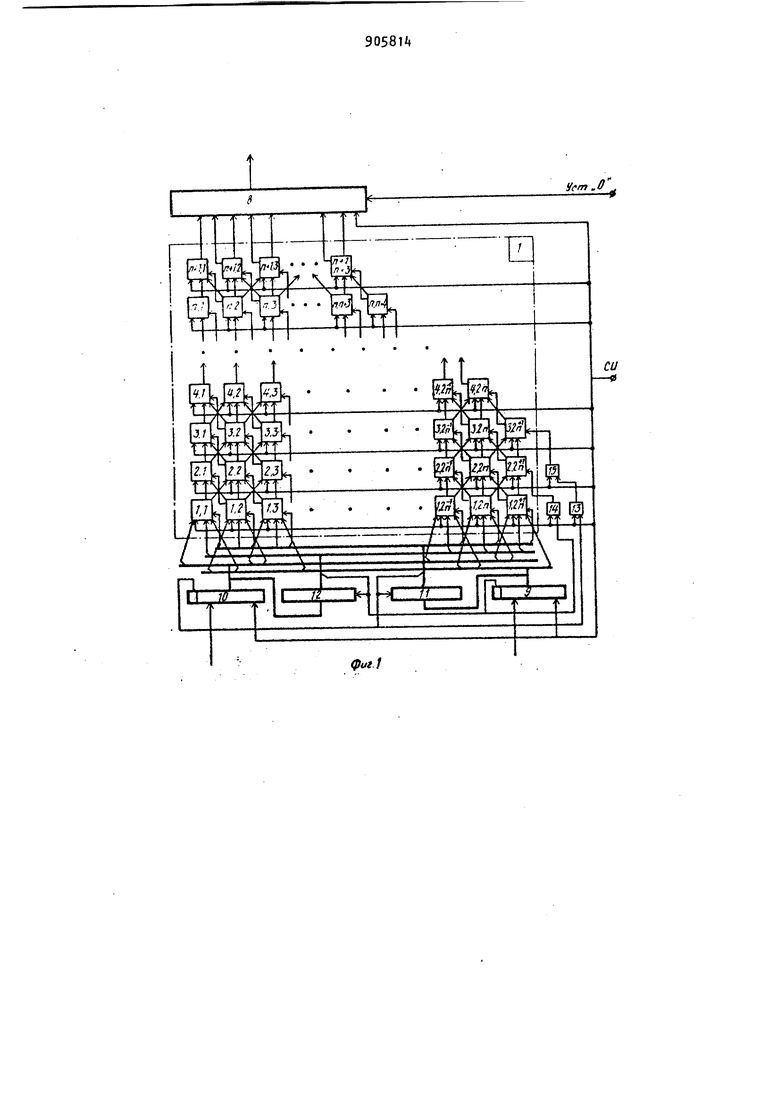

Каждый вычислительный элемент устройства содержит полусумматор, элемент И, первый, второй триггеры, триггер переноса и триггер поразрядной суммы, примем тактовые входы первого, второго триггеров, триггеров поразрядной суммы и переноса объединены и являются управляющим входом вычислительного элемента, информационный вход первого триггера является первым входом вычислительного элемента, информационный вход второго триггера является вторым входом вычислительного элемента (информационные входы триггеров поразрядной суммы и переноса являются соответственно входами поразрядной суммы и переноса вычислительного элемента, выход первого триггера соединен с первым входом элемента И и является первым входом вычислительного элемента, выход второго триггера соединен со вторым входом элемента И и является вторым выходом вычислительного элемента, выход элемента И соединен с первым входом полусумматора, второй и третий входы которого соответственно соединены с выходами триггеров поразрядной суммы и переноса, первый выход полусумматора является выходом переноса вычислительного элемента, второй выход полусумматора является выходом поразрядной суммы вычислительного элемента .

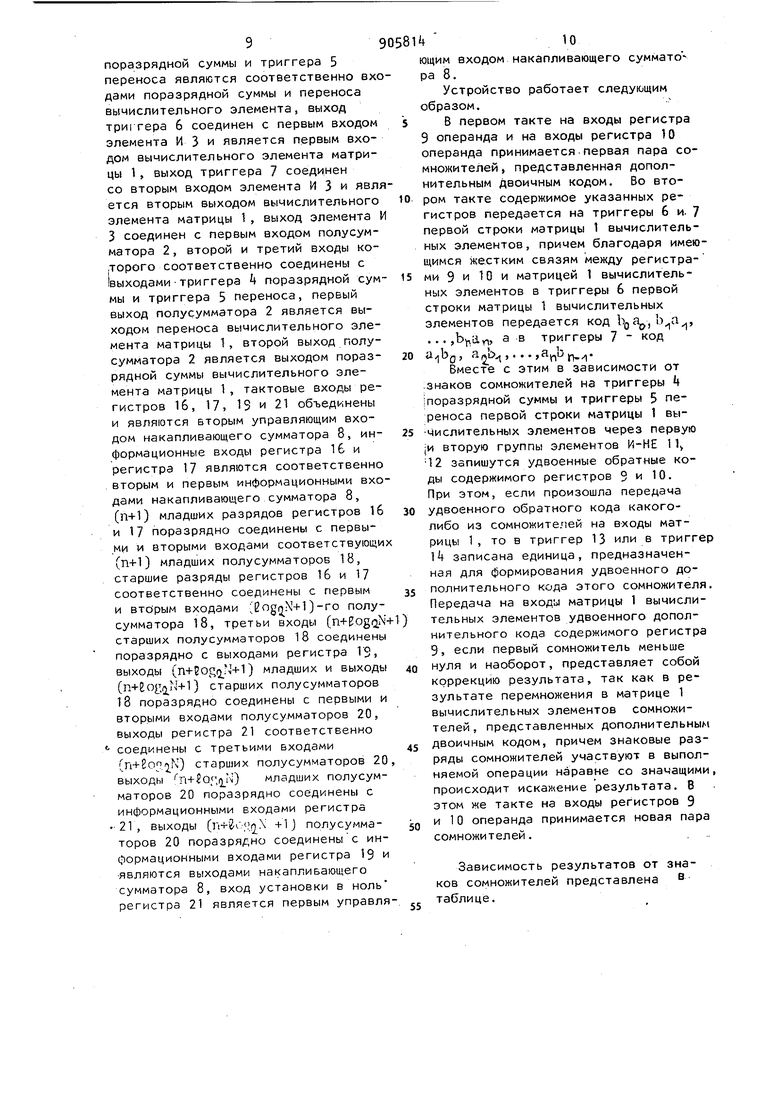

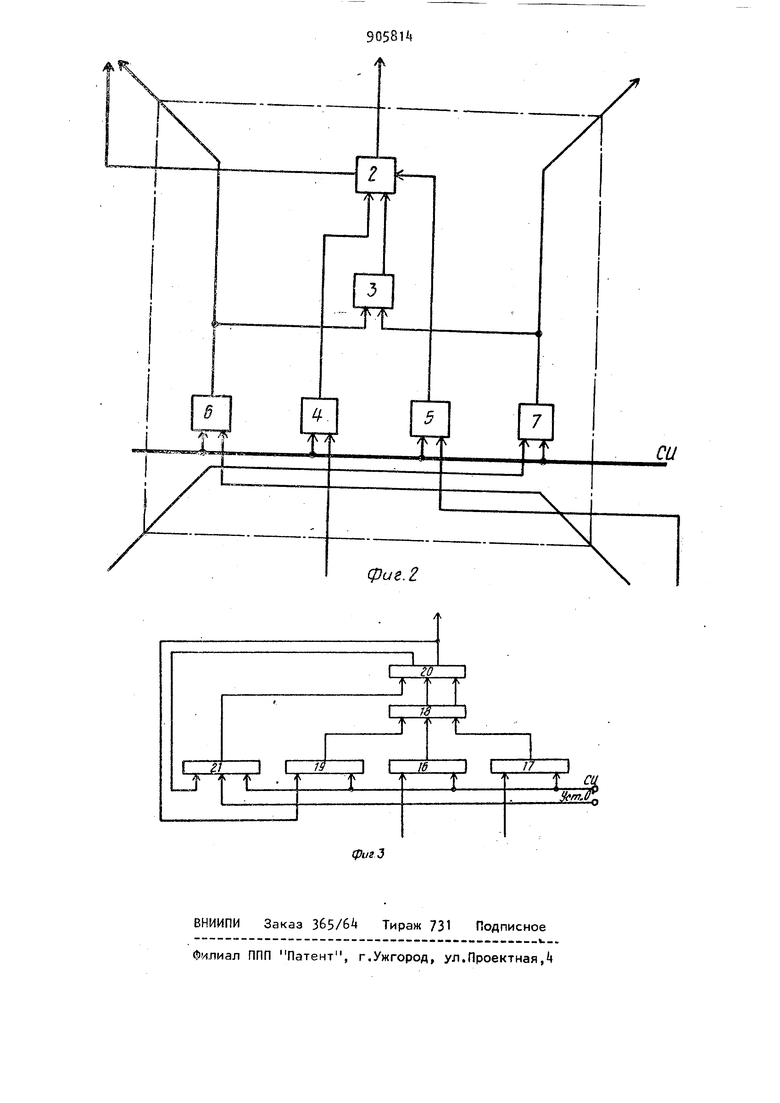

Накапливающий сумматор устройства содержит первую группу из (n+JojiQ N+Z) полусумматоров, вторую группу из (n+Sogtj N+l) полусумматоров, первый (n+JogijN)-разрядный, регистр, второй (п+Еод|К+1)-разрядный регистр,третий и четвертый (п+2)-разрядные регистры, причем тактовые входы первого, второго, третьего и четвертого регистров объединены и являются вторым управляющим входом накапливающего сумматора, информационные входы третьего и четвертого регистров являются соответственно вторым и первым информационными входами накапливающего сумматора, (п+1) младшие разряды третьего и четвертого регистров поразрядно соединены с первыми и вторыми входами соответствующих (п+1)-х младших полусумматоров первой группы, старшие разряды третьего и четвертого регистров соответственно соединены с первым и вторым входами (2 + 1)-го полусумматора перьой группы, третьи входы () старших полусумматоров первой группы соединены поразрядно с выходами второго регистра, выходы (n+ og N-t-1) младших и выходы (n+ ogftN+l) старших полусумматоров первой группы поразрядно соединены с первыми и . вторыми входами полусумматоров второй группы, выходы первого регистра соответственно соединены с третьими входами (n+fiopi N) старших полусумматоров второй группы, выходы () младших полусумматоров вторт й группы поразрядно соединены с информационными входами первого регистра, выходы (n+Eogi N+l) полусумматоров второй группы поразрядно соединены с информационными входами второго регистра и являются выходами накапливающего сумматора, вход установки в ноль первого регистра является первым управляющим входом Hc кaпливающего сумматора.

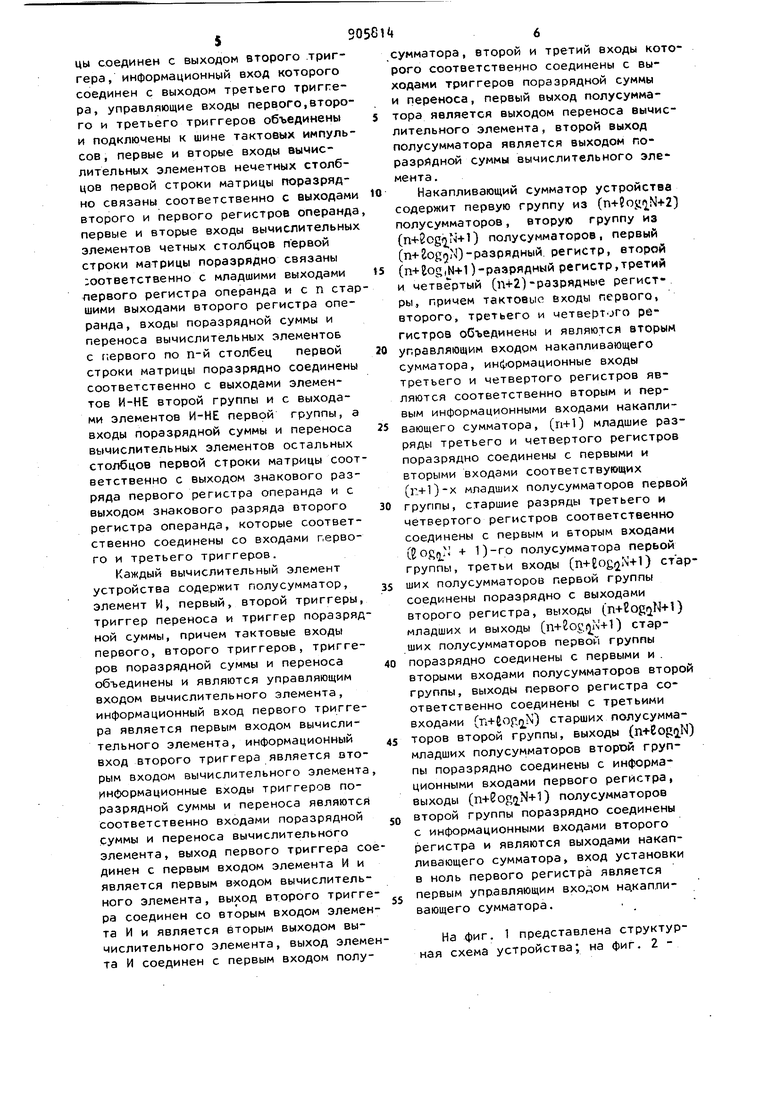

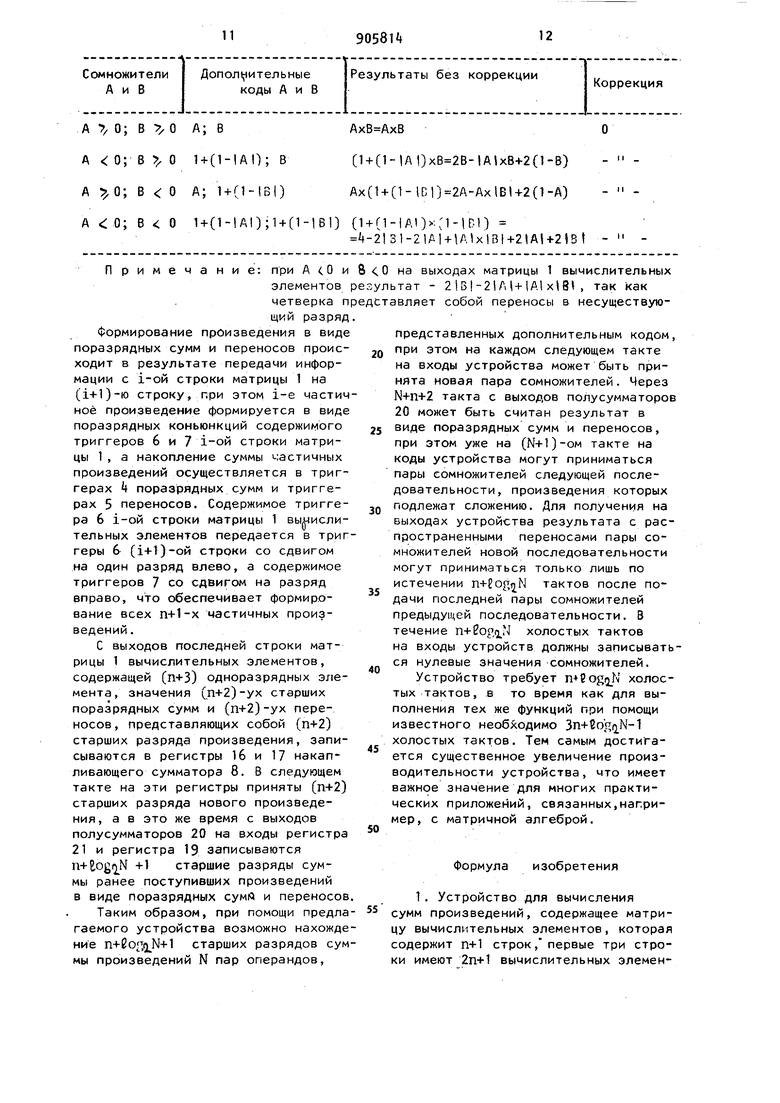

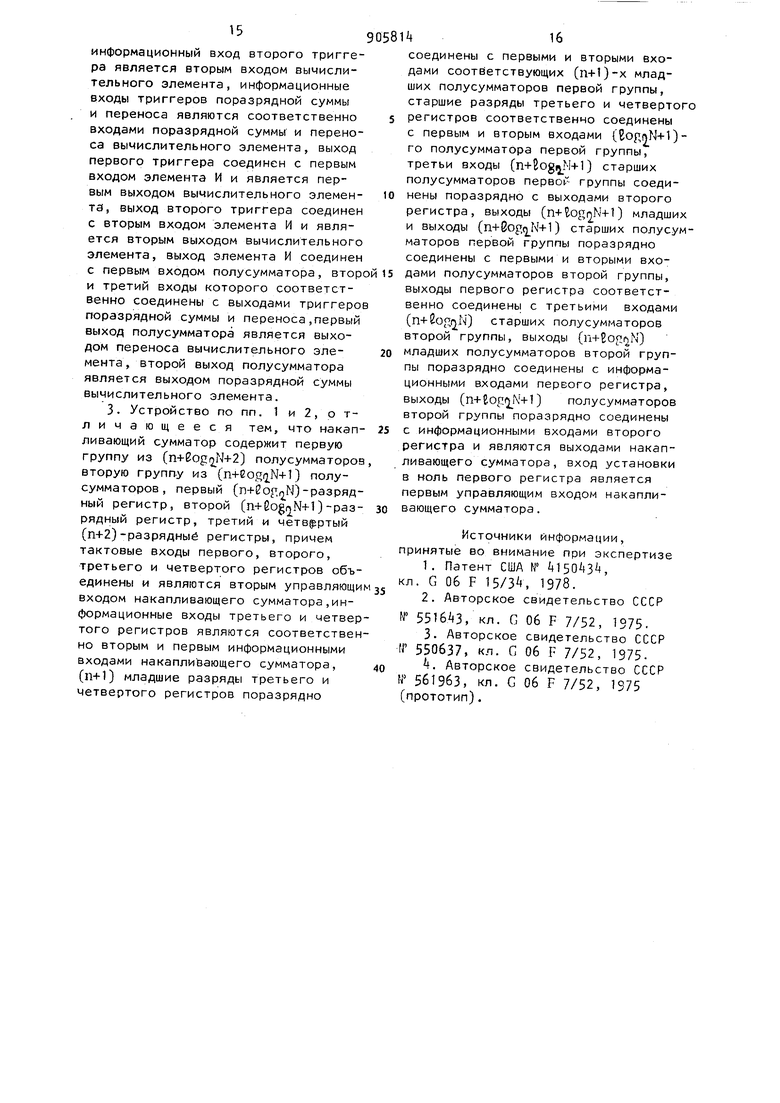

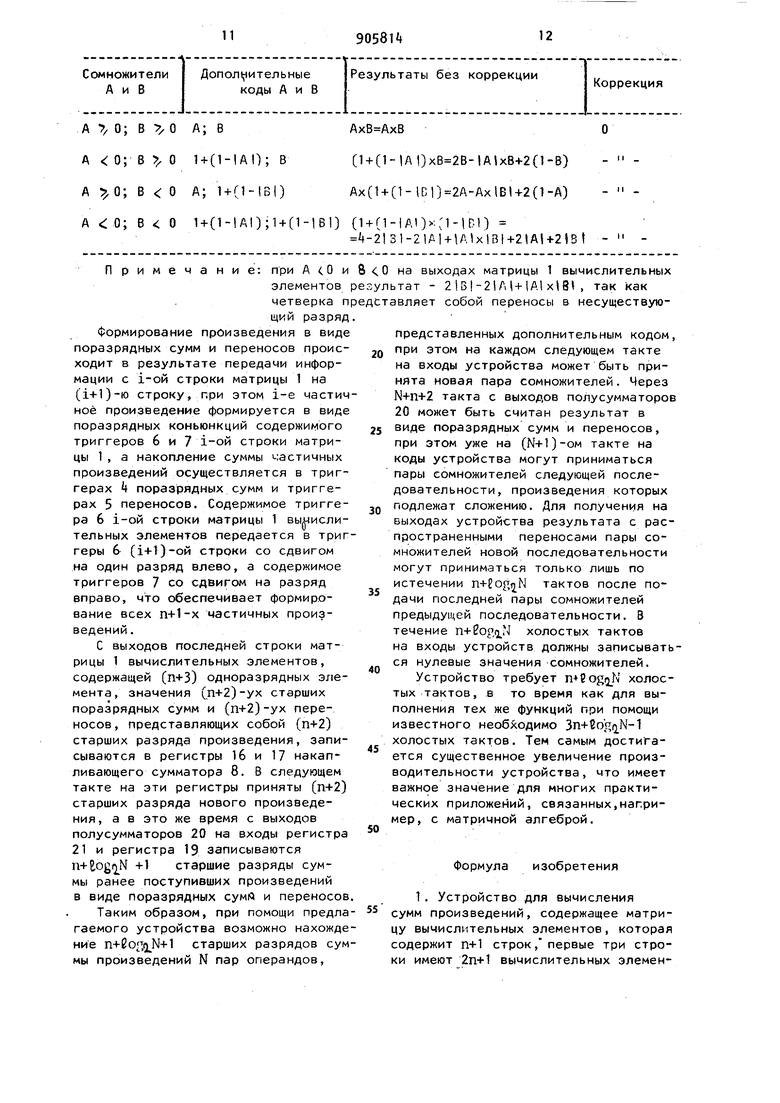

На фиг. 1 представлена структурная схема устройства; на фиг. 2 7структурная схема вычислительного элемента; на фиг. 3 структурная схема накапливающего сумматора. Устройство содержит матрицу ) вычислительных элементов, каждый вычислительный элемент включает в себя полусумматор 2, элемент 3 , триггер k поразрядной суммы ,триггер 5 переноса, триггеры 6 и 7, накапливающий сумматор 8, регистры 9 и 10 операнда, первую и вторую группу элементов 11 и 12 И-НЕ, триггеры . накапливающий суматор 8 содержит fn+2)-разрядные регистры 16 и 17, первую группу полусумматоров 18,(n+2opnN+1)-разрядный регистр 19,вторую группу полусумматоров 20,(n+5of Q N)Разрядный регистр 21. 8 устройстве для вычисления сумм произведений первая входная шина соединена с информационными входами регистра 9 операнда, вторая входная шина соединена с информацио ными входами регистра 10 операнда, выходы значащих разрядов регистра 9 операнда и регистра 10 операнда соответственно соединены с первыми вх дами элементов И-НЕ 11 и 12, вторые входы элементов И-НЕ 11 соединены с выходом знакового разряда регистр 10 операнда, вторые входы зле иентов М-НЕ 12 соединены с выходом знаково го разряда регистра 9 операнда, пер вые и вторые информационные входы накапливающего сумматора 8 соответственно соединены с (п+2) младшими выходами и с (п+2) старшими выходам вычислительных элементов последней строки матрицы 1, первый управляющий вход накапливающего сумматора 8 подключен к шине установки в ноль, выходы накапливающего сумматора 8 соединены с выходной шиной устройства, шина тактовых импульсов соединена со вторым управляющим входом накапливающего сумматора 8, с управ ляющим входом каждого вычислительно го элемента матрицы 1, с управляющи входами регистров 9 и 10 операнда, первый И второй выходы каждого (i,j)-ro вычислительного элемента (i 1,2,...,nj j 2,3,.,.,2n) сое динены соответственно с первым вхо дом (i+1 , j-1)-ro вычи(5лительного элемента и вторым входом (i+1, j+l)-ro вычислительного элемента, а выходы поразрядной суммы и переноса - соответственно со входом поразрядной суммы (i+1, i)ro вычислитель ного элемента и входом переноса (1+1, j-1)-ro вычислительного элемента, первый выход каждого (i,j)-ro вычислительного элемента (,2,..., п, ) соединен со вторым входом (1+1, j)-ro вычислительного элемента, а выход поразрядной суммы - со входом поразрядной суммы fi+1,j)-ro вычислительного элемента, выход переноса (i,j)-ro вычислительного элемента (1 1,2, j 2п+1) соединен с входом переноса (i+1,j)-ro вычислительного элемента, вход переноса (2п+1)-го вычислительного элемента второй строки матрицы 1 соединен с выходом триггера 1 ii, вход переноса (2п+1)-го вычислительного элемента третьей строки матрицы 1 соединен с выходом триггера 15, информационный вход которого соединен с выходом триггера 13, управляющие входы триггеров объединены и подключены к шине тактовых импульсов, первые и вторые входы вычислительных элементов нечетных столбцов первой строки матрицы 1 поразрядно связаны соответственно с выходами регистров S и 10 операнда, первые и вторые входы вычислительных элементов четных столбцов первой строки матрицы поразрядно связаны соответственно с п младшими выходами регистра 9 операнда и с п старшими выходами регистра 10 операнда, входы поразрядной суммы и переноса вычислительных элементов с первого по п-й столбец первой строки матрицы 1 поразрядно соединены соответственно с выходами элементов И-НЕ 12 и с выходами элементов И-НЕ П, а входы поразрядной суммы и переноса вычислительных элементов остальных столбцов первой строки матрицы 1, соответственно с выходом знакового разряда регистра 9 операнда и с выходом знакового разряда регистра 10 операнда, которые соответственно соединены со входами риггера 1 и триггера 13, тактовые входы триггеров 6 и 7) триггера 4 поразрядной суммы и триггера 5 переноса объединены и являются управляющим входом вычислительного элемента, информационный вход триггера б является первым входом вычисли- . тельного элемента, информационный вход триггера 7 является вторым входом вычислительного элемента, информационные входы триггера 9 поразрядной суммы и триггера 5 переноса являются соответственно вх дами поразрядной суммы и переноса вычислительного элемента, выход три| гера 6 соединен с первым входом элемента И 3 и является первым входом вычислительного элемента матрицы 1, выход триггера 7 соединен со вторым входом элемента И 3 и явл ется вторым выходом вычислительного элемента матрицы , выход элемента 3 соединен с первым входом полусумматора 2, второй и третий входы которого соответственно соединены с (выходами триггера 4 поразрядной сум мы и триггера 5 переноса, первый выход полусумматора 2 является выходом переноса вычислительного элемента матрицы 1, второй выход полусумматора 2 является выходом поразрядной суммы вычислительного элемента матрицы 1, тактовые входы регистров 16, 17, 13 и 21 объединены и являются вторым управляющим вхо дом накапливающего сумматора 8, информационные входы регистра 16 и регистра 17 являются соответственно вторым и первым информационными вхо дами накапливающего сумматора 8, (п+1) младших разрядов регистров 16 и 17 поразрядно соединены с первыми и вторыми входами соответствующи (п+1) младших полусумматоров 18, старшие разряды регистров 16 и 17 соответственно соединены с первым и вторым входами ;BognN+1)-ro полусумматора 18, третьи входы (n+EogQN старших полусумматоров 18 соединены поразрядно с выходами регистра 15, выходы (n+Eogij N +1) младших и выходы () старших полусумматоров 18 поразрядно соединены с первыми и вторыми входами полусумматоров 20, выходы регистра 21 соответственно соединены с третьими входами (n+Eon N) старших полусумматоров 20 выходы ri+5Qj,) младших полусумматоров 20 поразрядно соединены с информационными входами регистра -21, выходы (n+Jo. +1 полусумматоров 20 поразрядно соединены с информационными входами регистра 19 и являются выходами накапливающего сумматора 8, вход установки в ноль регистра 21 является первым управля 4 ющим входом накапливающего суммато ра 8. Устройство работает следующим образом. В первом такте на входы регистра 9 операнда и на входы регистра 10 операнда принимается первая пара сомножителей , представленная дополнительным двоичным кодом. Во втором такте содержимое указанных регистров передается на триггеры 6 и. 7 первой строки матрицы 1 вычислительных элементов, причем благодаря имеющимся жестким связям между регистрами 9 и 10 и матрицей 1 вычислительных элементов в триггеры 6 первой строки матрицы 1 вычислительных элементов передается код ЬдЯ-, Ь,а., ...,Ь,ау, а в триггеры 7 - код , a,jb,. ..,. Вместе с этим в зависимости от :знаков сомножителей на триггеры k поразрядной суммы и триггеры 5 переноса первой строки матрицы 1 выЧислительных элементов через первую }и вторую группы элементов И-НЕ 11 12 запишутся удвоенные обратные коды содержимого регистров 9 и 10. При этом, если произошла передача удвоенного обратного кода какоголибо из сомножителей на входы матрицы 1, то в триггер 13 или в триггер 1 записана единица, предназначенная для формирования удвоенного дополнительного кода этого сомножителя. Передама на входы матрицы 1 вычислительных элементов удвоенного дополнительного кода содержимого регистра 9, если первый сомножитель меньше нуля и наоборот, представляет собой коррекцию результата, так как в ре зультате перемножения в матрице 1 вычислительных элементов сомножителей, представленных дополнительным двоичным кодом, причем знаковые разряды сомножителей участвуют в выполняемой операции наравне со значащими, происходит искажение результата. В этом же такте на входы регистров 9 и 10 операнда принимается новая пара сомножителей. Зависимость результатов от знаков сомножителей представлена в таблице.

Допол1 ительные

Сомножители коды А и В A и В О;В / ОА; В 0;В / О1 + (1-|АП; В А: 0;В ОА; 1 + (1-1Б|) 0;В О1 + (1-|А1);1 + (1-1 Примечание: ЩИ И разряд формирование произведения в виде поразрядных сумм и переносов происходит в результате передачи информации с i-ой строки матрицы 1 на (1+1)-ю строку, при этом i-e частич ное произведение формируется в виде поразрядных коньюнкций содержимого триггеров 6 и 7 i-ой строки матрицы 1 , а накопление суммы частичных произведений осуществляется в триггерах k поразрядных сумм и триггерах 5 переносов. Содержимое триггера 6 i-ой строки матрицы 1 вычислительных элементов передается в триг геры 6 (i+l)-oй строки со сдвигом на один разряд влево, а содержимое триггеров 7 со сдвигом на разряд вправо, что обеспечивает формирование всех n+1-x частичных произведений. С выходов последней строки матрицы 1 вычислительных элементов, содержащей (п+3) одноразрядных элемента, значения (п+2)-ух старших поразрядных сумм и (п+2)-ух переносов, представляющих собой (п+2) старших разряда произведения, записываются в регистры 16 и 17 накапливающего сумматора 8. В следующем такте на эти регистры приняты (п+2) старших разряда нового произведения , а в это же время с выходов полусумматоров 20 на входы регистра 21 и регистра 19 записываются n+togQ N +1 старшие разряды суммы ранее поступивших произведений в виде поразрядных сумй и переносов Таким образом, при помощи предла гаемого устройства возможно нахожде ние , старших разрядов сум мы произведений N пар операндов.

Результаты без коррекции

Коррекция I) (1 + (1-|AI)-:i-(Dl) при А 0 и на выходах матрицы 1 вычислительных элементов результат - 2 |Б|-21А(+lAtх 8 , так как четверка представляет собой переносы в несуществуюАхВ АхВCI + CI-IA |)xB 2B-|AUB+2(1-B) Ax(l4-(l-|Bl)2A-AxlBI+2(1-A) -2 31-21А1 + 1Л1х1В|+21А|-ь21В t представленных дополнительным кодом, при этом на каждом следующем такте на входы устройства может быть принята новая пара сомножителей. Через N+n+2 такта с выходов полусумматоров 20 может быть считан результат в виде поразрядных сумм и переносов, при этом уже на (N+1)-OM такте на коды устройства могут приниматься пары сомножителей следующей последовательности, произведения которых подлежат сложению. Для получения на выходах устройства результата с распространенными переносами пары сомножителей новой последовательности могут приниматься только лишь по истечении n+EognN тактов после подачи последней пары сомножителей предыдущей последовательности. В течение n+Eogij N холостых тактов на входы устройств должны записываться нулевые значения сомножителей. Устройство требует n+Cogr N холостых тактов, в то время как для выполнения тех же функций при помощи известного необходимо 3n+2oV( холостых тактов. Тем самым достигается существенное увеличение производительности устройства, что имеет важное значение для многих практических приложений, связанных,например, с матричной алгеброй. Формула изобретения 1. Устройство для вычисления сумм произведений, содержащее матрицу вычислительных элементов, которая содержит п+1 строк,первые три строки имеют 2п+1 вычислительных элементов, каждая последующая строка матрицы имеет на один вычислительный элемент меньше, последняя строка со держит п+3 вычислительных элементов, (п+1)-разрядные первый и второй регистры операнда (где п - разрядность операндов), первую и вторую группу элементов И-НЕ, накапливающи сумматор, причем первая входная шина соединена с информационными входами первого регистра операнда, вторая входная шина соединена с информационными входами второго ре,гистра операнда, выходы значащих ра рядов первого регистра операнда и второго регистра операнда соответственно соединены с первыми входами элементов И-НЕ первой и второй груп вторые входы элементов И-НЕ первой группы соединены с выходом знаковог разряда второго регистра операнда, вторые входы элементов И-НЕ второй группы соединены с выходом знакового разряда первого регистра операнда, первые и вторые информационные входы накапливающего сумматора соответственно соединены с (п+2) младшими выходами и с (п+2) старшими выходами вычислительных элемен тов последней строки матрицы,первый управляющий вход накапливающего сумматора подключен к шине yctaHoeкй в ноль, выходы накапливающего су матора соединены с выходной шиной устройства, шина тактовых импульсов соединена с вторым управляющим входом накапливающего сумматора, с управляющим входом каждого вычислител ного элемента матрицы, с управляющи ми входами первого и второго регист ров операнда, отличающеес тем, что, с целью повышения произво дительности устройства, в него введены первый, второй, третий триггеры, причем первый и второй выходы каждого (i,i)-ro вычислительного элемента ( ,...,п,j 2,...,2п) сое динены соответственно с первым входом i+1 , j-1)-ro вычислительного элемента и вторым входом (i+1, j+1)-ro вычислительного элемента, а выходы поразрядной суммы и перено са соответственно с входом -поразрядной суммы (i+l,1)-ro вычислитель ного элемента и входом переноса (i+1, j-1)-ro вычислительного элемента, первый выход каждого (i,j)-r вычислительного элемента (,2,... n,j 1) соединен с вторым входом . (1+1,J)-ГО Вычислительного элемента, а выход поразрядной суммы с входом поразрядной суммы (i+l,j)-ro вычислительного элемента, выход переноса (1,j)-ro вычислительного элемента (,2,) соединен с входом переноса (1+1,j)-го вычислительного элемента, вход переноса (2п+1) -го вычислительного элемента второй строки матрицы соединен с выходом первого триггера, вход переноса (2п+1)-го вычислительного элемента третьей строки матрицы соединен с выходом второго триггера,информационный вход которого соединен с выходом третьего триггера, управляющие входы первого, второго и третьего триггеров объединены и подключены к шине тактовых импульсов, первые и вторые входы вычислительных элементов нечетных столбцов первой строки матрицы поразрядно свя;заны соответственно с выходами второго и первого регистров операнда, первые и вторые входы вычислительных элементов четных столбцов первой строки матрицы поразрядно связаны соответственно с п младшими выходами первого регистра операнда и с п старшими выходами второго регистра операнда, входы поразрядной суммы и переноса вычислительных элементов с первого по п-й столбец первой строки матрицы поразрядно соединень соответственно с выходами элементов И-НЕ второй группы и с выходами элементов И-НЕ первой группы, а входы поразрядной суммы и переноса вычислительных элементов остальных столбцов первой строки матрицы соответственно с выходом знакового разряда первого регистра.операнда и с выходом знакового разряда второго регистра операнда, которые соответственно соединены с входами первого и третьего триггеров. 2, Устройство по п.. 1 , о т л ичающееся тем, что каждый вычислительный элемент содержит полусумматор, элемент И,первый,второй триггеры, триггер переноса и триггер поразрядной суммы, причем тактовые входы первого, второго триггеров, триггеров поразрядной суммы и переноса объединены .и являются управляющим входом вычислительного элемента, информационный вход первого триггера является первым входом вычислительного элемента.

информационный вход второго триггера является вторым входом вычислительного элемента, информационные входы триггеров поразрядной суммы и переноса являются соответственно входами поразрядной суммы и переноса вычислительного элемента, выход первого триггера соединен с первым входом элемента И и является первым выходом вычислительного элемента, выход второго триггера соединен с вторым входом элемента И и является вторым выходом вычислительного элемента, выход элемента И соединен с первым входом полусумматора, второ и третий входы которого соответственно соединены с выходами триггеров поразрядной суммы и переноса,первый выход полусумматора является выходом переноса вычислительного элемента, второй выход полусумматора является выходом поразрядной суммь вычислительного элемента.

3. Устройство по пп. 1 и 2, о тличающееся тем, что накапливающий сумматор содержит первую группу из (n+Bogi N+2) полусумматоров вторую группу из (n+CogQiN+1) полусумматоров, первый ()-разрядный регистр, второй (n+CogQ N+1)-pa3рядный регистр, третий и четвертый (п+2)-разрядные регистры, причем тактовые входы первого, второго, третьего и четвертого регистров объединены и являются вторым управляющи входом накапливающего сумматора,информационные входы третьего и четвертого регистров являются соответственно вторым и первым информационными входами накапливающего сумматора, (ii+1) младшие разряды третьего и четвертого регистров поразрядно

соединены с первыми и вторыми входами соответствующих (п+1)-х младших полусумматоров первой группы, старшие разряды третьего и четверто регистров соответственно соединены с первым и вторым входами (BopnN+l)го полусумматора первой группы, третьи входы (n+2ogij N+1) старших полусумматоров первое группы соединены поразрядно с выходами второго регистра, выходы (n+tognN+1) младши и выходы (n+6og() старших полусуматоров первой группы поразрядно соединены с первыми и вторыми входами полусумматоров второй группы, выходы первого регистра соответственно соединень с третьими входами () старших полусумматоров второй группы, выходы (n+2opi N) младших полусумматоров второй группы поразрядно соединены с информационными входами первого регистра, выходы (п+6оро +1) полусумматоров второй группы поразрядно соединены с информационными входами второго регистра и являются выходами накапливающего сумматора, вход установки в ноль первого регистра является первым управляющим входом накапливающего сумматора.

Источники информации, принятые во внимание при экспертизе

1 . Патент США № iti5043 4, кл. G 06 F 15/3, 1978.

2. Авторское свидетельство СССР

N 5516АЗ, кл. С 06 F 7/52, 19753. Авторское свидетельство СССР

N 550637, кл. С Об F 7/52, 1975. Авторское свидетельство СССР

N 561963, кл. С Об F 7/52, 1975

(прототип).

г: 2 .7 3 . . « 1P/7.J fjflJ,

W4-ЦЛЦ

Уст, О

си

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для вычисления сумм произведений | 1988 |

|

SU1569826A1 |

| Устройство вычисления сумм произведений | 1990 |

|

SU1718216A1 |

| Конвейерное множительное устройство | 1980 |

|

SU903866A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

Авторы

Даты

1982-02-15—Публикация

1980-06-16—Подача