Изобретение относится к вычисли- тельной технике и может быть использовано при построении высокопроизводительных конвейерных вычислительных средств, выполненных на узлах с большой степенью интеграции.

Цель изобретения - уменьшение аппаратурных затрат при вычислении скалярного произведения векторов и уменьшение аппаратурных затрат и увеличение быстродействия при вычислении поэлементного произведения -векторов,

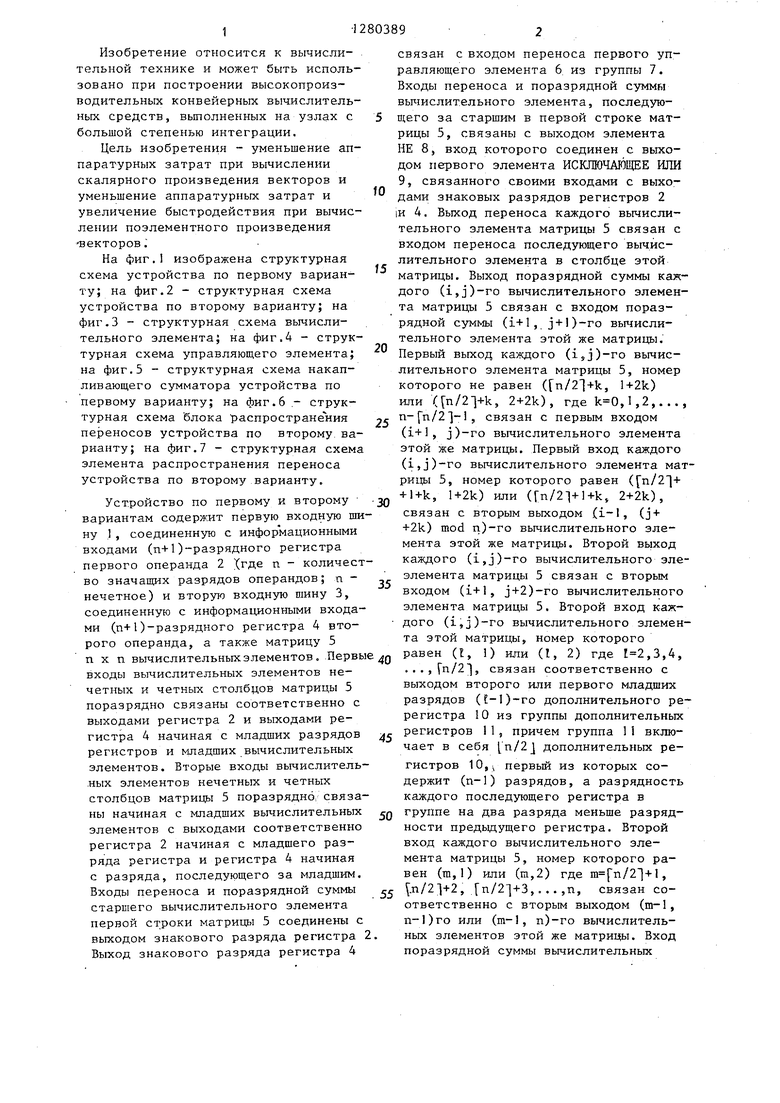

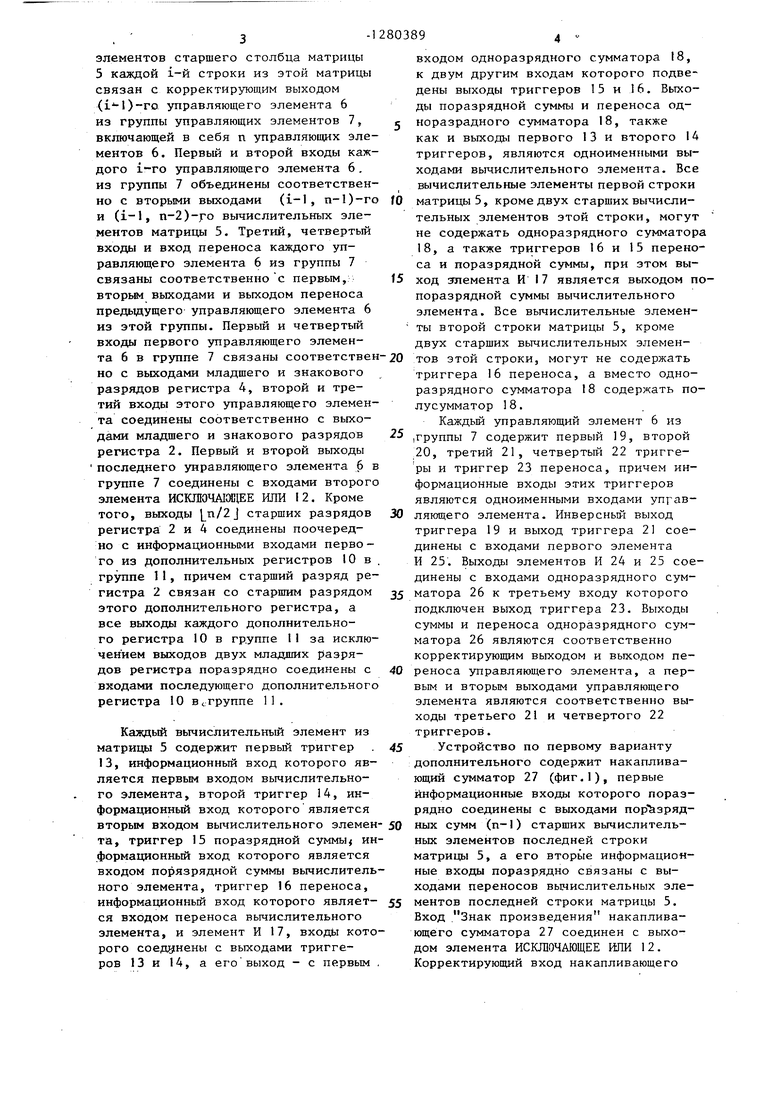

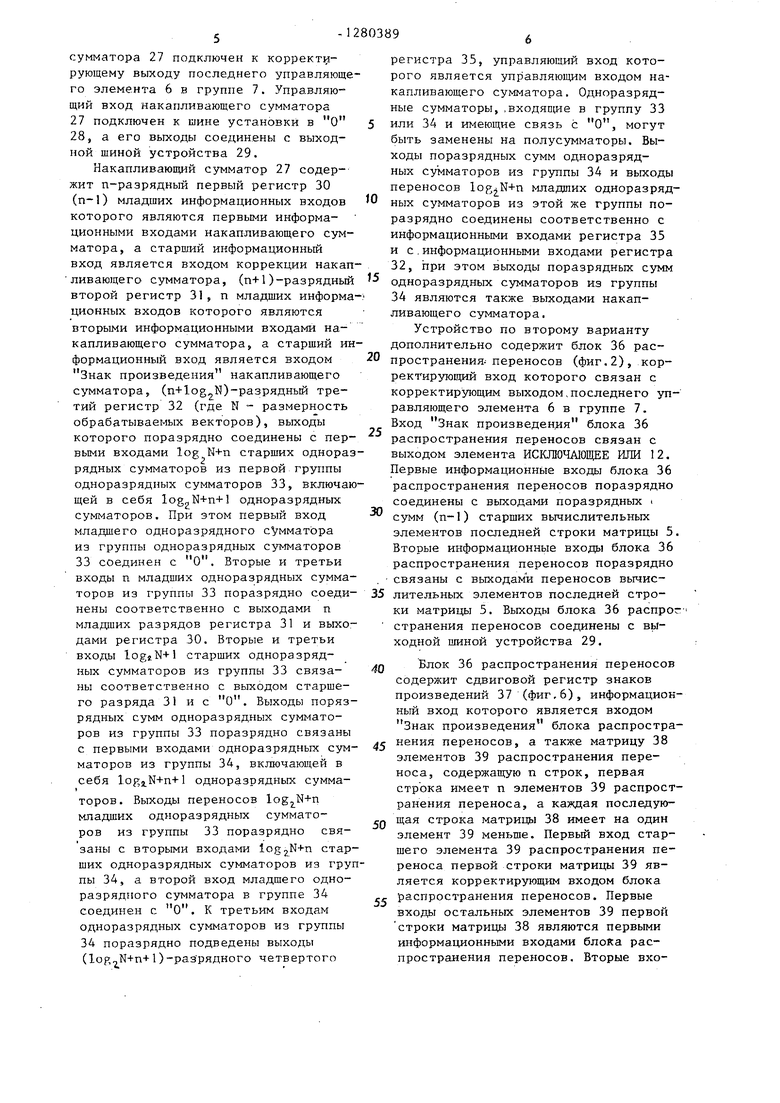

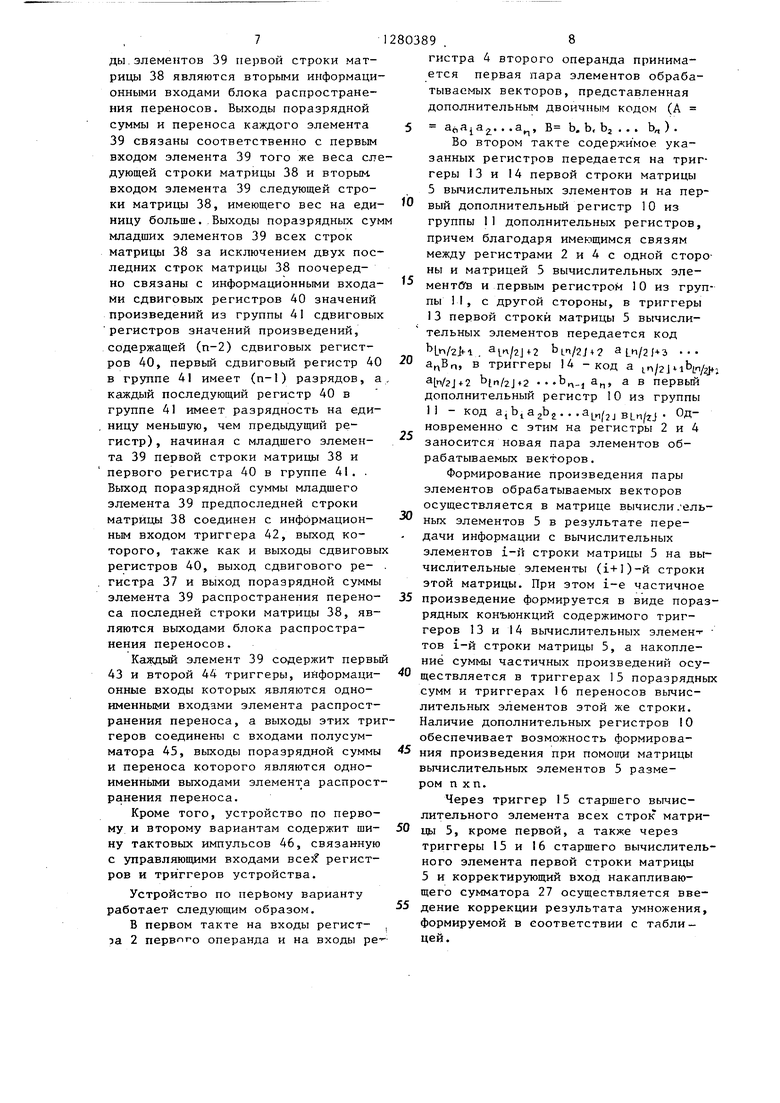

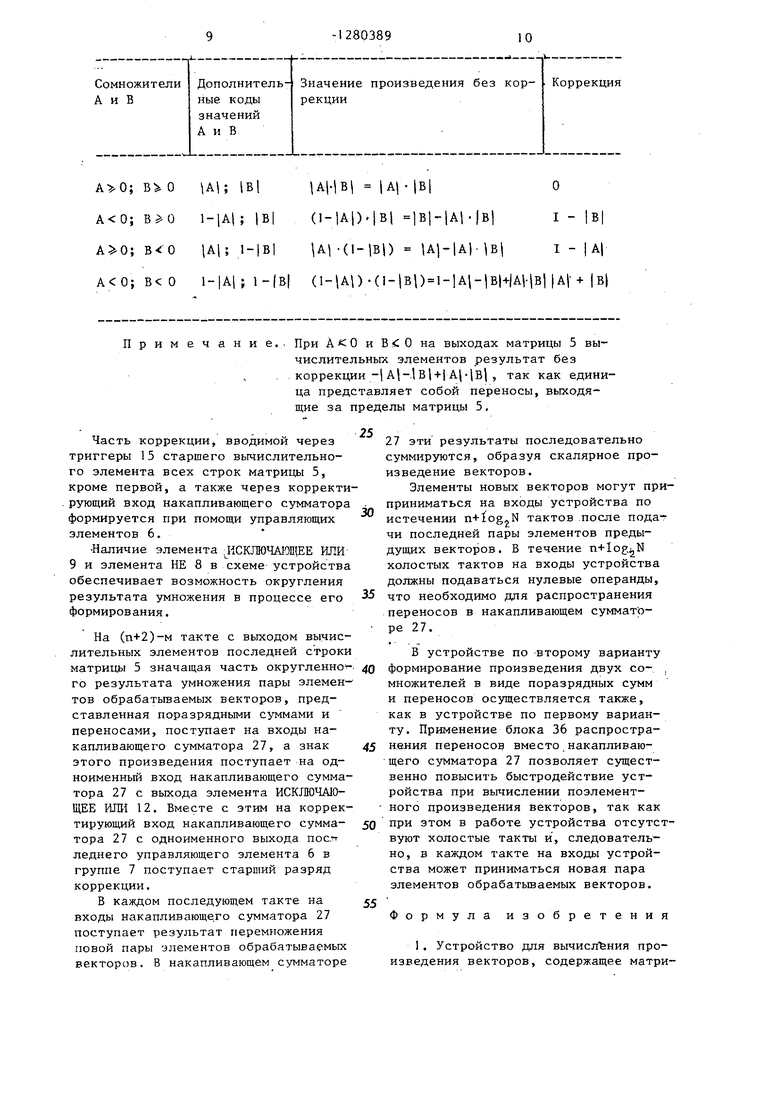

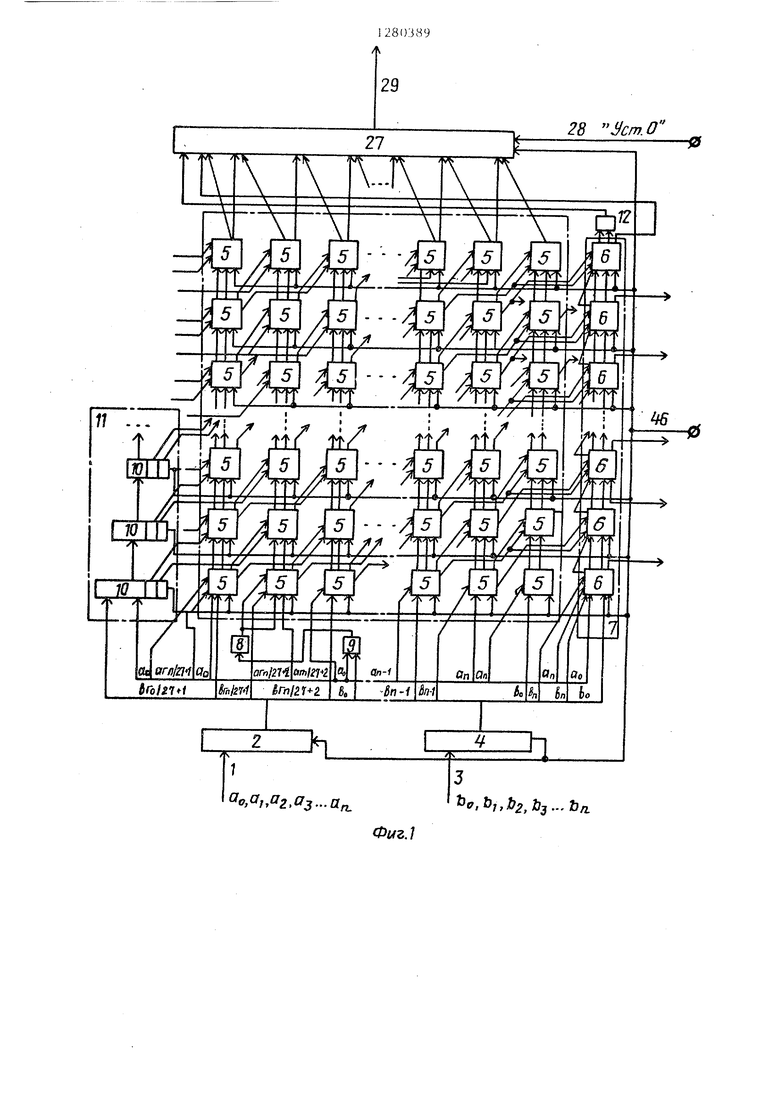

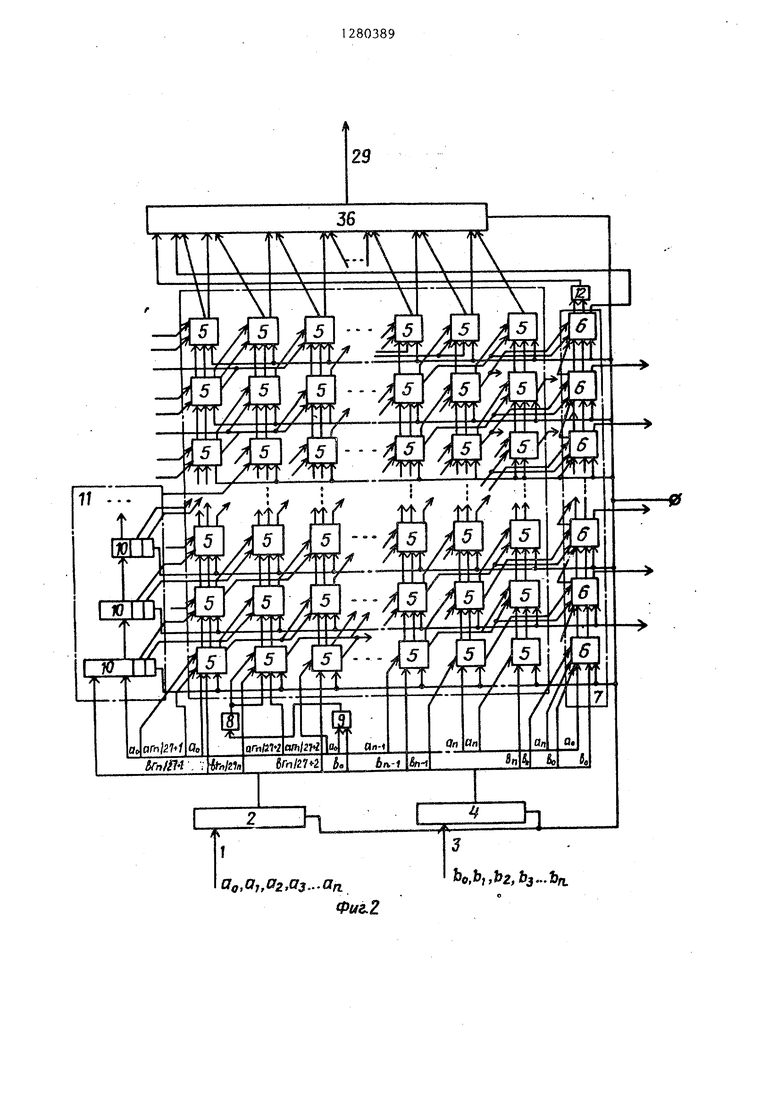

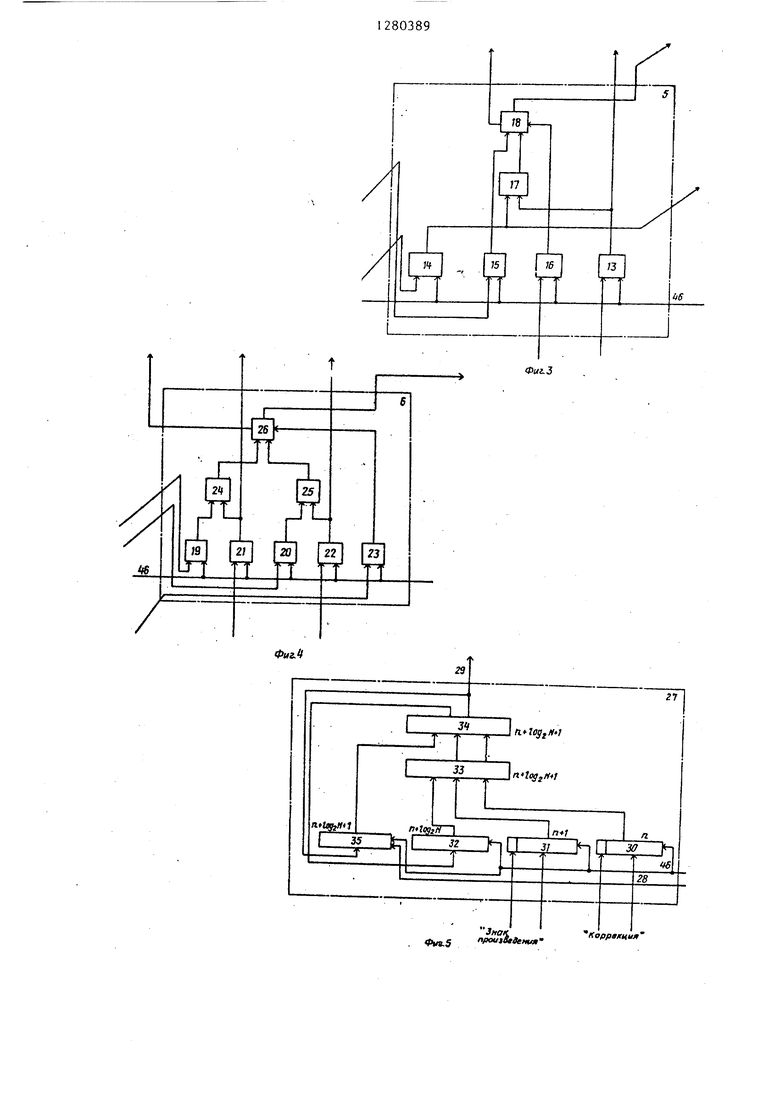

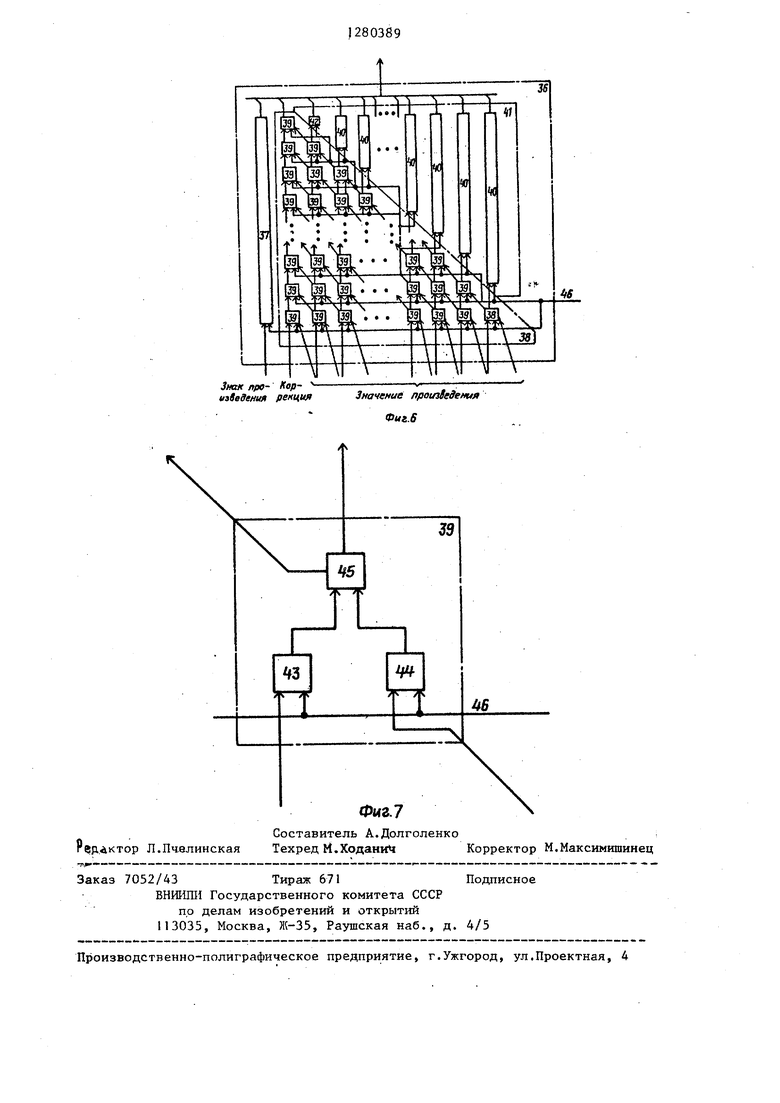

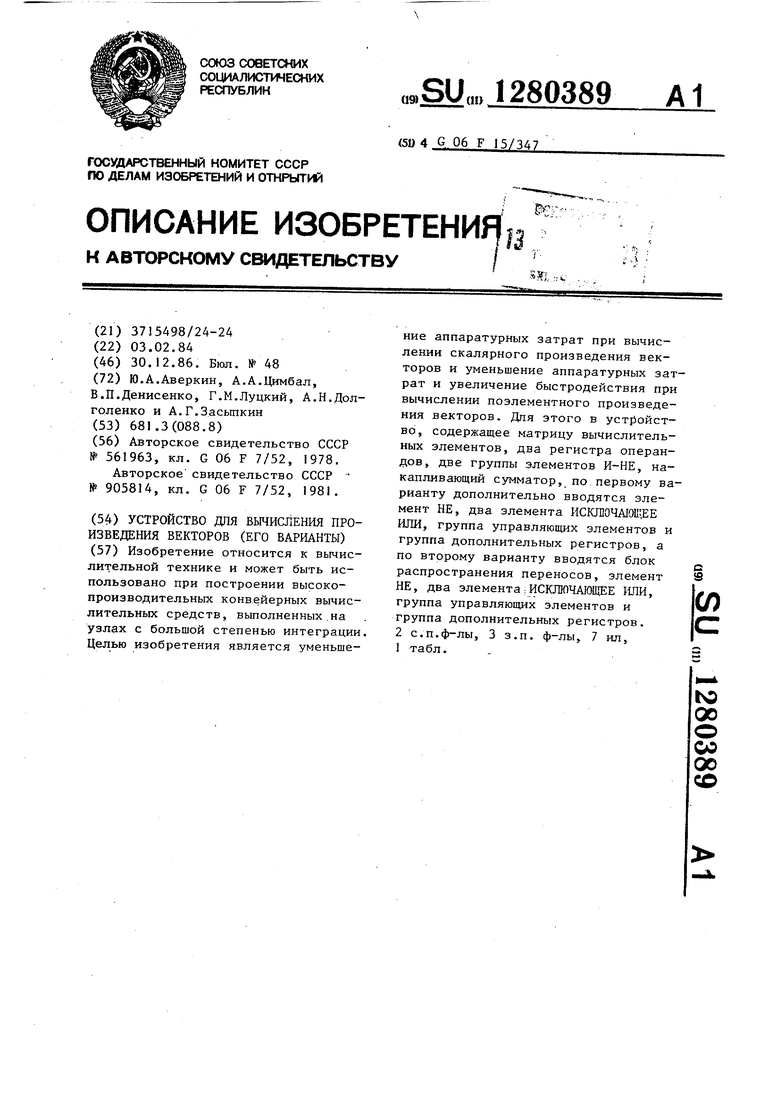

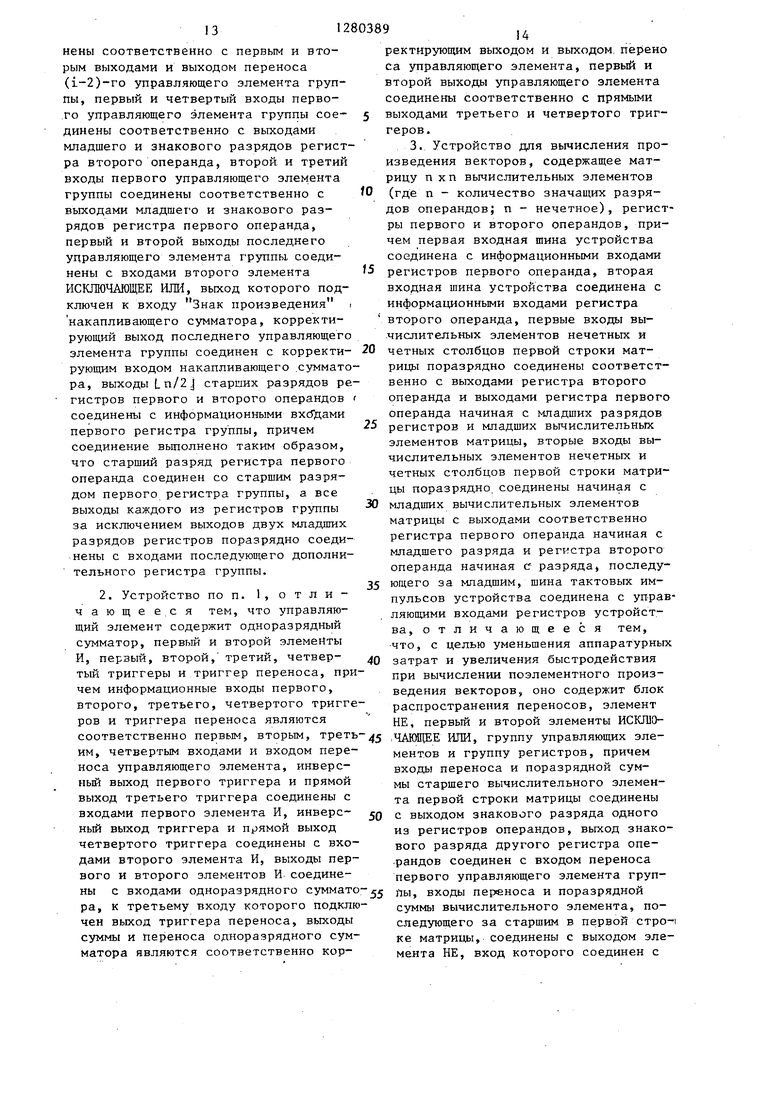

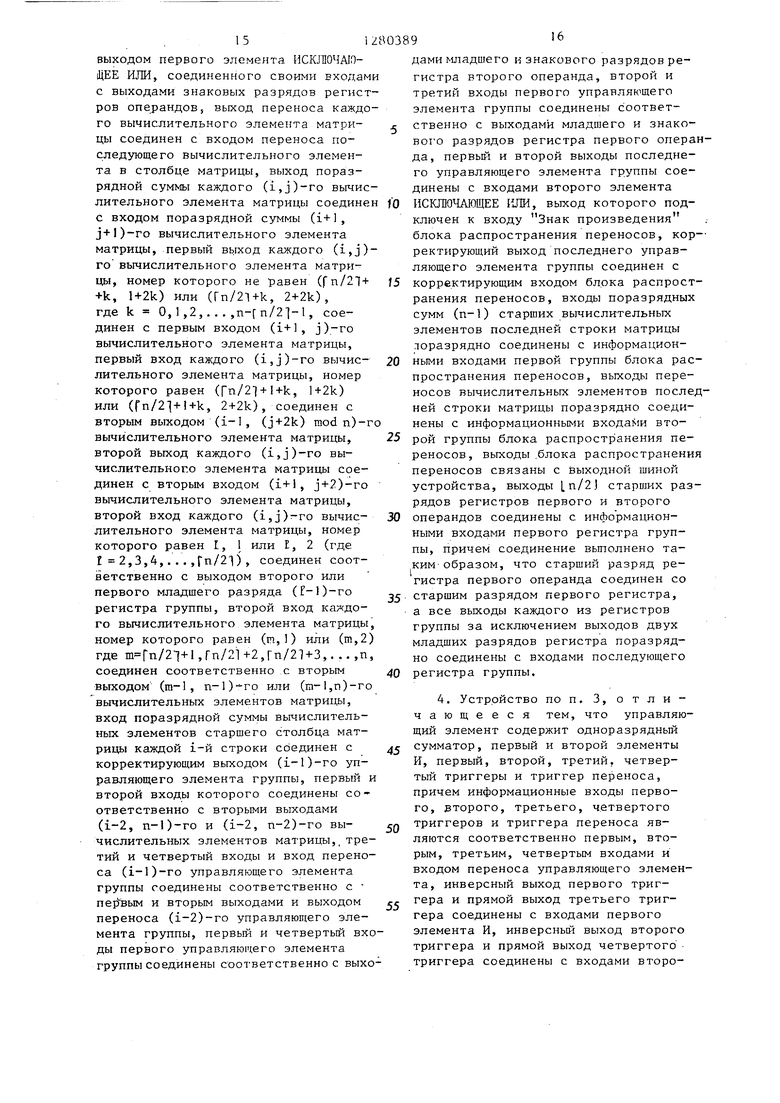

На фиг. изображена структурная схема устройства по первому варианту; на фиг.2 - структурная схема устройства по второму варианту; на фиг.3 - структурная схема вычислительного элемента; на фиг.4 - структурная схема управляющего элемента; на фиг.5 - структурная схема накапливающего сумматора устройства по первому варианту; на фиг.6 .- структурная схема блока распростране ния переносов устройства по второму варианту; на фиг.7 - структурная схема элемента распространения переноса устройства по второму варианту.

Устройство по первому и второму вариантам содержит первую входную шину I, соединенную с информационными входами (п+1)-разрядного регистра первого операнда 2 гц.е п - количество значащих разрядов операндов; п - нечетное) и вторую входную шину 3, соединенную с информационными входами (п+I)-разрядного регистра 4 второго операнда, а также матрицу 5 п X п вычислительныхэлементов. Первы входы вычислительных элементов нечетных и четных столбцов матрицы 5 поразрядно связаны соответственно с выходами регистра 2 и выходами регистра 4 начиная с младших разрядов регистров и младших вычислительных элементов. Вторые входы вычислительных элементов нечетных и четных столбцов матрицы 5 поразрядно/ связаны начиная с младших вычислительных элементов с выходами соответственно регистра 2 начиная с младшего разряда регистра и регистра 4 начиная с разряда, последующего за младшим. Входы переноса и поразрядной суммы старшего вычислительного элемента первой строки матрицы 5 соединены с выходом знакового разряда регистра Выход знакового разряда регистра 4

5

0

5

0

д

5

0

55

связан с входом переноса первого управляющего элемента 6 из группы 7. Входы переноса и поразрядной суммы вычислительного элемента, последующего за старшим в первой строке матрицы 5, связаны с выходом элемента НЕ 8, вход которого соединен с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9, связанного своими входами с выходами знаковых разрядов регистров 2 1И 4. Выход переноса каждого вычислительного элемента матрицы 5 связан с входом переноса последующего вычислительного элемента в столбце этой матрицы. Выход поразрядной суммы каждого (i,j)-ro вычислительного элемента матрицы 5 связан с входом поразрядной суммы (i+1, j+l)-ro вычислительного элемента этой же матрицы. Первый выход каждого (i5J)-ro вычислительного элемента матрицы 5, номер которого не равен (fn/2 l+k, l+2k) или (n/21+k, 2+2k), где ,I,2,..., n-fn/2 j-, связан с первым входом (i+1, j)-ro вычислительного элемента этой же матрицы. Первый вход каждого (i,j)-ro вычислительного элемента матрицы 5, номер которого равен ( +l+k, 1+2k) или (Гп/21+l+kj 2+2k), связан с вторым выходом (i-1, (j+ +2k) mod n)-ro вычислительного элемента этой же матрицы. Второй выход каждого (i,j)-ro вычислительного эле- элемента матрицы 5 связан с вторым входом (i+1, j+2)-ro вычислительного элемента матрицы 5. Второй вход каждого (i,j)-ro вычислительного элемента этой матрицы, номер которого равен (I, 1) или (I, 2) где ,3,4, ..,,fn/2 , связан соответственно с выходом второго или первого младших разрядов (C-l)-ro дополнительного ре- регистра 10 из группы дополнительных регистров 11, причем группа 11 включает в себя дополнительных регистров 10, первьй из которых содержит (п-1) разрядов, а разрядность каждого последующего регистра в группе на два разряда меньше разрядности предьщущего регистра. Второй вход каждого вычислительного элемента матрицы 5, номер которого равен (т,1) или (ш,2) где m n/21+I, . , ,. ,. ,п, связан соответственно с вторым выходом (т-1, п-1)го или (т-1, п)-го вычислительных элементов этой же матрицы. Вход поразрядной суммы вычислительных

W

элементов старшего столбца матрицы 5 каждой i-й строки из этой матрицы связан с корректирующим выходом ()-го управляющего элемента 6 из группы управляющих элементов 7, включающей в себя п управляющих элементов 6. Первый и второй входы кажого i-ro управляющего элемента 6, из группы 7 объединены соответственно с вторыми выходами (i-I, п-1)-го и (i-1, п-2)-го вычислительных элементов матрицы 5. Третий, четвертый входы и вход переноса каждого управляющего элемента 6 из группы 7 связаны соответственно с первым, вторым выходами и выходом переноса предьщущего управляющего элемента 6 из этой группы. Первый и четвертый входы первого управляющего элемента 6 в группе 7 связаны соответствен-20 но с выходами младшего и знакового разрядов регистра 4, второй и третий входы этого управляющего элемента соединены соответственно с выходами младшего и знакового разрядов регистра 2. Первый и второй выходы последнего управляющего элемента 6 в группе 7 соединены с входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12. Кроме того, выходы Ln/2J старших разрядов регистра 2 и 4 соединены поочередно с информационными входами перво - го из дополнительных регистров 10 в . группе 1I, причем старший разряд регистра 2 связан со старшим разрядом этого дополнительного регистра, а все выходы каждого дополнительного регистра 10 в группе 11 за исключением выходов двух младших разрядов регистра поразрядно соединены с входами последующего дополнительного регистра 10 в с группе 11.

15

35

25

30

40

Каждый вычислительный элемент из матрицы 5 содержит первый триггер 13, информационный вход которого является первым входом вычислительного элемента, второй триггер 14, информационный вход которого является

вторым входом вычислительного элемен- 50 ных сумм (п-1) старших вычислительта, триггер 15 поразрядной суммы информационный вход которого является входом порязрядной суммы вычислительного элемента, триггер 16 переноса.

информационный вход которого являет- 55ментов последней строки матрицы 5.

ся входом переноса вычислительногоВход .Знак произведения накапливаэлемента, и элемент И 17, входы кото-ющего сумматора 27 соединен с выхорого соеда нены с выходами трнгге-дом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12.

ров 13 и 14, а его выход - с первым ,Корректирующий вход накапливающего

0

входом одноразрядного сумматора 18, к двум другим входам которого подведены выходы триггеров 15 и 16. Выходы поразрядной суммы и переноса од- норазрадного сумматора 18, также как и выходы первого 13 и второго 14 триггеров, являются одноименными выходами вычислительного элемента. Все вычислительные элементы первой строки матрицы 5, кроме двух старших вычислительных элементов этой строки, могут не содержать одноразрядного сумматора 18, а также триггеров 16 и 15 переноса и поразрядной суммы, при этом вы- 5 ход элемента И I7 является выходом по- поразрядной суммы вычислительного элемента. Все вычислительные элемен- ты второй строки матрицы 5, кроме двух старших вычислительных элементов этой строки, могут не содержать триггера 16 переноса, а вместо одноразрядного сумматора 18 содержать полусумматор 18.

Каждьй управляющий элемент 6 из |Группы 7 содержит первый 19, второй 20, третий 21, четвертый 22 тригге- ры и триггер 23 переноса, причем информационные входы этих триггеров являются одноименными входами управляющего элемента. Инверсный выход триггера 19 и выход триггера 21 соединены с входами первого элемента И 25. ;Выходы элементов И 24 и 25 соединены с входами одноразрядного сум- 5 матора 26 к третьему входу которого подключен выход триггера 23. Выходы суммы и переноса одноразрядного сумматора 26 являются соответственно кoppeктиpyюшJ м выходом и выходом переноса управляющего элемента, а первым и вторым выходами управляющего элемента являются соответственно выходы третьего 21 и четвертого 22 триггеров.

Устройство по первому варианту дополнительного содержит накапливающий сумматор 27 (фиг.1), первые информационные входы которого поразрядно соединены с выходами пор &зряд5

0

0

5

ных элементов последней строки матрицы 5, а его вторые информационные входы поразрядно связаны с выходами переносов вычислительных элесумматора 27 подключен к корректирующему выходу последнего управляющего элемента 6 в группе 7. Управляющий вход накапливающего сумматора 27 подключен к шине установки в О 28, а его выходы соединены с выходной щиной устройства 29.

Накапливающий сумматор 27 содержит п-разрядный первый регистр 30 (п-1) младших информационных входов которого являются первыми информационными входами накапливающего сумматора, а старший информационный

регистра 35, управляющий вход которого является управляющим входом н капливающего сумматора. Одноразрядные сумматоры,.входяпще в группу 3 или ЗА и имеющие связь с О, могу быть заменены на полусумматоры. Выходы поразрядных сумм одноразрядных сумматоров из группы 34 и выход переносов младших одноразря ных сумматоров из этой же группы п разрядно соединены соответственно информационными входами регистра 3 и с.информационными входами регистр 32, при этом выходы поразрядных сум

вход является входом коррекции накапливающего сумматора, (п+1)-разрядный 5 одноразрядных сумматоров из группы второй регистр 31, п младших информа-) 34 являются также выходами накап

ционных входов которого являются вторыми информационными входами накапливающего сумматора, а старший информационный вход является входом Знак произведения накапливающего сумматора, (n+.)-paзpядный третий регистр 32 (где N - размерность обрабатываемых векторов), выходы которого поразрядно соединены с первыми входами log N+n старших одноразрядных сумматоров из первой группы одноразрядных сумматоров 33, включающей в себя log N+n+l одноразрядных сумматоров. При этом первый вход младщего одноразрядного сумматора из группы одноразрядных сумматоров 33 соединен с О. Вторые и третьи входы п младших одноразрядных сумматоров из группы 33 поразрядно соединены соответственно с выходами п младших разрядов регистра 31 и выходами регистра 30. Вторые и третьи входы logiN+l старших одноразрядных сумматоров из группы 33 связаны соответственно с выходом старшего разряда 31 и с О. Выходы поряз- рядных сумм одноразрядных сумматоров из группы 33 поразрядно связаны с первыми входами одноразрядных сумматоров из группы 34, включающей в

себя l.ogj N+n+1 одноразрядных сумма-

торов. Выходы переносов log.N+n младших одноразрядных сумматоров из группы 33 поразрядно связаны с вторыми входами log N-i-n старших одноразрядных сумматоров из группы 34, а второй вход младшего одноразрядного сумматора в группе 34 соединен с О. К третьим входам одноразрядных сумматоров из группы 34 поразрядно подведены выходы (1ор,,К+п+1)-раз рядного четвертого

регистра 35, управляющий вход которого является управляющим входом накапливающего сумматора. Одноразрядные сумматоры,.входяпще в группу 33 или ЗА и имеющие связь с О, могут быть заменены на полусумматоры. Выходы поразрядных сумм одноразрядных сумматоров из группы 34 и выходы переносов младших одноразрядных сумматоров из этой же группы поразрядно соединены соответственно с информационными входами регистра 35 и с.информационными входами регистра 32, при этом выходы поразрядных сумм

одноразрядных сумматоров из группы 34 являются также выходами накап

ливающего сумматора.

Устройство по второму варианту дополнительно содержит блок 36 распространения- переносов (фиг.2), корректирующий вход которого связан с корректирующим выходом,последнего управляющего элемента 6 в группе 7. Вход Знак пpoизвeдeн я блока 36 распространения переносов связан с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12. Первые информационные входы блока 36 распространения переносов поразрядно соединены с выходами поразрядных

сумм (п-1) старших вычислительных элементов последней строки матрицы 5. Вторые информационные входы блока 36 распространения переносов поразрядно связаны с выходами переносов вычислительных элементов последней строки матрицы 5. Выходы блока 36 распрог- странения переносов соединены с выходной шиной устройства 29.

Блок 36 распространения переносов содержит сдвиговой регистр знаков произведений 37 (фиг,6), информационный вход которого является входом Знак произведения блока распростра- нения переносов, а также матрицу 38 элементов 39 распространения переноса, содержащую п строк, первая строка имеет п элементов 39 распространения переноса, а каждая последующая строка матрицы 38 имеет на один элемент 39 меньше. Первый вход старшего элемента 39 распространения переноса первой строки матрицы 39 является корректирующим входом блока распространения переносов. Первые входы остальных элементов 39 первой строки матрицы 38 являются первыми информационными входами блока распространения переносов. Вторые вхо

ды.элементов 39 первой строки матрицы 38 являются вторыми информационными входами блока распространения переносов. Выходы поразрядной суммы и переноса каждого элемента 39 связаны соответственно с первым входом элемента 39 того же веса следующей строки матрицы 38 и вторын входом элемента 39 следующей строки матрицы 38, имеющего вес на единицу больше. Выходы поразрядных сум младших элементов 39 всех строк матрицы 38 за исключением двух последних строк матрицы 38 поочередно связаны с информационными входа- Ми сдвиговых регистров 40 значений произведений из группы АI сдвиговых регистров значений произведений, содержащей (п-2) сдвиговых регистров 40, первьш сдвиговый регистр 40 в группе 41 имеет (п-1) разрядов, а каждый последующий регистр 40 в группе 41 имеет разрядность на единицу меньшую, чем предыдущий ре гистр), начиная с младшего элемента 39 первой строки матрицы 38 и первого регистра 40 в группе 41. . Выход поразрядной суммы младшего элемента 39 предпоследней строки матрицы 38 соединен с информационным входом триггера 42, выход которого, также как и выходы сдвиговы регистров 40, выход сдвигового ре- гистра 37 и выход поразрядной суммы элемента 39 распространения переноса последней строки матрицы 38, являются выходами блока распространения переносов.

Каждый элемент 39 содержит первы 43 и второй 44 триггеры, информационные входы которых являются одноименными входами элемента распространения переноса, а выходы этих тригеров соединены с входами полусумматора 45, выходы поразрядной суммы и переноса которого являются одноименными выходами элемента распространения переноса.

Кроме того, устройство по первому и второму вариантам содержит шину тактовых импульсов 46, связанную с управляющими входами все регистров и три ггеров устройства.

Устройство по пербому варианту работает следующим образом.

В первом такте на входы регист- эа 2 первого операнда и на входы ре80389 .8

гистра 4 второго операнда принимается первая пара элементов обрабатываемых векторов, представленная дополнительным двоичным кодом (А а,,. . .а„, В Ь, Ь, Ь, . , . Ь ) .

to

15

20

25

30

40

45

5 - HffCi a., . . D- U, и, Uj

Bo втором такте содержи мое указанных регистров передается на триггеры 13 и 14 первой строки матрицы 5 вычислительных элементов и на первый дополнительный регистр 10 из группы 11 дополнительных регистров, причем благодаря имеьэщимся связям между регистрами 2 и 4 с одной стороны и матрицей 5 вычислительных эле- ментСГв и первым регистром 10 из группы II, с другой стороны, в триггеры 13 первой строки матрицы 5 вычислительных элементов передается код . ai A/2j+2 + aLn/2j+3 а,Вп, в триггеры 14 -код а i.n/2jMb.n/2jt; aiiV2j+2 btn/2j 2 ..., a в первый дополнительный регистр 10 из группы

11 - код .. .aL,,2J BLn/tJ Д новременно с этим на регистры 2 и 4 заносится новая пара элементов обрабатываемых векторов.

Формирование произведения пары элементов обрабатываемых векторов осуществляется в матрице вычислительных элементов 5 в результате передачи информации с вычислительных элементов i-й строки матрицы 5 на вычислительные элементы (1+)-й строки этой матрицы. При этом i-e частичное 35 произведение формируется в виде поразрядных конъюнкций содержимого триггеров 13 и 14 вычислительных элемен- тов i-й строки матрицы 5, а накопление суммы частичных произведений осуществляется в триггерах 15 поразрядных сумм и триггерах 16 переносов вычислительных элементов этой же строки. Наличие дополнительных регистров 10 обеспечивает возможность формирования произведения при noMouui матрицы вычислительных элементов 5 размером п хп.

Через триггер 15 старшего вычислительного элемента всех строк матрицы 5, кроме первой, а также через триггеры 15 и 16 старшего вычислительного элемента первой строки матрицы 5 и корректирующий вход накапливающего сумматора 27 осуществляется введение коррекции результата умножения, формируемой в соответствии с таблицей.

50

55

Примечание,

При А О и В О на выходах матрицы 5 вычислительных элементов результат без коррекции-| А|-.1 В1+|А| 1в1 , так как единица представляет собой переносы, выходящие за пределы матрицы 5,

Часть коррекции, вводимой через триггеры 15 старшего вычислительного элемента всех строк матрицы 5, кроме первой, а также через корректирующий вход накапливающего сумматора формируется при помощи управляющих элементов 6.

Наличие элемента 1СКЛЮЧА}ОЩЕЕ ИЛИ 9 и элемента НЕ 8 в схеме устройства обеспечивает возможность округления результата умножения в процессе его формирования.

На (п-1-2)-м такте с выходом вычислительных элементов последней строки матрицы 5 значащая часть округленно го результата умножения пары элементов обрабатьгааемых векторов, представленная поразрядными суммами и переносами, поступает на входы накапливающего сумматора 27, а знак этого произведения поступает на одноименный вход накапливающего сумматора 27 с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12. Вместе с этим на корректирующий вход накапливающего сумма- тора 27 с одноименного выхода пос.г леднего управляющего элемента 6 в группе 7 поступает старший разряд коррекции.

В каждом последующем такте на входы накапливающего сумматора 27 поступает результат перемножения повой пары элементов обрабатываемых вектор.)в. В накапливающем сумматоре

27 эти результаты последовательно суммируются, образуя скалярное произведение векторов.

Элементы новых векторов могут при- приниматься на входы устройства по истечении n+fog N тактов после пода-г чи последней пары элементов предыдущих векторов. В течение n+log N холостых тактов на входы устройства должны подаваться нулевые операнды, что необходимо для распространения переносов в накапливающем суммат р- ре 27.

В устройстве по -второму варианту формирование произведения двух со- , множителей в виде поразрядных сумм и переносов осуществляется также, как в устройстве по первому варианту. Применение блока 36 распространения переносов вместо накапливающего сумматора 27 позволяет существенно повысить быстродействие устройства при вычислении поэлементного произведения векторов, так как при зтом в работе устройства отсутствуют холостые такты и , следовательно, в каждом такте на входы устройства может приниматься новая пара элементов обрабатьшаемых векторов.

Формула изобретения

1 . Устройство для вычисл ёния произведения векторов, содержащее матрицу-nxn вычислительных элементов (где п - количество значащих разрядов операндов; п - нечетное), регистры - первого и второго операндов и накапливающий сумматор, причем первая входная шина устройства соединена с информационными входами рг- гистра первого операнда, вторая вход- ная шина устройства соединена с информационными входами регистра второго операнда, первые входы вычислительных элементов нечетных и четных столбцов

первой строки матрицы поразрядно соединены соответственно- с выходами регистра второго операнда и выходами регистра первого операнда начиная с младших разрядов регистров и с младших вычислительных элементов, вто- рые входы вычислительных элементов нечетных и четных столбцов первой строки матрицы поразрядно связаны начиная с младших вычислительных элементов с выходами соответственно

to

реноса и поразрядной сум(ы вычислительного элемента послед тощего за старшим в первой строке матрицы, соединены с выходом элемента НЕ, вход

5 которого соединен с выходом первого элемента ИСКЛЮЧАЮО ЕЕ ЮШ, соединенного своими входами с выходами знаковых разрядов регистров операндов, выход переноса каждого вычислительного элемента матрицы соединен с входом переноса последующего вычисли- тельного элемента в столбце матрицы, выход поразрядной суммы каждого (i,j)-ro (,..,,п; ,,,,,n) вы15 Числительного элемента матрицы соединен с входом поразрядной суммы (, j + l)-ro вычислительного эле- мента матрицы, первый выход каждого (i,j)-ro вычислительного элемента

20 матрицы, номер которого не равен

(fn/21-bk, l+2k) или (fn/Zl+k, 2-f2k), где k 0,1,2, .. . , п-Гп/21-1, соединен с первым входом (i+1, j)-ro

.единены с выходами поразрядных сумм (п-1) старших вычислительных элемен;тов последней строки матрицы, инфор- мационньш входы второй группы накаПвычислительного элемента матрицы, регистра первого операнда, начиная « „/- -ч

t- « первый вход каждого (i, i)-ro вычис,с младшего разряда регистра и регист- „„ ельного элемента матрицы, номер ра второго операнда начиная с раз- которого равен (Гп-ь21+1+и, l+2k) ряда, последующего за младшим, ин- (Гп/21 + l-bk, 2+2k), соединен с

формационные входы первой группы на-,. , /,о, j ч

. « I- t-jвторым выходом (i-l, ()mod п)-го

капливающего сумматора поразрядно со- ,,,

„.„ . вычислительного элемента матрицы,

второй выход каждого (i,j)-ro вычислительного элемента матрицы связан с вторым входом (i+I, j+2)-ro

вычислительного элемента матрицы, ливаняцего сумматора поразрядно соеди- . „/

i-i- 35 при этом второй вход каждого (i,i)- нены с выходами переносов вычислительго вычислительного элемента матрицы, ных элементов последней строки мат-/г i

.номер которого равен (I 1) или

.рицы, управляющий вход накапливающего rt р о о /. г /от V -. I, , где I - z,-, +,...,, со

сумматора подключен к шине установки- единен соответственно с выходом вто- ;в ноль устройства, выходы накапливаю-40 рого или первого младшего разряда 1щего сумматора соединены с выходной ()po регистра группы, второй шиной устройства, шина тактовых им- од каждого вычислительного элемен- пульсов устройства соединена с управ- матрицы, номер которого равен ляющими входами регистров, о т л и - (т, 1) или (т,2), где т Гп/21- -1, чающееся тем, что, с целью. 5 ,,, . . ,п соединен соот- уменьшения аппаратурных затрат при ветственно с вторым выходом (т-1, вычислении скалярного произведения п-1)-го или (ш-1, п)-го вычислитель- векторов устройство содержит элемент bix элементов матрицы, вход пораз- НЕ, первьй и второй элементы ИСКЛЮЧА- .рядной суммы вычислительного лемен- КЩЕЁ ИЛИ, группу управляющих элемент 50 та старшего столбца матрицы i-й стро- тов и группу регистров, причем входы ки матрицы соединен с корректирую- переноса и поразрядной суммы стар- щим выходом (i-l)-ro управляющего

элемента группы, первый и второй входы которого соединены соответст- знакового разряда одного из регист- 55 венно с вторыми выходами (i-2, п-1)- ров операндов, выход знакового раз- го и (i-2, п-2)-го вычислительных

элементов матрицы, третий и четвертый входы и вход переноса (i-l)-ro управляющего элемента группы соедишего вычислительного элемента первой строки матрицы соединены с вькодом

ряда другого регистра операндов соединен с (рходом переноса первого управляющего элемента группы, входы пе

реноса и поразрядной сум(ы вычислительного элемента послед тощего за старшим в первой строке матрицы, соединены с выходом элемента НЕ, вход

которого соединен с выходом первого элемента ИСКЛЮЧАЮО ЕЕ ЮШ, соединенного своими входами с выходами знаковых разрядов регистров операндов, выход переноса каждого вычислительного элемента матрицы соединен с входом переноса последующего вычисли- тельного элемента в столбце матрицы, выход поразрядной суммы каждого (i,j)-ro (,..,,п; ,,,,,n) выЧислительного элемента матрицы соединен с входом поразрядной суммы (, j + l)-ro вычислительного эле- мента матрицы, первый выход каждого (i,j)-ro вычислительного элемента

матрицы, номер которого не равен

(fn/21-bk, l+2k) или (fn/Zl+k, 2-f2k), где k 0,1,2, .. . , п-Гп/21-1, соединен с первым входом (i+1, j)-ro

fO

ts

20

25

йены соответственно с первым и вторым выходами и выходом переноса (i-2)-ro управляющего элемента группы, первый и четвертый входы первого управляющего элемента группы соединены соответственно с выходами младшего и знакового разрядов регистра второго операнда, второй и третий входы первого управляющего элемента группы соединены соответственно с выходами младшего и знако.вого разрядов регистра первого операнда, первый и второй выходы последнего управляющего элемента группы соединены с входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к входу Знак произведения i накапливающего сумматора, корректирующий выход последнего управляющего элемента группы соединен с корректирующим входом накапливающего .сумматора, выходы Ln/2j старших разрядов регистров первого и второго операндов соединены с информационными вхс5дами первого регистра группы, причем соединение вьшолнено таким образом, что старший разряд регистра первого операнда соединен со старшим разрядом первого регистра группы, а все выходы каждого из регистров группы за исключением выходов двух младших разрядов регистров поразрядно соединены с входами последующего дополнительного регистра группы.

2. Устройство по п. 1, о т л и - ч ающе е.ся тем, что управляющий элемент содержит одноразрядный сумматор, первый и второй элементы И, первый, второй, третий, четвер- Q тый триггеры и триггер переноса, причем информационные входы первого, второго, третьего, четвертого триггеров и триггера переноса являются соответственно первым, вторым, треть-45 им, четвертым входами и входом переноса управляющего элемента, инверсный выход первого триггера и прямой выход третьего триггера соединены с входами первого элемента И, инверс- Q ный выход триггера и прямой выход четвертого триггера соединены с входами второго элемента И, выходы первого и второго элементов И соединены

ра, к третьему входу которого подключен выход триггера переноса, вьтоды суммы и переноса одноразрядного сумматора являются соответственно кор30

ректирующим выходом и выходом, пар са управляющего элемента, первый второй выходы управляющего элемен соединены соответственно с прямым выходами третьего и четвертого тр геров.

3. Устройство для вычисления п изведения векторов, содержащее ма рицу п X п вычислительных элементо (где п - количество значащих разр дов операндов; п - нечетное), рег ры первого и второго операндов, п чем первая входная шина устройств соединена с информационными входа регистров первого операнда, втора входная шина устройства соединена информационными входами регистра второго операнда, первые входы вы числительных элементов нечетных и четных столбцов первой строки мат рицы поразрядно соединены соответ венно с выходами регистра второго операнда и выходами регистра перв операнда начиная с младших разряд регистров и младших вычислительны элементов матрицы, вторые входы в числительных элементов нечетных и четных столбцов первой строки мат цы поразрядно соединены начиная с младших вычислительных элементов матрицы с выходами соответственно регистра первого операнда начиная младшего разряда и регистра второ операнда начиная с разряда после ющего за младшим, шина тактовых и пульсов устройства соединена с уп ляющими входами регистров устройс ва, отличающееся тем, что, с целью уменьшения аппаратур затрат и увеличения быстродействи при вычислении поэлементного прои ведения векторов, оно содержит бл распространения переносов, элемен НЕ, первый и второй элементы ИСКШ ,ЧАЮЩЕЕ ИЛИ, группу управляющих эл ментов и группу регистров, причем входы переноса и поразрядной суммы старшего вычислительного элеме та первой строки матрицы соединен с выходом знакового разряда одног из регистров операндов, выход зна вого разряда другого регистра опе рандов соединен с входом переноса первого управляющего элемента гру

с входами одноразрядного суммато- fj входы переноса и поразрядной

суммы вычислительного элемента, п следующего за старшим в первой ст ке матрицы, соединены с выходом э мента НЕ, вход которого соединен

s

0

5

Q 5 Q

0

ректирующим выходом и выходом, парено са управляющего элемента, первый и второй выходы управляющего элемента соединены соответственно с прямыми выходами третьего и четвертого триггеров.

3. Устройство для вычисления произведения векторов, содержащее матрицу п X п вычислительных элементов (где п - количество значащих разрядов операндов; п - нечетное), регистры первого и второго операндов, причем первая входная шина устройства соединена с информационными входами регистров первого операнда, вторая входная шина устройства соединена с информационными входами регистра второго операнда, первые входы вычислительных элементов нечетных и четных столбцов первой строки матрицы поразрядно соединены соответственно с выходами регистра второго операнда и выходами регистра первого операнда начиная с младших разрядов регистров и младших вычислительных элементов матрицы, вторые входы вычислительных элементов нечетных и четных столбцов первой строки матрицы поразрядно соединены начиная с младших вычислительных элементов матрицы с выходами соответственно регистра первого операнда начиная с младшего разряда и регистра второго операнда начиная с разряда последующего за младшим, шина тактовых импульсов устройства соединена с управляющими входами регистров устройства, отличающееся тем, что, с целью уменьшения аппаратурных затрат и увеличения быстродействия при вычислении поэлементного произведения векторов, оно содержит блок распространения переносов, элемент НЕ, первый и второй элементы ИСКШО- ,ЧАЮЩЕЕ ИЛИ, группу управляющих элементов и группу регистров, причем входы переноса и поразрядной суммы старшего вычислительного элемента первой строки матрицы соединены с выходом знакового разряда одного из регистров операндов, выход знакового разряда другого регистра операндов соединен с входом переноса первого управляющего элемента групсуммы вычислительного элемента, последующего за старшим в первой стро-i ке матрицы, соединены с выходом элемента НЕ, вход которого соединен с

15

выходом первого элемента ИСКЛОЧАЮ- |ЦЕЕ ИЛИ, соединенного своими входа с выходами знаковых разрядов регисров опед андов, выход переноса каждго вычислительного элемента матрицы соединен с входом переноса последующего вычислительного элемента в столбце матрицы, выход поразрядной суммы каждого (i,j)-ro вычилительного элемента матрицы соедин с входом поразрядной суммы (i+1, j+l)-ro вычислительного элемента матрицы, первый выход каждого (i,j го вычислительного элемента матрицы, номер которого не равен (fn/21 +k, l+2k) или (Гп/21+k, 2+2k), где k О,1,2,,,.,n-fп/2 -1, соединен с первым входом (i+1, j)-ro вычислительного элемента матрицы, первый вход каждого (i,j)-ro вычислительного элемента матрицы, номер которого равен (Гп/2 j + l+k, l+2k) или (fn/2 l+l+k, 2+2k), соединен с вторым выходом (i-l, (j+2k) mod п)вычислительного элемента матрицы, второй выход каждого (i,j)-ro вычислительного элемента матрицы соединен с вторым входом (i+i, j+2)-ro вычислительного элемента матрицы, второй вход каждого (i,j)-ro вычислительного элемента матрицы, номер которого равен I, 1 или Е, 2 (где I 2,3,4,...,Гп/21), соединен соответственно с выходом второго или первого младшего разряда (E-l)-ro регистра группы, второй вход каждого вычислительного элемента матрицы номер которого равен (т,1) или (т,2 где т Гп/21+1,Гп/21+2,Гп/2 |+3,. .. ,п соединен соответственно с вторым выходом (т-1, п-1)то или (т-1,п)-г вычислительных элементов матрицы, вход поразрядной суммы вычислительных элементов старшего столбца матрицы каждой 1-й строки соединен с корректирующим выходом (i-l)-ro управляющего элемента группы, первый второй входы которого соединены соответственно с вторыми выходами (i-2, п-1)-го и (i-2, п-2)-го вычислительных элементов матрицы,, третий и четвертый входы и вход переноса (i-l)-ro управляющего элемента группы соединены соответственно с и вторым выходами и выходом переноса (i-2)-го управляющего элемента группы, первый и четвертый вхды первого управляющего элемента группы соединены соответственно с вых

0

5

0

дами младшего и знакового разрядов регистра второго операнда, второй и третий входы первого управляющего элемента группы соединены соответственно с выходами младшего и знакового разрядов регистра первого операнда, первьй и второй выходы последнего управляющего элемента группы соединены с входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к входу Знак произведения блока распространения переносов, кор-- ректирующий выход последнего управляющего элемента группы соединен с корректирующим входом блока распространения переносов, входы поразрядных сумм (п-1) старших вычислительных элементов последней строки матрицы поразрядно соединены с информационными входами первой группы блока распространения переносов, выходы переносов вычислительных элементов последней строки матрицы поразрядно соединены с информационными входами вто- 5 рой группы блока распространения переносов, выходы .блока распространения переносов связаны с выходной шиной устройства, выходы Ln/2J старших разрядов регистров первого и второго операндов соединены с информационными входами первого регистра группы, причем соединение вьшолнено таким- образом, что старший разряд регистра первого операнда соединен со старшим разрядом первого регистра, а все выходы каждого из регистров группы за исключением выходов двух младших разрядов регистра поразрядно соединены с входами последующего регистра группы.

4. Устройство по п. 3, о тли- чающееся тем, что управляющий элемент содержит одноразрядный сумматор, первый и второй элементы И, первый, второй, третий, четвертый триггеры и триггер переноса, причем информационные входы первого, зторого, третьего, четвертого триггеров и триггера переноса являются соответственно первым, вторым, третьим, четвертым входами и входом переноса управляющего элемента, инверсный выход первого триггера и прямой выход третьего триггера соединены с входами первого элемента И, инверсный выход второго триггера и прямой выход четвертого - триггера соединены с входами второ0

5

0

5

0

5

го элемента И, выходы первого и второго элементов И соединены с входами одноразрядного сумматора, к третьему входу которого подключен выход триггера переноса, выходы суммы и переноса одноразрядного сумматора являются соответственно корректирующим выходом и выходом переноса управляющего элемента, первый и второй выходы управляющего элемента соединены соответственно с прямыми выходами третьего и четвертого триггеров.

5. Устройство по н. 4, о т л и- чающееся тем, что блок распространения переносов содержит сдвиговый регистр, триггер., группу сдвиговых регистров и матрицу элементов распространения переноса, причем вход Знак произведения блока распространения переносов соединен с входом сдвигового регистра, выход которого и выход поразрядной суммы элемента распространения перерые входы элементов распространен ния переноса первой строки матрицы являются информационными входами второй группы блока распространения пе5 реносов, выходы поразрядной суммы и переноса каждого элемента распространения переноса матрицы соединены соответственно с первым входом элемента распространения переноса того

10 же веса следующей строки матрицы и вторым входом элемента распространения переноса следующей строки матрицы, имеющего вес на единицу больший, выходы поразрядных сумм младших эле15 ментов распространения переноса всех строк матриць: за исключением двух последних строк матрицы соединены с информационными входами сдвиговых регистров значений произведений начи20 ная с младшего элемента распространения переноса первой строки матрицы и первого сдвигового регистра-группы, выход поразрядной суммы младшего элемента распространения переноса предноса последней строки матрицы, выход последней строки матрицы соединен с триггера и выходы всех сдвиговых ре- информационным входом триггера, при- гистров группы являются выходами бло- чем каждый элемент распространения

блока распространения переносов, первый вход старшего элемента распространения переноса первой строки матрицы является корректирующим вхо- дом блока распространения переноса, первые входы остальных элементов распространения переноса первой строки матрицы являются инфор- мационными входами первой группы блока распространения переносов, вторые входы элементов распространен ния переноса первой строки матрицы являются информационными входами второй группы блока распространения переносов, выходы поразрядной суммы и переноса каждого элемента распространения переноса матрицы соединены соответственно с первым входом элемента распространения переноса того

же веса следующей строки матрицы и вторым входом элемента распространения переноса следующей строки матрицы, имеющего вес на единицу больший, выходы поразрядных сумм младших элементов распространения переноса всех строк матриць: за исключением двух последних строк матрицы соединены с информационными входами сдвиговых регистров значений произведений начиная с младшего элемента распространения переноса первой строки матрицы и первого сдвигового регистра-группы, выход поразрядной суммы младшего элемента распространения переноса пред

переноса содержит полусумматор первый и второй триггеры, причем информационные входы первого и второго триггеров являются одноименными входами элемента распространения переноса, выходы триггеров соединены с входами полусумматора, выходы пораз- рядной суммы и переноса которого

являются одноименными выходами эле- мента распространения переноса.

СядЗ Ш---45

Л

А У1 /я /д J Z JU

Y1T /TfT Arf /rif УЩ/

o,ai,a2,a...a

28 Уст.О

f/

tf

п.

o,bi,b2, b... bn

Фиг.1

Oo,ai,ci2,a3...an

Фиг.2

bo,b,,b2,bj,..bq.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Конвейерное множительное устройство | 1980 |

|

SU903866A1 |

| Вычислительное устройство | 1988 |

|

SU1647553A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных конвейерных вычислительных средств, выполненных.на узлах с большой степенью интеграции. Целью изобретения является уменьшение аппаратурных затрат при вычислении скалярного произведения векторов и уменьшение аппаратурных затрат и увеличение быстродействия при вычислении поэлементного произведения векторов. Для этого в устройство, содержащее матрицу вычислительных элементов, два регистра операндов, две группы элементов И-НЕ, накапливающий сумматор, по первому варианту дополнительно вводятся элемент НЕ, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, группа управляющих элементов и группа дополнительных регистров, а по второму варианту вводятся блок распространения переносов, элемент НЕ, два элемента;ИСКЛЮЧАЮЩЕЕ 1ШИ, группа управляющих элементов и группа дополнительных регистров. 2 с.п.ф-лы, 3 з.п. ф-лы, 7 ил, 1 табл. § (Л ГС 00 о со 00 со

, npoutSeicHtai

JHffIC

XM/tSei

Коррекция

Змеек про- Кор- из9ввений рещил

Значение лроиз1еден1 я Фиг.8

3

1

ив

Ре

ip.AKTOp Л.Лчвлинская

Фиг. 7

Составитель А.Долголенко

Техред М.Ходами Корректор М.Максимишинец

Заказ 7052/43Тираж 671Подписное

ВНИИПН Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная 4

| Устройство для вычисления сумм произведений | 1975 |

|

SU561963A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1984-02-03—Подача