Фиг. 7

Изобретение относится к технике цифровых систем передачи и может быть использовано для исправления ошибок в волоконно-оптических цифровых линейных трактах, использующих блочные балансные двоичные пВ-(п+1)В коды с минимальным кодовым расстоянием и соответствующие им двоичные сигналы.

Цель изобретения - повышение помехоустойчивости передачи информации.

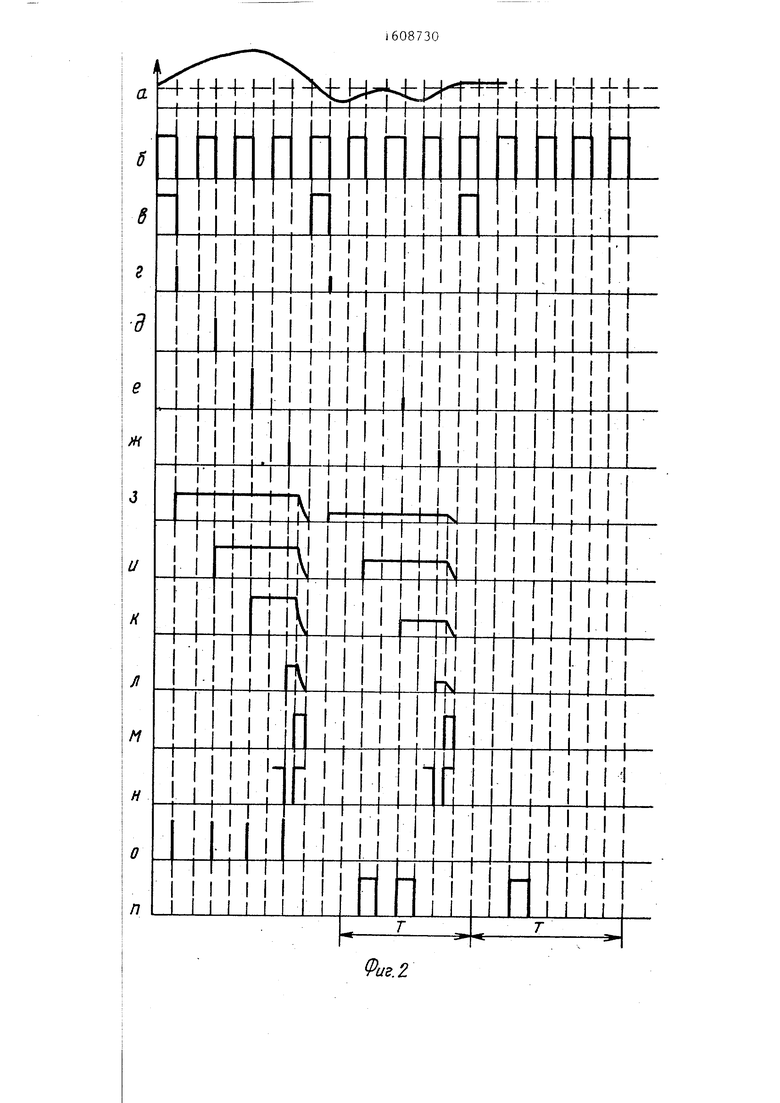

На фиг. представлена функциональная схема устройства; на фиг,2 - временные диаграммы работы устройства.

Устройство содержит мультиплексор 1, счетчик 2, синхронизатор 3, компаратор 4, пороговый элемент 5, блок пиковых детекторов 6,формирователь 7

16087304

плексора 1 формируется сигнал (фиг,2д), соответствующий отсчету второго разряда Х.принятого сигнала X и т,д,. (фиг.2е,ж)о Таким образом, на вход 17 устройства поступают два вектора сигналов X,(0,7; 0,9; 0,95; 0,65) и (0,20; 0,41; 0,15; 0,35), соответствующие первому и второму передан- JQ ных кодовым словам.

Принцип работы синхронизатора 3

. заключается в том, что он формирует сигналы блочной синхронизации (фиг,2в), соответствующие началу ко- J5 дового слова, С выхода мультиплексо- ; ра 1 принятый сигнал в параллельном коде поступает на соответствующие входы блока пиковых детекторов 6, который состоит из четырех одинаковых

стробирующих импульсов, первый и вто- 20 пиковых детекторов, управляемых сиг25

30

рой элементы 8 и 9 задержки, блок 10 сравнения, блок 11 вычитания, дешифратор 12, коммутатор 13, блок 14 постоянной памяти, преобразователь 15 параллельного кода в последовательный, сдвиговый регистр 16, информационный 17 и тактовый 18 входы, выход

19Устройство работает следующим образом.

Пусть для передачи информации в . волоконно-оптической цифровой системе передачи информации используется код ЗВ-4В, который трем двоичным символам ставит в соответствие блок из четырех двоичных символов (см,табл.1) причем минимальное кодовое расстояние . На информационный вход уст-, ройства поступают сигналы, искаженные помехой. Пусть на передающем конце переданы два кодовых слова Ап(0110) и А(0100), а сигнал на входе 17 устройства имеет вид, показанной на ,фиг,2а. Входной сигнал (фиг,2а) поступает на информационный вход муль- 45 типлексора 1 , который управляется . счетчиком 2, который осуществляет счет по импульсам тактовой частоты (фиг,2б), и синхронизируется импульса35

40

ми блочной частоты (фиг,2в), выраба- Q задержки

налом с выхода формирователя 7 стробирующих импульсов (фиг,2м). Принцип работы блока пиковых детекторов 6 заключается в том, что каждый из четырех пиковых детекторов выбирает максимальное значение сигнала на соответствующем своём входе и запоминает его до конца кодового слова. Затем осуществляется сброс пиковых детекторов по сигналу с первого выхода (фиг,2м) формирователя 7 стробирующих импульсов, Принцип работы формирователя 7 стробирующих импульсов состоит в том, что он генерирует импульсы с длительностью, равной 0,25 периода тактовой частоты только в те моменты, когда на его направляющих входах присутствуют сигналы логической 1, а на тактовом входе - отрицательный перепад напряжения, что Соответствует середине четвертого тактового интервала, т.е. середине четвертого разряда принятого кодового слова, при этом сигнал с первого выхода проходит через элемент задержки на 0,25 такта, находящийся внутри формирователя 7 стробирующих импульсов (фиг,2м), а сигнал с второго выхода (фиг,2п).поступает без

тываемой синхронизатором 3, Принцип работы мультиплексора 1 заключается в следующем: по управляющим сигналам, , вырабатьшаемым счетчиком 2 и .синхронизатором 3, на первом выходе мультиплексора 1 формируется сигнал (фиГо2г), соответствующий отсчету первого разряда Х принятого кодового сигнала X, на втором выходе мультиТаким образом, сброс пиковых детекторов 6 происходит после того, как на нем запомнится максимальное значение принятого кодового слова. Входной сигнал X (фиг,2а) поступает также на первый информационный вход компаратора 4, на второй информационный вход которого поступает сигнал с выхода порогового элемента 5, а на

заключается в том, что он формирует сигналы блочной синхронизации (фиг,2в), соответствующие началу ко- дового слова, С выхода мультиплексо- ; ра 1 принятый сигнал в параллельном коде поступает на соответствующие входы блока пиковых детекторов 6, который состоит из четырех одинаковых

пиковых детекторов, управляемых сиг0 пиковых детекторов, управляемых сиг5

0

5

5

0

налом с выхода формирователя 7 стробирующих импульсов (фиг,2м). Принцип работы блока пиковых детекторов 6 заключается в том, что каждый из четырех пиковых детекторов выбирает максимальное значение сигнала на соответствующем своём входе и запоминает его до конца кодового слова. Затем осуществляется сброс пиковых детекторов по сигналу с первого выхода (фиг,2м) формирователя 7 стробирующих импульсов, Принцип работы формирователя 7 стробирующих импульсов состоит в том, что он генерирует импульсы с длительностью, равной 0,25 периода тактовой частоты только в те моменты, когда на его направляющих входах присутствуют сигналы логической 1, а на тактовом входе - отрицательный перепад напряжения, что Соответствует середине четвертого тактового интервала, т.е. середине четвертого разряда принятого кодового слова, при этом сигнал с первого выхода проходит через элемент задержки на 0,25 такта, находящийся внутри формирователя 7 стробирующих импульсов (фиг,2м), а сигнал с второго выхода (фиг,2п).поступает без

задержки

Таким образом, сброс пиковых детекторов 6 происходит после того, как на нем запомнится максимальное значение принятого кодового слова. Входной сигнал X (фиг,2а) поступает также на первый информационный вход компаратора 4, на второй информационный вход которого поступает сигнал с выхода порогового элемента 5, а на

5 1

упрашяющий вход компаратора 4 по- ступгет сигнал тактовой частоты (ком

открывается О).

уровнем логиIII инцип работы компаратора 4 за- ется в следующем. В моменты вре задаваемые отрицательным перетактовой частоты и соответству середине тактового интервала, ойуществляет сравнение принятого ла со значением на выходе по- элемента Гфиг.2а),, и если сигна|л превьппает порог, то на выхо- компаратора 4 формируется сигнал

1, в противном случае - сигнал логического О. Фактически,

ключ

мени

падок

ющие

он

сигнг

рогового

си

де

логической

в компараторе жесткого

(фиг.

не

выход|е

ватьс1я

ния,

слова

0000

4 формируются оценки решения. Величина порога 2а) выбирается равной полови- аги(плитуды принятого сигнала. компаратора 4 будет формиро- оценок жесткого реше- который для первого кодового

С 1111, а для второго G.

сое гавляет

(фиг.2о).

жесткого решения с выхода 4 поступают на информа- вход регистра 16 сдвига, на сдвига которого поступает сиг- Т|актовой частоты с задержкой

15 НС с выхода первого элем задержки. Величина задержки такой исходя из того, что задержки включения компаратора

12 НС. На выходе регис формируются четыре оценки жест зешения в параллельном коде. С 1 пиковых детекторов 6 (фиг.2з л) отсчетные значения сигналов гея на соответствующие информационней входы блока 10 сравнений и блока 11 вычитания, на входы разрешения которых подается сигнал разрешения OV формирователя 7 стробирующих импульсов (фиг.2н). На управляющий: вход (шока 11 вычитания подается сигнал с выхода порогового элемента 5 (фиГоЗа).

Оценки компаратора цион4э1Й вход нал

поряд)ка та 8 выбрала время 4

ра 16 кого выход и, к, подаю

аклю ; т

Э Хз Хз

х х

Принцип работы блока 10 сравнений ается в том, что он осуществля- сле|дующие сравнения:

(I) (2) (3) (4)

X

2

X

X

ч

1

(5)

а в случае невыпол 0. В бло

08730 , 6

В рассматриваемом для первого кодового слова ,,9; ,,65; ,95 ,7; ,,65;Х2 0,,0,7, т.е. все неравенства выполняются.

Для второго кодового слова Xj 0,,41; ,,35; ,,0,2; X 0,41 ,35; Q Х,,0,,0,2.

Откуда видно, что первые три неравенства не вьшолняются.

В случае выполнения неравенств (О (5) на соответствующих выходах j блока 10 сравнений формируется-сигнал логической 1

нения - сигнал логического ке 11 вычитания производятся следующие операции:

20 Х,-Х,,5; (6) ,5; (7) X,-X -Xj+X О (8) В рассматриваемом случае для первого кодового слова

25 ,,7-0,95+0,,4 0,5; Х,-Х,,7-0,9+0,,,5 ; Х,-Х,-Х,,7-0,9-0,95+0,65 -0,5 0.

Для второго кодового слова 30 Х -Хз+Х 0,2-0,15+0,,,5; ., 2-0,41+0,,14 0,5; X,-Xi-X,,2-0,41-0,15+0,35 -0,01 ; Оо.

В случае выполнения неравенств (6) - (8) на соответствующих выходах блока I1 вычитания также формируется

35

-сигнал логической 1, а

в случае нё- 0.

выполнения - сигнал логического

Все сигналы, поступающие на входы

Q дещифратора 12, являются адресом данного дешифратора и в соответствии с пришедшей двоичной комбинацией активи- руется соответствующий выход дешифратора 12 (,,),- при этом вьпсоды

45 дешифратора 12 подключены к информа-. ционным входам коммутатора 13. Приведенные входные сигналы дешифрато- ра 12 поступают также и на первый, ,.- второй и пятый адресные входы комму50 татора 13 и на первые три информационных входа блока 14 постоянной памя.- ти. Первый и второй выходы блока-11 вычитания (формулы (6) и (7)) подключены к десятому и одиннадцатому ад5 ресным входам коммутатора 13. Третий выход блока вычитания (формула (8)) подключен к двенадцатому адрес ному входу блока 13, а также к чет- вертому адресному входу блока 14 nor ;

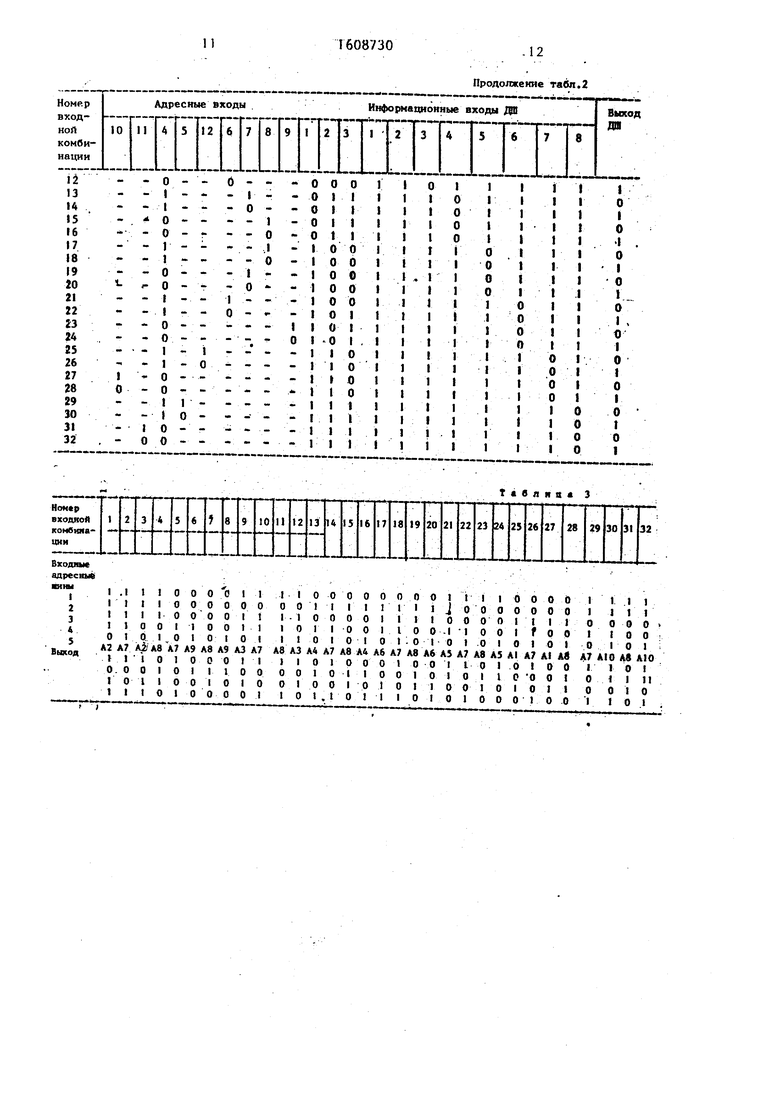

стоянкой памяти. Третий и четвертый выходы регистра 1-6 сдвига соединены третьим и четвертым адресными входам коммутатора 13, шестой, седьмой, - восьмой и девятый адресные входы которого подключены к второму, третьему, четвертому и пятому выходам блока 10 сравнений соответственно (формулы (2) - (5)). Принцип работы коммутатора 13 заключается в том, что он пропускает на выход только один соответствующий результат сравнения в каждом конкретном случае, задаваемом адресными сигналами (табл.2).

Для первого из переданных кодовых слов на вход коммутатора 13 поступает комбинация № 32 (табл.2). Ей соответствует уровень логической 1 на выходе. Для второго кодового ело- ва поступает комбинация № 4 (табл.2) Ей также соответствует 1 на выходе Выход коммутатора 13 подключен к пятому информационному входу блока 14 постоянной памяти, на первые четыре информационных входа которого подаются сигналы четырех следующих результатов сравнения: на первый вход Х,0,5; на второй вход ,5; на третий вход на четвертый вход X -X -Xj+X 0, которые вместе с сигналом с выхода коммутатора 13- составляют адрес для блока 14 постоянной памяти, в который заранее записаны необходимые кодовые слова по соответствующему адресу. В рассматриваемом случае для первого из переданных кодовьк слов на вход блока 14 постоянной памяти поступает комбинация № 4 (табл.3), а для второго кодового слова - комбинация № 8 (табл.3). Им соответствуют выходные слова А., 0110 и соответственно (фиг.2п). ,

Таким образом, происходит восстановление (регенерация) принятого кодового слова. Сигнал управления поступает на блок постоянной памяти от синхронизатора 3 фактически уже в на- чале следующего кодового слова.. Полученный на выходе блока 14 постоянной памяти четырехразрядньй параллельный код поступает на преобразователь 15, на управляющий вход которого поступает сигнал от синхронизатора 3 через второй элемент 9 задержки, а на так- I товый вход поступает тактовая частота, с помощью которой осуществляется

сдвиг информации и передача ее на выход 19 устройства.

Таким образом, полное восстановление п-го кодового слова происходит в (п+1) такте и в последовательном коде передается на выход 19 устройства. Таким образом, в устройстве за счет исправления ошибок в блочных двоичных пВ-(п+1)В кодах с минимальным кодовым расстоянием повьшга- ется помехоустойчивость волоконно- оптических цифровых систем передачи информации.

15

-,/, Q

рмула изобретени

5

/, Q

5

0

5

ь

Устройство для исправления ошибок в волоконно-оптических цифровых сие- i темах передачи информации, содержа- щее компаратор,сдвиговьй регистр, дешифратор и преобразователь параллельного кода в последовательньй, выход которого является выходом устройства, синхронизатор, тактовый вход которого и тактовый вход преобразователя параллельного кода в последовательный объединены и являются тактовым входом устройства, о т л и ч а ю - щ е ее. я тем, что, с целью повышения помехоустойчивости передачи информации, в него введены мультиплексор, счетчик, формирователь строби- рующих импульсов, блок пиковых детекторов, пороговый элемент, первый и второй элементы задержки, блок сравнения, блок вычитания, коммутатор, блок постоянной памяти, информационный вход мультиплексора, первый информационный вход компаратора и вход порогового элемента объединены и являются информационным входом устройства, тактовые входы счетчика и формирователя стробирующих импульсов объединены и являются тактовьм входом - устройства, выходы счетчика подключены к управляющим входам формирователя стробирующих импульсов и к адресным входам мультиплексора, выходы последнего подключены к информационным входам блока пиковых детекторов, выходы которого подключены к информационным входам блока сравнения и блока вычитания, первый и второй выходы формирователя стробирующих импульсов под, ключены к входам разрешения блока пи- коЕых детекторов, к блокам сравнения и вычитания соответственно, третий

, выход формирователя стробирующих импульсов подключен к управляющему входу компаратора и через первый элемен за,ержки к входу Сдвиг сдвигового регистра, выход порогового элемента подключен к управляющему входу блока вычитания и к второму информаци- онюму входу компаратора, выход кото ро О подключен к информационному входу сдвигового регистра, первый и второй выходы которого подключены к первому и второму входам дешифра- то:)а, к первому и второму адресным входам коммутатора и блока постоянной памяти, третий и четвертьй вько- ды|сдвигового регистра подключены к третьему и четвертому адресным входам коммутатора, первый выход блока сравнения подключен к третьему вхо ДУ Bxd

дешифратора, к пятому адресному 1ДУ коммутатора и к третьему адрес ному входу блока постоянной памяти.

втс xo

Фой, третий, четвертый и пятый вы- ,ы блока сравнения подключены к

o

шестому, седьмому, восьмому и девятому адресным входам коммутатора соответственно, первый и второй выходы блока вычитания подключены к десятому и одиннадцатому адресным входам коммутатора соответственно,, третий выход блока вычитания подключен к двенадцатому адресному входу коммутатора и к четвертому адресному входу блока постоянной памяти, выходы дешифратора подключены к информационным входам коммутатора, выход которого подключен к пятому адресному входу блока постоянной памяти, выходы которого подключены к информационным входам преобразователя параллельного кода в последовательный, выход синхронизатора подключен к управляющим входам счетчика,

блока постоянной памяти и через второй элемент задержки к управляющему входу преобразователя параллельного

кода в последовательный.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| Устройство для обработки изображений | 1989 |

|

SU1772806A1 |

| МНОГОКАНАЛЬНЫЙ ПАНОРАМНЫЙ ПРИЕМНИК | 1996 |

|

RU2115997C1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

Изобретение относится к технике цифровых систем передачи и может быть использовано в устройствах для исправления ошибок в волоконно-оптических цифровых линейных трактах, использующих блочные балансные двоичные NB - (N+1) B коды с минимальным кодовым расстоянием D = 1 и соответствующие им двоичные сигналы. Цель изобретения - повышение помехоустойчивости передачи информации. Поставленная цель достигается введением в устройство, содержащее компаратор 4, сдвиговый регистр 16, дешифратор 12, преобразователь 15 параллельного кода в последовательный и синхронизатор 3, мультиплексора 1, счетчика 2,формирователя 7 стробирующих импульсов, блока 6 пиковых детекторов, порогового элемента 5, двух элементов 8 и 9 задержки, блока 10 сравнения, блока 11 вычитания, коммутатора 13 и блока 14 постоянной памяти с соответствующими связями. 2 ил., 3 табл.

Т а о л и ц а 1

Таблица 2

О i

О I О

1 о I

о

/7

-I -iif

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1990-11-23—Публикация

1989-02-22—Подача