ffjfe«7

Sbixoff

Изобретение относится к цифровым системам.передачи информации и может быть использовано дпя исправления ошибок в цифровых, линейных трактах, использующих коды с минимальным кодовым расстоянием, не превышающим двух

Цель изобретения - повышение помехоустойчивости за счет учета избыточности сигнала.

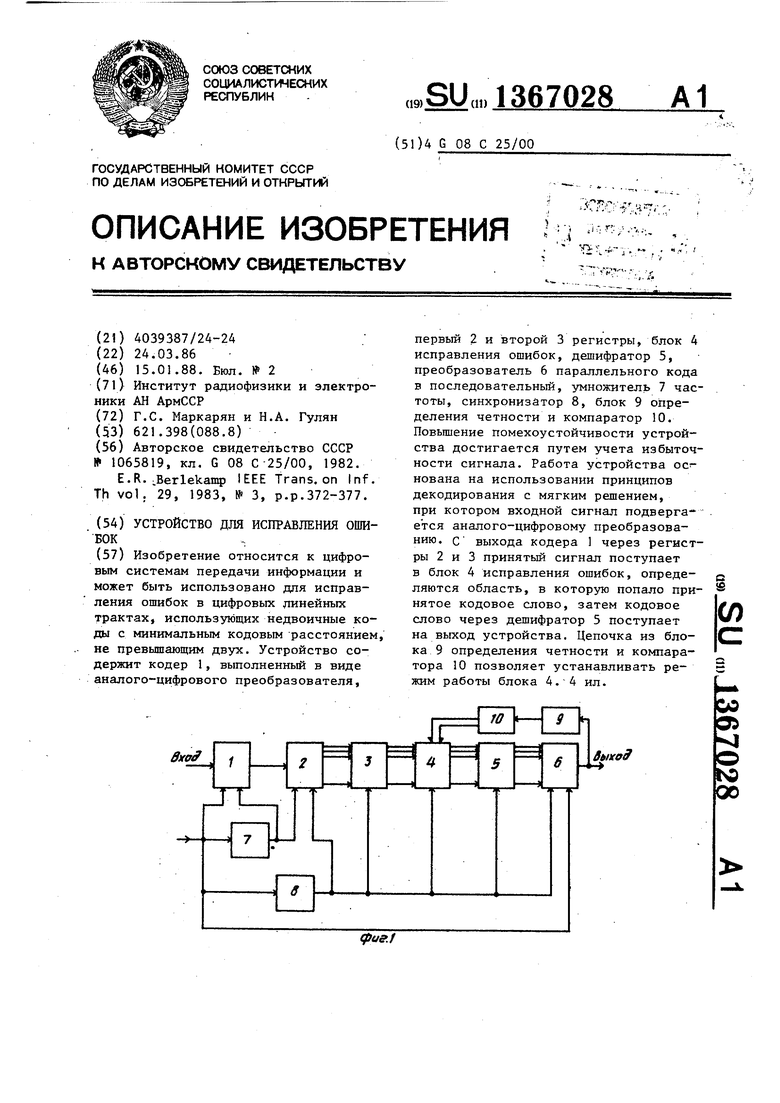

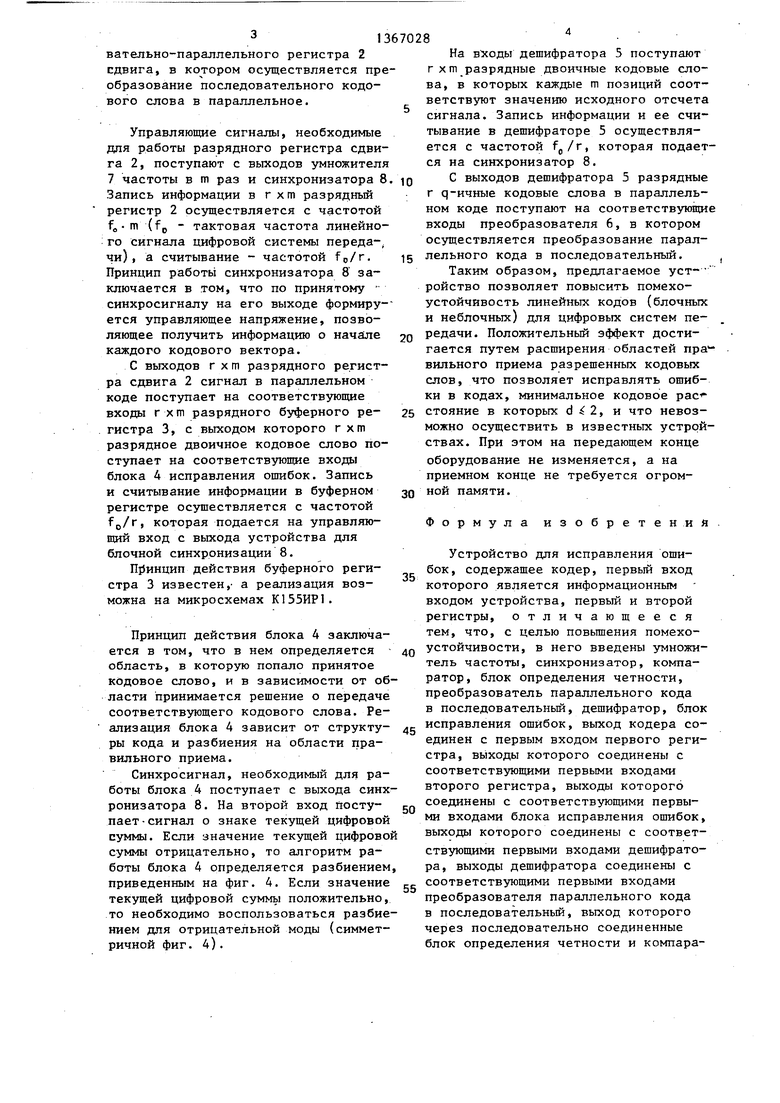

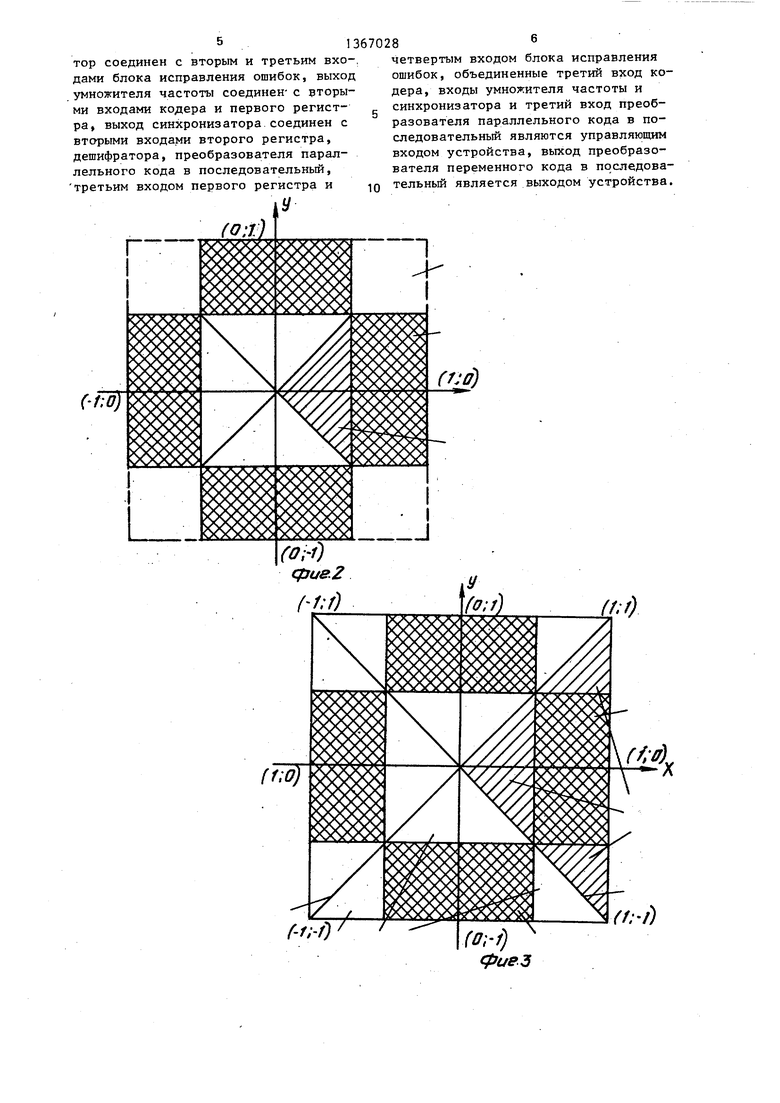

На фиг. 1 приведена функциональная схема устройства; на фиг. 2-4 диаграммы, поясняющие принцип исправления ошибок с использованием декоди рования мягким решением.

Устройство (фи г, I) содержит кодер 1, выполненный в виде аналого- цифрового преобразователя, первый 2 и второй 3 регистры, блок 4 исправления ошибок, дешифратор 5, преобразователь 6 паралл ельного кода в по- следовательньш, умножитель 7 частоты синхронизатор 8, блок 9 определения четности, компаратор 10.

Введение указанных элементов позволяет при декодировании сигнала использовать всю информацию о принятых символах, что эквивалентно повы- шению избыточности сигнала без снижения эффективности цифровой системы передачи, а полученная таким образом избыточность используется для улучшения корректирующей способности кода и позволяет исправлять ошибки в блочных кода, минимальное кодовое расстояние в которых .

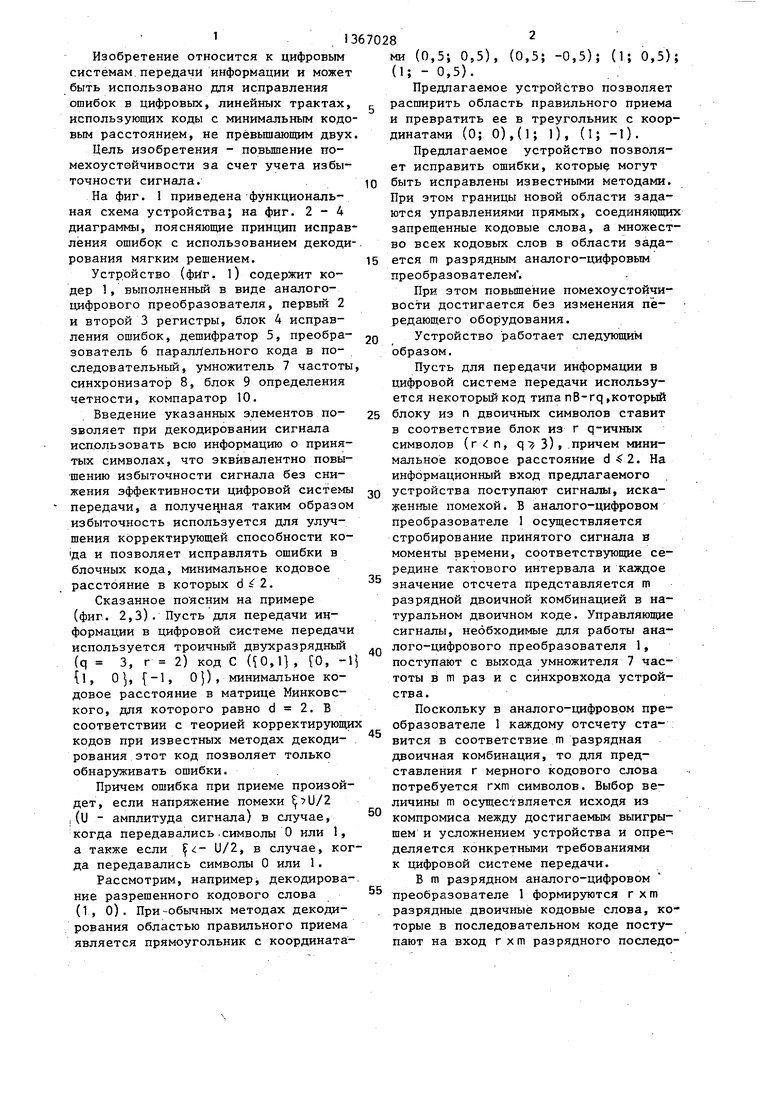

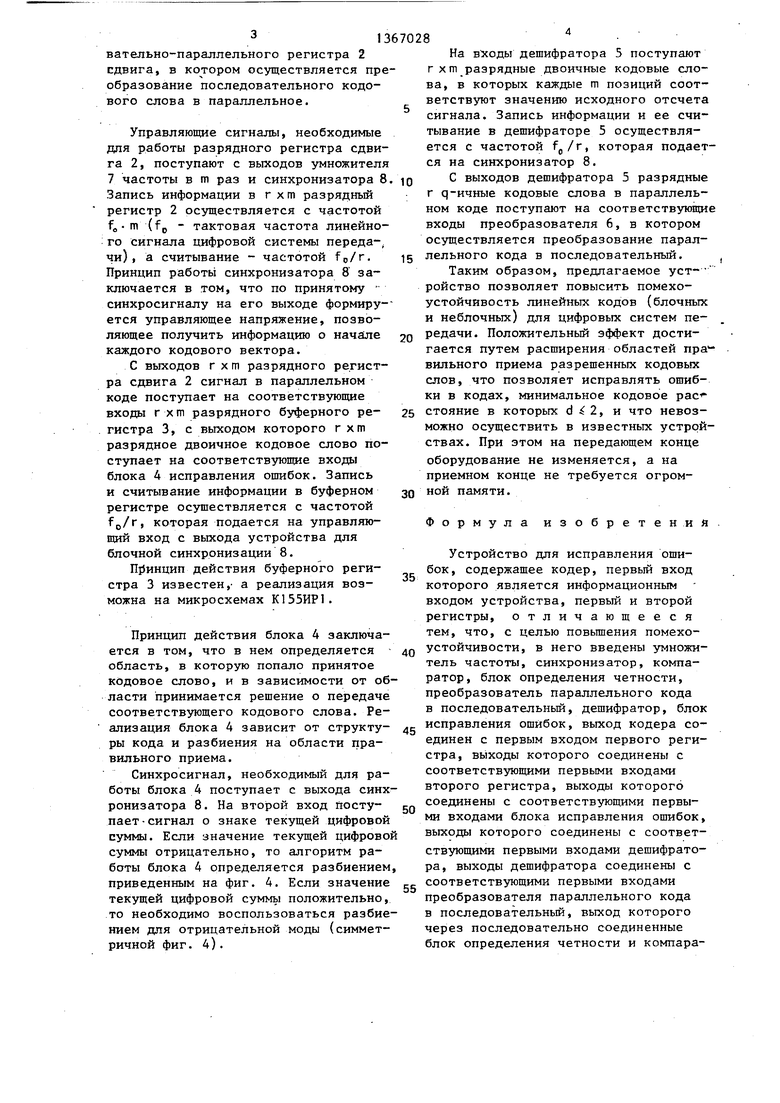

Сказанное по ясним на примере (фиг. 2,3). Пусть для передачи информации в цифровой системе передачи используется троичный двухразрядный (q 3, г 2) код С (0,1, О, - {, 0, {-1, О ), минимальное кодовое расстояние в матрице Минковс- кого, для которого равно d 2. В соответствий с теорией корректирующи кодов при известных методах декодирования этот код позволяет только обнаруживать ошибки.

Причем ошибка при приеме произойдет, если напряжение помехи U/2 , (и - амплитуда сигнала) в случае, когда передавались.символы О или 1, а также если i- U/2, в случае, когда передавались символы О или 1.

Рассмотрим, например, декодирование разрешенного кодового слова (1, 0). При-обычных методах декодирования областью правильного приема является прямоугольник с координата

5

0

5

0

5

0

5

0

5

ми (0,5; 0,5), (0,5; -0,5); (1; 0,5); (1; - 0,5).

Предлагаемое устройство позволяет расширить область правильного приема и превратить ее в треугольник с координатами (0; 0),(1; 1), (1; -1).

Предлагаемое устройство позволяет исправить ошибки, которые могут быть исправлены известными методами. При этом границы новой области задаются управлениями прямых, соединяющих запрещенные кодовые слова, а множество всех кодовьге слов в области задается m разрядным аналого-цифровым преобразователем.

При этом повьшение помехоустойчивости достигается без изменения передающего оборудования.

Устройство работает следующим образом.

Пусть для передачи информации в цифровой система передачи используется некоторый код типа nB-rq ,который блоку из п двоичных символов ставит в соответствие блок из г q-ичных символов ( г ; п, q 3) .причем минимальное кодовое расстояние d 2. На информационный вход предлагаемого устройства поступают сигналы, искаженные помехой. В аналого-цифровом преобразователе 1 осуществляется стробирование принятого сигнала в моменты времени, соответствующие середине тактового интервала и каждое значение отсчета представляется m разрядной двоичной комбинацией в натуральном двоичном коде. Управляющие сигналы, необходимые для работы аналого-цифрового преобразователя 1, поступают с выхода умножителя 7 частоты в m раз и с синхровхода устройства.

Поскольку в аналого-цифровом преобразователе 1 каждому отсчету ставится в соответствие m разрядная двоичная комбинация, то для представления г мерного кодового слова потребуется rxm символов. Выбор ве личины m осуществляется исходя из компромиса между достигаемым выигрышем и усложнением устройства и опре- деляется конкретными требованиями к цифровой системе передачи.

В m разрядном аналого-цифровом преобразователе 1 формируются rxm разрядные двоичные кодовые слова, которые в последовательном коде поступают на вход rxm разрядного последевательно-параллельного регистра 2 сдвига, в котором осуществляется преобразование последовательного кодового слова в параллельное.

Управляющие сигналы, необходимые для работы разрядного регистра сдвига 2, поступают с выходов умножителя 7 частоты в m раз и синхронизатора 8. ю Запись информации в г х m разрядный регистр 2 осуществляется с частотой fe-m (fp - тактовая частота линейного сигнала цифровой системы переда- чи), а считывание - частотой fo/r. 15 Принцип работы синхронизатора 8 заключается в том, что по принятому синхросигналу на его выходе формиру- ется управляющее напряжение, позволяющее получить информацию о начале 20 каждого кодового вектора.

С выходов г X m разрядного регистра сдвига 2 сигнал в параллельном коде поступает на соответствующие входы г X m разрядного буферного ре- 25 гистра 3, с выходом которого г хт разрядное двоичное кодовое слово поступает на соответствующие входы блока 4 исправления ошибок. Запись и считывание информации в буферном зо регистре осуществляется с частотой fp/r, которая подается на управляющий вход с выхода устройства для блочной синхронизации 8.

Принцип действия буферного регистра 3 известен,- а реализация возможна на микросхемах К155ИР1.

Принцип действия блока 4 заключается в том, что в нем определяется - 40 область, в которую попало принятое кодовое слово, и в зависимости от области принимается решение о передаче соответствующего кодового слова. Ре- ализация блока 4 зависит от структу- 45 ры кода и разбиения на области правильного приема.

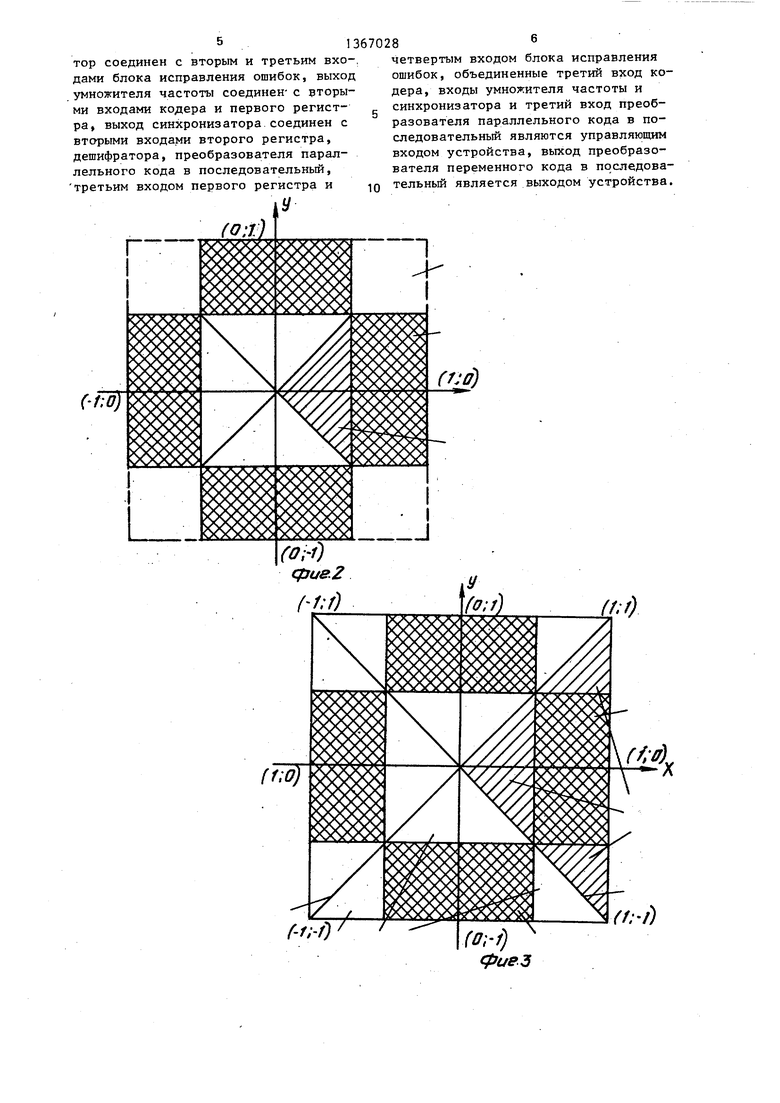

Синхросигнал, необходимый для работы блока 4 поступает с выхода синхронизатора 8. На второй вход йосту- gg паетсигнал о знаке текущей цифровой суммы. Если значение текущей цифровой суммы отрицательно, то алгоритм работы блока 4 определяется разбиением, приведенным на фиг. 4. Если значение gg текущей цифровой суммь положительно, то необходимо воспользоваться разбиением дпя отрицательной моды {симметричной фиг. 4).

35

5 0

5 о

0 5

g g

5

На дешифратора 5 поступают гхт разрядные двоичные кодовые слова, в которых каждые m позиций соот- ветств тот значению исходного отсчета сигнала. Запись информации и ее считывание в дешифраторе 5 осуществляется с частотой fp/r, которая подается на синхронизатор 8.

С выходов дешифратора 5 разрядные г q-ичные кодовые слова в параллельном коде поступают на соответствующие входы преобразователя 6, в котором осуществляется преобразование параллельного кода в последовательный. ,

Таким образом, предлагаемое уст- ройство позволяет повысить помехоустойчивость линейных кодов (блочных и неблочных) для цифровых систем передачи. Положительный эффект достигается путем расширения областей пра вильного приема разрешенных кодовых слов, что позволяет исправлять ошибки в кодах, минимальное кодовое рас- стояние в которых d 2, и что невозможно осуществить в известных устройствах. При этом на передающем конце оборудование не изменяется, а на приемном конце не требуется огромной памяти.

Формула изобретения.

Устройство для исправления ошибок, содержащее кодер, первый вход которого является информационным входом устройства, первый и второй регистры, отличающееся тем, что, с целью повьш1ения помехоустойчивости, в него введены умножитель частоты, синхронизатор, компаратор, блок определения четности, преобразователь параллельного кода в последовательный, дешифратор, блок исправления ошибок, выход кодера соединен с первым входом первого регистра, выходы которого соединены с соответствующими первыми входами второго регистра, выходы которого соединены с соответствующими первыми входами блока исправления ошибок, выходы которого соединены с соответствующими первыми входами дешифратора, выходы дешифратора соединены с соответствующими первыми входами преобразователя параллельного кода в последовательный, выход которого через последовательно соединенные блок определения четности и компаратор соединен с вторым и третьим вхо-, дами блока исправления ошибок, выход умножителя частоты соединен- с вторыми входами кодера и первого регистра, выход синхронизатора соединен с вторыми входами второго регистра, дешифратора, преобразователя параллельного кода в последовательный, третьим входом первого регистра и

Г

(Щ

r-f;-f)

четвертым входом блока исправления ошибок, объединенные третий вход кодера, входы умножителя частоты и синхронизатора и третий вход преобразователя параллельного кода в по- следовательньй являются управляющим входом устройства, выход преобразователя переменного кода в последовательный является выходом устройства,

(f:J)

(0:l;i

ff:l:l)

()

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

| Кодек блочных кодов | 1987 |

|

SU1473088A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ СВЯЗИ | 2003 |

|

RU2249918C1 |

| Система передачи и приема цифровых сигналов | 1985 |

|

SU1314463A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| Устройство для передачи информации с контролем ошибок высокой кратности | 1987 |

|

SU1480129A1 |

Изобретение относится к цифровым системам передачи информации и может быть использовано для исправления ошибок в цифровых линейных трактах, использующих недвоичные коды с минимальным кодовым расстоянием, не превышающим двух. Устройство содержит кодер 1, выполненный в виде аналого-цифрового преобразователя. первый 2 и второй 3 регистры, блок 4 исправления ошибок, дешифратор 5, преобразователь 6 параллельного кода в последовательный, умножитель 7 частоты, синхронизатор 8, блок 9 определения четности и компаратор 10. Ловьш1ение помехоустойчивости устройства достигается путем учета избыточности сигнала. Работа устройства основана на использовании принципов декодирования с мягким решением, при котором входной сигнал подвергается аналого-цифровому преобразованию. С выхода кодера 1 через регистры 2 и 3 принятый сигнал поступает в блок 4 исправления ошибок, определяются область, в которую попало принятое кодовое слово, затем кодовое слово через дешифратор 5 поступает на выход устройства. Цепочка из блока 9 определения четности и компаратора 10 позволяет устанавливать режим работы блока 4. 4 ил. (Л

| Устройство для обнаружения ошибок | 1981 |

|

SU1065819A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| E.R | |||

| Berlekamp IEEE Trans, on Inf | |||

| Th vol | |||

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1988-01-15—Публикация

1986-03-24—Подача