Изобретение относится к автоматике и вычислительной технике и может быть использовано при создании инвариантных к помехам линейных преобразователей.

Известно устройство для контроля и линеаризации передаточных характеристик многоканальных преобразователей, содержащее блок выявления неисправности преобразователей, блок вычисления характеристик преобразователей, коммутатор и инвертор, вход которого является входом устройства для ввода сигнала, равного подаваемому на один из контролируемых преобразователей, входы устройства для подключения выходов двух контролируемых преобразователей соединены с первыми и вторыми информационными входами блока выявления неисправности преобразователей и блока вычисления характеристик преобразователей, выход которого является информационным выходом устройства, первый информационный вход коммутатора соединен с входом устройства для ввода сигнала, равного подаваемого на один из контролируемых преобразователей, второй информационный вход коммутатора связан с выходом инвертора, управляющие входы коммутатора и блока вычисления характеристик преобразователей подключены к выходу блока выявления неисправности преобразователей, выход коммутатора служит выходом устройства для подачи сигнала на другой контролируемый преобразователь.

Блок вычисления характеристик преобразователей содержит четырнадцать сумматоров, четыре узла деления, три узла умножения и три узла оперативной памяти, входы первых слагаемых первого, третьего и седьмого, десятого и двенадцатого сумматоров, прямые входы восьмого и одиннадцатого и инвертирующий вход шестого сумматоров и вход первого сомножителя первого узла умножения служат для ввода постоянных величин вычислений, вход второго слагаемого первого сумматора связан с первым информационным входом блока, а выход соединен с входом первых слагаемых второго, четвертого и пятого сумматоров, второй информационный вход блока подключен к входам вторых слагаемых второго и третьего сумматоров, выход второго сумматора соединен с прямым входом шестого и с входом второго слагаемого седьмого сумматоров, выходы которых связаны соответственно с входами делимого и делителя второго узла деления, выход которого подключен к входу второго сомножителя первого узла умножения и к инвертирующему входу одиннадцатого сумматора, выход третьего сумматора соединен с входами вторых слагаемых четвертого и пятого сумматоров, выходы которых связаны соответственно с входами делимого и делителя первого узла деления, выход которого подключен к информационному входу первого узла оперативной памяти и к инвертирующим входам восьмого и девятого сумматоров, выход первого узла оперативной памяти соединен с прямым входом девятого сумматора, с первым прямым входом тринадцатого сумматора и с входом второго слагаемого десятого сумматора, выход которого связан с входом первого сомножителя третьего узла умножения, выход которого подключен к второму прямому входу тринадцатого сумматора, а вход второго сомножителя, прямой вход четырнадцатого сумматора и вход второго слагаемого двенадцатого сумматора соединены с выходом второго узла оперативной памяти, информационный вход которого связан с выходом четвертого узла деления, вход делимого которого подключен к выходу первого узла умножения, а вход делителя к выходу одиннадцатого сумматора, входы делителя и делимого третьего узла деления соответственно с выходами восьмого и девятого сумматоров, а выход связан с входом первого сомножителя второго узла умножения, вход второго сомножителя которого подключен к выходу двенадцатого сумматора, а выход к инвертирующему входу тринадцатого сумматора и к первому информационному входу третьего узла оперативной памяти, второй информационный вход которого соединен с выходом четырнадцатого сумматора, инвертирующий вход которого и третий информационный вход третьего узла оперативной памяти связаны с выходом тринадцатого сумматора, управляющие входы всех узлов оперативной памяти подключены к управляющему входу блока, выход третьего узла оперативной памяти связан с выходом блока.

Недостатками устройства являются большое время, требуемое для осуществления линеаризации передаточных характеристик преобразователей, а также сложность устройства.

Цель изобретения упрощение устройства и повышение его быстродействия.

Повышение быстродействия достигается тем, что часть математических операций блок вычисления характеристик преобразователей осуществляет на этапе выявления неисправности преобразователей.

Для достижения цели в устройстве для контроля и линеаризации передаточных характеристик многоканальных преобразователей блок вычисления характеристик преобразователей содержит блок выявления неисправности преобразователей, первые и вторые информационные входы блока вычисления характеристик преобразователей одновременно являются соответственно первыми и вторыми информационными входами блока выявления неисправности преобразователей. Блок вычисления характеристик преобразователей содержит устройство для подключения выходов двух контролируемых преобразователей, т.е. одни и те же элементы блока вычисления характеристик преобразователей осуществляют математические операции и по контролю, и по линеаризации передаточных характеристик преобразователей.

Упрощение устройства достигнуто за счет того, что первый, второй, третий, четвертый, пятый, шестой, седьмой сумматоры, первый и второй узлы деления блока вычисления характеристик преобразователей выполнены в виде мостовой схемы, состоящей из включенных между шинами питания двух резистивных ветвей, одна из которых содержит последовательно соединенные первый резистор, устройство для подключения выходов двух контролируемых преобразователей и второй резистор, а другая третий, четвертый, пятый и шестой последовательно соединенные резисторы, устройство для подключения выходов двух контролируемых преобразователей имеет четыре входа и три выхода, первый и второй входы которого соединены с первыми информационными входами блока вычисления характеристик преобразователей, а третий и четвертый вход с его вторыми информационными входами, третий и второй выходы устройства для подключения выходов двух контролируемых преобразователей соединены соответственно с первым и вторым резисторами, мостовая схема имеет два выхода, первым выходом мостовой схемы являются точка соединения четвертого и пятого резисторов и первый выход устройства для подключения выходов двух контролируемых преобразователей, а вторым выходом точка соединения пятого и шестого резисторов и второй выход устройства для подключения выходов двух контролируемых преобразователей, блок вычисления характеристик преобразователей содержит пятнадцатый и шестнадцатый сумматоры, вход пятнадцатого сумматора подключен к первому выходу мостовой схемы, а выход к информационным входам первого узла оперативной памяти и к инвертирующим входам восьмого и девятого сумматоров, вход шестнадцатого сумматора подключен к второму выходу мостовой схемы, а выход к входу второго сомножителя первого узла умножения и к инвертирующему входу одиннадцатого сумматора и является выходом блока выявления неисправности преобразователей.

Использование мостовой схемы уменьшает количество необходимых для реализации устройства операционных усилителей (на семь штук). Процесс линеаризации передаточных характеристик преобразователей совмещен по времени с процессом их контроля.

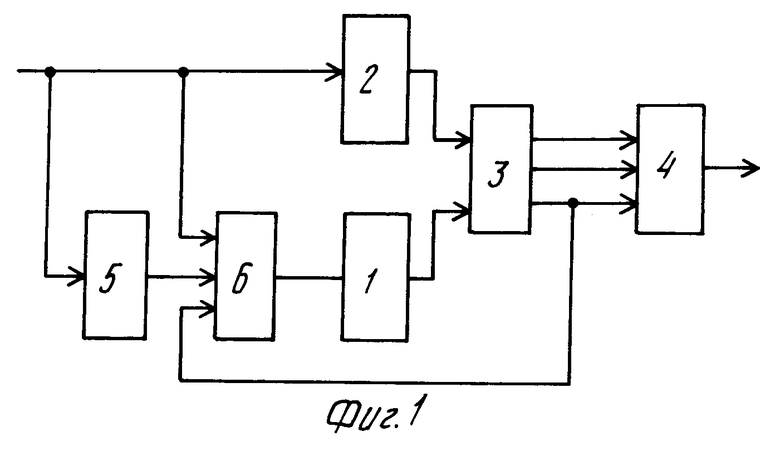

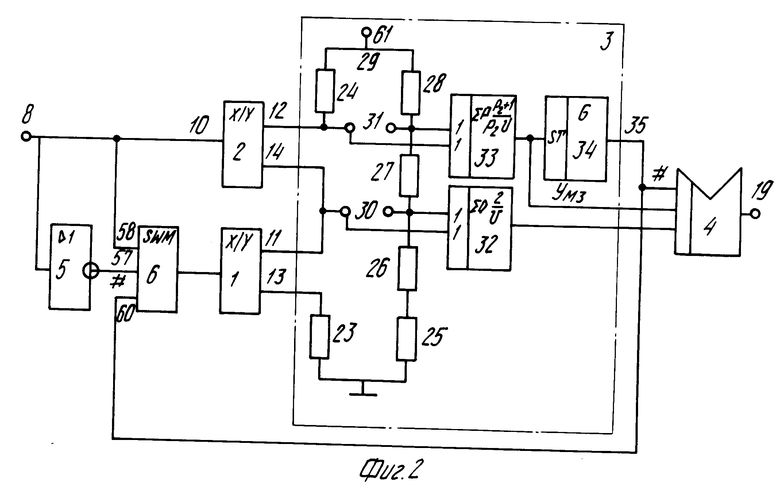

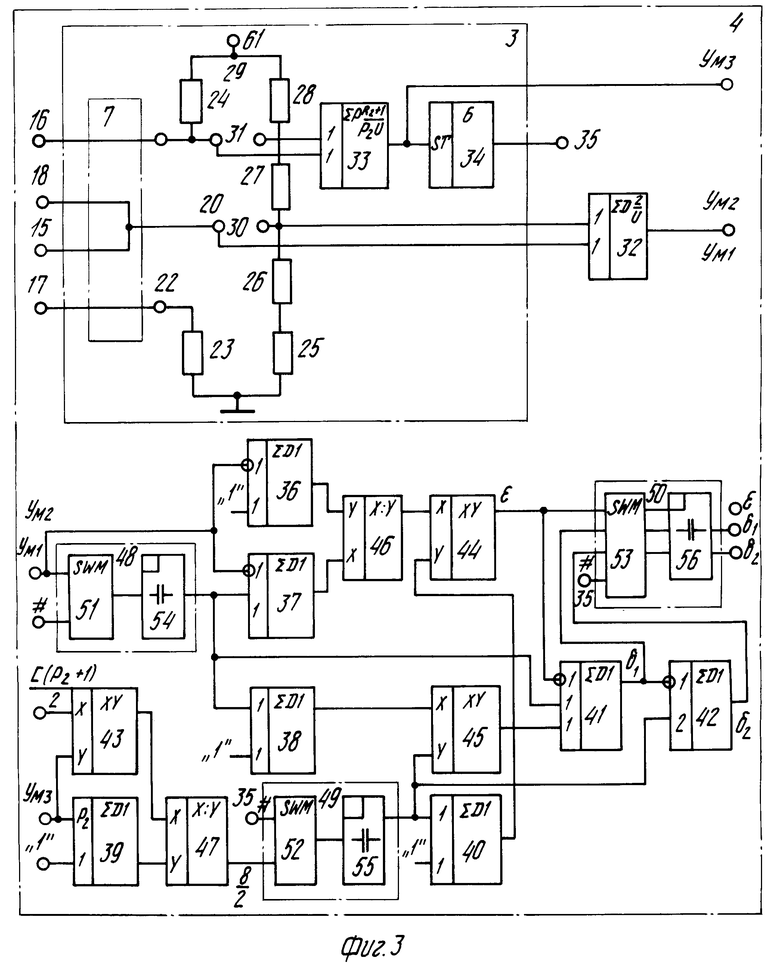

На фиг.1 представлена структурная схема устройства; на фиг.2 функциональная схема блока вычисления характеристик преобразователей; на фиг.3 функциональная схема устройства.

На схемах представлены первый 1 и второй 2 преобразователи полевые транзисторы с постоянными уровнями смещения рабочих точек Z10 Z20 Zi0, блок 3 выявления неисправностей преобразователей, блок 4 вычисления характеристик преобразователей, инвертор 5 и коммутатор 6, устройство 7 для подключения выходов двух контролируемых преобразователей, вход 8 устройства, вход 9 первого преобразователя затвор полевого транзистора 1, вход 10 второго преобразователя затвор полевого транзистора 2, первый выход 11 первого преобразователя сток полевого транзистора 1, первый выход 12 второго преобразователя сток полевого транзистора 2, второй выход 13 первого преобразователя исток полевого транзистора 1, второй выход 14 второго преобразователя исток полевого транзистора 2, первые информационные входы 15 и 16 блока 4, вторые информационные входы 17 и 18 блока 4, выход 19 блока 4, первый 20, второй 21 и третий 22 выходы устройства 7, резисторы 23-28 с первого по шестой, образующие мостовую схему 29, первый 30 и второй 31 выходы мостовой схемы 29, сумматор 32, сумматор 33 и генератор 34, выход 35 блока 3, в блоке 4: сумматоры 36-42 с восьмого по четырнадцатый, три узла 43-45 умножения, третий 46 и четвертый 47 узлы деления, три узла 48-50 оперативной памяти, включающие коммутаторы 51-53 в первом, втором и третьем узлах соответственно и ячейки 54-56 памяти, в блоке 6: информационные входы 57, 58 и выход 59, управляющий вход 60.

Коммутатор 6 имеет два режима работы в зависимости от наличия сигнала на управляющем входе 60. Первым режимом работы коммутатора является соединение выхода 59 и входа 57. Вторым режимом работы является соединение выхода 59 и входа 58.

На один вход узла 43 подано смещение (р2 + 1)C/2. Смещение, соответствующее константе "1", подано на входы сумматоров 36, 38, 39 и 40.

Выходом 19 устройства является выход узла 50, включающий три составные части (с первой снимают сигнал, соответствующий величине ε со второй величине δ1 а с третьей величине δ2 ).

Управление блоком 4 осуществляют путем подачи тактовых прямоугольных импульсов с выхода 35 на управляющие входы включающих коммутаторов 51-53. Коммутаторы 51 и 52 являются нормально замкнутыми, а коммутатор 53 нормально разомкнутым.

Мостовая схема 29 состоит из двух мостовых схем. В первое плечо первой мостовой схемы последовательно включены первый полевой транзистор 1 и первый резистор 23, во второе плечо второй полевой транзистор 2 и второй резистор 24, в третье плечо третий 25 и четвертый 26 резисторы, в четвертое плечо пятый и шестой резисторы 27 и 28.

В первое плечо второй мостовой схемы последовательно включены первый резистор 23 и полевые транзисторы 1 и 2, во второе плечо второй резистор 24, в третье плечо третий 25, четвертый 26 и пятый 27 резисторы, в четвертое плечо шестой 28 резистор.

Мостовая схема подключена к источнику 61 питания U. На основе мостовой схемы реализуют три алгебраических уравнения.

Первое и второе алгебраические уравнения реализуют на основе первой мостовой схемы. В исходном состоянии на полевые транзисторы 1 и 2 поданы постоянные уровни смещения Zi0. При отсутствии информационных сигналов на входах 9 и 10 (r1 r2 0) выполнены соотношения

Z1j Z10+Z10' Z31; Z2j Z20 + Z20' Z41;

Z1j Z2j; j 1,2, (1) где Z10', Z20' сопротивления первого 23 и второго 24 резисторов соответственно;

Z31, Z41 сопротивления третьего и четвертого плеч первого моста;

Z10, Z20 сопротивления исток сток транзисторов 1 и 2.

Сумматор 32 имеет входной дифференциальный каскад на полевых транзисторах. Следовательно, мостовая схема работает на нагрузку с большим входным сопротивлением и напряжение на выходе 30

yj=U

U

U  j1,2. (2)

j1,2. (2)

Первое алгебраическое уравнение. Первый режим работы коммутатора 6.

j 1, Z11 Z10' + Z10 + k1r1 + Δ1 (3)

Z21 Z20' + Z20 k2r2 + Δ1 Z10 Z20 kizi0, (4) где r1 r2 ri информационные сигналы на затворах транзисторов 1 и 2 соответственно;

k1 k2 ki чувствительности сопротивлений Z1j и Z2j к изменению сигналов r1 и r2 соответственно;

Δ1, Δ2 погрешности функционирования транзисторов 1 и 2 соответственно в момент контроля и линеаризации их характеристик.

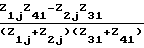

Подставив (3) и (4) в (2), получим, что первая мостовая схема реализует уравнение Kj=

Kj=  j=1.

j=1.

Откуда

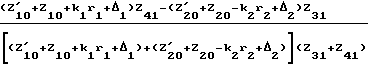

[2+(1-p1)yм1]ε+(1-p1yм1)δ1-(1+yм1)δ2= (p1+1)yм1, (5)

где

ε1=  ε2=

ε2=  ε1=ε2=ε; δ1=

ε1=ε2=ε; δ1=  δ2=

δ2=

yм1=  ·

·  p1=

p1=

.

.

Второе алгебраическое уравнение. Второй режим работы коммутатора 6.

j 2, Z12 Z10' + Z10 k1r1 + Δ1 (6)

Z22 Z20' + Z20 k2r2 + Δ1 (7)

Подставив (6) и (7) в (2), получим, что первая мостовая схема реализует уравнение

(p1+1) yм2 ε +(1-p1yм2) -(1+yм2) δ2= (p1+1) yм2, (8) где yм2=  ·

·  .

.

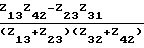

Третье алгебраическое уравнение реализуют на основе второй мостовой схемы. В исходном состоянии, при отсутствии и информационных сигналов на входах 9 и 10 преобразователей, r1 r2 0, выполнены соотношения

Z13 Z10' + Z10 + Z20 Z32; Z23 Z20' Z42; (9) где Z13, Z23, Z32, Z42 сопротивления первого, второго, третьего и четвертого плеч второй мостовой схемы.

Сумматор 33 имеет входной дифференциальный каскад на полевых транзисторах. Следовательно, вторая мостовая схема работает на нагрузку с большим входным сопротивлением и напряжение на выходе 31 равно

y3=U

U

U  . (10)

. (10)

Первый режим работы коммутатора 6. j 3, Z13 (Z10'+ Z10+ k1r1+ Δ1)+(Z20'+ Z20- k2r2+ Δ2 ), (11)

Z23 Z20'. (12)

Подставив выражения (11) и (12) в (10), получим уравнение

δ1+δ2=  ·C, (13) где

·C, (13) где

yм3=  ·

·  C 1+

C 1+  .

.

Таким образом, на основе мостовой схемы 29, при преобразовании полевыми транзисторами 1 и 2 последовательно парафазных и синфазных сигналов, реализуют систему уравнений

(14)

(14)

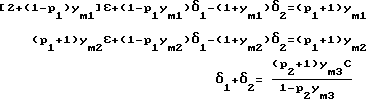

Откуда

ε

+ 1

+ 1 , (15) где b

, (15) где b  ,

,

δ1= (yм1-ε)+  (1+yм1), (16)

(1+yм1), (16)

δ2=b-δ1 (17)

Порядок функционального диагностирования преобразователей 1 и 2 состоит в следующем.

1. Исходя из максимально возможных значений входных информационных сигналов на основе выражений (1) и (9) выбирают Z10' и Z20', задают смещения Z10 и Z20 и выбирают соответствующие сопротивления третьего Z30, четвертого Z40, пятого Z50 и шестого Z60 резисторов.

2. На входы преобразователей последовательно подают сначала парафазные r1|-r2| а затем синфазные r1=r2 сигналы, чередуя режим работы коммутатора 6.

3. С использованием напряжений, снимаемых с выходов 30 и 31 первой и второй мостовых схем, на основе сумматоров 32 и 33, рассчитывают коэффициенты системы уравнений (14).

4. Определяют решение системы уравнений на основе сумматоров 36-42, узлов 43-45 умножения, узлов 46 и 47 деления и узлов 48-50 оперативной памяти.

Устройство работает следующим образом.

Пусть преобразователи функционируют без погрешностей. Об этом свидетельствует отсутствие напряжения на выходе сумматора 33. Генератор 34 не включен. На выходе 19 устройства значения сигналов равны нулю.

Информационный сигнал с входа 8 устройства через инвертор 5 и коммутатор 6 поступает на затвор транзистора первого преобразователя 1 и непосредственно на затвор 10 транзистора второго преобразователя 2. Сигналы на затворах 9 и 10 транзисторов 1 и 2 являются парафазными. Сигналы с выходов 30 и 31 мостовой схемы используют в информационно-измерительной системе без обработки. Устройство контроля и линеаризации постоянно контролирует величину погрешности функционирования транзисторов 1 и 2, путем сложения сигналов на выходе 31, и одновременно рассчитывает величину ум1 и ум3.

Расчет величин ум1 и ум3 осуществляют путем подачи сигналов с выходов 30 и 31 на входы сумматоров 32 и 33 соответственно. Реализуют уравнения (5) и (13). Сигнал, соответствующий величине ум1, получают на выходе сумматора 32, а сигнал, соответствующий величине ум3, на выходе сумматора 33. Сигнал ум1 запоминают в ячейке 54, куда он поступает через нормально замкнутый коммутатор 51. Сигнал ум3 дополнительно преобразуют в сумматоре 39, узлах умножения 43 и деления 47, получая таким образом сигнал, соответствующий величине b/2, используемый в дальнейшем при расчете величин ε,δ1 и δ2 Сигнал b/2 поступает в ячейку 55.

При возникновении погрешностей функционирования в транзисторах 1 и/или 2 на выходе сумматора 33 появляется сигнал, включающий генератор 34, прямоугольный импульс которого поступает на управляющий выход 35 блока 3 и таким образом на управляющие входы коммутаторов 51-53, а также на управляющий вход 60 коммутатора 6.

Коммутаторы 51 и 52 размыкают электрические цепи, способствуя запоминанию величин ум1 и b/2 в ячейках 54 и 55 соответственно. Коммутатор 53 подключает ячейку 56 к сумматорам 41 и 42 и узлу 44 умножения для запоминания величин εδ1 и δ2 которые будут рассчитаны.

Коммутатор 6 подключает затвор полевого транзистора 1 непосредственно к входу 8 устройства. Таким образом, на затворы 9 и 10 транзисторов поступает синфазный сигнал. Сигнал на выходе 31 остается отличным от нуля. Генератор не выключается.

На основе сумматора 32 рассчитывают величину ум2. Сигнал, соответствующий величине ум2 (с выхода сумматора 32) поступает одновременно с сигналами, соответствующими величинам ум1 и b/2 (из ячеек 54 и 55), на входы сумматоров 36, 37, 38 и 40. Эти три сигнала преобразуются сумматорами 32, 33, 34, 40, 41 и 42, узлами деления 46 и умножения 44 и 45. Находится решение системы уравнений (14) по формулам (15), (16) и (17).

На входы коммутатора 53 поступают три сигнала, соответствующие величинам εδ1 и δ2 Сигнал ε поступает с выхода узла 44 умножения, сигнал δ1 с выхода сумматора 41, сигнал δ2 с выхода сумматора 42. Коммутатор 53 замкнут, поэтому сигналы, соответствующие величинам ε,δ1 и δ2 поступают в ячейку 56.

В момент окончания действия прямоугольного импульса коммутатор 6 и коммутаторы 51-53 возвращаются в исходное состояние. Если погрешности функционирования полевых транзисторов 1 и 2 отсутствуют, то сигнал на выходе сумматора 33 нулевой, генератор 34 выключен, устройство контролирует величину погрешностей Δ1 и Δ2 функционирования транзисторов 1 и 2 и одновременно рассчитывает величину ум1 и b/2. При появлении погрешностей генератор 34 включается, генерирует прямоугольный импульс и процессы расчета величин ε,δ1 и δ2 повторяются.

Технико-экономическая эффективность от использования изобретения заключается в повышении быстродействия за счет осуществления параллельно процессов контроля и расчета величин ум1 и ум3. Упрощение устройства достигается за счет замены семи операционных усилителей одной мостовой схемой.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство Титова В.Б. для контроля и линеаризации передаточных характеристик многоканальных преобразователей | 1989 |

|

SU1675854A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА | 1991 |

|

RU2006916C1 |

| Устройство для управления многофазным вентильным преобразователем | 1989 |

|

SU1721755A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В ПОЛИНОМИАЛЬНОЙ СИСТЕМЕ КЛАССА ВЫЧЕТОВ | 2004 |

|

RU2267808C2 |

| Резистивный узел сеточной модели | 1983 |

|

SU1120366A1 |

| Множительное устройство | 1980 |

|

SU924720A1 |

| Программный генератор | 1982 |

|

SU1062858A2 |

| Устройство для измерения температуры | 1985 |

|

SU1390515A1 |

| РЕКОНФИГУРИРУЕМЫЙ АСИНХРОННЫЙ СУММАТОР-УМНОЖИТЕЛЬ | 1999 |

|

RU2159464C1 |

| СИСТОЛИЧЕСКИЙ ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1992 |

|

RU2029437C1 |

Изобретение относится к радиоэлектронике и предназначено для использования в автоматике, вычислительной технике и радиотехнических устройствах. Устройство для контроля и линеаризации передаточных характеристик преобразователей содержит устройство для ввода сигнала и блок вычисления характеристик преобразователей, содержащий устройство для подключения выходов двух контролируемых преобразователей и блок выявления неисправности преобразователей. Блок выявления неисправности преобразователей выполнен в виде мостовой схемы, которая позволяет не только осуществлять контроль, но и одновременно проводить расчет характеристик преобразователей. 3 ил.

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ЛИНЕАРИЗАЦИИ ПЕРЕДАТОЧНЫХ ХАРАКТЕРИСТИК ПРЕОБРАЗОВАТЕЛЕЙ, содержащее блок выявления неисправностей преобразователей, включающий генератор импульсов и первый сумматор, подключенный выходом к входу запуска генератора импульсов, блок вычисления характеристик преобразователей, выход которого является информационным выходом устройства, инвертор, подключенный выходом к первому информационному входу коммутатора, выход которого соединен с входом первого преобразователя, вход инвертора и второй информационный вход коммутатора объединены и являются информационным входом устройства, подключенным к входу второго преобразователя, выход генератора импульсов соединен с управляющими входами блока вычисления характеристик преобразователей и коммутатора, отличающееся тем, что блок выявления неисправностей преобразователей содержит второй сумматор и мостовую схему, включающую первую резистивную ветвь, содержащую первый и второй резисторы, подключенные первыми выводами к первым выводам соответственно первого и второго преобразователей, вторые выводы которых объединены и являются первым выводом первого выхода мостовой схемы, и вторую резистивную ветвь, содержащую включенные последовательно третий, четвертый, пятый и шестой резисторы, общий вывод четвертого и пятого резисторов является вторым выводом первого выхода мостовой схемы, объединенные первый вывод второго резистора и первый вывод второго преобразователя, а также общий вывод пятого и шестого резисторов являются соответственно первым и вторым выводами второго выхода мостовой схемы, подключенной вторым и первым выходами к входам соответственно первого сумматора и второго сумматора, связанного выходом с первым информационным входом блока вычисления характеристик преобразователей, подключенного вторым информационным входом к выходу первого сумматора, общие выводы второго и шестого резисторов, первого и третьего резисторов являются соответственно шинами питания и нулевого потенциала устройства.

| Устройство Титова В.Б. для контроля и линеаризации передаточных характеристик многоканальных преобразователей | 1989 |

|

SU1675854A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1995-12-27—Публикация

1991-04-19—Подача