(54) МНОЖИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое множительное устройство | 1986 |

|

SU1319047A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| Аналоговое множительное устройство | 1985 |

|

SU1280401A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Аналоговое множительное устройство | 1987 |

|

SU1497625A1 |

| Аналоговое множительное устройство | 1979 |

|

SU860087A1 |

| Множительное устройство | 1977 |

|

SU667971A1 |

| Множительное устройство | 1982 |

|

SU1119037A1 |

| Четырехквадрантное множительное устройство | 1980 |

|

SU957225A1 |

| Перемножающее устройство | 1987 |

|

SU1465896A1 |

Изобретение относится к аналоговой вычислительной технике и может быть использовано, в частности, в системах векторного управления, а также.в измерительной технике.

Известны множительные устройства, содержащие два полевых транзистора, три операционных усилителя, семь резисторов 1 .; .

К недостаткам данного устройства относится невысокая термостабильностк. и точность,

Наиболее близким по технической сущности является множительное устройство, содержащее две идентичные множительные мостовые схемы: рабочую и компенсирующую, в первом и втором плечах каждой из которых имеется по балансировочному резистору, а в третьем и четвертых плечах содержатся элементы с управляемой проводимостью, выполненные на полевом транзисторе, образующие.первую и вторую интегральные согласованные пары, содержащее также два интегральных операционных усилителя, при этом к выходной диагонали мостовых схем подключены дифференциальные входы операционных усилителей, причем инвертирующий вход первого усилителя подключен к общим

выводам первого балансировочного резистора и стока первого полевого транзистора рабочей мостовой схемы и к первому выводу первого масштабного резистора, другой вывод которого подключен к выходу первого усилителя и выходу множительного устройства, а неинвертирующий вход операционного усилителя подключен к общим выводам

10 второго балансировочного резистора и стока второго полевого транзистора рабочей мостовой схемы и к первому выводу второго масштабного резистора, другой вывод которого соединен с ис

15 токами полевых транзисторов рабочей и компенсирующей мостовой схем и шиной нулевого потенциала, а входная диагональ рабочей мостовой схемы является первым входом множительного

20 устройства, инвертирующий вход второго операционного усилителя подключен к общим выводам первого балан.сировочного резистора и стока первого полевого транзистора компенси25рующей мостовой схемы и к первому выводу третьего масштабного резистора, другой вывод которого соединен со вторым входом множительного устройства, а неинвертирующий вход вто30рого уся;р1теля подключен к общим выводам второго балансировочного резистора и стока второго полевого транзистора компенсирующей мостовой схемы и к первому выводу четвертого масштабного резистора, другой вывод которого соединен с шиной нулевого (Потенциала, к входной диагонали компенсирующей мостовой схемы подключен средний вывод первого подстроечного потенциометра, первый крайний вывод которого соединен с шиной нулевого потенциала, а второй крайний вывод подключен к выходу источника опорного сигнала, выход второго операционного усилителя соединен с затворами вторых полевых транзисторов рабочей и компенсирующей мостовыхсхем, а затворы первых полевых транзисторов рабочей и компенсирующей .мостовых схем соединены со средними выводами соответственно третьего и четвертого подстроечных потенциометров , первые крайние выводы которых соединены с выходом источника сигнала смещения, а вторые крайние выводы - с шиной нулевого потенциала 2. . Однако известное множи1 ельное уст фойство обладает недостатком. При высокой линейности (статической точности) в каждом из четырех квадранто устройство в общем случае имеет различные масштабные- коэффициенты в каж дом из квадрантов, что обусловлено отличием коэффициентов угла наклона вольт-амперных характеристик полевого транзистора (oL) при изменении знака напряжения на стоке (U(.) и неизменном напряжении на затворе З, .,при Uc О- ПРИ U( и разбросом характеристик транзисторов пары (в частности зависимости сопротивления сток-исток от напряжения на затворе). Линейность этого множитель ного устройства в каждом из квадрантов составляет 0,2-0,5%. Разброс же коэффициентов передачи в квадрантах |ДК%| достигает 5%. Например, результат перемножения сигналов, равных I U-11 iU/j.1 10 В, в раз ных квадрантах по абсолютной величине может составить 9,5 до 10 и не может быть для конкретного устройства предугадан и скорректирован. . Использовать же устройство для перемножения гармонического сигнала с аналоговым с точностью до 1% уже нельзя. Так как если входные сигналы и 10 sin wt и иII 10, то на выxqpe вместо сигнала и(,| 10 sinu)t мы получим UftbiK- (10-iK)sinwtl+.uK, в частном случае, например, ,1 (9,5 siniut)+0,5 (выходной гармони1ческий сигнал имеет постоянную составляющую и К% , превышающую 1%, /дК%/ 100%, где ДК в вольтах). Можно далее показать, что перемножение с помощью прототипа двух гармонических сигналов вида sin Ч вызовет недопустимые искажения выходных сигналов (относительная ве-кторная погрешность больше допустимой) . Это ограничивает точность работы множительного устройства. Цель изобретения - повышение точности работы множительного устройства, Поставленная цель достигается тем, что в известное множительное устройство, содержащее два операционных усилителя, четыре масштабных резистора, три подстрочных потенциометра, источник стабильного сигнгипа, компенсирующий и рабочий множительные мосты, в первое и второе плечи множительных мостов включены соответственно первый, вхорой, третий и четвертый балансировочные резисторы, а в третье и четвертое плечи включены соответственно первый, второй, третий и четвертый элементы с управляемой проводимостью, выполненные на управляемых полевых транзисторах, истоки всех управляемых полевых транзисторов объединены и подключены к шине нулевого потенциала, сток первого управляемого транзистора и первый вывод первого балансировочного резистора объединены и подключены к инвертирующему входу первого операционного усилителя, сток второго управляемого полевого транзистора и первый вывод второго балансировочного резистора объединены и подключены к неинвертирующему входу первого операционного усилителя и через первый масштабный резистор подключены к шине нулевого потенциала, сток третьего управляемого полевого транзистора и первый вывод третьего балансировочного резистора объединены и подключены к инвертирующему входу второго операционного усилителя, сток четвертого управляемого полевого транзистора и первый вывод четвертого балансировочного резистора объединены и подключены к неинвертирующему, входу второго операционного усилателя и через второй масштабный резистор подключены к шине нулевого потенциала, выход второго операционного усилителя через третий масштабный резистор подключен к его инвертирующему входу и является выходом устройства, инвертирующий вход первого операционного усилителя через четвертый масштабный резистор подключен к первому входу устройства, вторле выводы третьего и четвертого балансировочных резисторов объединены и являются вторым входом устройства, вторые выводы первого и второго балансировочных резисторов объединены и подключены к среднему выводу первого подстроечного потенциометра, первый крайний вывод которого подключен к шине нулевого потенциала, затйоры первого и третьего управляемых полевьЬс транзисторов соответственно подключены к средним выводам второго и третьего подстроечных потенциометров, первые крайние выводы которых объединены и подключены к шине нулевого потенциала, а вторые крайние выводы второго

и третьего подстроечных потенциометров объединены и подключены к выходу источника стабильного сигнала, затвора второго и четвертого управляемых полевых транзисторов объединены и подключены к выходу первого операционного усилителя, введены два пороговых блока, элемент И, сумматор, четвертый, пятый и шестой подстроечные потенциометры и источник опорного сигнала, входы первого и второго пороговых блоков соответственно под- ключены к первому и второму входам устройства, выходы пороговых блоков подключены соответственно к первому и второму входам элемента И и к первым крайним выводам четвертого и пя- того подстроечных потенциометров, вторле крайние выводы которых подключены к нулевого потенциала, выход элемента И подключен к первому крайнему выводу шестого подстроечног потенциометра, второй крайний вывод которого подключен к шине нулевого потенциала, первьШ вход сумматора подключен к выходу источника опорного сигнала, второй, третий и четверктый входы сумматора подключены к средним выводам соответственно четвертого пятого и шестого подстроечных потенциометров, выход сумматора подключен ко второму крайнему выводу первого подстроечного потенци- ометра.

Указанное множительное устройство обладает не только высокой теЕялостабйльностью, но и обеспечивает пере- множение сигналов с масштабным коэффициентом, равным К, во всех четырех квадрантах, что важно при перемножении гармонических сигналов (при преобразованиях векторных величин).,

В предлагаемом устройстве можно . устранить разброс коэффициента передачи в квадрантах с погрешностью ,2, а следовательно, уменьшить общую погрешность четырехквадрантных множительных устройств до 0,2-0,5%, что позволяет существенно повысить точность четырехквадрантного перемножения сигналов.

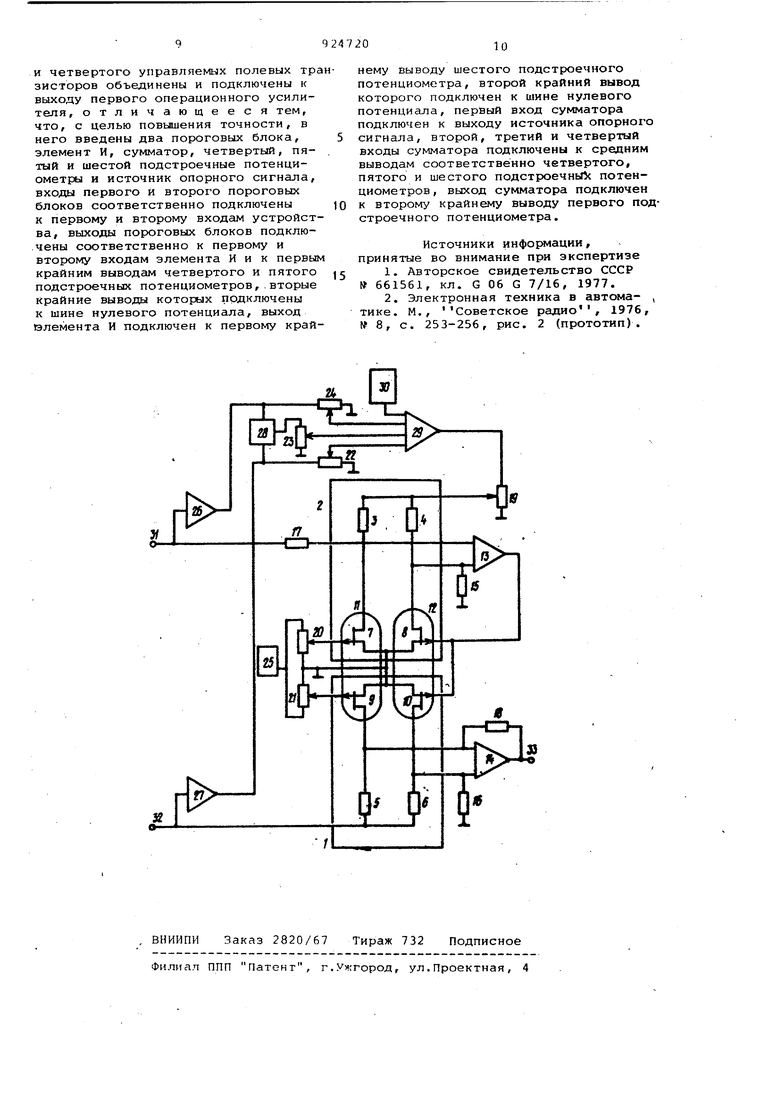

На чертеже приведена функциональная схема предлагаемого, устройства.

Множительное устройство содержит два идентичных множительных моста рабочий 1 и компенсирующий 2, кгикдый из которых содержит в первсил и втором плечах соответственно балансировочные резисторы 3-6, а в третьем-и

четвертом плечах - элементы с управляемой проводимо .тью, выполненные на .управляемых полевых транзисторах 7-10 соответственно из первой 11 и второй 12 согласованных пар, операционные .усилители 13 и 14, масштабные резисторы 15-18, подстроечные потенциометры 19-24, источник 25 стабильного сигнала, пороговые блоки 26 и 27, элемент И 28, сумматор 29, источник 30 опорного сигнала, первый вход устройства 31, второй вход устройства 32 и выход устройства 33.

Множительное устройство работает следующим образом.

Сигнал первого сомножителя и поступает на вход 32 устройства. Коэффициент передачи рабочего моста 1 к зависит от сигнала второго сомножителя UQ на входе 31 устройства, а напряжение с выходной диагонали рабочего моста 1 поступает на дифференциальные входы второго операционного усилителя 14.

С целью линеаризации характеристики множительного устройства Uat f(U|2), нелинейность которой обусловлена нелинейностью зависимости сопротивления сток-исток от напряжения на затворе полевого транзистора 10 (в режиме управляемого резистора) и нелинейной зависимостью коэффициента передачи рабочего моста 1 от изменения сопротивления сток-исток полевого транзистора 10, а также для обеспечения стабильности устройства сигнал второго сомножителя UQ через масштабный резистор 17 поступает на инвертирующий вход первого операционного усилителя 13, в цепь обратной связи которого включен идентичный по параметрам рабочего моста 1 компенсиг рующий мост 2, а с выхода опергщионного усилителя 13 сигнал, связанный с сигналом второго 1сомнс житёлй Uij зависимостью U fi(Uq) , обратной линеаризуемой характеристике множительного устройства, поступает на затвор полевого транзистора 10 рабочего моста 1. На выводы балансировочных резисторов 3 и 4 компенсирующего моста 2 с подвижного котакта первого подстроечного потенциометра 19 через сумматор 29 подается опорный сигнал с выхода источника 30 опорного сигнала, обратно пропорциональный масштабному коэффициенту множительного устройства.

Для обеспечения умножения в четырех квадрантах с высокой линейностью в каждом из квадрантов и для получения максимального подавления сигнала первого сомножителя и на выходе устройства используются соответственно подстроечные потенциометры 20 и 21, на которые поступает стабильный сигнал с выхода источника 25 стабильного сигнала. Так как ввиду неизбежного технологического разброса характеристик полевых транзисторов в.интегральной паре и неравенства коэффициентов наклона вольт-амперных характеристик при смене полярности напряжения сток исток полевого транзистора, при пост янстве напряжения на затворе (при смене знака сигнала на входе 32) в общем случае в каждом из четырех ква рантов масштабные коэффициенты устройства неравны K Kj Kj7K4, для их выравнивания и получения общего коэф фициента, равного эталонному , на входы сумматора 29, кроме опорного сигнала, подаются корректирующие сиг налы. На второй вход подается сигнал с подстроечного потенциометра 24, который уменьшает по абсолютной величине выходное напряжение сумматора 29 пропорционально ошибке при сигнале сомножителя на входе 32, имеющем знак, обратный знаку этого сомножителя в эталонном квадранте На третий вход сумматора 29 подается сигнал с движка потенциометра 24, уменьшающий по абсолютной величине выходное напряжение сумматора 29 пропорционально ошибке при сигнале сомножителя на входе 31, имеющем знак, обратный знаку этого сомножиг теля в эталонном квадранте Кз-лКз К-1 На четвертый вход сумматора 29 посту пает сигнал с движка подстроечного потенциометра 23, изменяющий величину выходного напряжения сумматора 29 пропорционально ошибке при сигналах на входах 31 и 32, имеющих знаки, обратные знакам соответствующих сигналов в эталонном квадранте К4-ДК К. Сигнал на подстроечный потенциометр 22 поступает с выхода порогового блока 27 только при сигнале первого сомножителя на входе 32, имею.-, щем знак, противоположный знаку этого сигнала в эталонном квадранте, а на подстроечный потенциометр 24 - с выхода порогового блока 26 при сигнале второго сомножителя на входе 31 со знаком, обратным знаку сигнала второго сомножителя в эталонном квадранте. Сигнал на подстроечный потенциометр 23 поступает с выхода элемента И 28 при знаках сигналов сомножителей, поступающих с выходов 31, и 32 на входы элемента 28, проти войоложных знаком сомножителей в эта лонном квадранте. Предлагаемое множительное устройство позволяет значительно повысить точность четырехквадрантного перемно жения сигналов. Формула изобретения Множительйое устройство, содержащее два операционных усилителя, четыре масштабных резистора, три подстроечных потенциометра, источник стабильного сигнала, компенсирующий и рабочий множительные мосты, в первое и второе плечи множительных мостов включены соответственно первый, второй, третий и четвертый балансировочные резисторы, а в третье и четвертое плечи включены соответственно первый, второй, третий и четвертый элементы с управляемой проводимостью, выполненные на управляемых полевых транзисторах, истоки всех управляемых полевых транзисторов объединены и подключены к шине нулевого потенциала, сток первого управляемого полевого транзистора и первый вывод первого балансировочного резистора объединены и подключены /к инвертирующему входу первого операционного усилителя, сток второго Iуправляемого полевого транзистора и первый вывод второгобалансировочного резистора объединены и подключены к.неинвертирующему входу первого операционного усилителя и через первый масштабный резистор подключены к шине нулевого потенциала, сток третьего управляемого полевого, транзистора и первый вывод третьего балансиро вочного резистора объединены и подключены к инвертирующему входу второго операционного усилителя, сток четвертого управляемого полевого транзистора и первый вывод четвертого балансировочного резистора объединены и подключены к неинвертирующему входу второго операционного усилителя и через второй масштабный резистор подключены к шине нулевого потенциала, выход второго операционного усилителя через третий мас штабный резистор подключен к его инвертирующему входу и является выходом устройства, инвертирующий вход операционного усилителя через четвертый масштабный резистор подключен к первому входу устройства, вторые выводы третьего и четвертого балансировочных резисторов объединены и являются вторым входом устройства, вторые выводы первого и второго балансировочных резисторов объединены и подключены к среднему выводу первого подстроечного потенциометра, первый крайний вывод которого подключен к шине нулевого потенциала, затвори первого и третьего управляемых полевых транзисторов соответственно подключены к средним выводам второго и трютьего подстроечных потенциометров, первые крайние Быводы которых объединены и подключены к шине нулевого потенциала, а вторые крайние вывода второго и третьего подстроечных потенциометров объединены и подключены к выходу источника стабильного сигнгша, затворы второго

И четвертого управляемых полевых тра зисторов объединены и подключены к выходу первого операционного усилителя, отличающееся тем, что, с целью повышения точности, в него введены два пороговвлх блока, элемент И, сумматор, четвертый, пятый и шестой подстроечные потенциометры и источник опорного сигнала, входы первого и второго пороговых блоков соответственно подключены к первому и второму входам устройства, выходы пороговых блоков подклю.чены соответственно к первому и второму входам элемента И и к первым крайним выводгии четвертого и пятого подстроечных потенциометров,.вторые крайние выводы которых подключены к шине нулевого потенциала, выход 1элемента И подключен к первому крайнему выводу шестого подстрюемного потенциометра, второй крайний вывод которого подключен к шине нулевого потенциала, первый вход сумматора подключен к выходу источника опорного сигнала, второй, третий и четвертый входы сумматора подключены к средним выводам соответственно четвертого, пятого и шестого подстроечньЛ потенциометров, выход сумматора подключен к второму крайнему выводу первого подстроечного потенциометра.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-04-30—Публикация

1980-07-21—Подача