Изобретение относится к вычислительной технике и может быть использовано в области управления, связи и обработки сигналов.

Известен способ представления и обработки цифровой информации в системе с троичным основанием, в которой используются троичные весовые коэффициенты разрядов 30, 31, 32 и три возможных логических уровня цифрового сигнала 1, 0 и -1 в каждом из разрядов (Поспелов Д. А. Арифметические основы вычислительных машин дискретного действия. М. Высшая школа, 1970, с. 156-163).

Однако практическая реализация этих преимуществ затруднена в связи с отсутствием надежных и быстродействующих элементов с тремя устойчивыми состояниями.

Наиболее близким к изобретению является способ суммирования двоичных цифровых сигналов (R. H. S. Riordans and R. R. A. Morton. The Use of Analog Techniques in Binari Arithmetic Units. "IEEE Transactions on Electronic Computers", 1965, v. ЕS-14, N 1, р. 29-35), включающий одновременное преобразование с помощью первой группы ключей каждого цифрового сигнала в каждом i-м разряде, где i= 1.n, в n нормированных по уровню аналоговых сигналов, одновременное во всех n разрядах поразрядное суммирование нормированных по уровню аналоговых сигналов совместно с нормированными по уровню аналоговыми сигналами переноса из младших по весу по отношению к каждому i-му разрядов (i-1), (i-2), (i-k), где k число сигналов переноса в каждом разряде, а также одновременное выделение из суммарного аналогового сигнала в каждом i-ом разряде нормированных по уровню выходного аналогового сигнала и k аналоговых сигналов переноса в последующие старшие по весу (i+1), (i+2),(i+k)-й разряды с помощью второй группы ключей и аналоговых сумматоров в соответствии с правилами перевода десятичных натуральных чисел в цифровой код.

В известном способе на всех этапах преобразования цифровых сигналов используются двухпозиционные ключи, что позволяет производить преобразования только двоичных цифровых сигналов.

Недостатком этого способа является ограниченное быстродействие, обусловленное невозможностью работы с троичными цифровыми сигналами. Троичная система по сравнению с двоичной имеет меньшее число разрядов и меньшее количество сигналов переноса при равных объемах цифровой информации, откуда вытекает более высокое быстродействие при аналоговых преобразованиях цифровых сигналов.

Задача изобретения усовершенствование способа суммирования цифровых сигналов, в котором новое преобразование входных цифровых сигналов, представленных в троичном коде, в нормированные по уровню аналоговые сигналы позволило уменьшить число разрядов при аналоговом суммировании нормированных по уровню сигналов и количество нормированных по уровню сигналов переноса в процессе получения результата, а также повышение быстродействия способа.

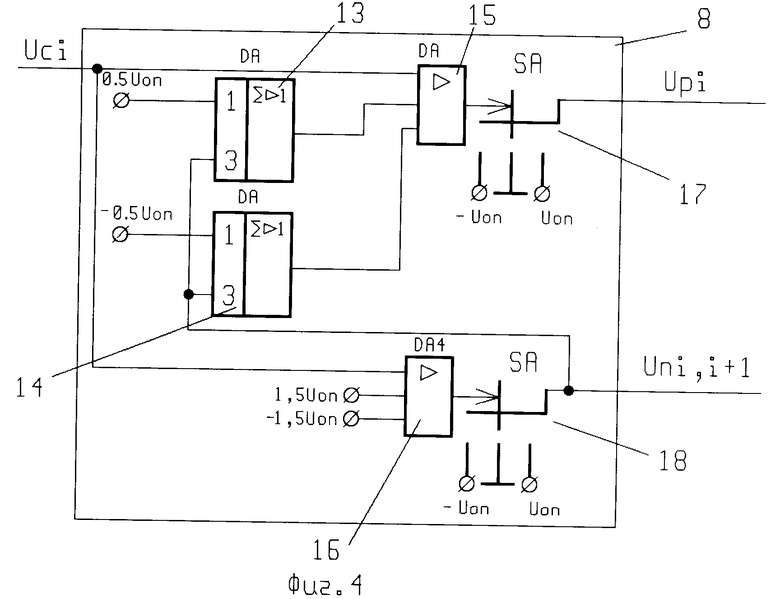

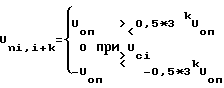

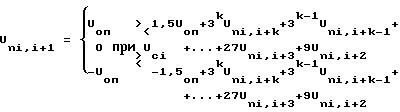

Для этого в способе суммирования цифровых сигналов разрядности n, включающем одновременное преобразование с помощью первой группы ключей каждого цифрового сигнала в каждом i-м разряде, где i=1.n, в n нормированных по уровню аналоговых сигналов, одновременное во всех n разрядах поразрядное суммирование нормированных по уровню аналоговых сигналов совместно с нормированными по уровню аналоговыми сигналами переноса из младших по весу по отношению к каждому i-му разрядов (i-1), (i-2),(i-k), где k число сигналов переноса в каждом разряде, а также одновременное выделение из суммарного аналогового сигнала в каждом i-ом разряде нормированных по уровню выходного аналогового сигнала и k аналоговых сигналов переноса в последующие старшие по весу (i+1), (i+2), (i+k)-й разряды с помощью второй группы ключей и аналоговых сумматоров в соответствии с правилами перевода десятичных натуральных чисел в цифровой код, согласовано изобретению преобразование цифровых сигналов, представленных в троичном коде, осуществляют с помощью первой группы ключей, выполненных трехпозиционными и формирующих на выходах аналоговые сигналы, принимающие в зависимости от логического уровня цифрового сигнала в данном i-м разряде один из трех нормированных уровней, равных нулю при логическом нуле, положительному опорному сигналу при логической единице и отрицательному опорному сигналу при отрицательной логической единице, выделение из суммарного аналогового сигнала в каждом i-м разряде нормированных по уровню выходного аналогового сигнала и сигналов переноса в последующие старшие по весу разряды осуществляют с помощью трехпозиционных ключей, образующих вторую группу, и аналоговых сумматоров в соответствии с правилами перевода десятичных натуральных чисел в троичный цифровой код, при этом пороги переключений ключей в каждом i-м разряде формируют как средние арифметические значения между соседними дискретными уровнями суммарного аналогового сигнала в соответствии со следующими выражениями:

где n число разрядов троичного цифрового сигнала;

i номер разряда (i= 1.n; i=1 самый младший по весу разряд; i=n самый старший по весу разряд);

k число сигналов переноса из каждого i-го разряда в последующие старшие по весу разряды;

Uоп опорный сигнал;

Uci суммарный дискретный по уровню аналоговый сигнал в i-м разряде;

Upi нормированный по уровню выходной аналоговый сигнал в i-м разряде;

Uпi, i+1 нормированный по уровню аналоговый сигнал переноса из i-го разряда в (i+1)-й разряд;

Uпi, i+2 нормированный по уровню аналоговый сигнал переноса из i-го разряда в (i+2)-й разряд;

Uпi, i+k-1 нормированный по уровню аналоговый сигнал переноса из i-го разряда в (i+k-1)-й разряд;

Uпi, i+k нормированный по уровню аналоговый сигнал переноса из i-го разряда в (i+k)-й разряд.

Сущностью предлагаемого способа является наличие преобразования каждого входного цифрового сигнала, представленного в троичном коде, в совокупность нормированных по уровню аналоговых сигналов, отражающих структуру троичного цифрового сигнала, что позволяет далее осуществить аналоговую обработку полученных совокупностей нормированных по уровню аналоговых сигналов и реализовать преимущество в быстродействии, присущее троичной системе. Это преимущество вытекает из того, что троичная система по сравнению с двоичной при равных объемах цифровой информации имеет меньшее число разрядов и меньшее число сигналов переноса.

Предложенный способ описывается на примере устройства суммирования трех n-разрядных троичных цифровых сигналов. Число суммируемых сигналов, равное трем, выбрано с целью наглядного описания работы устройства, так как здесь в соответствии с выражениями (1) достаточно ограничиться одним (k=1) сигналом переноса в следующий старший по весу разряд, при этом максимальный абсолютный уровень суммарного сигнала в любом разряде не превышает 4Uоп.

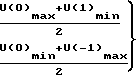

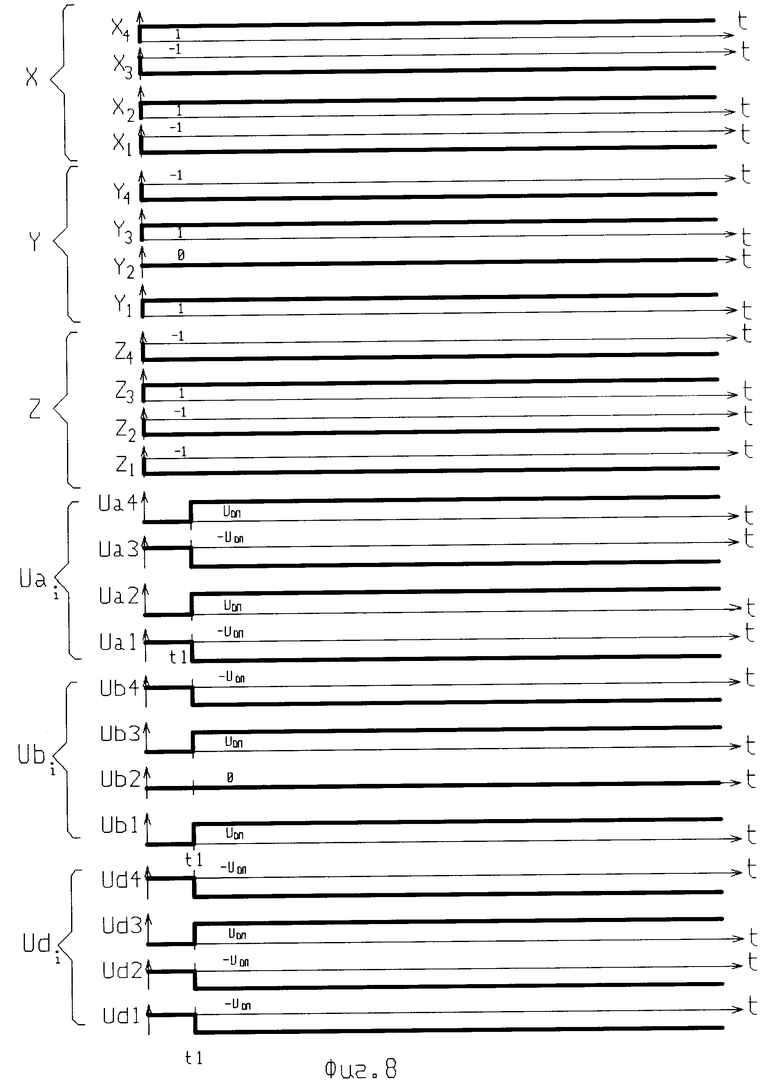

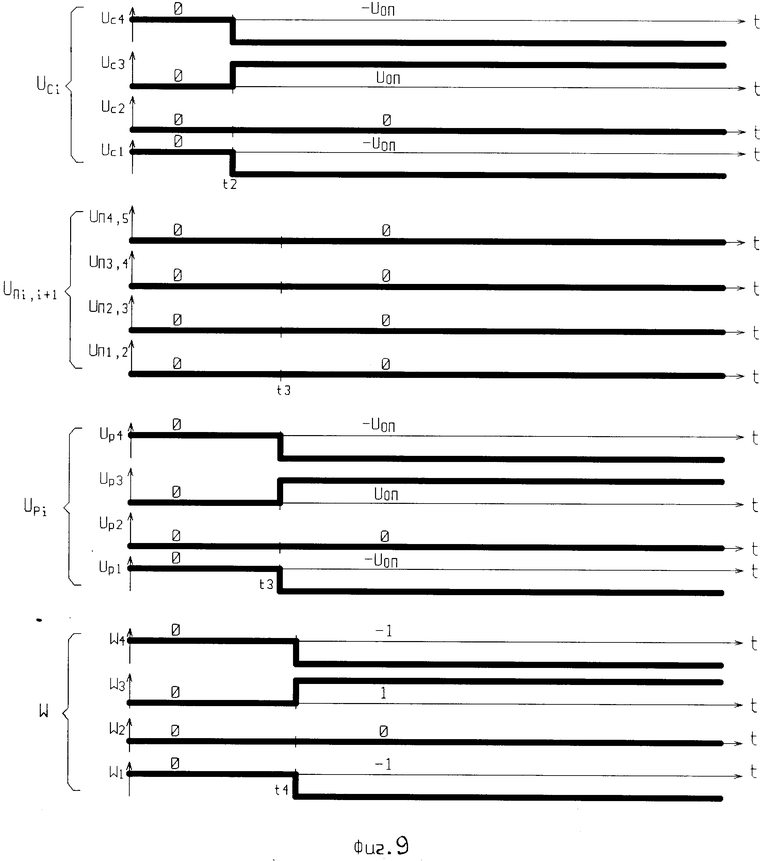

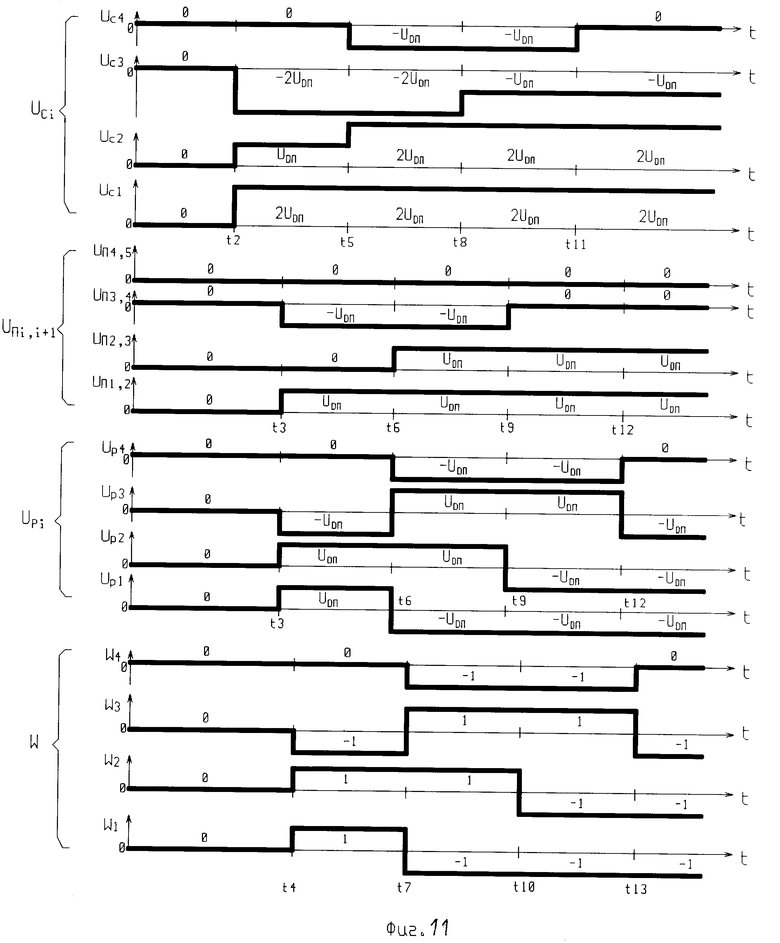

На фиг. 1 представлена функциональная схема устройства суммирования трех троичных цифровых сигналов; на фиг. 2 функциональная схема трехпозиционного ключа первой группы; на фиг. 3 характеристика вход-выход трехпозиционного ключа первой группы; на фиг. 4 функциональная схема трехпозиционного ключа второй группы; на фиг. 5 а и б характеристики входы-выходы трехпозиционного ключа второй группы выходного сигнала в i-й разряд и сигнала переноса в (i+1)-й разряд соответственно; на фиг. 6 функциональная схема выходного каскада; на фиг. 7 характеристика вход-выход выходного каскада; на фиг. 8 и 9- временные диаграммы сигналов 4-разрядного устройства при суммировании троичных цифровых сигналов х=1-1 1-1, Y=-1 1 0 1 и Z=-1 1-1-1; на фиг. 10 и 11 временные диаграммы сигналов 4-разрядного устройства при суммировании троичных цифровых сигналов Х=-1 0-1 1, Y=1-1 1 1 и Z=0-1 1 0.

Функциональная схема устройства суммирования трех n-разрядных цифровых сигналов показана на фиг. 1. Устройство включает блоки 1-3, содержащие первую группу трехпозиционных ключей 4, общее число которых равно 3n, служащих для одновременного преобразования каждого цифрового сигнала в каждом i-м разряде, где i=1.n, в n нормированных по уровню аналоговых сигналов, блок 5, состоящий из n аналоговых сумматоров 6, служащих для одновременного во всех n разрядах поразрядного суммирования нормированных по уровню аналоговых сигналов совместно с нормированными по уровню аналоговыми сигналами переноса из младших по весу по отношению к каждому i-му разрядов (i-1), (i-2),(i-k), где k число сигналов переноса в каждом разряде (в данном случае k=1, что соответствует одному сигналу переноса из предыдущего младшего по весу (i-1)-го разряда), блок 7, содержащий, вторую группу трехпозиционных ключей 8, число которых равно n, предназначенных для одновременного выделения из суммарного аналогового сигнала в каждом i-ом разряде нормированных по уровню выходного аналогового сигнала и k аналоговых сигналов переноса в последующие старшие по весу (i+1), (i+2),(i+k)-й разряды (в данном случае k=1, что соответствует выделению одного сигнала переноса в последующий старший по весу (i+1)-й разряд).

В случае несоответствия нормированных уровней выходных аналоговых сигналов в разрядах стандартным электрическим уровням троичного цифрового сигнала в устройство дополнительно вводится блок 9, содержащий n выходных каскадов 10, служащих для согласования уровней указанных сигналов.

На входы первой группы трехпозиционных ключей 4 блоков 1-3 поразрядно подают цифровые сигналы Х, Y и Z, логические уровни которых хi, yi и zi в каждом из разрядов i=1.n принимают одно из трех значений -1, 0 и 1, а соответствующие уровни электрических сигналов Uxi, Uyi и Uzi принимают одно из значений U(-1), U(0) и U(1). Выходы трехпозиционных ключей 4 блока 1 (сигналы Ua1.Uan) соединены поразрядно с первыми входами аналоговых сумматоров 6 блока 5, выходы трехпозиционных ключей 4 блока 2 (сигналы Ub1.Ubn) соединены поразрядно с вторыми входами аналоговых сумматоров 6 блока 5, выходы трехпозиционных ключей 4 блока 3 (сигналы Ud1.Udn) соединены поразрядно с третьими входами аналоговых сумматоров 6 блока 5. Выходы аналоговых сумматоров 6 блока 5 (сигналы Uc1.Ucn) поразрядно связаны с входами трехпозиционных ключей 8 блока 7. Когда нормированные уровни выходных аналоговых сигналов разрядов Uр1.Upn на первых выходах трехпозиционных ключей 8 блока 7, равные нулю, Uоп или -Uоп, соответствуют стандартным уровням троичного цифрового сигнала, указанные выходные сигналы блока 7 могут непосредственно использоваться для дальнейшей цифровой обработки. В случае несоответствия этих уровней необходимо преобразование выходных аналоговых сигналов разрядов Up1.Upn блока 7 в стандартные уровни троичного цифрового сигнала с помощью блока 9 выходных каскадов 10. При этом первые выходы (выходы сигналов разрядов Up1. Upn) трехпозиционных ключей 8 блока 7 поразрядно соединяются с входами выходных каскадов 10 блока 9. Вторые выходы (выходы сигналов переноса Uп1, 2.Uпn-1, n) трехпозиционных ключей 8 блока 7 по цепной схеме, соответствующей выражениям (1), соединены с четвертыми входами аналоговых сумматоров 6 блока 5 ближайших старших по весу разрядов, а именно: второй выход ключа 8 в первом (самом младшем по весу) разряде соединен с четвертым входом сумматора 6 во втором разряде, второй выход ключа 8 во втором разряде соединен с четвертым входом сумматора 6 в третьем разряде и т.д. При этом второй выход ключа 8 в n-ом (самом старшем по весу) разряде не используется в работе устройства, но появление сигнала на этом выходе, свидетельствующее о переполнении разрядной сетки, может служить командой для аварийного останова. Четвертый вход сумматора 6 в первом (самом младшем по весу) разряде соединен с нулевым потенциалом.

На выходах блока 9 выходных каскадов 10 получают результирующий выходной цифровой сигнал W, логические уровни которого wi принимают в каждом из n разрядов одно из значений -1, 0, 1, а соответствующие уровни электрических сигналов Uwi принимают одно из значений U(-1), U(0), U(1). Когда нормированные уровни аналоговых сигналов на первых выходах трехпозиционных ключей 8 блока 7, равные -Uоп, 0, Uоп, соответствуют стандартным уровням троичного цифрового сигнала U(-1), U(0), U(1), указанные нормированные по уровню аналоговые сигналы могут непосредственно использоваться для дальнейшей цифровой обработки. В этом случае устройство может быть выполнено без блока 9 выходных каскадов 10.

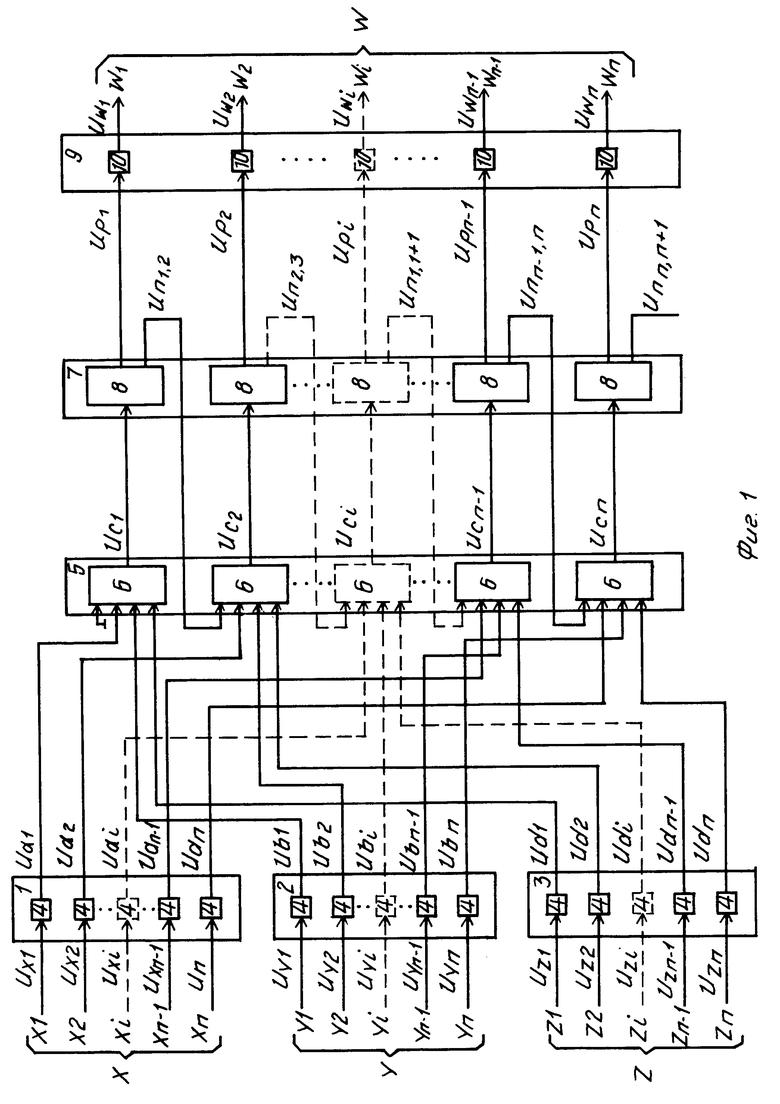

Тpехпозиционные ключи 4 блоков 1-3, образующие первую группу ключей, в каждом разряде каждого входного цифрового сигнала (фиг. 2) включают в себя трехпозиционный компаратор 11, формирующий сигнал управления, и собственно электронный ключ 12. Первый вход компаратора 11 является входом трехпозиционного ключа 4, а второй и третий входы компаратора 11 соединены соответственно с источниками сигналов смещения Uсм1 и Uсм2. Выход компаратора 11 соединен с управляющим входом ключа 12, три коммутируемых входа которого соединены соответственно с нулевым потенциалом и с источниками положительного опорного сигнала Uоп и отрицательного опорного сигнала -Uоп. Выход ключа 12 является выходом трехпозиционного ключа 4 первой группы.

Уровни сигналов смещения Uсм1 и Uсм2 на втором и третьем входах компаратора 11 достаточно выбрать такими, чтобы они занимали промежуточные положения между электрическими уровнями цифровых сигналов U(0), U(1) и U(-1), соответствующими логическому нулю, логической единице и отрицательной логической единице (фиг. 3):

Поскольку в цифровых системах допускается определенная нестабильность электрических уровней сигналов U(0), U(1) и U(-1), то наиболее целесообразно выбирать уровни сигналов смещения Uсм1 и Uсм2 из соотношений

,

,

где U(0)max возможный максимальный электрический уровень цифрового сигнала, соответствующий логическому нулю;

U(1)min возможный минимальный электрический уровень цифрового сигнала, соответствующий логической единице;

U(0)min возможный минимальный электрический уровень цифрового сигнала, соответствующий логическому нулю;

U(-1)max возможный максимальный электрический уровень цифрового сигнала, соответствующий отрицательной логической единице.

Такой выбор уровней сигналов смещения Uсм1 и Uсм2 позволяет надежно различать уровни цифрового сигнала в каждом из разрядов с помощью компаратора 11.

Сумматоры 6 блока 5 (фиг. 1) в каждом разряде i=1.n представляют собой аналоговый сумматор электрических сигналов с четырьмя входами, одним выходом и с единичными коэффициентами передачи по каждому из входов.

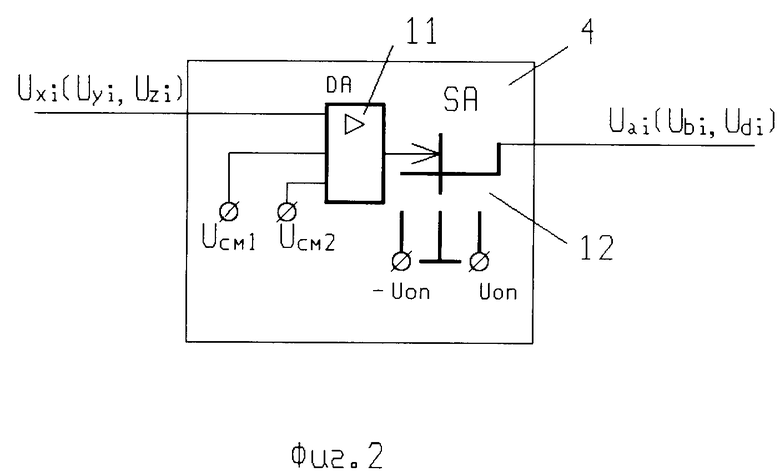

Трехпозиционные ключи 8 блока 7, образующие вторую группу ключей, в каждом разряде (фиг. 4) содержат два аналоговых сумматора 13 и 14, два трехпозиционных компаратора 15 и 16, формирующих сигналы управления, и два электронных ключа 17 и 18. Объединенные первые входы компараторов 15 и 16 являются входом трехпозиционного ключа 8 блока 7. Второй и третий входы компаратора 15 соединены соответственно с выходами аналоговых сумматоров 13 и 14. Второй и третий входы компаратора 16 подключены соответственно к источникам сигналов уровней 1,5 Uоп и -1,5 Uоп. Выходы компараторов 15 и 16 соединены соответственно с управляющими входами ключей 17 и 18, а три коммутируемых входа каждого из ключей 17 и 18 соединены соответственно с нулевым потенциалом, с источником положительного опорного сигнала Uоп и с источником отрицательного опорного сигнала -Uоп. Выход ключа 17 является первым выходом (выходом сигнала данного разряда) трехпозиционного ключа 8 блока 7, а выход ключа 18 является вторым выходом (выходом сигнала переноса) трехпозиционного ключа 8 блока 7. Первые входы аналоговых сумматоров 13 и 14, имеющие единичные коэффициенты передачи, соединены соответственно с источниками сигналов уровней 0,5 Uоп и -0,5 Uоп. Вторые входы аналоговых сумматоров 13 и 14, имеющие коэффициенты передачи, равные трем, соединены с выходом ключа 18. Уровни ± 0,5 Uоп и ±1,5 Uоп являются соответственно средними арифметическими значений 0. ±Uоп и ±Uоп.± 2Uоп, что позволяет с помощью компараторов 15 и 16 надежно различать дискретные уровни входных сигналов, равные 0, ±Uоп, ±2Uоп, ±3Uоп и ±4Uоп (фиг. 5).

Выходные каскады 10 блока 9 являются известными аналоговыми устройствами согласования уровней электрических сигналов, например трехпозиционными ключами. Выходной каскад 10 в каждом разряде (фиг. 6) включает в себя трехпозиционный компаратор 19, формирующий сигнал управления, и трехпозиционный электронный ключ 20. Первый вход компаратора 19 является входом выходного каскада 10, а второй и третий входы компаратора 19 соединены соответственно с источниками сигналов уровней 0,5 Uоп и -0,5 Uоп, являющихся средними арифметическими значений 0 и ± Uоп (фиг. 7). Выход компаратора 19 соединен с управляющим входом ключа 20, три коммутируемых входа которого соединены с источниками сигналов уровней U(0), U(1) и U(-1), соответствующих стандартным уровням логического нуля, логической единицы и отрицательной логической единицы троичного цифрового сигнала. Выход ключа 20 является выходом выходного каскада 10 в каждом разряде блока 9.

Суммирование трех n-разрядных цифровых сигналов в устройстве суммирования, показанном на фиг. 1, осуществляется следующим образом.

Каждый из троичных цифровых сигналов Х, Y и Z, имеющий логические уровни сигналов -1, 0, 1, одновременно преобразуют с помощью первой группы трехпозиционных ключей 4 блоков 1-3 в каждом i-м разряде, где i=1.n, в n нормированных по уровню аналоговых сигналов Uai, Ubi, Udi. При этом преобразование цифровых сигналов, представленных в троичном коде, осуществляют таким образом, что на выходах трехпозиционных ключей 4 формируют аналоговые сигналы, принимающие в зависимости от логического уровня цифрового сигнала в данном i-м разряде один из трех нормированных уровней, а именно равных нулю при логическом нуле, положительному опорному сигналу Uоп при логической единице и отрицательному опорному сигналу -Uоп при отрицательной логической единице. При подаче на вход трехпозиционного ключа 4 (фиг. 2) сигнала U(0), соответствующего логическому нулю, управляемый компаратором 11 электронный ключ 12 будет подключен к нулевому потенциалу, при подаче сигнала U(1), соответствующего логической единице, ключ 12 будет подключен к источнику положительного опорного сигнала Uоп, а при подаче сигнала U(-1), соответствующего отрицательной логической единице, ключ 12 будет подключен к источнику отрицательного опорного сигнала -Uоп. Таким образом, трехпозиционные ключи 4 блоков 1-3 в каждом разряде каждого из цифровых сигналов реализуют релейную характеристику вход-выход трехпозиционного ключа, как показано на фиг. 3, давая на выходе аналоговый сигнал одного из трех нормированных уровней 0, Uоп или -Uоп.

Далее одновременно во всех n разрядах производят поразрядное суммирование нормированных по уровню аналоговых сигналов Uai, Ubi, Udi совместно с нормированными по уровню аналоговыми сигналами переноса из младших по весу по отношению к каждому i-му разрядов (i-1), (i-2),(i-k), где k число сигналов переноса в каждом разряде. В соответствии с выражениями (1) при суммировании трех цифровых сигналов достаточно одного сигнала переноса (k=1) из предыдущего младшего по весу разряда (i-1). Суммирование производят с помощью n аналоговых сумматоров 6 блока 5 (фиг. 1), для этого на первый, второй и третий входы каждого из сумматоров 6 подают аналоговые сигналы Uai, Ubi, Udi с выходов первой группы трехпозиционных ключей 4 соответствующих блоков 1-3 из одновременных разрядов, а на четвертый вход каждого из сумматоров 6, находящихся в разрядах i=2.n, подают аналоговый сигнал переноса Uni,i+1 с второго выхода трехпозиционного ключа 8 блока 7 ближайшего младшего по весу (i-1)-го разряда. Сигнал переноса в самый младший по весу разряд i=1 отсутствует, поэтому на четвертый вход сумматора 6, находящегося в первом разряде, подают нулевой потенциал.

Так как все поступающие на входы каждого сумматора 6 блока 5 аналоговые сигналы нормированы по уровню, те. каждый из сигналов может иметь либо нулевое значение, либо значение положительного опорного сигнала Uоп, либо значение отрицательного опорного сигнала -Uоп, то суммарные сигналы Uci на выходах аналоговых сумматоров 6 блока 5 могут иметь только дискретные уровни: нулевой уровень, положительный или отрицательный уровень опорного сигнала ±Uоп, уровень± 2 Uоп, уровень ±3 Uоп и максимально возможный уровень ±4 Uоп. В первом (самом младшем по весу) разряде сигнал переноса на входе аналогового сумматора 6 отсутствует, поэтому максимально возможный уровень сигнала на выходе аналогового сумматора первого разряда равен ±3 Uоп.

Далее с помощью второй группы трехпозиционных ключей 8 блока 7 (фиг. 1) и аналоговых сумматоров 13 и 14, входящих в состав ключей 8 (фиг. 4), производят одновременное выделение из суммарного аналогового сигнала Uci в каждом i-м разряде нормированных по уровню выходного аналогового сигнала Upi и k аналоговых сигналов переноса в последующие старшие по весу разряды (i+1), (i+2), (i+k). В данном случае k=1, что соответствует одному аналоговому сигналу Uпi, i+1 переноса из i-го разряда в следующий старший по весу (i+1)-й разряд.

Выделение из суммарного аналогового сигнала Uсi в каждом i-м разряде нормированных по уровню выходного аналогового сигнала Upi и сигналов переноса в последующие старшие по весу разряды (в данном случае для k=1 одного аналогового сигнала Uпi, i+1 переноса в следующий старший по весу разряд), осуществляемое с помощью второй группы трехпозиционных ключей 8 блока 7 и входящих в их состав аналоговых сумматоров 13 и 14, производят в соответствии с правилами перевода десятичных натуральных чисел в троичный цифровой код. При этом пороги переключений ключей в каждом i-м разряде формируют как средние арифметические значения между соседними дискретными уровнями суммарного аналогового сигнала Uci в соответствии с выражениями (1), которые для k=1 представлены в таблице соответствий.

Трехпозиционные ключи 8 блока 7 (фиг. 1 и 4), образующие третью группу, имеют релейный характер зависимостей уровней выходного сигнала данного разряда и сигнала переноса в следующий старший по весу разряд (фиг. 5) и работают следующим образом. При нулевом входном сигнале Uci=0 на вторые и третьи входы компараторов 15 и 16 поступают сигналы, соответственно равные ± 0,5 Uоп и ±1,5 Uоп, поэтому ключи 17 и 18 оказываются подключенными к нулевому потенциалу, и выходные сигналы трехпозиционного ключа 8 равны нулю. При входном сигнале, равном опорному Uсi=Uоп, управляемый компаратором 15 ключ 17 переключается в положение, при котором выходной сигнал данного разряда становится равным опорному Upi= Uоп, тогда как ключ 18 остается в прежнем положении, и сигнал переноса по-прежнему равен нулю. При входном сигнале Uci= 2Uоп с помощью компаратора 16 происходит переключение ключа 18 в положение, при котором сигнал переноса становится равным опорному Uпi, i+1=Uоп. Одновременно этот сигнал поступает на вторые входы сумматоров 13 и 14, поэтому выходные сигналы сумматоров 13 и 14 соответственно становятся равными 3,5 Uоп и 2,5 Uоп, и ключ 17 переключается в положение, при котором Upi=-Uоп. При входном сигнале Uci=3 Uоп ключ 18 продолжает оставаться в положении контакта с источником сигнала Uоп, поэтому сигнал переноса Uпi, i+1=Uоп, а ключ 17 возвращается в нулевое положение, и выходной сигнал данного разряда Upi= 0. При максимальном входном сигнале Uci=4Uоп сигнал переноса на выходе ключа 18 по-прежнему равен опорному сигналу Uпi, i+1=Uоп, а ключ 17 также подключается к источнику опорного сигнала, поэтому выходной сигнал разряда Upi= Uоп. Таким же образом происходят переключения ключей 17 и 18 при отрицательных дискретных значениях входного сигнала Uci, равных -Uоп, -2 Uоп, -3 Uоп и -4 Uоп.

Таким образом, переключения ключа 17 происходят при восьми пороговых уровнях входного сигнала ±0,5 Uоп, ±1,5 Uоп, ±2,5 Uоп и ±3,5 Uоп, а переключения ключа 18 при двух пороговых уровнях ±1,5 Uоп. Эти пороговые уровни максимально удалены от дискретных значений входного сигнала 0, ±Uоп, ±2Uоп, ± 3Uоп и ± 4Uоп, которые отмечены точками на фиг. 5. Дискретные уровни выходных сигналов разряда Upi и переноса Uпi,i+1 трехпозиционного ключа 8 третьей группы соответствуют значениям таблицы.

Преобразование аналогового результата в виде n выходных нормированных по уровню аналоговых сигналов Upi в n-разрядный троичный цифровой сигнал W осуществляют одновременно во всех разрядах i=1.n с помощью устройств согласования уровней электрических сигналов, например трехпозиционных ключей 20, реализованных в блоке 9 выходных каскадов 10 (фиг. 1 и 6). При этом в каждом из разрядов нулевому уровню аналогового сигнала Upi присваивают значение логического нуля цифрового сигнала, уровню аналогового сигнала Upi, равному опорному сигналу Uоп, присваивают значение логической единицы цифрового сигнала, и уровню аналогового сигнала Upi, равному отрицательному опорному сигналу -Uоп, присваивают значение отрицательной логической единицы цифрового сигнала. При подаче на вход каждого выходного каскада 10 блока 9 нормированного по уровню аналогового сигнала Upi из соответствующего разряда i=1.n блока 7 с выхода ключа 8 управляемый компаратором 19 ключ 20 будет переключаться в одно из трех положений, и выходной сигнал Uwi будет принимать один из трех стандартных электрических уровней цифровых сигналов, а именно уровень U(0), соответствующий логическому нулю, при входном сигнале Upi=0, уровень U(1), соответствующий логической единице, при Upi=Uоп и уровень U(-1), соответствующий отрицательной логической единице, при Upi=-Uоп. Таким образом, выходной каскад 10 блока 9 в каждом из разрядов реализует релейную характеристику вход-выход трехпозиционного ключа (фиг. 7), давая на выходе цифровой сигнал W стандартных уровней логического нуля, логической единицы и отрицательной логической единицы.

Процесс суммирования трех троичных цифровых сигналов иллюстрируют фиг. 8-11, где показаны изменения во времени всех сигналов на входах и выходах узлов функциональной схемы устройства (фиг. 1) в процессе их преобразований для случая 4-разрядных (n=4, i=1.4) цифровых сигналов. На фиг. 8-11 приняты следующие обозначения:

Х цифровой сигнал на входах трехпозиционных ключей 4 первой группы, находящихся в блоке 1, х1.х4 логические уровни сигнала Х в разрядах i=1.4;

Y цифровой сигнал на входах трехпозиционных ключей 4 первой группы, находящихся в блоке 2, Y1.Y4 логические уровни сигнала Y в разрядах i=1.4;

Z цифровой сигнал на входах трехпозиционных ключей 4 первой группы, находящихся в блоке 3, z1.z4 логические уровни сигнала Z в разрядах i=1.4;

Uai совокупность 4-х нормированных по уровню аналоговых сигналов Ua1.Ua4 на выходах ключей 4 блока 1;

Ubi совокупность 4-х нормированных по уровню аналоговых сигналов Ub1.Ub4 на выходах ключей 4 блока 2;

Udi совокупность 4-х нормированных по уровню аналоговых сигналов Ud1.Ud4 на выходах ключей 4 блока 3;

Uci совокупность 4-х дискретных по уровню аналоговых сигналов Uc1.Uc4 на выходах аналоговых сумматоров 6 блока 5;

Uпi,i+1 совокупность 4-х нормированных по уровню аналоговых сигналов переноса Uп1,2.Uп4,5 на вторых выходах трехпозиционных ключей 8 блока 7;

Upi совокупность 4-х нормированных по уровню аналоговых выходных сигналов Up1.Up4 в разрядах i=1.4 на первых выходах трехпозиционных ключей 8 блока 7;

W цифровой сигнал на выходах выходных каскадов 10 блока 9.

W1.W4 логические уровни сигнала W в разрядах i=1.4.

Для упрощения и наглядности временных диаграмм переходные процессы в отдельных узлах устройства рассматриваются как реакции звеньев с чистым запаздыванием со следующими временами: τну время реакции первой группы трехпозиционных ключей 4 в процессе нормализации уровня; τc время реакции аналоговых сумматоров 6, а также аналоговых сумматоров 13 и 14, входящих в состав третьей группы трехпозиционных ключей 8; τнк время реакции компараторов 15 и 16 совместно с ключами 17 и 18, входящих в состав второй группы трехпозиционных ключей 8, в процессе нормализации кода; τвк время реакции выходных каскадов 10.

Временные диаграммы на фиг. 8 и 9 соответствуют случаю максимального быстродействия устройства, когда при суммировании цифровых сигналов отсутствуют сигналы переноса. В данном случае временные диаграммы на фиг. 8 и 9 соответствуют суммированию цифровых сигналов Х=1-1 1-1(3)=20(10), Y=-1 1 0 1(3)= -17(10) и Z=-1 1-1-1(3)=-22(10) c результатом W=X+Y+Z=-1 1 0-1(3)=-19(10).

В момент времени t= 0 цифровые сигналы Х, Y и Z подаются одновременно соответственно на входы блоков 1-3 трехпозиционных ключей 4 первой группы. В момент времени

t1= τну (4)

на выходах первой группы трехпозиционных ключей 4 появляются три совокупности нормированных по уровню аналоговых сигналов Uai, Ubi и Udi, каждая из которых состоит из четырех аналоговых сигналов. Эти сигналы принимают одно из нормированных по уровню значений (0, Uоп, -Uоп) в зависимости от того, каков логический уровень соответствующих цифровых сигналов Х, Y и Z в данном разряде. Поразрядное аналоговое суммирование совокупностей нормированных по уровню аналоговых сигналов Uai, Ubi и Udi с помощью аналоговых сумматоров 6 блока 5 приводит к появлению на выходах аналоговых сумматоров 6 блока 5 совокупности четырех аналоговых сигналов Uci (Uc1=-Uоп, Uс2=0, Uс3=Uоп, Uc4= -Uоп) в момент времени

t2=t1+tc= τну+τc (5)

Эти аналоговые сигналы попадают на входы трехпозиционных ключей 8 блока 7, реакция которых имеет место в момент времени

t3=t2+ τнк=τну+τc+τнк (6)

Поскольку во всех разрядах абсолютные уровни аналоговых сигналов Uсi не превышают значения Uоп, все четыре аналоговых сигнала переноса Uпi,i+1 в старшие разряды имеют нулевой нормированный уровень, т.е. отсутствуют, а совокупность четырех выходных аналоговых сигналов в разрядах Upi повторяет совокупность сигналов Uci.

Реакция выходных каскадов 10 блока 9 на совокупность четырех нормированных по уровню аналоговых сигналов в разрядах Upi наблюдается в момент времени

t4=t3+ τвк=τну+τс+τнк+τвк (7)

Этот момент времени соответствует установлению результирующего выходного цифрового сигнала W=-1 1 0 -1(3)=-19(10), поэтому выражение (7) определяет минимальное полное время задержки устройства

τmin=τну+τс+τнк+τвк (8)

Это время не зависит от числа разрядов, так как цифровые сигналы преобразуются одновременно во всех разрядах, а сигналы переноса из разряда в разряд по цепной схеме отсутствуют.

Временные диаграммы на фиг. 10 и 11 соответствуют другому крайнему случаю, когда сигналы переноса имеют место во всех разрядах, вследствие чего полное время задержки результирующего цифрового сигнала оказывается максимально возможным. На этих временных диаграммах показаны переходные процессы в устройстве при суммировании цифровых сигналов Х=-1 0-1 1(3)=-29(10), Y=1-1 1 1(3)=22(10) и Z=0-1 1 0(3)=-6(10) с конечным результатом W=X+Y+Z=0-1-1-1(3)= -13(10). При суммировании этих сигналов Х, Y и Z начальные этапы диаграмм, соответствующие моментам времени t1, t2, t3 и t4, описываются качественно точно так же, как и диаграммы на фиг. 8, причем соотношения (4)-(7) остаются в силе. Отличие состоит лишь в уровнях сигналов, так как в момент времени t2 аналоговые сигналы Uci на выходах аналоговых сумматоров 6 блока 5 будут иными, чем на фиг. 8, а именно: Uс1=2Uоп; Uс2=Uоп; Uc3=-2Uоп; Uс4=0. В связи с тем, что в момент t2 на вход трехпозиционных ключей 8 первого и третьего разрядов соответственно поступают сигналы 2Uоп и -2Uоп, в момент t3 на вторых выходах этих ключей 8 появляются нормированные сигналы переноса из первого разряда во второй Uп1,2=Uоп и из третьего разряда в четвертый Uп3,4=-Uоп. Одновременно в этот же момент t3 возникают сигналы в разрядах Upi, которые в момент t4 дают реакцию выходных каскадов W=0-1 1 1. В связи с появлением сигналов переноса этот цифровой сигнал не соответствует окончательному результату и является промежуточным. Возникшие в момент t3 сигналы переноса Uп1,2=Uоп и Uп3,4=-Uоп поступают соответственно на входы аналоговых сумматоров 6 второго и четвертого разрядов, вследствие чего в момент времени

t5= t3+ τc= τну+2τc+τнк (9) сигнал на выходе этих аналоговых сумматоров изменится до значений Uc2=2Uоп, Uc4=-Uоп. Это приведет к реакции трехпозиционных ключей 8 второго и четвертого разрядов в момент времени

t6=t5+ τнк=τну+2τc+2τнк (10) заключающейся в возникновении сигнала переноса Uп2,3=Uоп, поступающего в этот же момент времени t6 на вход аналогового сумматора 6 третьего разряда. Поскольку время реакции сумматоров 13 и 14, входящих в состав трехпозиционных ключей 8, принято равным времени реакции τ с аналогового сумматора 6, в тот же момент времени t6 трехпозиционный ключ первого разряда придет в установившееся положение, соответствующее его входному сигналу Uc1=2Uоп на его входе, а именно сигнал Up1 станет равным -Uоп. Это видно из того, что

t6-t3= τc+τнк (11)

Одновременно в момент времени t6 появится сигнал на первом выходе трехпозиционного ключа 8 четвертого разряда Up4=-Uоп и изменится уровень сигнала в третьем разряде до значения Uр3=Uоп. Соответственно в момент времени

t7= t6+ τвк= τну+2τс+2τнк+τвк (12) изменятся уровни сигналов выходных каскадов 10 первого, третьего и четвертого разрядов и выходной цифровой сигнал устройства станет равным новому промежуточному значению W=-1 1 1-1.

В момент времени

t8= t6+ τc= τну+3τc+2τнк (13) выходной сигнал аналогового сумматора 6 третьего разряда изменится до значения Uc3=-Uоп вследствие реакции на сигнал переноса из второго разряда, а в момент времени

t6=t8+ τнк=τну+3τс+3τнк (14)

последует реакция трехпозиционного ключа 8 третьего разряда, а именно исчезнет сигнал переноса, т.е. Uп3,4=0. Учитывая, что

t9-t6= τc+τнк (15) одновременно с этим в момент времени t9 трехпозиционный ключ 8 второго разряда придет в установившееся состояние, соответствующее его входному сигналу Uс2=2Uоп, т.е. выходной сигнал второго разряда станет равным Uр2=-Uоп. Соответственно в момент времени

t10= t9+ τвк= τну+3τс+3τнк+τвк (16) сигнал выходного каскада 10 второго разряда примет уровень отрицательной логической единицы, а выходной цифровой сигнал станет равным третьему промежуточному значению W=-1 1-1-1.

В момент времени

t11= t9+ τc= τну+4τс+3τнк (17) аналоговый сумматор 6 четвертого разряда прореагирует на исчезновение сигнала переноса из третьего разряда увеличением своего выходного сигнала Uс4 от -Uоп до нуля. Вследствие этого трехпозиционный ключ 8 четвертого разряда прореагирует в момент времени

t12= t11+ τнк=τну+4τс+4τнк (18) увеличением выходного сигнала в разряде Up4 от -Uоп до нуля. Одновременно с этим, учитывая, что

t12-t9= τc+τнк (19) трехпозиционный ключ 8 третьего разряда придет в установившееся положение, соответствующее уровню его входного сигнала Uс3= 2Uоп, а именно выходной сигнал в третьем разряде Uр3 станет равным -Uоп.

В момент времени

t13= t12+ τвк=τну+4τс+4τнк+τвк (20) выходные каскады 10 третьего и четвертого разрядов прореагируют соответственно на изменения сигналов Uр3 и Uр4, в результате чего выходной цифровой сигнал примет окончательное значение W= 0-1-1-1(3)= -13(10), соответствующее результату суммирования цифровых сигналов Х, Y и Z.

Таким образом, максимальное время установления результирующего выходного цифрового сигнала в четырехразрядном устройстве суммирования, реализующем предлагаемый способ, равно

τmax=τну+4(τc+τнк)+τвк (21)

В общем случае n-разрядного устройства суммирования максимальное время установления результата равно

τmax= τну+n(τc+τнк)+τвк (22) и соответствует случаю, когда последовательно изменяются сигналы переноса во всех разрядах.

Если в процессе суммирования цифровых сигналов наблюдается появление сигнала переноса Un, n+1 на втором выходе трехпозиционного ключа 8 самого старшего по весу n-го разряда, то это свидетельствует о переполнении разрядной сетки, и такой сигнал может использоваться для организации аварийного останова.

Реализация предлагаемого способа суммирования n-разрядных троичных цифровых сигналов с помощью устройства, выполненного по функциональной схеме на фиг. 1, приведена для наиболее простого случая суммирования не более трех цифровых сигналов с целью наглядного описания работы устройства. В этом устройстве применены трехпозиционные ключи второй группы с одним (k=1) выходом нормированного по уровню аналогового сигнала переноса в следующий старший по весу разряд. Если применить трехпозиционные ключи второй группы с числом сигналов переноса k>1, то можно одновременно суммировать 4-11 сигналов, при k=3 12-37 сигналов и т.д. что следует из соотношений (1).

Изобретение относится к вычислительной технике. Задачей изобретения является получение возможности суммирования как двоичных (с основанием λ=2 ), так и троичных (с основанием λ=3 ) цифровых сигналов, достижение точности результата, равной точности суммирования цифровых сигналов, и обеспечение быстродействия, свойственного способу обработки и преобразования аналоговых сигналов. Для этого в предложенном способе предусматривается преобразование с помощью λ позиционных ключей каждого входного n-разрядного двоичного или троичного цифровых сигналов, в n нормированных по уровню аналоговых сигналов, принимающих для l=2 и λ=3 значения нуля либо уровня опорного сигнала, и дополнительно для λ=3- отрицательного опорного сигнала, в зависимости от логического уровня цифрового сигнала в данном разряде. При дальнейшей обработке производят одновременное поразрядное аналоговое суммирование n нормированных по уровню аналоговых сигналов и нормированных по уровню аналоговых сигналов переноса из младших по весу разрядов, после чего суммарные аналоговые сигналы преобразуют с помощью λ-позиционных ключей и аналоговых сумматоров путем выделения в каждом разряде i=i.h нормированных по уровню одного выходного аналогового сигнала и k аналоговых сигналов переноса в последующие старшие по весу разряды в соответствии с правилами перевода десятичных натуральных чисел в цифровой код с основанием l. При этом пороги переключений ключей формируют как средние арифметические значения между соседними дискретными уровнями суммарного аналогового сигнала в данном разряде. Если нормированные уровни выходных аналоговых сигналов не соответствуют стандартным уровням цифрового сигнала, то с помощью аналоговых устройств согласования уровней электрических сигналов, например l-позиционных ключей, осуществляют одновременно во всех разрядах i=i.h преобразование h выходных аналоговых сигналов в h=разрядный цифровой сигнал с основанием l3.11 ил. 1 табл.

СПОСОБ СУММИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ разрядности n, включающий одновременное преобразование с помощью первой группы ключей каждого цифрового сигнала в каждом i-м разряде, где i 1.n, в n нормированных по уровню аналоговых сигналов, одновременное во всех n разрядах поразрядное суммирование нормированных по уровню аналоговых сигналов совместно с нормированными по уровню аналоговыми сигналами переноса из младших по весу по отношению к каждому i-му разряду (i 1), (i 2).(i k), где k число сигналов переноса в каждом разряде, а также одновременное выделение из суммарного аналогового сигнала в каждом i-м разряде нормированных по уровню выходного аналогового сигнала и k аналоговых сигналов переноса в последующие старшие по весу (i + 1), (i + 2), (i + k)-й разряды с помощью второй группы ключей и аналоговых сумматоров в соответствии с правилами перевода десятичных натуральных чисел в цифровой код, отличающийся тем, что преобразование цифровых сигналов, представленных в троичном коде, осуществляют с помощью первой группы ключей, выполненных трехпозиционными и формирующих на выходах аналоговые сигналы, принимающие в зависимости от логического уровня цифрового сигнала в данном i-м разряде один из трех нормированных уровней, равных нулю при логическом нуле, положительному опорному сигналу при логической единице и отрицательному опорному сигналу при отрицательной логической единице, выделение из суммарного аналогового сигнала в каждом i-м разряде нормированных по уровню выходного аналогового сигнала и сигналов переноса в последующие старшие по весу разряды осуществляют с помощью трехпозиционных ключей, образующих вторую группу, и аналоговых сумматоров в соответствии с правилами перевода десятичных натуральных чисел в троичный цифровой код, при этом пороги переключений ключей в каждом i-м разряде формируют как средние арифметические значения между соседними дискретными уровнями суммарного аналогового сигнала в соответствии со следующими выражениями:

где n число разрядов троичного цифрового сигнала;

i номер разряда (i 1.n; i 1 самый младший по весу разряд; i n самый старший по весу разряд);

k число сигналов переноса из каждого 1-го разряда в последующие старшие по весу разряды;

Uоп опорный сигнал;

Uci суммарный дискретный по уровню аналоговый сигнал в i-м разряде;

Upi нормированный по уровню выходной аналоговый сигнал в i-м разряде;

Uni,i-1 нормированный по уровню аналоговый сигнал переноса из i-го разряда в (i + 1)-й разряд;

Uni,i+2 нормированный по уровню аналоговый сигнал переноса из i-го разряда в (i + 2)-й разряд;

Uni,i+k-1 нормированный по уровню аналоговый сигнал переноса из i-го разряда в (i + k + 1)-й разряд;

Uni,i+k нормированный по уровню аналоговый сигнал переноса из i-го разряда в (i + k)-й разряд.

| RHS Riordans and R.R.A | |||

| Morton | |||

| The use of Analog Technigues in Binary Arifmetic Units "IEEE Transactions on Electronic Computers, 1965, V.ES -14, N 1, p.29-35. |

Авторы

Даты

1995-12-27—Публикация

1993-07-06—Подача