Изобретение относится к измерительной технике и может быть использовано при построении измерительных систем для очувствления роботов, функционирующих автономно от человека на всех этапах от восприятия до обработки и использования измерительной информации.

Известно устройство для автономных измерений физических величин, содержащее два блока измерительных преобразователей, три коммутатора, два компаратора, инвертор, делитель и блок вычитания.

Недостатком известного устройства является недостаточное быстродействие.

Целью изобретения является повышение быстродействия устройства.

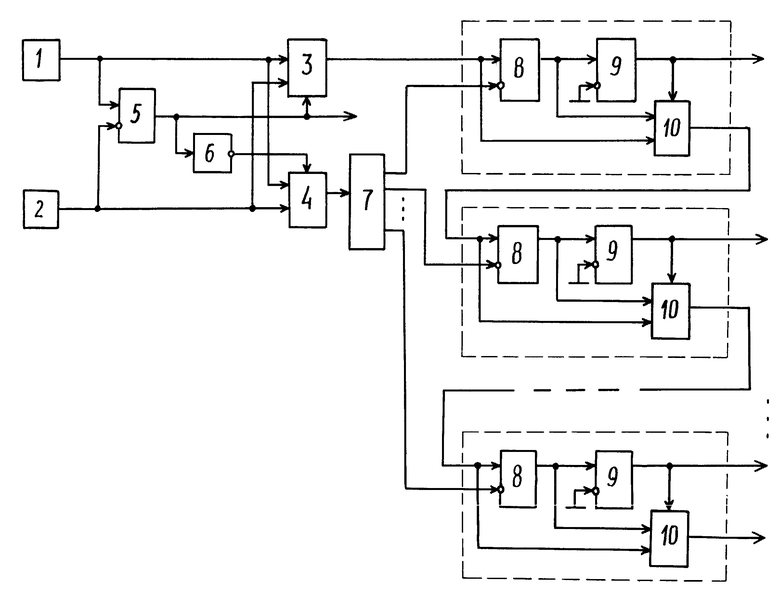

На чертеже показана схема устройства для автономных измерений физических величин.

Устройство содержит два блока 1 и 2 измерительных преобразователей, подключенных соответственно к первым и вторым входам первого 3 и второго 4 коммутаторов, компаратор 5, прямой вход которого подключен к выходу первого блока 1 измерительных преобразователей, а инверсный к выходу второго блока 2 измерительных преобразователей. Выход компаратора 5 подключен напрямую к управляющему входу компаратора 3 и через инвертор 6 к управляющему входу коммутатора 4, выход которого подключен ко входу делителя 7, имеющего N выходов и выполненного в виде резистивной матрицы. Устройство содержит также N групп, каждая включает в себя блок 8 вычитания, компаратор 9 и коммутатор 10, где выход блока 8 вычитания соединен с прямым входом компаратора 9 и первым входом коммутатора 10, со вторым входом которого соединен вход уменьшаемого блока 8 вычитания. Инверсный вход каждого компаратора 9 соединен с нулевой шиной, а выход с управляющим входом коммутатора 10 соответствующей группы. Выход первого коммутатора 3 устройства соединен со входом уменьшаемого блока 8 вычитания первой группы, а входы вычитаемого блока 8 вычитания каждой последующей группы соединены с выходами коммутаторов 10 предшествующей группы. Входы вычитающего блока 8 вычитания каждой группы соединены с соответствующими выходами делителя 7. Выходы компараторов 5, 9 и коммутатора 10 последней группы являются выходами устройства.

Устройство работает следующим образом.

Вследствие работы блоков 1 и 2 измерительных преобразователей на их выходах получаем соответственно значения U1 и U2, несущие информацию об измеряемых величинах, которые характеризуют какое-либо свойство объектов. Значения U1 и U2 с выходов блоков 1 и 2 поступают соответственно на прямой и инверсный входы компаратора 5, который осуществляет операцию их сравнения. При этом его выходной сигнал несет информацию о том, какое из двух значений U1 и U2 измеряемых величин больше (или меньше) по отношению друг к другу. Сигнал с выхода компаратора 5 управляет работой первого и второго коммутаторов 3 и 4. При этом на управляющий вход коммутатора 3 он поступает непосредственно, а на управляющий вход коммутатора 4 через инвертор 6. Если U1<U2, то на выход первого коммутатора 3 с его первого входа подается значение U1, а на выход второго коммутатора 4 с его второго входа подается значение U2. Если U1>U2, на выход первого коммутатора 3 с его второго входа подается значение U2, а на выход второго коммутатора 4 с его первого входа значение U1. Таким образом, на выходе первого коммутатора 3 всегда находится меньшее из двух значений U1 и U2, в то время как на выходе второго коммутатора 4 всегда находится большее из них.

Пусть для определенности U1<U2. Тогда на выходе первого коммутатора 3 будет присутствовать значение U1, а на выходе второго коммутатора 4 значение U2. Последнее поступает на вход делителя 7, который осуществляет N раз деление U1 на основание системы счисления, в которой будет представлен результат измерения, возведенное в соответствующую степень. При двоичной системе счисления на выходах делителя 7 будут присутствовать N значений U2/21, U2/22,U2/2N. Число выходов делителя 7 соответствует числу разрядов представления результата измерения. При этом точность представления результата измерения будет определяться младшим разрядом, вес которого равен U2/2N. Таким образом, чем больше N, тем выше точность измерения и лучше разрешающая способность.

Сигнал U2/2N с первого выхода делителя 7 поступает на вход уменьшающего блока 8 вычитания первой группы элементов 8, 9, 10, на вход уменьшаемого которого поступает сигнал U1. В результате на его выходе получаем сигнал S1= U1-U2/21. Если U1<U2/21, то на выходе (обозначим его а1) компаратора 9 первой группы будет уровень логического нуля. Если U1>U2/21, то на выходе а1 будет уровень логической единицы. Этот сигнал поступает на управляющий вход коммутатора 10 первой группы, на выход которого при а1=0 подается с выхода коммутатора 3 сигнал U1, а при а1=1 с выхода блока 8 вычитания сигнал S1. Сигнал с выхода коммутатора 10 первой группы подается на вход вычитаемого блока 8 вычитания второй группы, на вычитающий вход которого со второго выхода делителя 7 подается сигнал U2/22. Если на вычитаемом входе названного блока 1 вычитания получено значение U1, то на его выходе получаем сигнал S2= U1-U2/22. Если U1<U2/22, то дальнейшая работа второй группы элементов 8, 9, 10 будет аналогична работе первой группы элементов 8, 9, 10, когда выполнялось условие U1<U2/21. Если U1>U2/22, дальнейшая работа второй группы будет аналогична работе первой группы, когда выполнялось условие U1>U2/21. При этом уровень логического нуля или единицы будет зафиксирован на выходе компаратора 9 второй группы, который обозначим а2. Если на вычитаемом входе блока 8 вычитания второй группы получено значение S1, то на его выходе получаем сигнал S2=S1 U2/22. При этом если S1<U2/22, то на выходе компаратора 9 второй группы будет зафиксирован уровень логического нуля, если же S1>U2/22, на выходе названного компаратора будет зафиксирован уровень логической единицы.

Аналогично работают последующие группы элементов 8, 9, 10. При этом на выходе аN компаратора 9 последней N-й группы будет зафиксирован бит информации (нулевой или единичный), соответствующий младшему разряду результата измерения. А на выходе коммутатора 10 данной группы будет представлено значение R абсолютной погрешности измерения.

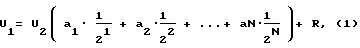

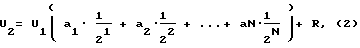

В итоге двоичный код, зафиксированный на выходах компараторов 5, 9, будет соответствовать результату измерения. Дальнейшая обработка может быть выполнена в цифровом виде. Математически результат измерения, связывающий значения U1 и U2, записывается в виде:

если U1<U2,

если U2<U1,

где а1, а2, аN записанные в компараторах 9 биты информации; R - значения абсолютной погрешности.

Информация о представлении результата измерения в виде (1) или (2) записана в компараторе 5.

Данное устройство позволяет повысить быстродействие по сравнению с аналогом [1] в 2N раз, а по сравнению с прототипом [2] в N раз, если суммарное время переходных процессов в группах элементов 8, 9, 10 не превышает периода тактовой частоты их стробирующих генераторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АВТОНОМНЫХ ИЗМЕРЕНИЙ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1992 |

|

RU2047840C1 |

| УСТРОЙСТВО ДЛЯ АВТОНОМНЫХ ИЗМЕРЕНИЙ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1997 |

|

RU2132043C1 |

| УСТРОЙСТВО ДЛЯ АВТОНОМНЫХ ИЗМЕРЕНИЙ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1994 |

|

RU2087869C1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| МНОГОКАНАЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2177637C2 |

| ИНВАРИАНТНЫЙ ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ В ВИДЕ ДЕЛИТЕЛЯ НАПРЯЖЕНИЯ | 1993 |

|

RU2117951C1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182358C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| ЦИФРОВОЙ ПИРОМЕТР СПЕКТРАЛЬНОГО ОТНОШЕНИЯ | 1996 |

|

RU2108554C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1996 |

|

RU2121129C1 |

Использование: в измерительной технике, в частности при построении измерительных систем для очувствления роботов. Сущность изобретения: устройство для автономных измерений физических величин содержит два блока 1 и 2 измерительных преобразователей, подключенных соответственно к первым и вторым входам первого 3 и второго 4 коммутаторов, компаратор 5, прямой вход которого подключен к выходу первого блока 1 измерительных преобразователей, а инверсный - к выходу второго блока 2 измерительных преобразователей. Выход компаратора 5 подключен напрямую к управляющему входу коммутатора 3 и через инвертор 6 - к управляющему входу коммутатора 4, выход которого подключен ко входу делителя 7, имеющего N выходов и выполненного в виде резистивной матрицы. Устройство содержит также N групп, каждая из которых включает в себя блок 8 вычитания, компаратор 9 и коммутатор 10, где выход блока 8 вычитания соединен с прямым входом компаратора 9 и первым входом коммутатора 10, со вторым входом которого соединен вход уменьшаемого блока 8 вычитания. Инверсный вход каждого компаратора 9 соединен с нулевой шиной, а выход - с управляющим входом коммутатора 10 соответствующей группы. Выход первого коммутатора 3 устройства соединен со входом уменьшаемого блока 8 вычитания первой группы, а входы вычитаемого блоков 8 вычитания каждой последующей группы соединен с выходами коммутаторов 10 предшествующей группы. Входы вычитаемого блоков 8 вычитаемого каждой группы соединены с соответствующими выходами делителя 7. Выходы компараторов 5, 9 и коммутатора 10 последней группы являются выходами устройства. 1 ил.

Устройство для автономных измерений физических величин, содержащее два блока измерительных преобразователей, два управляемых коммутатора, компаратор, инвертор, делитель и блок вычитания, где выход первого блока измерительных преобразователей соединен с первыми входами первого и второго коммутаторов и прямым входом компаратора, выход второго блока измерительных преобразователей соединен с вторыми входами первого и второго коммутаторов и инверсным входом компаратора, выход которого является одним из выходов устройства и соединен с управляющим входом одного из названных коммутаторов напрямую, а через инвертор с управляющим входом другого, выход которого соединен с входом делителя, отличающееся тем, что устройство снабжено дополнительными группами из блока вычитания, компаратора и управляемого коммутатора, причем выход блока вычитания в каждой группе соединен с прямым входом компаратора и первым входом коммутатора, с вторым входом которого соединен вход уменьшаемого блока вычитания, инверсные входы компараторов групп соединены с нулевой шиной, а выходы с управляющими входами соответствующих коммутаторов и одновременно являются выходами устройства, выход первого коммутатора устройства соединен с входом уменьшаемого блока вычитания первой группы, входы уменьшаемого блоков вычитания каждой последующей группы соединены с выходами коммутаторов предшествующей группы, входы вычитаемого блоков вычитания каждой группы соединены с соответствующими выходами делителя, который выполнен в виде резистивной матрицы, а выход коммутатора последней группы является выходом для контроля погрешности устройства.

| Авторское свидетельство СССР N 1324521, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1997-10-10—Публикация

1994-04-18—Подача