Изобретение относится к области вычислительной техники и может быть применено в аналоговых вычислительных машинах.

Известно устройство для решения дифференциальных уравнений, содержащее первый и второй интегрирующие операционные усилители, третий операционный усилитель, первый, второй, третий, четвертый и пятый резисторы, причем вход устройства через первый резистор соединен со входом первого интегрирующего операционного усилителя, выход которого через второй резистор соединен с его входом и через третий резистор со входом второго интегрирующего операционного усилителя, выход которого через последовательно соединенные четвертый резистор, третий операционный усилитель и пятый резистор соединен со входом первого интегрирующего операционного усилителя и является выходом устройства [1]

Недостатком данного устройства является его недостаточная точность, обусловленная наличием цепи обратной связи решения дифференциального уравнения по которой ошибки с выхода устройства поступают на его вход.

Наиболее близким к изобретению является устройство для решения дифференциальных уравнений, содержащее первый интегратор, вход которого является информационным входом устройства, фильтр, первый и второй сумматоры, второй интегратор, состоящий из трех операционных усилителей, разделительного конденсатора и шести токозадающих резисторов, первый вывод первого токозадающего резистора соединен с информационным входом устройства, второй вывод первого токозадающего резистора соединен с первыми выходами второго и третьего токозадающих резисторов и подключен к входу первого операционного усилителя, выход которого соединен с вторым выводом второго токозадающего резистора и первым выводом четвертого токозадающего резистора, второй вывод которого соединен с первым выводом пятого токозадающего резистора и через второй операционный усилитель с вторым выводом пятого токозадающего резистора, первым входом первого сумматора и первой обкладкой первого разделительного конденсатора, вторая обкладка которого соединена с первым выводом шестого токозадающего резистора и входом третьего операционного усилителя, выход которого соединен с вторыми выводами шестого и третьего токозадающих резисторов, выход первого интегратора подключен к второму входу первого и первому входу второго сумматоров, выход первого сумматора через фильтр соединен с вторым входом второго сумматора, выход которого является выходом устройства [2]

Недостатком данного устройства является недостаточная точность обусловленная тем, что на входы двух цепей решения дифференциальных уравнений поступают ошибки с их выходов.

Цель изобретения повышение точности решения дифференциальных уравнений.

Указанная цель достигается тем, что в устройство для решения дифференциальных уравнений, содержащее фильтр, первый и второй сумматоры, первый интегратор, состоящий из операционного усилителя, конденсатора обратной связи и двух токозадающих резисторов, второй интегратор, состоящий из трех операционных усилителей, разделительного конденсатора и шести токозадающих резисторов, первый вывод первого токозадающего резистора соединен с информационным входом устройства, второй вывод первого токозадающего резистора соединен с первым выводом второго токозадающего резистора и первой обкладкой первого конденсатора обратной связи и подключен к входу первого операционного усилителя, выход которого соединен со второй обкладкой первого конденсатора обратной связи, первым входом первого сумматора и первым входом второго сумматора, первый вывод третьего токозадающего резистора соединен с информационным входом устройства, второй вывод третьего токозадающего резистора соединен с первыми выводами четвертого и пятого токозадающих резисторов и подключен к входу второго операционного усилителя, выход которого соединен с вторым выводом четвертого токозадающего резистора и первым выводом шестого токозадающего резистора, второй вывод которого соединен с первым выводом седьмого токозадающего резистора и через третий операционный усилитель с вторым выводом седьмого токозадающего резистора и вторым входом первого сумматора, второй вывод пятого токозадающего резистора соединен с первым выводом восьмого токозадающего резистора и выходом четвертого операционного усилителя, вход которого соединен с вторым выводом восьмого резистора и первой обкладкой первого разделительного конденсатора, выход первого сумматора через фильтр соединен с вторым входом второго сумматора, выход которого является выходом устройства, дополнительно введены пятый операционный усилитель, девятый и десятый токозадающие резисторы, причем выход второго сумматора соединен с второй обкладкой первого разделительного конденсатора и первым выводом девятого токозадающего резистора, второй вывод которого соединен с первым выводом десятого токозадающего резистора и через пятый операционный усилитель соединен с вторым выводом десятого токозадающего резистора и вторым выводом второго токозадающего резистора.

Новыми признаками, обладающими существенными отличиями являются:

наличие в схеме устройства дополнительного операционного усилителя и двух токозадающих конденсаторов,

новые связи между известными и новыми признаками.

Данные признаки обладают существенными отличиями, так как в известных технических решениях не обнаружены.

Применение в устройстве всех новых признаков позволяет повысить точность решения дифференциальных уравнений за счет исключения ошибок из сигналов поступающих на выходы цепей решения дифференциального уравнения.

На чертеже изображена принципиальная схема устройства.

Устройство для решения дифференциальных уравнений содержит операционный усилитель 1 с конденсатором 2 обратной связи, операционный усилитель 3 с резистором 4 обратной связи, операционный усилитель 5 с резистором 6 обратной связи, операционный усилитель 7 с резистором 8 обратной связи, операционный усилитель 9 с резистором 10 обратной связи, операционный усилитель 11 с резистором 12 обратной связи и операционный усилитель 13 с резистором 14 обратной связи, конденсаторы 15 и 16, резисторы 17 27. Операционный усилитель 1, конденсатор 2, резисторы 17 и 18 в совокупности составляют интегратор 28, операционный усилитель 9, резисторы 10, 22 и 27 в совокупности составляют сумматор 29, резистор 23 и конденсатор 16 в совокупности составляют фильтр 30, операционный усилитель 11, резисторы 12, 24 и 25 в совокупности составляют сумматор 31, операционные усилители 3, 5 и 7, конденсатор 15 и резисторы 4, 6, 8, 19, 20 и 21 в совокупности составляют схему интегратора 32.

Устройство работает следующим образом.

Устройство предназначено для решения дифференциального уравнения: .

.

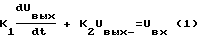

Подаваемый на вход сигнал через первый 18 и третий 19 резисторы одновременно подаются на две независимые параллельные цепи решения дифференциального уравнения. Через шестой резистор 18 входной сигнал Uвх поступает на вход первого операционного усилителя 1. Одновременно на вход первого операционного усилителя 1 через второй резистор 17 с выхода пятого операционного усилителя 13 поступает сигнал решения дифференциального уравнения взятый с противоположным знаком (-Uвых). На первом операционном усилителе 1 с первым конденсатором 2 обратной связи осуществляется интегрирование и инвертирование суммарного сигнала. Сигнал U1 с выхода первого операционного усилителя 1 представляет собой сумму сигнала ошибки решения дифференциального уравнения методом понижения порядка производной и сигнала решения дифференциального уравнения, взятую с противоположным знаком. При интегрировании высокочастотная составляющая ошибки гасится, но происходит усиление низкочастотной составляющей ошибки. Через третий резистор 13 входной сигнал Uвх также поступает на вход второго операционного усилителя 3. Одновременно на вход второго операционного усилителя 3 через пятый резистор 20 поступает сигнал с выхода четвертого операционного усилителя 7. Сигнал на выходе четвертого операционного усилителя представляет собой сигнал производной выходного сигнала взятый с противоположным знаком  , и получается путем дифференцирования и инвертирования выходного сигнала на дифференцирующей цепочке, состоящей из конденсатора 15, четвертого операционного усилителя 7. При дифференцировании низкочастотная составляющая ошибки решения гасится, а высокочастотная составляющая ошибки усиливается. Сигнал на выходе второго операционного усилителя 3 U1 представляет собой инвертированную сумму сигналов

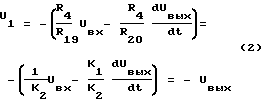

, и получается путем дифференцирования и инвертирования выходного сигнала на дифференцирующей цепочке, состоящей из конденсатора 15, четвертого операционного усилителя 7. При дифференцировании низкочастотная составляющая ошибки решения гасится, а высокочастотная составляющая ошибки усиливается. Сигнал на выходе второго операционного усилителя 3 U1 представляет собой инвертированную сумму сигналов  и Uвх, взятых со своими весовыми коэффициентами. Значение весовых коэффициентов определяется величиной сопротивлений резисторов 4, 19 и 20

и Uвх, взятых со своими весовыми коэффициентами. Значение весовых коэффициентов определяется величиной сопротивлений резисторов 4, 19 и 20

Сигнал с выхода второго операционного усилителя 3 через шестой резистор 21 поступает на вход третьего операционного усилителя 5 с седьмым резистором 6 обратной связи. С выхода третьего операционного усилителя 5 снимается сигнал решения дифференциального уравнения Uвых. Ошибка решения дифференциального уравнения на выходе третьего операционного усилителя 5 носит высокочастотный характер.

Сигнал с выхода первого операционного усилителя 1 через одиннадцатый резистор 27 поступает на вход шестого операционного усилителя 9. На вход шестого операционного усилителя 9 через двенадцатый резистор 22 поступает сигнал с выхода третьего операционного усилителя 5. Сигнал на выходе шестого операционного усилителя 9 представляет собой разность ошибки решения дифференциального уравнения методом понижения порядка производной и ошибки решения дифференциального уравнения методом повышения порядка производной. Сигнал ошибки решения дифференциального уравнения методом понижения порядка производной содержит преимущественно низкочастотные составляющие, а сигнал ошибки решения дифференциального уравнения методом повышения порядка производной содержит преимущественно высокочастотные составляющие.

Основная часть низкочастотных составляющих выходного сигнала шестого операционного усилителя 9 проходит через фильтр 30 на второй вход второго сумматора 31. Так как емкостное сопротивление малая величина для высокочастотных сигналов, то основная часть высокочастотной составляющей выходного сигнала шестого операционного усилителя 9 не проходят через фильтр 30.

Таким образом, на второй вход второго сумматора 31 поступает низкочастотная составляющая сигнала, а так как выходной сигнал шестого операционного усилителя 9 представляет собой разность сигналов ошибки решения дифференциального уравнения методом понижения порядка производной и ошибки решения дифференциального уравнения методом повышения порядка производной, то на второй вход второго сумматора 31 с выхода шестого операционного усилителя 9 поступает сигнал ошибки решения дифференциального уравнения методом понижения порядка производной. Одновременно на первый вход второго сумматора 31 с выхода первого операционного усилителя 1 поступает сигнал, равный сумме сигналов решения дифференциального уравнения методом понижения порядка производной и ошибки решения дифференциального уравнения методом понижения порядка производной, но взятых с противоположным знаком. На втором сумматоре 31 происходит суммирование этих сигналов и инвертирование суммарного сигнала. При суммировании сигналов происходит компенсация ошибки решения дифференциальных уравнений. На выходе второго сумматора 31 имеем сигнал решения дифференциального уравнения Uвых. Данный сигнал используется для организации обратной связи и подается в первую цепь решения дифференциального уравнения через инвертор реализованный на пятом операционном усилителе 13 с десятым резистором 14 обратной связи и девятом резисторе 26, а также подается во вторую цепь решения дифференциального уравнения на дифференциальную цепочку, состоящую из конденсатора 15 и четвертого операционного усилителя 7 с шестым резистором 8 обратной связи.

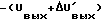

Величина ошибки решения дифференциального уравнения методом понижения порядка производной на выходе первого операционного усилителя 1 в предлагаемом устройстве меньше чем в прототипе. Это происходит потому, что на вход первого операционного усилителя 1 через второй резистор 17 поступает сигнал не с выхода первого операционного усилителя 1, а с выхода устройства через инвертор, состоящий из девятого резистора 26 и пятого операционного усилителя 13 с десятым резистором 14 обратной связи. Сигнал на выходе пятого операционного усилителя 13 представляет собой сумму сигналов решения дифференциального уравнения и ошибки решения дифференциального уравнения, взятую с обратным знаком: -(Uвых+ΔUвых). Сигнал на выходе первого операционного усилителя 1 представляет собой сумму сигналов решения дифференциального уравнения и ошибки решения дифференциального уравнения методом понижения порядка производной, взятую с обратным знаком:  Однако сигнал ошибки решения дифференциального уравнения ΔUвых меньше сигнала ошибки решения дифференциального уравнения методом понижения порядка производной

Однако сигнал ошибки решения дифференциального уравнения ΔUвых меньше сигнала ошибки решения дифференциального уравнения методом понижения порядка производной  Так как на вход первого операционного усилителя 1 через второй резистор 17 поступает сигнал с меньшей ошибкой, то и на выходе первого операционного усилителя 1 имеем решение дифференциального уравнения с меньшей ошибкой. Аналогично на выходе третьего операционного усилителя 5 имеем сумму сигналов решения дифференциального уравнения и ошибки решения дифференциального уравнения методом повышения порядка производной, причем ошибка меньше чем у прототипа. Действительно, если сигнал на конденсатор 15 в прототипе подавался с выхода третьего операционного усилителя 5, то в предлагаемом устройстве сигнал на конденсатор 15 подается с выхода устройства. Так как ошибка решения дифференциального уравнения на выходе устройства меньше ошибки решения дифференциального уравнения методом повышения порядка производной, то и ошибка на выходе третьего операционного усилителя 5 меньше аналогичной ошибки в прототипе.

Так как на вход первого операционного усилителя 1 через второй резистор 17 поступает сигнал с меньшей ошибкой, то и на выходе первого операционного усилителя 1 имеем решение дифференциального уравнения с меньшей ошибкой. Аналогично на выходе третьего операционного усилителя 5 имеем сумму сигналов решения дифференциального уравнения и ошибки решения дифференциального уравнения методом повышения порядка производной, причем ошибка меньше чем у прототипа. Действительно, если сигнал на конденсатор 15 в прототипе подавался с выхода третьего операционного усилителя 5, то в предлагаемом устройстве сигнал на конденсатор 15 подается с выхода устройства. Так как ошибка решения дифференциального уравнения на выходе устройства меньше ошибки решения дифференциального уравнения методом повышения порядка производной, то и ошибка на выходе третьего операционного усилителя 5 меньше аналогичной ошибки в прототипе.

Уменьшение ошибок на выходе двух параллельных цепей решения дифференциальных уравнений в свою очередь приводит к уменьшению ошибки на выходе устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ | 2013 |

|

RU2538945C1 |

| УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ | 2015 |

|

RU2583705C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ | 2022 |

|

RU2786339C1 |

| Устройство для решения дифференциальных уравнений | 1987 |

|

SU1509948A1 |

| Узловой элемент RC-сеточного процессора для решения задач теории переноса | 1988 |

|

SU1580405A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| МИКРОКОНТРОЛЛЕРНЫЙ ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ЕМКОСТИ И СОПРОТИВЛЕНИЯ В ДВОИЧНЫЙ КОД | 2013 |

|

RU2546713C1 |

| Аналоговый решающий узел | 1979 |

|

SU849244A1 |

| ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ МНОГОЭЛЕМЕНТНЫХ ПАССИВНЫХ ДВУХПОЛЮСНИКОВ | 2010 |

|

RU2466412C2 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 1987 |

|

RU1709841C |

Изобретение относится к области аналоговой вычислительной техники и может быть использовано для решения дифференциальных уравнений. Цель изобретения - повышение точности. Устройство содержит первую цепь решения, состоящую из операционного усилителя 1 с конденсатором 2 обратной связи, резисторы 17 и 18, вторую цепь решения, состоящую из операционных усилителей 5 и 7 с резисторами 4, 6 и 8 обратной связи, конденсатора 15 и резисторов 19 и 20, инвертора, состоящего из операционного усилителя 13, резистора 14 обратной связи и резистора 26, схему компенсации, состоящую из сумматоров 29 и 31 и фильтра 30. 1 ил.

Устройство для решения дифференциальных уравнений, содержащее фильтр, первый и второй сумматоры, первый интегратор, состоящий из операционного усилителя, конденсатора, обратной связи и двух токозадающих резисторов, второй интегратор, состоящий из трех операционных усилителей, разделительного конденсатора и шести токозадающих резисторов, первый вывод первого токозадающего резистора, первого интегратора соединен с информационным входом устройства, второй вывод первого токозадающего резистора первого интегратора соединен с первым выводом второго токозадающего резистора первого интегратора и первой обкладкой конденсатора обратной связи первого интегратора и подключен к входу операционного усилителя первого интегратора, выход которого соединен с второй обкладкой конденсатора обратной связи первого интегратора и с первым входом первого и второго сумматоров, первый вывод первого токозадающего резистора второго интегратора соединен с информационным входом устройства, второй вывод первого токозадающего резистора второго интегратора соединен с первыми выводами второго и третьего токозадающих резисторов второго интегратора и подключен к входу первого операционного усилителя второго интегратора, выход которого соединен с вторым выводом второго и первым выводом четвертого токозадающих резисторов второго интегратора, второй вывод последнего из которых соединен с первым выводом пятого токозадающего резистора второго интегратора и через второй операционный усилитель второго интегратора с вторым выводом пятого токозадаюшего резистора второго интегратора и с вторым входом первого сумматора, второй вывод третьего токозадающего резистора второго интегратора соединен с первым выводом шестого токозадающего резистора второго интегратора и с выходом третьего операционного усилителя второго интегратора, вход которого соединен с вторым выводом шестого токозадающего резистора второго интегратора и первой обкладкой разделительного конденсатора второго интегратора, выход первого сумматора через фильтр соединен с вторым входом второго сумматора, выход которого является выходом устройства, отличающееся тем, что в него введены операционный усилитель и два токозадающих резистора, причем выход второго сумматора соединен с второй закладкой разделительного конденсатора второго интеграторы и с первым выводом первого токозадающего резистора, второй вывод которого соединен с первым выводом второго токозадающего резистора и через операционный усилитель с вторым выводом второго токозадающего резистора первого интегратора и с вторым выводом второго токозадающего резистора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Прагер И.Л | |||

| Элeктpoнныe аналоговые вычислительные машины | |||

| - М.: Машиностроение, 1979, с | |||

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для решения дифференциальных уравнений | 1987 |

|

SU1509948A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-10-10—Публикация

1992-03-20—Подача