Изобретение относится к области вычислительной техники и может быть применено в аналоговых вычислительных машинах.

Известно устройство для решения дифференциальных уравнений, содержащее первый интегратор, вход которого является информационным входом устройства, фильтр, первый и второй сумматоры, второй интегратор, состоящий из трех операционных усилителей, разделительного конденсатора и шести токозадающих резисторов, первый вывод первого токозадающего резистора соединен с информационным входом устройства, второй вывод первого токозадающего резистора соединен с первыми выходами второго и третьего токозадающих резисторов и подключен к входу первого операционного усилителя, выход которого соединен с вторым выводом второго токозадающего резистора и первым выводом четвертого токозадающего резистора, второй вывод которого соединен с первым выводом пятого токозадающего резистора и через второй операционный усилитель с вторым выводом пятого токозадающего резистора, первым входом первого сумматора и первой обкладкой первого разделительного конденсатора, вторая обкладка которого соединена с первым выводом шестого токозадающего резистора и входом третьего операционного усилителя, выход которого соединен с вторыми выводами шестого и третьего токозадающих резисторов, выход первого интегратора подключен к второму входу первого и первому входу второго сумматоров, выход первого сумматора через фильтр соединен с вторым входом второго сумматора, выход которого является выходом устройства [Авторское свидетельство СССР №1509948 А1, кл. G01G 7/38].

Недостатком данного устройства является недостаточная точность, обусловленная тем, что всплеск высокочастотных помех во второй цепи решения дифференциального уравнения не контролируется в устройстве и проходит на выход устройства.

Известно устройство для решения дифференциальных уравнений, содержащее фильтр, первый и второй сумматоры, первый интегратор, состоящий из операционного усилителя, конденсатора, обратной связи и двух токозадающих резисторов, второй интегратор, состоящий из трех операционных усилителей, разделительного конденсатора и шести токозадающих резисторов, операционный усилитель и два токозадающих резистора, первый вывод первого токозадающего резистора, первого интегратора соединен с информационным входом устройства, второй вывод первого токозадающего резистора первого интегратора соединен с первым выводом второго токозадающего резистора первого интегратора и первой обкладкой конденсатора обратной связи первого интегратора и подключен к входу операционного усилителя первого интегратора, выход которого соединен с второй обкладкой конденсатора обратной связи первого интегратора и с первым входом первого и второго сумматоров, первый вывод первого токозадающего резистора второго интегратора соединен с информационным входом устройства, второй вывод первого токозадающего резистора второго интегратора соединен с первыми выводами второго и третьего токозадающих резисторов второго интегратора и подключен к входу первого операционного усилителя второго интегратора, выход которого соединен с вторым выводом второго и первым выводом четвертого токозадающих резисторов второго интегратора, второй вывод последнего из которых соединен с первым выводом пятого токозадающего резистора второго интегратора и через второй операционный усилитель второго интегратора с вторым выводом пятого токозадающего резистора второго интегратора и с вторым входом первого сумматора, второй вывод третьего токозадающего резистора второго интегратора соединен с первым выводом шестого токозадающего резистора второго интегратора и с выходом третьего операционного усилителя второго интегратора, вход которого соединен с вторым выводом шестого токозадающего резистора второго интегратора и первой обкладкой разделительного конденсатора второго интегратора, выход первого сумматора через фильтр соединен с вторым входом второго сумматора, выход которого является выходом устройства, выход второго сумматора соединен с второй обкладкой разделительного конденсатора второго интегратора и с первым выводом первого токозадающего резистора, второй вывод которого соединен с первым выводом второго токозадающего резистора и через операционный усилитель с вторым выводом второго токозадающего резистора первого интегратора и с вторым выводом второго токозадающего резистора [Патент РФ №2092899 С1, кл. G01G 7/38, 10.10.1997 (аналог)].

Недостатком данного устройства является недостаточная точность, обусловленная тем, что отсутствует возможность отключения второй цепи решения дифференциального уравнения при возникновении высокочастотных помех.

Наиболее близким к изобретению является устройство для решения дифференциальных уравнений, содержащее фильтр, первый и второй сумматоры, первую цепь решения дифференциального уравнения, состоящую из операционного усилителя, конденсатора, обратной связи и двух токозадающих резисторов, вторую цепь решения дифференциального уравнения, состоящую из трех операционных усилителей, разделительного конденсатора и шести токозадающих резисторов, первый вывод первого токозадающего резистора, первой цепи решения дифференциального уравнения соединен с информационным входом устройства, второй вывод первого токозадающего резистора первой цепи решения дифференциального уравнения соединен с первым выводом второго токозадающего резистора первой цепи решения дифференциального уравнения и первой обкладкой конденсатора обратной связи первой цепи решения дифференциального уравнения и подключен к входу операционного усилителя первой цепи решения дифференциального уравнения, выход которого соединен с второй обкладкой конденсатора обратной связи первой цепи решения дифференциального уравнения и с первым входом первого и второго сумматоров, первый вывод первого токозадающего резистора второй цепи решения дифференциального уравнения соединен с информационным входом устройства, второй вывод первого токозадающего резистора второй цепи решения дифференциального уравнения соединен с первыми выводами второго и третьего токозадающих резисторов второго интегратора и подключен к входу первого операционного усилителя второй цепи решения дифференциального уравнения, выход которого соединен с вторым выводом второго и первым выводом четвертого токозадающих резисторов второй цепи решения дифференциального уравнения, второй вывод последнего из которых соединен с первым выводом пятого токозадающего резистора второй цепи решения дифференциального уравнения и через второй операционный усилитель второй цепи решения дифференциального уравнения с вторым выводом пятого токозадаюшего резистора второй цепи решения дифференциального уравнения и с вторым входом первого сумматора, второй вывод третьего токозадающего резистора второй цепи решения дифференциального уравнения соединен с первым выводом шестого токозадающего резистора второй цепи решения дифференциального уравнения и с выходом третьего операционного усилителя второй цепи решения дифференциального уравнения, вход которого соединен с вторым выводом шестого токозадающего резистора второй цепи решения дифференциального уравнения и первой обкладкой разделительного конденсатора второй цепи решения дифференциального уравнения, выход первого сумматора соединен с входом фильтра, выход второго сумматора является выходом устройства, кроме того имеется компаратор и ключ, причем выход операционного усилителя первой цепи решения дифференциального уравнения соединен с вторым выводом второго токозадающего резистора, выход первого сумматора через компаратор соединен с первым входом ключа второй вход которого соединен с выходом фильтра, а выход с вторым входом второго сумматора, выход второго операционного резистора второй цепи решения дифференциальных уравнений соединен с второй обкладкой разделительного конденсатора второй цепи решения дифференциальных уравнений [Патент РФ №2538945 С1, кл. G01G 7/38. 10.01.2015 (прототип)].

Недостатком данного устройства является недостаточная точность, обусловленная тем, что при отключении второй цепи решения дифференциального уравнения, в случае возникновении в ней высокочастотных помех, отсутствует возможность запоминания компенсационного сигнала и использование его для уточнения выходного сигнала.

Цель изобретения - повышение точности решения дифференциальных уравнений.

Указанная цель достигается тем, что в устройство для решения дифференциальных уравнений, содержащее первый и второй сумматоры, первую цепь решения дифференциального уравнения, состоящую из операционного усилителя, конденсатора, обратной связи и двух токозадающих резисторов, вторую цепь решения дифференциального уравнения, состоящую из трех операционных усилителей, разделительного конденсатора и шести токозадающих резисторов, первый вывод первого токозадающего резистора первой цепи решения дифференциального уравнения соединен с информационным входом устройства, второй вывод первого токозадающего резистора первой цепи решения дифференциального уравнения соединен с первым выводом второго токозадающего резистора первой цепи решения дифференциального уравнения и первой обкладкой конденсатора обратной связи первой цепи решения дифференциального уравнения и подключен к входу операционного усилителя первой цепи решения дифференциального уравнения, выход которого соединен со второй обкладкой конденсатора обратной связи первой цепи решения дифференциального уравнения, со вторым выводом второго токозадающего резистора первой цепи решения дифференциального уравнения и с первым входом второго сумматора, первый вывод первого токозадающего резистора второй цепи решения дифференциального уравнения соединен с информационным входом устройства, второй вывод первого токозадающего резистора второй цепи решения дифференциального уравнения соединен с первыми выводами второго и третьего токозадающих резисторов второй цепи решения дифференциального уравнения и подключен к входу первого операционного усилителя второй цепи решения дифференциального уравнения, выход которого соединен со вторым выводом второго и первым выводом четвертого токозадающих резисторов второй цепи решения дифференциального уравнения, второй вывод последнего из которых соединен с первым выводом пятого токозадающего резистора второй цепи решения дифференциального уравнения и через второй операционный усилитель второй цепи решения дифференциального уравнения - со вторым выводом пятого токозадающего резистора второй цепи решения дифференциального уравнения и со второй обкладкой разделительного конденсатора второй цепи решения дифференциального уравнения, второй вывод третьего токозадающего резистора второй цепи решения дифференциального уравнения соединен с первым выводом шестого токозадающего резистора второй цепи решения дифференциального уравнения и с выходом третьего операционного усилителя второй цепи решения дифференциального уравнения, вход которого соединен со вторым выводом шестого токозадающего резистора второй цепи решения дифференциального уравнения и первой обкладкой разделительного конденсатора второй цепи решения дифференциального уравнения, выход первого сумматора через компаратор соединен с первым входом ключа, выход второго сумматора является выходом устройства, дополнительно введен интегратор, причем выход первого операционного усилителя второй цепи решения дифференциального уравнения соединен с первым входом первого сумматора, второй вход первого сумматора соединен с выходом устройства, выход первого сумматора соединен с вторым входом ключа, выход которого через интегратор соединен со вторым входом второго сумматора.

Новыми признаками, обладающими существенными отличиями, являются:

наличие в схеме устройства интегратора;

новые связи между известными и новыми признаками.

Данные признаки обладают существенными отличиями, так как в известных технических решениях не обнаружены.

Применение в устройстве всех новых признаков позволяет повысить точность решения дифференциальных уравнений за счет запоминания и использования последнего актуального компенсационного сигнала и слежения за погрешностью на выходе устройства.

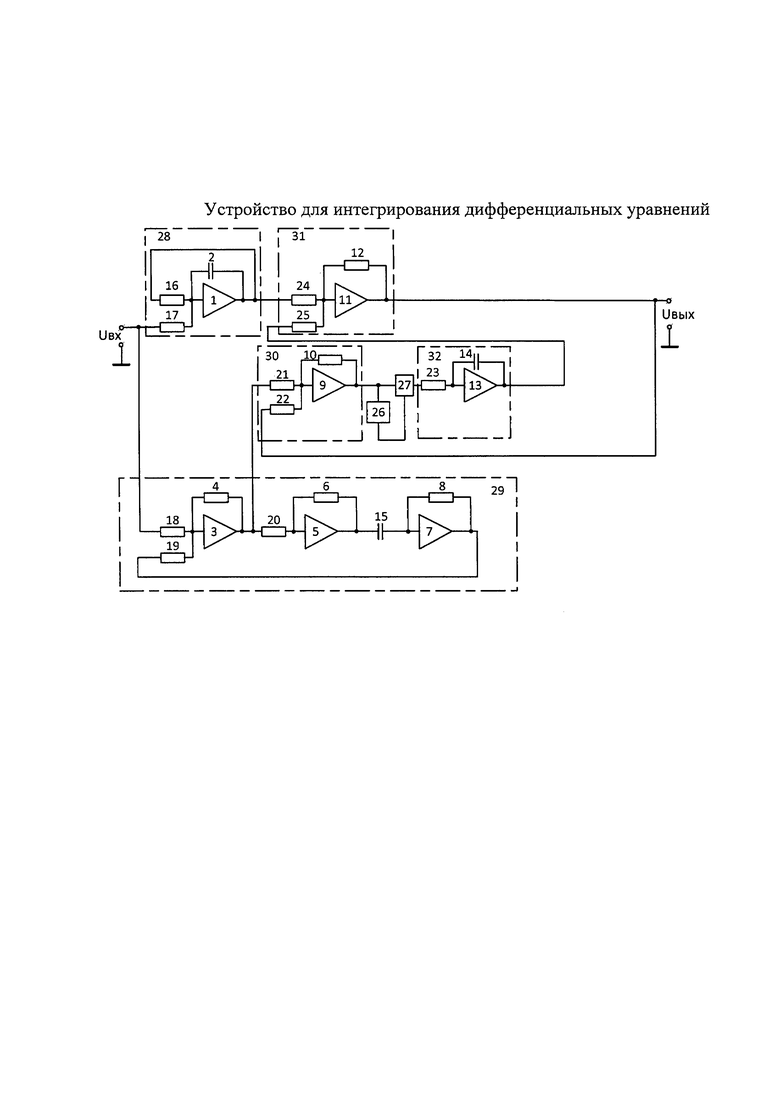

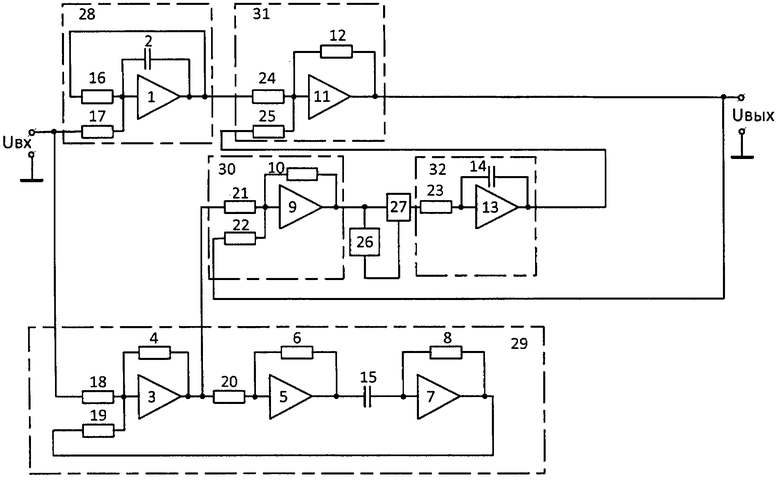

На чертеже изображена принципиальная схема устройства.

Устройство для интегрирования дифференциальных уравнений содержит операционный усилитель 1 с конденсатором 2 обратной связи, операционный усилитель 3 с резистором 4 обратной связи, операционный усилитель 5 с резистором 6 обратной связи, операционный усилитель 7 с резистором 8 обратной связи, операционный усилитель 9 с резистором 10 обратной связи, операционный усилитель 11 с резистором 12 обратной связи и операционный усилитель 13 с конденсатором 14 обратной связи, конденсатор 15, резисторы 16-25, компаратор 26 и ключ 27. Операционный усилитель 1, конденсатор 2, резисторы 16 и 17 в совокупности составляют первую цепь решения дифференциальных уравнений 28, операционный усилитель 9, резисторы 10, 21 и 22 в совокупности составляют первый сумматор 30, операционный усилитель 13, конденсатор 14, резистор 23 в совокупности составляют интегратор 32, операционный усилитель 11, резисторы 12, 24 и 25 в совокупности составляют второй сумматор 31, операционные усилители 3, 5 и 7, разделительный конденсатор 15 и резисторы 4, 6, 8, 18, 19 и 20 в совокупности составляют вторую цепь решения дифференциального уравнения 29.

Устройство работает следующим образом.

Устройство предназначено для решения дифференциального уравнения:

Подаваемый на вход сигнал через резисторы 17 и 18 одновременно подается на две независимые параллельные цепи решения дифференциального уравнения. Через резистор 17 входной сигнал Uвх поступает на вход операционного усилителя 1. Одновременно на вход операционного усилителя 1 через резистор 16 поступает сигнал решения дифференциального уравнения, взятый с противоположным знаком (-Uвых) с выхода операционного усилителя 1. На операционном усилителе 1 с конденсатором 2 обратной связи осуществляется интегрирование и инвертирование суммарного сигнала. Сигнал U1 с выхода операционного усилителя 1 представляет собой сумму сигнала ошибки решения дифференциального уравнения методом понижения порядка производной и сигнала решения дифференциального уравнения, взятого с противоположным знаком. При интегрировании высокочастотная составляющая ошибки гасится, но происходит усиление низкочастотной составляющей ошибки. Через резистор 18 входной сигнал Uвх также поступает на вход операционного усилителя 3. Одновременно на вход операционного усилителя 3 через резистор 19 поступает сигнал с выхода операционного усилителя 7. Сигнал на выходе операционного усилителя 7 представляет собой сигнал производной выходного сигнала, взятый с противоположным знаком  , и получается путем дифференцирования и инвертирования выходного сигнала на дифференцирующей цепочке, состоящей из разделительного конденсатора 15 и четвертого операционного усилителя 7 с резистором 8 обратной связи. Сигнал на выходе операционного усилителя 3 U1 представляет собой инвертированную сумму сигналов

, и получается путем дифференцирования и инвертирования выходного сигнала на дифференцирующей цепочке, состоящей из разделительного конденсатора 15 и четвертого операционного усилителя 7 с резистором 8 обратной связи. Сигнал на выходе операционного усилителя 3 U1 представляет собой инвертированную сумму сигналов  и взятых со своими весовыми коэффициентами. Значение весовых коэффициентов определяется величиной сопротивлений резисторов 4, 18 и 19

и взятых со своими весовыми коэффициентами. Значение весовых коэффициентов определяется величиной сопротивлений резисторов 4, 18 и 19

При дифференцировании низкочастотная составляющая ошибки гасится, а высокочастотная составляющая ошибки усиливается. Следовательно, ошибка решения дифференциального уравнения во второй цепи решения дифференциального уравнения носит высокочастотный характер.

Сигнал с выхода устройства через резистор 22 поступает на вход операционного усилителя 9. На вход операционного усилителя 9 через резистор 21 поступает сигнал с выхода операционного усилителя 3. Сигнал на выходе операционного усилителя 9 представляет собой разность ошибки решения дифференциального уравнения методом повышения порядка производной и ошибки решения дифференциального уравнения. Сигнал разности ошибок решения дифференциального уравнения одновременно подается на ключ 27 и на компаратор 26. Открытие и закрытие ключа 27 осуществляется по сигналам компаратора 26. Сигнал компаратора 26 принимает два дискретных значения - высокий уровень напряжения (лог. 1) и низкий уровень напряжения (лог. 0). Высокий уровень напряжения на выходе компаратора 26 формируется в том случае, если выходной сигнал первого сумматора 30 превышает заданную величину, то есть ошибки решения дифференциального уравнения во второй цепи 29 решения дифференциального уравнения и на выходе устройства значительно отличаются друг от друга. Большой сигнал на выходе первого сумматора 30 возникает при всплеске высокочастотных помех во второй цепи решения дифференциального уравнения 29 при воздействии искусственных или естественных помех. Низкий уровень напряжения на выходе компаратора 26 формируется в том случае, если выходной сигнал первого сумматора 30 не превышает заданную величину, то есть ошибки решения дифференциального уравнения во второй цепи 29 решения дифференциального уравнения и на выходе устройства не значительно отличаются друг от друга. В этом случае сигнал с выхода первого сумматора 30 через открытый ключ 27 поступает на интегратор 32. На интеграторе 32 осуществляется интегрирование входного разностного сигнала. При этом происходит подавление высокочастотного сигнала, соответствующего ошибке решения дифференциального уравнения во второй цепи 29, и восстановление погрешности решения дифференциального уравнения в первой цепи 28. Сигнал с выхода интегратора 32, представляющий собой оценку ошибки решения дифференциального уравнения в первой цепи решения дифференциального уравнения (28), подается на второй вход второго сумматора 31, где происходит компенсация ошибки решения дифференциального уравнения. Выходной сигнал второго сумматора 31 представляет собой решение дифференциального уравнения и является выходом устройства. Таким образом, осуществляется слежение за погрешностью на выходе устройства. При возникновении помех сигнал на выходе первого сумматора превышает допустимую величину, что приводит к изменению выходного сигнала компаратора. В этом случае сигнал с выхода первого сумматора 30 через закрытый ключ 27 не поступает на интегратор 32. Сигнал на выходе интегратора 32, в этом случае, представляет последнее запомненное значение сигнала коррекции. Данный запомненный сигнал используется для уточнения выходного сигнала устройства.

Предлагаемое изобретение по сравнению с прототипом и другими известными решениями имеет следующее преимущество - снижены погрешности вычисления решения дифференциального уравнения за счет: слежения за погрешностью на выходе устройства; запоминания последнего актуального компенсационного сигнала и использования его для уточнения решения дифференциального уравнения. Устройство может применяться в устройствах, в которых необходимо решать дифференциальные уравнения, например в инерциальных навигационных системах [Патент РФ №2362977 С1, кл. G01C 21/10, 27.07.2009, Патент РФ №2156959 С1, кл. G01C 25/00, G01P 21/00, 27.09.2000].

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ | 2013 |

|

RU2538945C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ | 1992 |

|

RU2092899C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ | 2022 |

|

RU2786339C1 |

| Устройство для решения дифференциальных уравнений | 1987 |

|

SU1509948A1 |

| Устройство для измерения дифференциального коэффициента передачи тока транзисторов | 1980 |

|

SU938220A1 |

| Узловой элемент RC-сеточного процессора для решения задач теории переноса | 1988 |

|

SU1580405A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Аналоговый решающий узел | 1979 |

|

SU849244A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1005082A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1420537A1 |

Изобретение относится к области аналоговой вычислительной техники и может быть использовано для решения дифференциальных уравнений. Технический результат заключается в повышении точности решения дифференциальных уравнений. Устройство содержит первую цепь решения, состоящую из операционного усилителя с конденсатором обратной связи и резисторов, вторую цепь решения, состоящую из операционных усилителей с резисторами обратной связи, конденсатора и резисторов, схему слежения, состоящую из сумматоров и интегратора, схему отключения сигнала коррекции. 1 ил.

Устройство для интегрирования дифференциальных уравнений, содержащее первый и второй сумматоры, первую цепь решения дифференциального уравнения, состоящую из операционного усилителя, конденсатора обратной связи и двух токозадающих резисторов, вторую цепь решения дифференциального уравнения, состоящую из трех операционных усилителей, разделительного конденсатора и шести токозадающих резисторов, первый вывод первого токозадающего резистора первой цепи решения дифференциального уравнения соединен с информационным входом устройства, второй вывод первого токозадающего резистора первой цепи решения дифференциального уравнения соединен с первым выводом второго токозадающего резистора первой цепи решения дифференциального уравнения и первой обкладкой конденсатора обратной связи первой цепи решения дифференциального уравнения и подключен к входу операционного усилителя первой цепи решения дифференциального уравнения, выход которого соединен со второй обкладкой конденсатора обратной связи первой цепи решения дифференциального уравнения, со вторым выводом второго токозадающего резистора первой цепи решения дифференциального уравнения и с первым входом второго сумматора, первый вывод первого токозадающего резистора второй цепи решения дифференциального уравнения соединен с информационным входом устройства, второй вывод первого токозадающего резистора второй цепи решения дифференциального уравнения соединен с первыми выводами второго и третьего токозадающих резисторов второй цепи решения дифференциального уравнения и подключен к входу первого операционного усилителя второй цепи решения дифференциального уравнения, выход которого соединен со вторым выводом второго и первым выводом четвертого токозадающих резисторов второй цепи решения дифференциального уравнения, второй вывод последнего из которых соединен с первым выводом пятого токозадающего резистора второй цепи решения дифференциального уравнения и через второй операционный усилитель второй цепи решения дифференциального уравнения - со вторым выводом пятого токозадающего резистора второй цепи решения дифференциального уравнения и со второй обкладкой разделительного конденсатора второй цепи решения дифференциального уравнения, второй вывод третьего токозадающего резистора второй цепи решения дифференциального уравнения соединен с первым выводом шестого токозадающего резистора второй цепи решения дифференциального уравнения и с выходом третьего операционного усилителя второй цепи решения дифференциального уравнения, вход которого соединен со вторым выводом шестого токозадающего резистора второй цепи решения дифференциального уравнения и первой обкладкой разделительного конденсатора второй цепи решения дифференциального уравнения, выход первого сумматора через компаратор соединен с первым входом ключа, выход второго сумматора является выходом устройства, отличающееся тем, что в него введен интегратор, причем выход первого операционного усилителя второй цепи решения дифференциального уравнения соединен с первым входом первого сумматора, второй вход первого сумматора соединен с выходом устройства, выход первого сумматора соединен с вторым входом ключа, выход которого через интегратор соединен со вторым входом второго сумматора.

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ | 2013 |

|

RU2538945C1 |

| Устройство для решения дифференциальных уравнений | 1984 |

|

SU1257671A1 |

| Устройство для решения дифференциальных уравнений | 1987 |

|

SU1509948A1 |

| US 7555507 B2, 30.06.2009. | |||

Авторы

Даты

2016-05-10—Публикация

2015-03-27—Подача