Изобретение относится к радиотехнике. В настоящее время на линиях и сетях спутниковой связи отсутствуют устройства обнаружения и анализа сигналов, позволяющие оперативно обнаружить факт мешающего воздействия посторонних станций спутниковой связи (ССС) или преднамеренных помех. Предлагаемый обнаружитель может быть использован для обнаружения сигналов и анализа сигнально-помеховой обстановки (СПО) на линиях спутниковой связи (ЛСС), работающих в условиях воздействия помех.

Известны устройства совместного обнаружения сигналов на фоне помех (шумов), работающие по различным алгоритмам и используемые, как правило, в радиолокационных системах. Так, устройства обнаружения сигналов в шумах, алгоритмы функционирования которых описаны в книге Репина В.Г., Тартаковского Г. П. Статистический синтез при априорной неопределенности и адаптация информационных систем. М. : Советское радио, 1977, с. 269, 277, 279, 291, содержат генераторы сигналов, интеграторы, реле.

Недостаток их заключается в том, что каждый из рассматриваемых обнаружителей решает частную задачу, т.е. задачу обнаружения сигнала в шуме определенного вида. Таким же недостатком обладают и устройства, описанные [1, 2] .

Обнаружители описанные в патенте Германии N 2158982, кл. H 02 H 7/10, [3] , а также устройства, функционирующие по алгоритмам, которые изложены в книге Левина Б.Р., Шварца В. Вероятностные модели и методы в системах связи и управления. М.: Радио и связь, 1985, с. 254-265, позволяют обнаружить сигнал лишь на известном шумовом фоне.

Наиболее близким аналогом (прототипом) к заявляемому по технической сущности является обнаружитель, описанный [4] и содержащий вычислительное устройство (ВУ), вход которого связан с выходом приемников, пороговое устройство (ПУ), первый вход которого соединен с выходом ВУ, а на второй вход ПУ подается значение порога.

Однако данный обнаружитель (прототип) также имеет недостаток, заключающийся в том, что обнаружитель позволяет принимать одну из двух альтернатив - есть сигнал или нет, но не позволяет принимать решение - присутствует ли только полезный сигнал или только помеха, или смесь полезного сигнала и помехи.

Задачей изобретения является разработка обнаружителя, обеспечивающего достижение технического результата, заключающегося в обнаружении сигнала и(или) помехи в условиях априорной неопределенности.

Указанный технический результат достигается тем, что в известный обнаружитель, содержащий вычислительное устройство, выход которого подключен к информационному входу порогового устройства, дополнительно введены дискретизатор, блоки задержки, адаптации, формирования порогов, формирования текущей гипотезы, причем вход дискретизатора является информационным входом обнаружителя сигналов, а его выход соединен параллельно с первыми информационными входами блока адаптации, вычислительного устройства и входом блока задержки, выход которого соединен параллельно с вторыми информационными входами вычислительного устройства и блока адаптации, выход которого соединен параллельно с вторым параметрическим входом вычислительного устройства и пятым параметрическим входом блока формирования порогов, первые четыре параметрических входа которого являются соответственно четырьмя параметрическими входами обнаружителя сигналов, причем его первый параметрический вход соединен параллельно с первым параметрическим входом вычислительного устройства и параметрическим входом блока адаптации, четыре выхода блока формирования порогов соединены с соответствующими четырьмя пороговыми входами порогового устройства, четыре выхода которого соединены с соответствующими четырьмя входами блока формирования текущей гипотезы, четыре выхода которого соответственно являются четырьмя выходами обнаружителя сигналов. Вычислительное устройство состоит из перемножителя, сумматора, первого и второго накапливающих сумматоров, причем первые входы первого и второго накапливающих сумматоров являются соответственно вторым и первым информационными входами вычислительного устройства, вторые входы соответствующих накапливающих сумматоров объединены и являются первым параметрическим входом вычислительного устройства, выход первого накапливающего сумматора соединен с первым входом перемножителя, второй вход которого является вторым параметрическим входом вычислительного устройства, выход второго накапливающего сумматора соединен с первым входом сумматора, второй вход которого соединен с выходом перемножителя, а выход сумматора является выходом вычислительного устройства. Пороговое устройство состоит из четырех узлов сравнения, первые входы которых объединены и являются информационным входом порогового устройства, вторые входы каждого узла сравнения являются соответствующими четырьмя пороговыми входами порогового устройства, выходы каждого узла сравнения являются соответствующими четырьмя выходами порогового устройства. Блок адаптации состоит из первого, второго перемножителей, первого, второго накапливающих сумматоров и делителя, причем вторые входы накапливающих сумматоров объединены и являются параметрическим входом блока адаптации, первый вход первого перемножителя является первым информационным входом блока адаптации, вторые входы перемножителей и первый вход второго перемножителя объединены и являются вторым информационным входом блока адаптации, выход первого перемножителя соединен с первым входом первого накапливающего сумматора, выход которого соединен с первым входом делителя, выход второго перемножителя соединен с первым входом второго накапливающего сумматора, выход которого соединен с вторым входом делителя, выход которого является выходом блока адаптации. Блок формирования порогов состоит из первого, второго, третьего, четвертого, пятого, шестого и седьмого сумматоров, первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого перемножителей, первого, второго и третьего делителей, регистра и инвертора, причем второй вход первого перемножителя является первым параметрическим входом блока формирования порогов, выход первого перемножителя соединен с первым входом первого делителя, второй вход которого соединен с выходом седьмого сумматора, первые входы второго, третьего, четвертого и пятого перемножителей объединены и соединены с выходом первого делителя, вторые входы второго сумматора, второго и седьмого перемножителей объединены и являются вторым параметрическим входом блока формирования порогов, первый вход второго сумматора, вторые входы четвертого и шестого перемножителей объединены и являются третьим параметрическим входом блока формирования порогов, первые входы восьмого и девятого перемножителей объединены и являются четвертым параметрическим входом блока формирования порогов, вторые входы третьего и пятого перемножителей объединены и соединены с выходом второго сумматора, первые входы первого, шестого и седьмого перемножителей объединены и соединены с выходом первого сумматора, первый вход которого соединен с выходом инвертора, вход которого является пятым параметрическим входом блока формирования порогов, вторые входы первого сумматора, второго и третьего делителей, первый и второй входы седьмого сумматора объединены и соединены с выходом регистра, второй вход восьмого перемножителя соединен с выходом второго делителя, второй вход девятого перемножителя соединен с выходом третьего делителя, выход второго перемножителя соединен с первым входом третьего сумматора, выход третьего перемножителя соединен с первым входом четвертого сумматора, вторые входы третьего и четвертого сумматоров объединены и соединены с выходом девятого перемножителя, выход четвертого перемножителя соединен с первым входом пятого сумматора, выход пятого перемножителя соединен с первым входом шестого сумматора, вторые входы пятого и шестого сумматоров объединены и соединены с выходом восьмого перемножителя, выход шестого перемножителя соединен с первым входом второго делителя, выход седьмого перемножителя соединен с первым входом третьего делителя, выходы третьего, четвертого, пятого и шестого сумматоров являются соответственно первым, вторым, третьим и четвертым выходами блока формирования порогов.

Сущность данного технического решения заключается в том, что по наблюдаемому случайному процессу (аналоговому сигналу) на входе дискретизатора, представляющему собой либо шум, либо смесь полезного сигнала и шума, либо смесь помехи, шума и полезного сигнала, либо смесь помехи и шума (итого четыре возможных гипотезы), т.е. в условиях априорной неопределенности относительно сигнала (помехи) и в целях ее преодоления, благодаря новой указанной выше совокупности признаков формируется достаточная статистика, по которой осуществляется проверка статистических гипотез, образующих полную группу событий, одно из которых всегда имеет место в текущий момент времени.

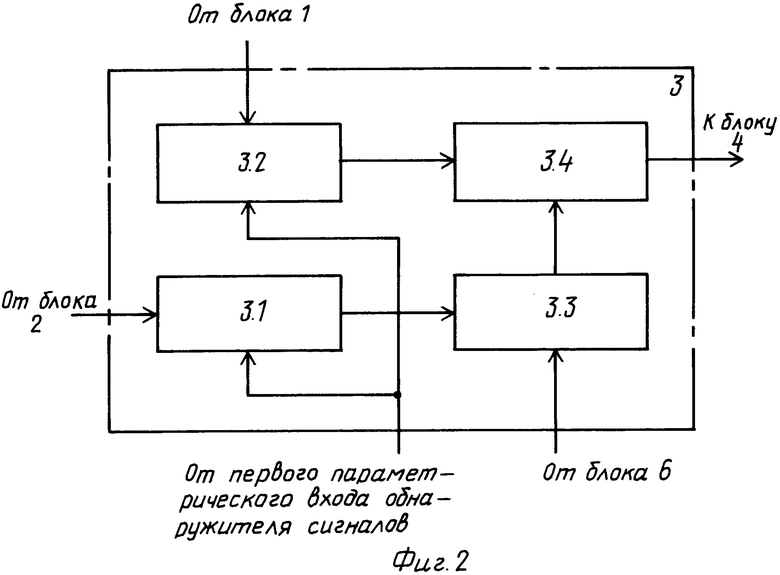

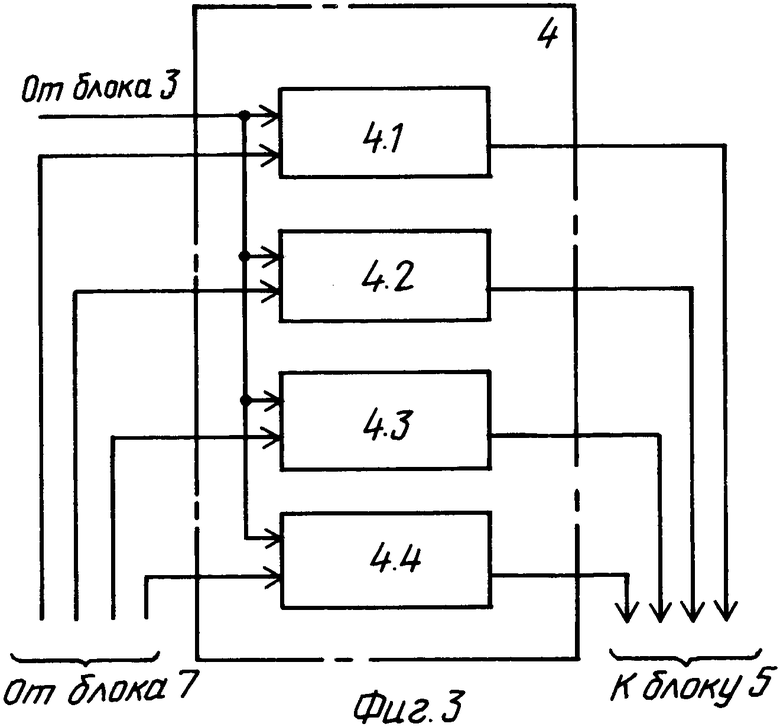

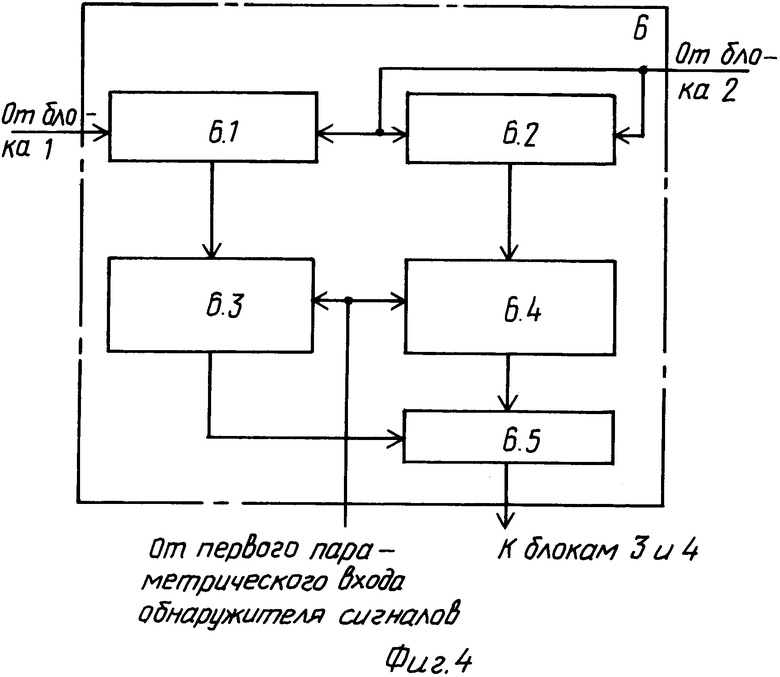

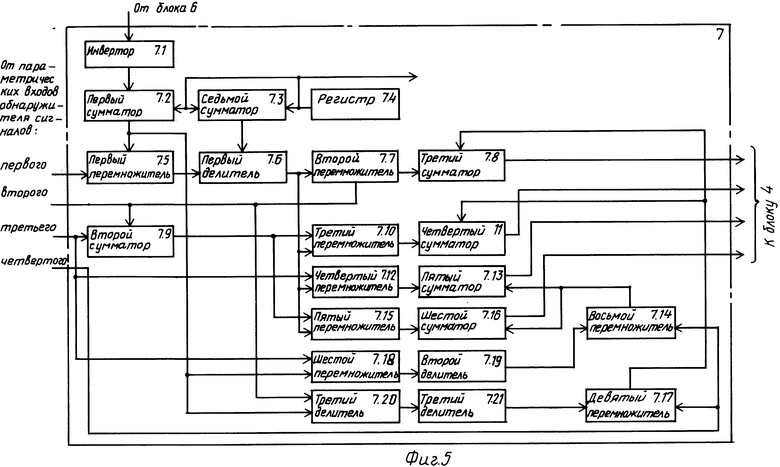

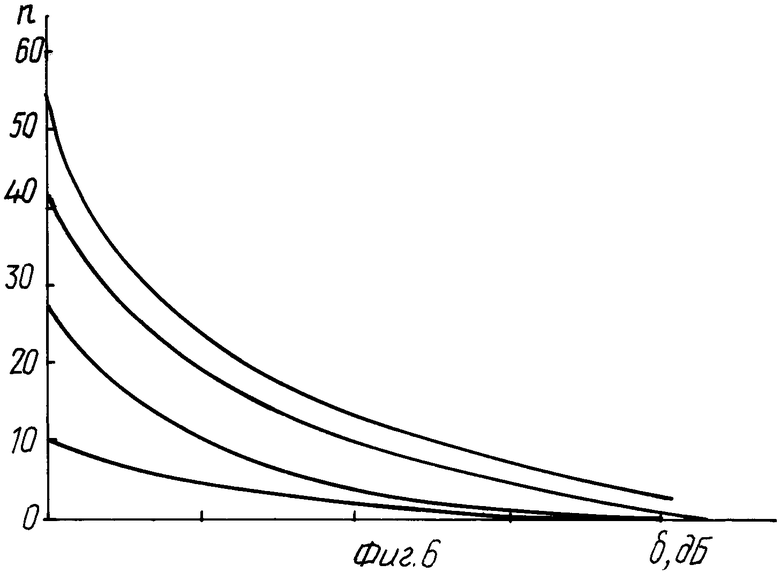

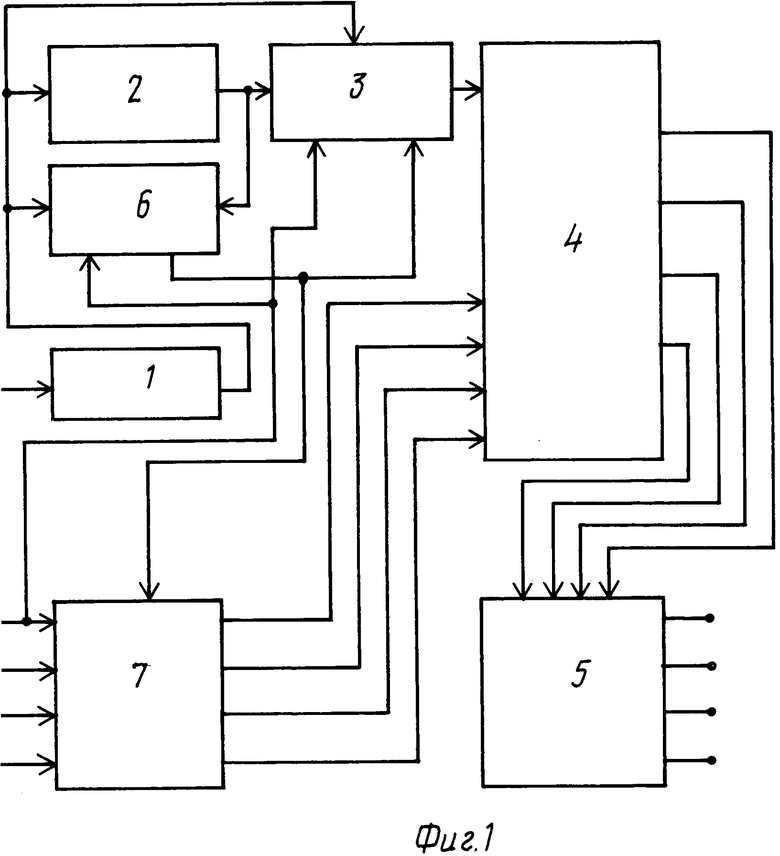

На фиг. 1 изображена структурная схема заявляемого обнаружителя сигналов; на фиг. 2 - структурная схема вычислительного устройства; на фиг. 3 - структурная схема порогового устройства; на фиг. 4 - структурная схема блока адаптации; на фиг. 5 - структурная схема блока формирования порогов; на фиг. 6 - графики зависимостей результатов анализа технико-экономической эффективности заявляемого обнаружителя сигналов.

Обнаружитель сигналов, показанный на фиг. 1, состоит из дискретизатора 1, вычислительного устройства 3, порогового устройства 4, блоков задержки 2, формирования текущей гипотезы 5, адаптации 6 и формирования порогов 7. Вход дискретизатора 1 является информационным входом обнаружителя сигналов, первый, второй, третий и четвертый параметрические входы блока формирования порогов 7 являются соответственно первым, вторым, третьим и четвертым параметрическими входами обнаружителя сигналов, причем его первый параметрический вход соединен параллельно с первым параметрическим входом вычислительного устройства 3 и параметрическим входом блока адаптации 6. Вход блока задержки 2, первые информационные входы вычислительного устройства 3 и блока адаптации 6 объединены и соединены с выходом дискретизатора 1. Вторые информационные входы вычислительного устройства 3 и блока адаптации 6 объединены и соединены с выходом блока задержки 2. Выход блока адаптации 6 соединен параллельно с вторым параметрическим входом вычислительного устройства 3 и пятым параметрическим входом блока формирования порогов 7, четыре выхода которого соединены с соответствующими четырьмя пороговыми входами порогового устройства 4, четыре выхода которого соединены с соответствующими четырьмя входами блока формирования текущей гипотезы 5, четыре выхода которого являются соответственно четырьмя выходами обнаружителя сигналов. Выход вычислительного устройства 3 соединен с информационным входом порогового устройства 4.

Дискретизатор 1 предназначен для выполнения над принимаемым аналоговым сигналом процедур дискретизации по времени, квантования по уровням, кодирования и получения после их процедур цифрового сигнала, представляющего собой значения отсчета принятого аналогового сигнала. Он может быть реализован в виде известного аналого-цифрового преобразователя (АПА), описанного в книге Микропроцессоры: в 3-х книгах. Кн. 2. Средства сопряжения. Контролирующие и информационно-управляющие системы: Учебник для ВТУЗов/ Под редакцией Л.Н. Преснухина. М.: Высшая школа, 1986, с. 156, рис. 1.96.

Блок задержки (БЗ) 2 предназначен для задержки j-го отсчета принятого сигнала на один такт, т.е. для получения на своем выходе в текущий момент времени (j-1)-го отсчета. БЗ 2 может быть реализован в виде элементов задержки импульсов, описанных в книге Справочник по схемотехнике для радиолюбителя / Под ред. В.П. Боровского. Киев.: Техника, 1987, с. 308, рис. 14.5.

Блок формирования текущей гипотезы (БФТГ) 5 предназначен для формирования цифрового сигнала в виде логической единицы на одном из четырех выходов (при этом на оставшихся трех выходах формируются цифровые сигналы в виде логического нуля), характеризующего одну из возможных четырех гипотез в зависимости от комбинации цифровых сигналов, поступающих на его четыре входа. БФТГ 5 может быть реализован в виде известной схемы дешифратора, описанной в кн. Шляпоберского В. И. Основы техники передачи дискретных сообщений. М.: Связь, 1973, с. 147, рис. 3.38.

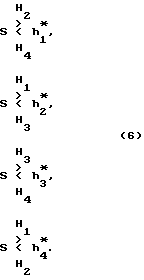

Итак, на выходе ВФТГ 5 формируется одна из возможных в текущий момент времени гипотез о состоянии СПО в ЛСС:

H1 - обнаружен и сигнал корреспондента, и преднамеренная помеха;

H2 - обнаружен только сигнал корреспондента;

H3 - обнаружена только преднамеренная помеха;

H4 - не обнаружены ни сигнал корреспондента, ни преднамеренная помеха.

При этом предполагается наличие постоянного шумового фона для всех четырех случаев. Для принятия решения о выборе одной из введенных гипотез Hi необходимо вначале сформировать достаточную статистику S, вычислить значения порогов h*, а затем произвести их сравнение в ВФТГ 5.

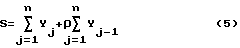

Вычислительное устройство 3 предназначено для вычисления по выборке отсчетов сигнала и с учетом коэффициента ρ , значения которых поступают на его входы, достаточной статистики S. Вычислительное устройство (ВУ) 3, структурная схема которого показана на фиг. 2, состоит из перемножителя 3.3, сумматора 3.4, первого 3.1 и второго 3.2 накапливающих сумматоров. Первые входы первого 3.1 и второго 3.2 накапливающих сумматоров являются соответственно вторым и первым информационными входами ВУ 3, вторые входы соответствующих накапливающих сумматоров 3.1 и 3.2 объединены и являются первым параметрическим входом ВУ 3. Выход первого накапливающего сумматора 3.1 соединен с первым входом перемножителя 3.3, второй вход которого является вторым параметрическим входом ВУ 3. Выход второго накапливающего сумматора 3.2 соединен с первым входом сумматора 3.4, второй вход которого соединен с выходом перемножителя 3.3. Выход сумматора 3.4 является выходом ВУ 3.

Блок адаптации 6 предназначен для вычисления оценочного значения коэффициента ρ , учитывающего статистическую зависимость (корреляцию) j-го Yj и (j-1)-го Yj-1 отсчетов сигнала. Блок адаптации (ВА) 6, структурная схема которого показана на фиг. 4, состоит из первого 6.1, второго 6.2 перемножителей, первого 6.3, второго 6.4 накапливающих сумматоров и делителя 6.5. Вторые входы накапливающих сумматоров 6.3 и 6.4 объединены и являются параметрическим входом БА 6. Первый вход первого перемножителя 6.1 является первым информационным входом БА 6. Вторые входы перемножителей 6.1, 6.2 и первый вход второго перемножителя 6.2 объединены и являются вторым информационным входом БА 6. Выход первого перемножителя 6.1 соединен с первым входом первого накапливающего сумматора 6.3, выход которого соединен с первым входом делителя 6.5. Выход второго перемножителя 6.2 соединен с первым входом второго накапливающего сумматора 6.4, выход которого соединен со вторым входом делителя 6.5. Выход делителя 6.5 является выходом БА 6.

Блок формирования порогов 7 предназначен для вычисления значений порогов h

Пороговое устройство 4 предназначено для сравнения достаточной статистики S со значениями порогов h

ВУ 3, БА 4, БФП 7 заявляемого обнаружителя сигналов реализуются из конструктивно известных элементов, а именно:

1) сумматоров 3.4, 7.2, 7.3, 7.8, 7.9, 7.11, 7.13, 7.16, которые можно реализовать аналогично сумматорам, описанным в книге Пятлина О.А., Овсищера П. И., Лазера И.М. и др. Проектирование микроэлектронных цифровых устройств. - М.: Сов. радио, 1977, с. 123, рис. 4.12 и Папернов А.А. Логические основы цифровой вычислительной техники. Изд. 3-е, переработанное и дополненное. Учебное пособие для ВТУЗов. М.: Сов. радио, 1972, с. 146-150, рис. 2-5;

2) накапливающих сумматоров 3.1, 3.2, 6.3, 6.4, которые можно реализовать аналогично накапливающим сумматорам, описанным в книге Папернова А.А. Логические основы цифровой вычислительной техники. Изд. 3-е, переработанное и дополненное. Учебное пособие для ВТУЗов. М.: Сов. радио, 1972, с. 158, рис. 13;

3) перемножителей 3.3, 6.1, 6.2, 7.5, 7.7, 7.10, 7.12, 7.14, 7.15, 7.17, 7.18, 7.20, 7.21, 7.23, которые можно реализовать аналогично множительным устройствам, описанным там же, с. 202 - 204, рис. 4;

4) делителей 6.5, 7,6, 7,19, 7,22, которые можно реализовать аналогично делителям, описанным в книгах Шляпоберского В.И. Основы техники передачи дискретных сообщений. М.: 1973, с. 133, рис. 3.25 и Папернова А.А.. Логические основы цифровой вычислительной техники. Изд. 3-е, переработанное и дополненное. Учебное пособие для ВТУЗов. М.: Сов. радио, 1972, с. 228, рис. 1;

5) регистра 7.4, представляющего собой цифровой автомат с памятью для хранения единицы, который можно реализовать в виде триггера, описанного в книге Мальцева Л.А. и др. Основы цифровой техники. М.: Радио и связь, 1987, с. 24 - 25, рис. 12;

инвертора 7.1, который можно реализовать в виде элемента НЕ, описанного в книге Мальцева Л. А. и др. Основы цифровой техники. М.: Радио и связь, 1987, с. 21, рис.9.

Обнаружитель сигналов работает следующим образом.

Реализация случайного процесса y(t), представляющего собой принятый аналоговый сигнал, поступает на вход дискретизатора 1, который выполняет над ним процедуры дискретизации по времени, квантования по уровням, кодирования и получения после этих процедур цифрового сигнала, представляющего собой значения отсчетов действующего значения принятого аналогового сигнала. Принятый аналоговый сигнал поступает на вход дискретизатора 1, например, с выхода приемника по промежуточной частоте, входящего в состав приемного тракта ССС. На выходе дискретизатора 1 последовательность выборочных данных имеет вид (Кокс Д.. Хинкли Д. Теоретическая статистика. М.: Мир, 1978, с. 71):

Yj=Z(t,θс,θп)=θсμс+θпμп+ρ(Yj-1-θсμс-θпμп)+εj,(1)

где  - вектор-строка индикаторов наличия сигнала θс и помехи θп , причем значения индикаторов при отсутствии и наличии сигнала (помехи) соответственно равны [1,0];

- вектор-строка индикаторов наличия сигнала θс и помехи θп , причем значения индикаторов при отсутствии и наличии сигнала (помехи) соответственно равны [1,0]; - вектор-столбец математических ожиданий уровней сигнала и помехи соответственно;

- вектор-столбец математических ожиданий уровней сигнала и помехи соответственно; - взвешивающий коэффициент, определяющий зависимость временных отсчетов (j, j-1),

- взвешивающий коэффициент, определяющий зависимость временных отсчетов (j, j-1),  ;

;

εj - независимые нормально распределенные случайные величины, характеризующие шум с дисперсией σ

n -объем выборки.

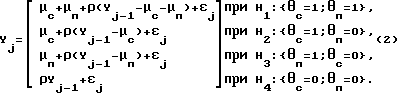

В терминах задачи многоальтернативного обнаружения для возможных статистических ситуаций, возникающих на выходе блока дискретизации, формулу (1) можно интерпретировать следующим образом:

Решение по наблюдаемой последовательности случайного процесса Yj относительно введенных гипотез Hi (i=1,2,3,4) будет приниматься по достаточной статистике S, определяемой объемом выборки зависимых отсчетов j  . Значение j-го отсчета с выхода дискретизатора 1 поступает на первые информационные входы ВУ 3, БА 6 и вход БЗ 2. БЗ 2 оьеспечивает задержку j-го отсчета Yj на один такт, т.е. в текущий момент времени на выходе БЗ 2 присутствует (j-1)-й отсчет Yj-1, который поступает одновременно на вторые информационные входы ВУ 3 и БА 6. Дальнейшее решение задачи связано с анализом модифицированных отношений правдоподобия, которые можно записать в виде

. Значение j-го отсчета с выхода дискретизатора 1 поступает на первые информационные входы ВУ 3, БА 6 и вход БЗ 2. БЗ 2 оьеспечивает задержку j-го отсчета Yj на один такт, т.е. в текущий момент времени на выходе БЗ 2 присутствует (j-1)-й отсчет Yj-1, который поступает одновременно на вторые информационные входы ВУ 3 и БА 6. Дальнейшее решение задачи связано с анализом модифицированных отношений правдоподобия, которые можно записать в виде

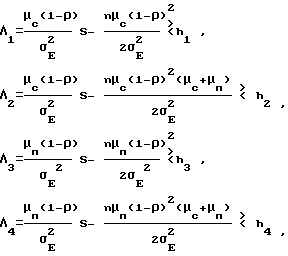

которые после преобразования примут вид

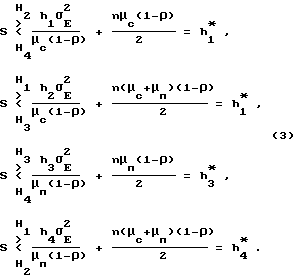

Полагая одинаковой степень риска принятия решений, по гипотезам Hi можно считать h1= h2= h3=h4=h. Из формулы (3) следует, что для принятия решения о выборе одной из введенных гипотез Hi необходимо сформировать достаточную статистику S, вычислить значение порогов h*, а затем произвести их сравнение.

БА 6 осуществляет формирование оценочных значений коэффициента ρ, учитывающего статистическую зависимость (корреляцию) j-го Yi и (j-1)-го Yj-1 отсчетов, поступающих на его первый и второй информационные входы. В книге Кокса Д., Хинкли Д. Теоретическая статистика. М.: Мир, 1978, с.336, показано, что для регулярных плотностей распределения f(Y0, Y1,...Yn, ρ ) предельное распределение оценки ρ асимптотически нормальное со средним  . Вычисление оценочных значений коэффициента корреляции отсчетов осуществляется в БА 6 по формуле

. Вычисление оценочных значений коэффициента корреляции отсчетов осуществляется в БА 6 по формуле

Первый перемножитель 6.1 совместно с первым накапливающим сумматором 6.3 вычисляют значения числителя формулы (4), используя для этого значения Yj, Yj-1 и n, поступающие соответственно на первый, второй информационные входы и на параметрический вход БА 6. Второй перемножитель 6.2 совместно с вторым накапливающим сумматором 6.4 вычисляют значения знаменателя формулы (4), используя для этого те же значения Yj, Yj-1 и n. Делитель 6.5 предназначен для вычисления значения ρ в соответствии с формулой (4), используя для этого значения числителя и знаменателя, поступающие на его входы соответственно с выходов первого 6.1 и второго 6.2 накапливающих сумматоров. В результате на выход БА 6 с выхода делителя 6.5 выдаются значения

которые поступают одновременно на второй параметрический вход ВУ 3 и пятый параметрический вход БФП 7.

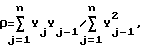

ВУ 3 по выборке отсчетов Yi и Yj-1, поступающих соответственно на его первый и второй информационные входы с выходов дискретизатора 1 и БЗ 2, и с учетом коэффициента ρ , значения которого поступают с выхода БА 6, вычисляют значения достаточной статистики S вида

путем весового сложения j-го Yi и (j-1)-го Yj-1 отсчетов. В формуле (5) n - объем выборки зависимых отсчетов  . Первый накапливающий сумматор 3.1 вычисляет значения суммы вида ,

. Первый накапливающий сумматор 3.1 вычисляет значения суммы вида , , причем значения отсчетов Yj-1 и параметра n поступают на его первый и второй входы соответственно с второго информационного и первого параметрического входов ВУ 3. Второй накапливающий сумматор 3.2 вычисляет значения суммы вида

, причем значения отсчетов Yj-1 и параметра n поступают на его первый и второй входы соответственно с второго информационного и первого параметрического входов ВУ 3. Второй накапливающий сумматор 3.2 вычисляет значения суммы вида  , при этом значения отсчетов Yj и параметра n поступают на его первый и второй входы соответственно со второго информационного и первого параметрического входов ВУ 3. Перемножитель 3.3 вычисляет второе слагаемое формулы (5) путем перемножения значений коэффициента ρ , поступающих на его второй вход с второго параметрического входа ВУ 3, и значений суммы, поступающих на его первый вход с выхода первого накапливающего сумматора 3.1. Сумматор 3.4 вычисляет значения статистики S в соответствии с формулой (5), при этом значения первого и второго слагаемых формулы (5) поступают на его входы соответственно с выходов второго накапливающего сумматора 3.2 и перемножителя 3.3. С выхода сумматора 3.4 значения статистики S поступают на выход ВУ 3 и далее подаются на информационный вход ПУ 4. На первый, второй, третий и четвертый пороговые входы ПУ 4 поступают значения порогов h

, при этом значения отсчетов Yj и параметра n поступают на его первый и второй входы соответственно со второго информационного и первого параметрического входов ВУ 3. Перемножитель 3.3 вычисляет второе слагаемое формулы (5) путем перемножения значений коэффициента ρ , поступающих на его второй вход с второго параметрического входа ВУ 3, и значений суммы, поступающих на его первый вход с выхода первого накапливающего сумматора 3.1. Сумматор 3.4 вычисляет значения статистики S в соответствии с формулой (5), при этом значения первого и второго слагаемых формулы (5) поступают на его входы соответственно с выходов второго накапливающего сумматора 3.2 и перемножителя 3.3. С выхода сумматора 3.4 значения статистики S поступают на выход ВУ 3 и далее подаются на информационный вход ПУ 4. На первый, второй, третий и четвертый пороговые входы ПУ 4 поступают значения порогов h

БФП 7 выполняет операцию формирования значений порогов в соответствии с равенствами выражений формулы (3) с учетом того, что h1=h2=h3=h4=h. На параметрические входы БФП 7 с соответствующих параметрических входов обнаружителя сигналов поступают;

- на первый параметрический вход - значения параметра n;

- на второй параметрический вход - значения параметра μс ;

- на третий параметрический вход - значения параметра μп ;

- на четвертый параметрический вход - значения произведения параметров вида hσ

Эти параметры могут поступать на параметрические входы обнаружителя сигналов, например, с выхода пульта управления ССС, в который они предварительно вводятся, либо, например, поступать на ССС и входы обнаружителя сигналов иным образом, зависящим от конкретной реализации ССС. Значения параметра ρ-1 поступают на пятый параметрический вход БФП 7 с выхода БА 6. В регистре 7.4 постоянно хранится число 1. На выходе седьмого сумматора 7.3 постоянно формируется число 2. Последовательно соединенные инвертор 7.1 и первый сумматор 7.2 с подключенным к его второму входу регистром 7.4 вычисляют значения выражения (1-ρ)Z, которые с выхода первого сумматора 7.2 поступают одновременно на первые входы первого 7.5, шестого 7.18 и седьмого 7.21 перемножителей. Последовательно соединенные первый перемножитель 7.5 и первый делитель 7.6 с подключенным к его второму входу седьмым сумматором 7.3 вычисляют значения выражения n(1-ρ)/2, которые с выхода первого делителя 7.6 поступают одновременно на первые входы второго 7.7, третьего 7.10, четвертого 7.12 и пятого 7.15 перемножителей. Второй сумматор 7.9 вычисляет значения суммы (μс+μп), которые с его выхода поступают на вторые входа третьего 7.10 и пятого 7.15 перемножителей. Второй перемножитель 7.7 вычисляет значения второго слагаемого первого выражения формулы (3), третий перемножитель 7.10 вычисляет значения второго слагаемого второго выражения формулы (3), четвертый перемножитель 7.12 вычисляет значения второго слагаемого третьего выражения формулы (3), пятый перемножитель 7.15 вычисляет значения второго слагаемого четвертого выражения формулы (3), шестой перемножитель 7.18 вычисляет значения знаменателей первых слагаемых третьего и четвертого выражений формулы (3), седьмой перемножитель 7.21 вычисляет значения знаменателей первых слагаемых первого и второго выражений формулы (3). Восьмой перемножитель 7.14 вычисляет значения первых слагаемых третьего и четвертого выражений формулы (3), а девятый перемножитель 7.17 вычисляет значения первых слагаемых первого и второго выражений формулы (3). На входы третьего 7.8, четвертого 7.11, пятого 7.13 и шестого 7.16 сумматоров поступают значения первых и вторых слагаемых соответственно первого, второго, третьего и четвертого равенств выражений формулы (3), которые суммируются в соответствующих сумматорах и с их выходов значения порогов h

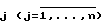

Пороговое устройство осуществляет операцию сравнения вычисленной достаточной статистики S с порогами h

При этом на первые входы узлов сравнения 4.1, 4.2, 4.3 и 4.4 одновременно поступают значения статистики S, а на каждый второй вход соответствующих узлов сравнения соответственно поступают значения порогов h

где Λ - знак логического умножения.

Если условия, указанные в соответствующем выражении формулы (7), выполняются, то на соответствующем гипотезе Hi i-ом выходе БФТГ 5 формируется уровень логической единицы. В противном случае формируется уровень логического нуля.

Итак, на соответствующем выходе БФТГ 5 формируется одна из возможных в текущий момент времени гипотез о состоянии сигнально-помеховой обстановки в линии спутниковой связи:

H1 - обнаружен и сигнал корреспондента, и преднамеренная помеха;

H2 - обнаружен только сигнал корреспондента;

H3 - обнаружена только преднамеренная помеха;

H4 - не обнаружены ни сигнал корреспондента, ни преднамеренная помеха.

При этом предполагается наличие постоянного шумового фона для всех четырех случаев. Полученные результаты решения задачи о принятии соответствующей гипотезы с выходов обнаружителя сигналов могут далее подаваться, например, в систему управления ССС (линии или сети спутниковой связи) для обеспечения управления ими.

Предлагаемый обнаружитель сигналов обладает универсальностью в том смысле, что за счет идентификации неизвестного параметра ρ принятой модели и учета априорных энергетических параметров ЛСС возможно его использование для стационарных, узловых и автономных станций спутниковой связи. При этом изменяются лишь входные параметры μп,μс , n. Адаптивность устройства заключается в самоподстройке коэффициента корреляции по величине отсчетов дискретной случайной величины.

Оценку технико-экономической эффективности предлагаемого обнаружителя сигналов целесообразно провести на основе анализа зависимости функционирования предложенного алгоритма от объема выборки n, формирующей достаточную статистику S по сравнению с известными алгоритмами, т.е. по быстродействию принятия решения. На фиг. 6 представлена графическая зависимость требуемого объема выборки n от отношения сигнал(помеха)/шум (δ) наблюдаемой реализации случайного процесса при различных требованиях по вероятностям ошибок 1 и 2 рода. Из графиков видно, что с увеличением отношения сигнал(помеха)/шум величина объема выборки для принятия решения резко уменьшается. Из анализа представленных зависимостей следует, что требуемый объем выборки даже при низких соотношениях δ<5 дБ не превышает 60 отсчетов в широком диапазоне изменений вероятностей ошибок, что является более эффективным по сравнению с известными устройствами (Сосулин Ю.Г. Теория обнаружения и оценивания стохастических сигналов. М. : Советское радио, 1978, с.320), т.к. для тех же вероятностей ошибок требуется не менее 100 отсчетов для двухальтернативного и 80 для рангового обнаружителей.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОЙ ОЦЕНКИ ЗАКОНА РАСПРЕДЕЛЕНИЯ ПОТОКОВ СООБЩЕНИЙ | 1994 |

|

RU2094844C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127903C1 |

| ИНТЕРПОЛЯТОР | 1998 |

|

RU2132568C1 |

| АДАПТИВНОЕ УСТРОЙСТВО РАЗДЕЛЕНИЯ СИГНАЛОВ ДВОИЧНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 1998 |

|

RU2134026C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| СПОСОБ ОЦЕНИВАНИЯ НЕСУЩЕЙ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2100812C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2127901C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

Изобретение относится к радиотехнике и может быть использовано на линиях спутниковой связи, работающих в условиях воздействия помех. Задачей является разработка устройства, обеспечивающего обнаружение сигнала и (или) помехи и анализа сигнально-помеховой обстановки в условиях априорной неопределенности. Обнаружитель сигналов состоит из дискретизатора 1, вычислительного устройства 3, порогового устройства 4, блоков задержки 2, формирования текущей гипотезы 5, адаптации 6, формирования порогов 7 и имеет один информационный вход, четыре параметрических входа и четыре выхода по числу возможных гипотез. Обнаружение сигнала и (или) помехи в условиях априорной неопределенности осуществляется благодаря указанной совокупности признаков путем формирования по наблюдаемому случайному процессу, поступающему на информационный вход обнаружителя сигналов, достаточной статистики, по которой осуществляется проверка статистических гипотез, образующих полную группу из четырех событий, одно из которых всегда имеет место в текущий момент времени. 4 з.п. ф-лы, 6 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, авторское свидетельство, 500591, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| SU, авторское свидетельство, 535739, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| US, патент, 3775770, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Ширман Я.Д., Манжос В.Н | |||

| Теория и техника обработки радиолокационной информации на фоне помех | |||

| - М.: Радио и связь, 1981, с.13, рис.2.3. | |||

Авторы

Даты

1998-04-27—Публикация

1997-01-23—Подача