Изобретение относится к области тестирования и измерения параметров полупроводниковых приборов дискретных и, в первую очередь, интегральных транзисторов компонентов БИС и СБИС.

В данный период развития высококачественных биполярных БИС с высокими технико-экономическими параметрами высокими технологическим и системным быстродействием, степенью интеграции первоочередное значение приобретают вопросы надежности, стабильности и воспроизводимости электрических параметров как статических, так и динамических. Дело в том что, следуя законам "скэйлинга" или масштабирования транзисторов для БИС, изготовляемых на основе субмикронной технологии с 0,3 0,8 мкм минимальными размерами, для обеспечения высоких параметров по усилению и быстродействию необходимо использовать режим высоких и сверхвысоких плотностей тока (0,5 - 1,2)•105 А/см2. Это дает возможность быстрой зарядки паразитных и барьерных емкостей переходов, с одной стороны, и, с другой стороны, таит потенциальную опасность деградации усилительных и высокочастотных свойств транзистора.

Недавно были открыты и исследованы явления "токовых стрессов" в транзисторах с малой площадью эмиттера, когда после пропускания в течение нескольких часов значительных плотностей тока (0,6 1)•105 А/см2 через прямосмещенный эмиттерный переход в активном нормальном режиме могли возникать значительные утечки эмиттерного перехода, увеличивающие ток базы в микрорежиме (для смещений Uэ ≃ 0,4 0,6 В) и снижающие коэффициент передачи тока [1] Информация, представленная в [1] позволяет сформулировать процедуру тестирования транзистора, включающую в себя стадию пропускания эмиттерного тока через прямосмещенный эмиттерно-базовый p-n переход для небольших прямых смещений 0,5 0,7 В и измерения базового тока, затем стадию пропускания эфиттерного тока в течение 103 106 с через эмиттерно-базовый переход при подаче обратного смещения на коллекторный p-n переход, с обеспечением плотности эмиттерного тока (0,6 - 1)•105 А/см2, измерение после второй стадии базового тока в рамках первой стадии, сравнение базовых токов при одинаковых прямых смещениях эмиттерно-базового перехода и отбраковки тестируемых транзисторов по значительному увеличению базового тока (более 10 20%).

К недостаткам данного способа относятся большая длительность тестирования десятки часов и даже несколько суток, а также невысокая информативность тестирования вследствие не столь значительного проявления стрессово-индуцированных токов утечек базы в режиме активном, нормальном - тестирования транзистора.

Для увеличения информативности тестирования и достоверности результатов предложен модифицированный способ тестирования в активном инверсном режиме токов утечек [2] взятым нами в качестве прототипа. В данном способе, включающем на первой стадии пропускание эмиттерного тока через прямосмещенный эмиттерно-базовый p-n переход при соединении коллекторы и базы к источнику обратного смещения или к общей шине и измерение базового тока, на второй стадии пропускание коллекторного тока через прямосмещенный коллекторный переход при соединении эмиттера и базы к источнику обратного смещения или к общей шине реализации высокой плотности эмиттерного тока на эмиттерном контакте и оценки зависимостей базового тока до и после стрессовых испытаний. Суть данного способа в более сильном воздействии инверсного нормального режима при пропускании высокой плотности тока через эмиттерный контакт на возникновение утечек перехода эмиттер-база. Недостаток данного способа - большой временной диапазон стрессовых испытаний десятки часов несколько суток, отсутствие критериев тестирования на качество испытуемых объектов, влияние саморазогрева рабочих областей транзистора на характеристики тестирования.

Предлагается способ тестирования токов утечек транзистора, включающий на первой стадии пропускание эмиттерного тока через прямосмещенный эмиттерно-базовый p-n переход при соединении коллектора и базы к общей шине и измерение базового тока, на второй стадии пропускание коллекторного тока через прямосмещенный коллекторно-базовый переход при соединении эмиттера и базы к общей шине и реализации высокой плотности эмиттерного тока на эмиттерном контакте, причем на второй стадии прямое напряжение коллектор-база подают в виде последовательности импульсов со скважностью не менее 104 и длительностью импульса не более 3•10-4 с, с амплитудой, обеспечивающей плотность эмиттерного тока не менее 2•106 А/см2, а на третьей стадии повторяют первую стадию, сравнивают измерение базовых токов в диапазоне 10-12 10-6 А для первой стадии и после процедуры второй стадии и затем по значительному более чем 10% -му увеличению базового тока при одинаковых смещениях эмиттерно-базового перехода отбраковывают испытуемые транзисторы, характеризуемые возникновением нежелательных стрессовых токовых утечек.

Технический результат предложенного способа заключается в повышении эффективности тестирования, в первую очередь, за счет значительного сокращения временного интервала в режиме постоянного тока при переходе на импульсный режим стрессового токового тестирования; во-вторых, за счет использования более высокой импульсной плотности тока на второй стадии тестирования в активном инверсном режиме с закороченными эмиттером и базой. Импульсное использование активного инверсного режима с достижением высокой плотности тока на контакте эмиттера около 2•106 А/см2 (превышающего диапазон (0,5-5,8)•105 А/см2 на постоянном токе в течение ≈ 106 с прототипа) позволяет более эффективно и целенаправлено реализовать возможности возбуждения стрессового индуцированного тока на периферии эмиттерного перехода вследствие деградации окисла на его поверхности за счет усиленной инжекции электронов со дна коллекторного перехода. Данные инжектированные высокоэнергетичные электроны, получив дополнительную энергию во время пересечения эмиттерного перехода (даже при закороченных электродах базы и эмиттера), создают на поверхности эмиттерного p-n перехода дополнительные дислокационные центры, способствующие увеличению тока периферии или утечки составляющей базового тока. Если энергия инжектированных электронов со дна коллекторного перехода увеличивалась за счет приложения дополнительного обратного смещения эмиттер база, то в заявленном способе условия на эмиттерном переходе единообразны для цикла тестирования и для всех тестовых транзисторов внешнее напряжение эмиттер база равно нулю (что говорит о единообразии свойств собственно p-n перехода). Однако созданием импульсного большого отпирающего напряжения коллектор база, задающего большой стрессовый ток электронов со дна коллектора, мы подвергаем более жесткому, но кратковременному испытанию облучаемые окисные участки на периферии p-n перехода и создаем более благоприятные условия для интенсификации стрессовых утечек. В случае однородных с минимальным количеством дислокаций окисла по периферии p-n перехода жесткий стрессовый режим тестирования приводит к возникновению меньших точек утечек, чем в случае дислоцированных окислов в рамках используемых технологических процессов. На стабильные и недислоцированные окисные поверхности на периферии эмиттерного p-n перехода импульсные стрессовые режимы оказывают значительно меньшее влияние и возникающие токи утечки минимальны, и рост базового тока в активном нормальном режиме минимален.

В плане импульсного стрессового воздействия на поверхностные свойства p-n перехода в режиме сверхвысоких плотностей тока используемый инверсный активный режим близок к режиму оборванного коллектора и прямосмещенного эмиттерного перехода, где наблюдается обратная инжекция со дна коллектора.

Сущность изобретения и его отличительные от прототипа признаки заключаются в следующем. В отличие от способа тестирования прототипа на постоянном токе, требующем долговременных испытаний более 104 - 106 с, форсированный импульсный режим испытаний, заключающийся в подаче коротких импульсов тока в активном нормальном и инверсном режимах tи≅3•10-4 с со значительной скважностью прохождения импульсов в цикле тестирования на первой и второй стадиях Q≥104 и сравнение на третьей стадии испытаний вольт-амперных зависимостей базового тока (в полулогарифмическом масштабе Iб=f(Uэб) так называемых кривых Гуммеля) в диапазоне микротоков 10-12 10-6 А, до и после форсированных импульсных стрессовых плотностей тока на эмиттерном контакте J ≥ 2•106 А/см2 в инверсном нормальном режиме (при прямом смещении коллекторного p-n перехода и закороченных электродах эмиттера и базы). Выбором наиболее жесткого режима форсирования индуцированных токов утечки эмиттерного p-n перехода в ходе импульсных стрессовых воздействий в активном инверсном режиме достигается фаза интенсивного токового воздействия на интерфейсную окисную поверхность p-n перехода и в случае значительных несовершенств технологии, дислокаций поверхности, дальнейшего стрессового образования новых центров рекомбинации-генерации тестируются дополнительно вызываемые токи утечки перехода сравнением базовых токов до и после форсированного импульсного стрессового испытания в активном инверсном режиме высоких плотностей тока для основного активного нормального функционирования, по 10%-ному увеличению токов утечки отбраковываются транзисторы с несовершенством окисной поверхности p-n перехода. Технический положительный результат и преимущества предлагаемого метода заключаются в отказе от долговременных испытаний, переходе от постоянных токов тестирования к импульсным с высокой скважностью, а также в более высокой плотности тока тестирования на второй стадии испытаний.

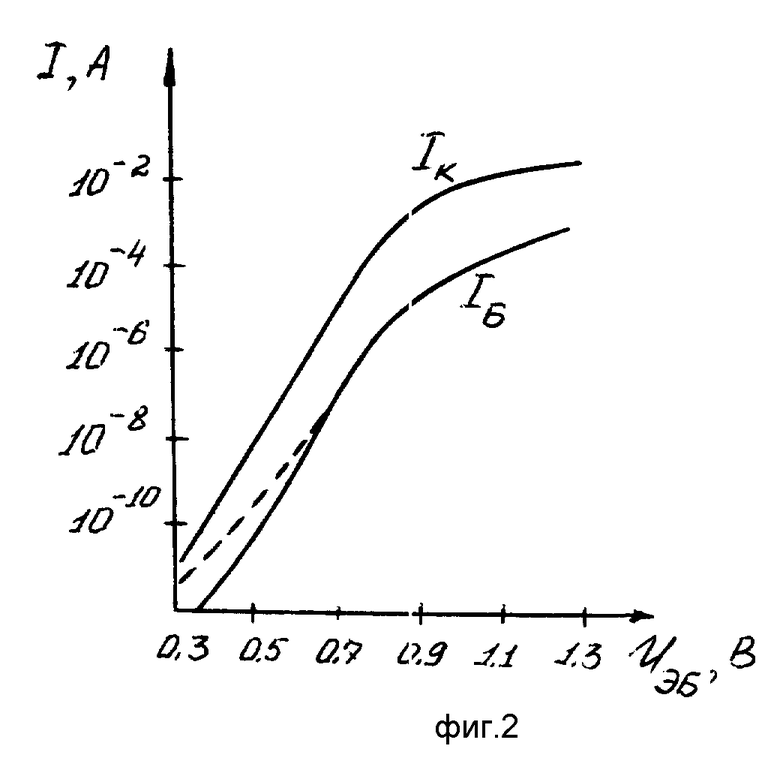

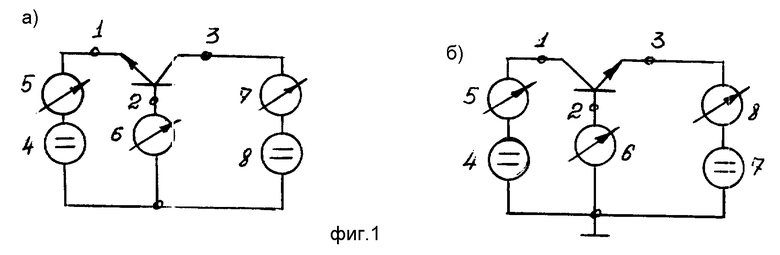

На фиг.1 приведены структурные схемы измерений на первой и второй стадиях тестирования соответственно: а в активном нормальном режиме, б в инверсном нормальном режиме; на фиг. 2 приведены экспериментальные ВАХ коллекторного и базового тока в активном нормальном режиме, причем сплошные кривые соответствуют режиму тестирования до импульсного стрессового с протеканием больших плотностей тока на контакте в инверсном нормальном режиме, а пунктиром обозначена кривая после стрессового испытания.

Исследуемый транзистор на первой стадии включается согласно схеме измерения (фиг. 1,а) подключается клеммами 1-3 соответственно эмиттером, базой и коллектором. Для задания импульсного тока эмиттера через прямосмещенный эмиттерный p-n переход используется практически идеальный источник напряжения 4 (с выходным сопротивлением < 0,1 Ом). В цепях эмиттера, базы и коллектора измеряются токи микроамперметрами 5-7, практически не вносящими омических потерь в измерительных трактах при подключении тестовых транзисторов и приборов. Для единообразия напряжение между базой и коллектором устанавливается равным нулю идеальным источником напряжения 8 (с измерителей тока 7). Для измерения составляющих тока и напряжений смещения в инверсном нормальном режиме используется схема, приведенная на фиг. 1,б, где тестируемый транзистор на второй стадии испытаний подключен своими эмиттером, базой и коллектором к клеммам 1-3. Для создания прямого смещения на коллекторном p-n переходе используется практически идеальный источник напряжения 4 с измерителем тока 5. Для измерения базового тока используется измеритель базового тока 6. Между базой и эмиттером выставляется напряжение равное нулю источником напряжения 7 с измерителем коллекторного тока 8. Измеритель тока не вносит омических потерь в результаты измерений.

Способ тестирования токов утечки реализуется следующим образом. На первой стадии согласно измерительной схеме фиг. 1,а источником напряжения 4 осуществляется пропускание эмиттерного тока через прямосмещенный p-n переход. Величина тока фиксируется измерителем 5. Производятся измерения базового и коллекторного тока измерителями 6, 7, ВАХи измерений Iб, Iк f(Uэб), Uкб 0 в широком диапазоне измерений токов приведены на фиг. 2. Режим подачи напряжений и токов в транзисторе импульсный, длительность импульса tи≅3•10-4 с, скважность Q≥ 104. Основное внимание уделяется измерению токов базы в диапазоне токов 10-12-10-6 А, поскольку влияние токов утечки наиболее характерно именно в этом диапазоне.

Далее на втором этапе происходит импульсный режим тестирования в активном инверсном режиме согласно измерительной схеме фиг. 1,б. Соответственно этой стадии и процедуре испытания реализуется пропускание коллекторного тока через прямосмещенный коллекторно-базовый переход источником 4, измеряются токи эмиттера, базы и коллектора измерителями 5, 6, 8 при Uэб=0 и создании импульсного стрессового режима с длительностью импульса tи ≅3•10-4 с и плотности тока на эмиттерном контакте не менее 2•106 А/см2. Процедуру прохождения токовых стрессовых импульсов со скважностью ≥ 104 можно осуществлять в один или несколько прогонов (единицы десятки). По времени испытаний в ходе стрессовых прогонов это занимает на несколько порядков меньше времени, чем при долговременных испытаниях на постоянном токе, длящихся более чем 104 - 106с в способах аналога и прототипа [1, 2]

После процедуры испытаний в активном инверсном режиме заново повторяют на третьей стадии процедуру измерений ВАХ Iб, Iк=f(Uэб) Uкб=0 (фиг. 1,а) в активном нормальном режиме, где основное внимание уделяется отличию ВАХ токов базы в диапазоне 10-12-10-6 А на первой и второй стадиях. По сравнению ВАХ Iб(Uэб) на третьей стадии (фиг.2) производят отбраковку транзисторов, для которых 10%-ное увеличение базового тока для одинаковых смещений эмиттерно-базового перехода возникает в результате нежелательных стрессовых токовых утечек после проведения второй стадии испытаний. Если ток утечек после проведения второй стадии импульсного режима с реализацией сверхвысокой плотности тока на эмиттерном контакте Jэ=2•106 А/см2 не возникает или их возникновение не превышает 10% то такие транзисторы считаются прошедшими тестовые стрессовые испытания, не отбраковываются и рекомендуются к работе в составе импульсных сверхскоростных схем в диапазоне нормальных рабочих плотностей тока J ; 105 А/см2.

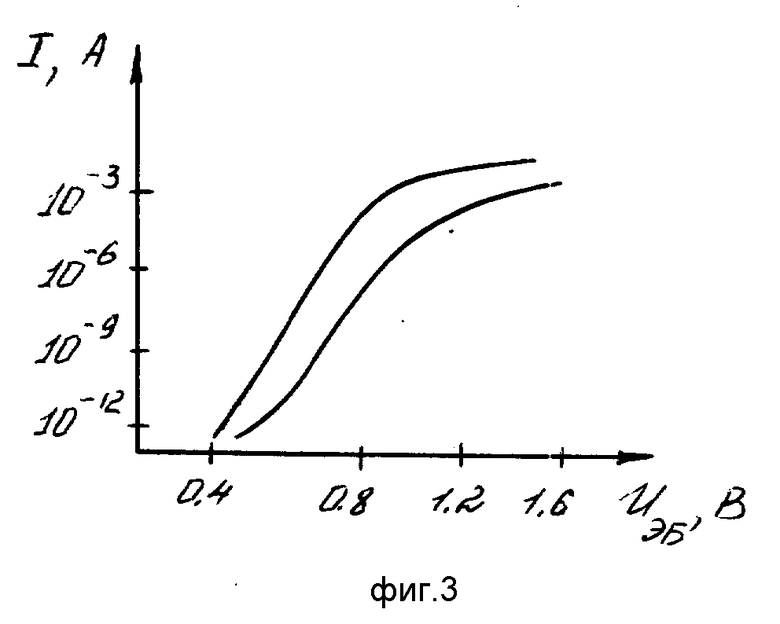

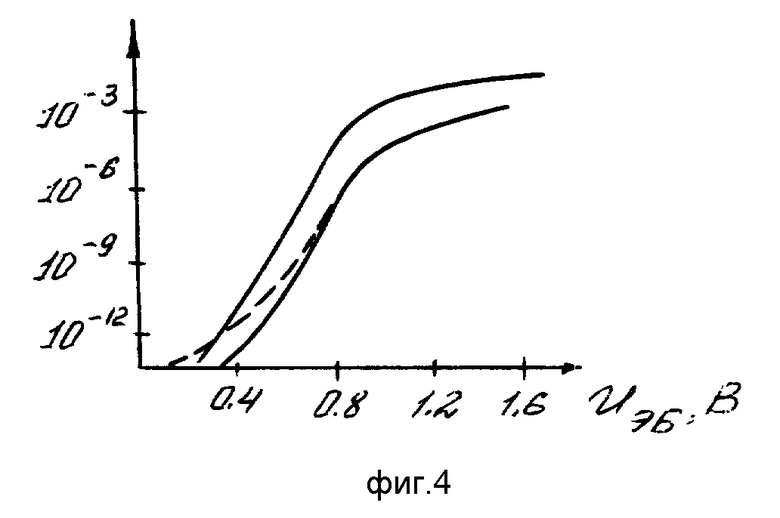

В качестве дополнительного примера реализации способа приведем два семейства ВАХ, прошедшего и не прошедшего испытания транзисторов в результате стрессового тестирования в указанном режиме трехстадийной процедуры. На фиг. 3 приведены ВАХ транзистора, у которого практически нет отличий коллекторного и базового тока (менее 1%) после стрессовых импульсных испытаний. Соответственно на фиг. 4 приведены ВАХ транзистора, у которого отличия базового тока из-за возникновения токов утечки после стрессовых импульсных испытаний значительно превышают норму 10% увеличения. Такой транзистор отбраковывается.

Дополнительно сущность изобретения может быть раскрыта следующим образом. В импульсном стрессовом режиме на второй стадии испытаний происходит усиленная инжекция дна коллекторного перехода и создание в течение очень короткого времени, т.е. длительности импульса tи≅3•10-4 с, очень высокой плотности тока на эмиттерном контакте. Вследствие очень высокой плотности тока ≈ 2•106 А/см2 и высокой энергии электронов, инжектирующих со дна коллектора, в области эмиттерно-базового перехода данные высокоэнергетические электроны способны вызывать значительные нарушения на окисной поверхности p-n переходов (на периферии и боковых его частях, соответственно, создавая локальные центры рекомбинации, приводящие к потенциальной возможности возникновения токов утечки и деградации коэффициента усиления в области микротоков 10-6-1012 А.

Наиболее подвержены возникновению стрессовых токовых утечек именно такие транзисторы, у которых плохая воспроизводимость поверхностных свойств для неотработанных технологических маршрутов с сильным легированием периферийных областей и большой концентрацией донорных и акцепторных примесей у поверхности p-n перехода. Вследствие нерегулярной и невоспроизводимой структуры поверхности эмиттерного p-n перехода априорное (до опыта стрессового инверсного испытания) ухудшение идеальности базового тока (фактор неидеальности базового тока в области микротоков определяется уже поверхностными токами рекомбинации) такие транзисторы более подвержены влиянию стрессовых воздействий в режиме высоких плотностей тока и возникновению значительных токов утечек (фиг. 4).

Технико-экономическая эффективность от использования предлагаемого способа тестирования по сравнению с известными способами заключается в сокращении времени тестирования за счет перехода к импульсному методу пропускания стрессового тока высокой плотности. Использование не долговременных испытаний на постоянном токе, а экспресс-методов тестирования позволяет также значительно улучшить качество тестирования и получить более объективные данные о надежности прибора, факторах его деградации, интенсивности токов утечки и работоспособности прибора в широком режимно-эксплуатационном диапазоне токов и напряжений.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| ЗАПИРАЕМЫЙ ТИРИСТОР И СПОСОБ ЕГО РАБОТЫ | 2007 |

|

RU2335824C1 |

| ТРАНЗИСТОР | 1992 |

|

RU2062531C1 |

| РЕВЕРСИВНО-УПРАВЛЯЕМЫЙ ПОЛУПРОВОДНИКОВЫЙ ПРИБОР | 1986 |

|

RU2006992C1 |

| ИНТЕГРАЛЬНЫЙ БИПОЛЯРНЫЙ ТРАНЗИСТОР | 1989 |

|

SU1831966A3 |

| Способ изготовления биполярных транзисторов | 1988 |

|

SU1544108A1 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2010 |

|

RU2436190C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2479116C1 |

| БИПОЛЯРНЫЙ ТРАНЗИСТОР | 1998 |

|

RU2166220C2 |

| КОМПЛЕМЕНТАРНАЯ БИПОЛЯРНАЯ СХЕМА И - НЕ (ВАРИАНТЫ) | 1993 |

|

RU2094910C1 |

Изобретение относится к области тестирования и измерения параметров полупроводниковых приборов. Сущность изобретения: в способе тестирования токов утечек транзистора на первой стадии пропускают эмиттерный ток через прямосмещенный эмиттерно-базовый p-n переход при закороченных коллекторе и базе. На второй стадии пропускают коллекторный ток через прямосмещенный коллекторно-базовый переход при подключении эмиттера и базы к общей шине. При этом прямое напряжение коллектор - база подают в виде последовательности импульсов со скважностью не менее 104 и длительностью импульса не более 3•10-4 с, с амплитудой, обеспечивающей плотность эмиттерного тока не менее 2•106 А/см2. На третьей стадии повторяют процедуру первой стадии и сравнивают базовые токи в диапазоне 10-12-10-6 А для первой и третьей стадии, после чего по более чем 10%-му увеличению базового тока отбраковывают испытуемые транзисторы. 4 ил.

Способ разбраковки транзисторов по величине токов утечки, включающий пропускание тока через прямосмещенный эмиттерно-базовый переход контролируемого транзистора в схеме с общей базой при нулевом напряжении коллектор-база, измерение базового тока и последующее пропускание тока через прямосмещенный коллекторно-базовый переход контролируемого транзистора в схеме с общей базой при нулевом напряжении эмиттер-база, отличающийся тем, что ток через прямосмещенный коллекторно-базовый переход подают в виде последовательности импульсов со скважностью не менее 104, длительностью импульса не более 3 • 10- 4 и с амплитудой, обеспечивающей плотность эмиттерного тока не менее 2 • 106 A/см2, после чего вновь пропускают ток через прямосмещенный эмиттерно-базовый переход в схеме с общей базой при нулевом напряжении коллектор-база и отбраковывают транзисторы с более чем 10%-ным увеличением базового тока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Watchnik R, Bucelot T., Li G., I.Appl Phys, 1988, N 9, р | |||

| Снеговой плуг | 1926 |

|

SU4734A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Tang D, Hackaoth E, Chen T, IEEE Trans, v | |||

| Пишущая машина | 1922 |

|

SU37A1 |

| Способ очертания зубцов зубчатых колес | 1921 |

|

SU1698A1 |

Авторы

Даты

1997-12-10—Публикация

1992-06-05—Подача