Изобретение относится к устройствам энергонезависимой электрически перепрограммируемой памяти, реализуемым с помощью методов микро- и нанотехнологии.

Известна ячейка матрицы памяти (Мордвинцев В.М., Кудрявцев С.Е., Левин В.Л. Ячейка матрицы памяти. Патент РФ №2263373), включающая проводящую шину первого уровня, выполненную из полупроводника p-типа, перекрещивающуюся с ней проводящую шину второго уровня, разделяющий шины первого и второго уровней слой диэлектрика (диоксида кремния) толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика в областях перекрещивания шин первого и краев шин второго уровней, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду над поверхностью изолирующей щели, обеспечивающую обмен частицами материала с переменной проводимостью. В качестве исходного вещества для материала с переменной проводимостью могут служить либо органические молекулы, адсорбируемые на поверхности изолирующей щели из газовой фазы, либо материал собственно диэлектрика (диоксида кремния) изолирующей щели. В первом случае деструкция органических молекул под действием потока электронов, возникающего при приложении к ячейке напряжения, приводит к образованию частиц проводящей фазы (ЧИФ) углеродистого проводящего материала, во втором - к диссоциации молекул диоксида кремния, удалению кислорода в газовую фазу и обогащению поверхности изолирующей щели остающимися атомами кремния, играющими роль ЧПФ. Накопление ЧПФ сопровождается образованием в изолирующей щели проводящей среды и самоформированием в ней в дальнейшем нанометрового изолирующего зазора (процесс электроформовки), стационарная ширина h которого зависит от приложенного напряжения и определяется балансом процессов возникновения ЧПФ и их термически активируемого исчезновения, происходящего за счет окисления ЧПФ кислородом из газовой фазы («выгорания»). Изолирующий зазор переменной ширины h выполняет функцию элемента памяти. При относительно малом значении напряжения образуется высокопроводящее состояние (ON) элемента памяти с малой (около 1 нм) шириной h зазора. Подача короткого импульса относительно большой амплитуды приводит к увеличению ширины h зазора за счет исчезновения («выгорания») ЧПФ, элемент памяти при этом переводится в низкопроводящее состояние (OFF), поскольку его проводимость определяется туннелированием через изолирующий зазор. Оба состояния сохраняются неограниченно долго при отключенном питании, и переключения между ними возможны многократно, поэтому такой элемент может служить основой для построения устройства энергонезависимой электрически перепрограммируемой памяти. Чтобы соединить такие элементы в матрицу памяти, необходимо обеспечить электрическую развязку их друг от друга, т.е. ячейка матрицы должна иметь выпрямляющую (запирающую при обратном напряжении) вольт-амперную характеристику (ВАХ). Это реализуется за счет использования в качестве нижнего электрода ячейки памяти, являющегося одновременно и проводящей шиной первого уровня, полупроводника p-типа. На границе раздела проводящей среды, расположенной в изолирующей щели, и полупроводника образуется барьер Шоттки, который и обеспечивает выпрямляющую ВАХ ячейки матрицы. Недостатками такой ячейки являются, во-первых, плохие запирающие характеристики барьера Шоттки, связанные с тем, что в поверхность относительно слабо легированного полупроводника упирается расположенная в изолирующей щели проводящая наноструктура, по форме представляющая собой проводящее «нанолезвие», которое создает в полупроводнике локальное увеличение напряженности электрического поля, во-вторых, большие падения напряжения на шине первого уровня, сопротивление которой принципиально нельзя сделать достаточно низким. Все это сильно ограничивает размерность матрицы на основе такой ячейки памяти и уменьшает надежность ее функционирования.

Предложена ячейка матрицы энергонезависимой памяти (Мордвинцев В.М., Кудрявцев С.Е. Ячейка энергонезависимой памяти. Патент РФ №2302058), включающая проводящую шину первого уровня, выполненную из полупроводника p-типа, соединенный с ней полупроводниковый биполярный n-p-n-транзистор, обеспечивающий электрическую развязку ячеек в матрице, причем часть шины первого уровня является одновременно базовой областью транзистора, над которой расположен эмиттер транзистора в виде локальной области с высокой концентрацией носителей из полупроводника n+-типа, перекрещивающуюся с шиной первого уровня проводящую шину второго уровня, расположенный непосредственно под шиной второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика непосредственно над областью с высокой концентрацией носителей, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду, контактирующую с поверхностью изолирующей щели и обеспечивающую обмен частицами материала с переменной проводимостью. В такой ячейке памяти достигается резкое улучшение запирающих характеристик (увеличение пробивных напряжений и уменьшение токов утечки), поскольку они определяются уже обратно смещенным эмиттерным переходом биполярного транзистора. Кроме того, за счет транзисторного эффекта на несколько порядков (пропорционально коэффициенту усиления транзистора по току) уменьшаются токи, протекающие в открытом состоянии по проводящей шине первого уровня, выполненной из полупроводника p-типа, поскольку она включена в базу транзистора, что пропорционально уменьшает падения напряжения на ней. Все это позволяет резко увеличить размерность матрицы памяти и надежность ее функционирования. По совокупности признаков эта ячейка матрицы энергонезависимой памяти наиболее близка к предлагаемым техническим решениям.

Такая ячейка имеет следующий недостаток. В ней область с высокой концентрацией носителей из полупроводника n+-типа выполняет сразу две разнородные функции: она является и эмиттером биполярного транзистора, и нижним электродом изолирующей щели. Поскольку требования к этим функциям не полностью совпадают, такая конструкция не может обеспечить оптимальное выполнение каждой из них и ограничивает характеристики ячейки в целом. В частности, ячейка обладает недостаточно высокой радиационной стойкостью в режиме считывания информации, требует слишком высокого напряжения питания, является очень нетехнологичной при изготовлении ее методами традиционной кремниевой технологии.

Предлагаемая ячейка матрицы позволяет решить следующие технические задачи: достичь высокой радиационной стойкости во всех режимах функционирования матрицы памяти; на несколько вольт уменьшить напряжение питания, что упрощает совместную работу матрицы с современными схемами электронного обрамления; резко улучшить технологичность изготовления матрицы памяти методами традиционной кремниевой технологии, что облегчает ее изготовление на одном чипе со схемами электронного обрамления.

Решение этих технических задач достигается тем, что в предлагаемой ячейке матрицы памяти, включающей проводящую шину первого уровня, соединенную с ней полупроводниковую структуру (например, диод или транзистор), обеспечивающую электрическую развязку ячеек в матрице и содержащую область с высокой концентрацией носителей тока из полупроводника n+- или p+-типа, перекрещивающуюся с шиной первого уровня проводящую шину второго уровня, расположенный непосредственно под шиной второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду, контактирующую с поверхностью изолирующей щели и обеспечивающую обмен частицами материала с переменной проводимостью, в отличие от известной ячейки под изолирующей щелью между слоем диэлектрика и областью с высокой концентрацией носителей тока полупроводниковой структуры расположен дополнительный проводящий элемент, а его форма и размеры таковы, что, соединяя электрически материал с переменной проводимостью в изолирующей щели и область с высокой концентрацией носителей тока, он электрически изолирован от всех других элементов ячейки памяти.

Достигаемый при этом основной технический результат состоит в следующем. Область с высокой концентрацией носителей тока из полупроводника n+- или p+-типа выполняет теперь только традиционную функцию элемента полупроводниковой структуры (например, эмиттера биполярного или истока полевого транзистора) и обеспечивает возможность омического контакта с соответствующим электродом полупроводниковой структуры. Дополнительный проводящий элемент, т.е. элемент из проводящего материала, выполняет функцию нижнего электрода изолирующей щели и обеспечивает электрическое соединение с областью высокой концентрации носителей, поэтому его характеристики (материал, форма, размеры) могут выбираться независимо от полупроводниковой структуры с целью оптимизации свойств ячейки памяти. Форма и размеры дополнительного проводящего элемента обеспечивают его электрическую изоляцию от всех элементов ячейки памяти, кроме материала с переменной проводимостью в изолирующей щели и области с высокой концентрацией носителей, иначе будет нарушено нормальное функционирование ячейки. Введение дополнительного проводящего элемента, в частности, увеличивает радиационную стойкость ячейки памяти в режиме считывания информации, что связано, очевидно, с «отрывом» изолирующей щели, содержащей проводящую среду и изолирующий зазор переменной ширины, от поверхности полупроводника.

В частности, дополнительный проводящий элемент может быть выполнен из нитрида титана. Достигаемый при этом основной технический результат состоит в следующем. Значительно (приблизительно на 1 B) уменьшается пороговое напряжения образования ЧПФ по сравнению с известной ячейкой памяти, что дает возможность на 1-2 B уменьшить амплитуды управляющих импульсов напряжения. Это позволяет уменьшить напряжение питания ячейки памяти на несколько вольт. Изменение порогового напряжения образования ЧПФ, связано, очевидно, с уменьшением высоты потенциального барьера на границе раздела слой диэлектрика - нижний электрод (анод) изолирующей щели при замене его материала с кремния (в известной ячейке) на нитрид титана. Кроме того, улучшается ряд других электрических характеристик, и можно рассчитывать на увеличение стабильности ее функционирования, поскольку нитрид титана обладает более высокой температурой плавления, чем кремний, и практически не окисляется кислородом вплоть до температур около 500°C.

В частности, дополнительный проводящий элемент может включать нижний электрод изолирующей щели в виде слоя, прилегающего к диэлектрику, и дорожку, электрически соединяющую прилегающий к диэлектрику слой и область с высокой концентрацией носителей тока. Достигаемый при этом технический результат состоит в следующем. Нижний электрод изолирующей щели может быть выполнен из оптимального для характеристик ячейки материала, например нитрида титана, а соединяющая проводящая дорожка - из обычных для изготовления многослойной металлизации интегральных микросхем материалов. Это позволяет пространственно оторвать элемент памяти от поверхности кремния, чего нельзя сделать в известной ячейке памяти, и, в частности, вынести его на поверхность многослойной металлизации, исключив необходимость формирования глубоких и узких колодцев в многослойной металлизации, обеспечивающих необходимый контакт изолирующей щели с газовой фазой. При этом резко улучшится технологичность изготовления матрицы памяти с помощью методов традиционной кремниевой технологии.

В частности, слой диэлектрика может быть выполнен из осажденного диоксида кремния. Достигаемый при этом технический результат состоит в упрощении технологии изготовления матрицы памяти с хорошими техническими характеристиками, которые обеспечивает диоксид кремния в качестве исходного вещества для материала с переменной проводимостью. В известной ячейке памяти слой диэлектрика (диоксида кремния) получается путем термического окисления ниже лежащего слоя кремния n+-типа, при этом процесс электроформовки приводит к образованию в изолирующей щели материала с переменной проводимостью, удовлетворяющего всем требованиям к ячейке памяти. В предлагаемой ячейке памяти сформировать слой диоксида кремния над дополнительным проводящим элементом методом термического окисления невозможно, но это можно сделать путем его низкотемпературного осаждения, например плазмохимического. Такие процессы широко используются в традиционной кремниевой технологии, что позволяет упросить технологию изготовления матрицы памяти при сохранении всех достоинств диоксида кремния в качестве слоя диэлектрика ячейки.

В источниках информации не обнаружено сведений, аналогичных предложенной ячейке памяти, что позволяет сделать вывод о ее новизне.

Кроме того, предлагаемое устройство для специалиста явным образом не следует из уровня техники, что подтверждает соответствие предлагаемого технического решения критерию «изобретательский уровень».

Обоснование предлагаемого устройства вместе со сведениями, подтверждающими возможность его осуществления, приводятся ниже с использованием графических материалов.

На фиг.1 схематически показана изолирующая щель в виде открытой «сэндвич»-структуры после выполнения электроформовки. 1 - верхний электрод изолирующей щели (катод); 2 - слой диэлектрика (диоксида кремния) толщиной около 20 нм; 3 - поверхность изолирующей щели в виде открытого торца слоя диэлектрика; 4 - нижний электрод изолирующей щели (анод); 5 - проводящая среда на поверхности изолирующей щели; 6 - изолирующий зазор переменной ширины h (элемент памяти); 7 - газовая среда (среда, контактирующая с поверхностью изолирующей щели и обеспечивающая обмен частицами материала с переменной проводимостью).

На фиг.2 показаны фрагмент матрицы в плане и поперечное сечение ячейки памяти в соответствии с прототипом. 1 - проводящая шина второго уровня и верхний электрод изолирующей щели (вольфрам); 2 - слой диэлектрика (диоксида кремния) толщиной около 20 нм; 3 - поверхность изолирующей щели в виде открытого торца слоя диэлектрика; 4 - область кремния n+-типа, эмиттер транзистора и нижний электрод изолирующей щели; 7 - газовая среда; 8 - область кремния p-типа, проводящая шина первого уровня и база транзистора; 9 - подложка кремния n-типа, коллектор транзистора; 10 - слой толстого (0,5 мкм) диоксида кремния.

На фиг.3 показаны фрагмент матрицы в плане и поперечное сечение предлагаемой ячейки памяти для варианта с биполярным транзистором в качестве полупроводниковой структуры, обеспечивающей электрическую развязку ячеек в матрице. 1 - проводящая шина второго уровня и верхний электрод изолирующей щели (вольфрам); 2 - слой диэлектрика (диоксида кремния) толщиной около 20 нм; 3 - поверхность изолирующей щели в виде открытого торца слоя диэлектрика; 4 - область кремния n+-типа, эмиттер транзистора; 7 - газовая среда; 8 - область кремния p-типа, проводящая шина первого уровня и база транзистора; 9 - подложка кремния n-типа, коллектор транзистора; 10 - слой толстого (0,5 мкм) диоксида кремния; 11 - дополнительный проводящий элемент, нижний электрод изолирующей щели (слой нитрида титана).

На фиг.4 приведены квазистатические ВАХ ячеек памяти с изолирующей щелью в виде открытой «сэндвич»-структуры: (а) - n+Si-SiO2-W (прототип), (б) - TiN-SiO2-W (предлагаемая ячейка). Исходно ячейки находились в состоянии с низкой проводимостью (OFF). J - ток в цепи шины второго уровня (W), U - напряжение между шинами первого (p-Si) и второго (W) уровня. Скорость развертки напряжения 0,5 В/с. На коллекторном переходе транзистора запирающее напряжение 2 B.

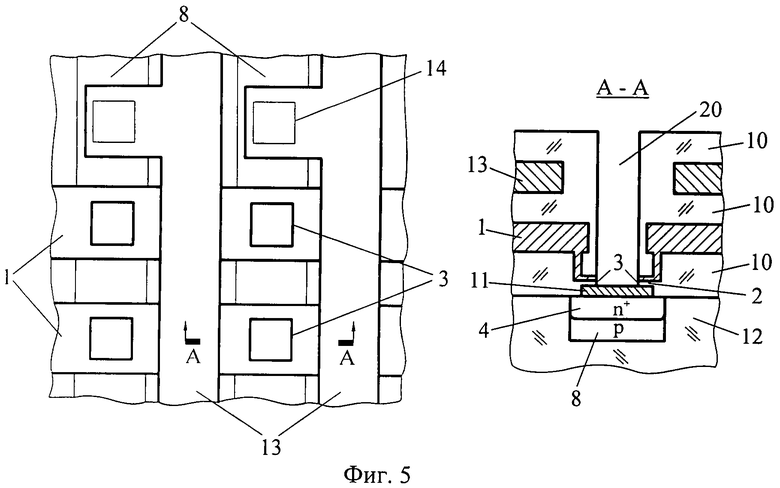

На фиг.5 показаны фрагмент матрицы в плане и поперечное сечение предлагаемой ячейки памяти для варианта с диодом в качестве полупроводниковой структуры, обеспечивающей электрическую развязку ячеек в матрице, выполненным по КНИ-технологии. 1 - проводящая шина второго уровня и верхний электрод изолирующей щели; 2 - слой диэлектрика (диоксида кремния) толщиной около 20 нм; 3 - поверхность изолирующей щели в виде открытого торца слоя диэлектрика; 4 - локальная область кремния n+-типа, эмиттер диода; 8 - область кремния p-типа, проводящая шина первого уровня и база диода; 10 - слои толстого (0,5-1,0 мкм) диоксида кремния; 11 - дополнительный проводящий элемент, нижний электрод изолирующей щели (слой нитрида титана); 12 - изолирующая подложка; 13 - проводящая металлическая шина третьего уровня; 14 - области омического контакта между шинами первого и третьего уровней; 20 - канал в многослойной металлизации, обеспечивающий поступление газовой среды к поверхности изолирующей щели.

На фиг.6 показаны фрагмент матрицы в плане и поперечное сечение предлагаемой ячейки памяти для варианта с полевым транзистором в качестве полупроводниковой структуры, обеспечивающей электрическую развязку ячеек в матрице, выполненным по КНИ-технологии. 1 - проводящая шина второго уровня и верхний электрод изолирующей щели; 2 - слой диэлектрика (диоксида кремния) толщиной около 20 нм; 3 - поверхность изолирующей щели в виде открытого торца слоя диэлектрика; 4 - область кремния n+-типа, исток транзистора; 8 - проводящая шина первого уровня и затвор транзистора (поликремний); 10 - слои толстого (0,5-1,0 мкм) диоксида кремния; 11 - дополнительный проводящий элемент, нижний электрод изолирующей щели (слой нитрида титана); 12 - изолирующая подложка; 15 - область кремния n+-типа, сток транзистора; 16 - область кремния p-типа; 17 - подзатворный диэлектрик; 18 - область омического контакта к стоку; 19 - шина стоков; 20 - канал в многослойной металлизации, обеспечивающий поступление газовой среды к поверхности изолирующей щели.

На фиг.7 показаны фрагмент матрицы в плане и поперечное сечение предлагаемой ячейки памяти для варианта с диодом в качестве полупроводниковой структуры, обеспечивающей электрическую развязку ячеек в матрице, изолирующая щель с элементом памяти вынесена на поверхность многослойной металлизации. 1 - проводящая шина второго уровня и верхний электрод изолирующей щели; 2 - слой диэлектрика (диоксида кремния) толщиной около 20 нм; 3 - поверхность изолирующей щели в виде открытого торца слоя диэлектрика; 4 - локальная область кремния n+-типа, эмиттер диода; 8 - область кремния p-типа, проводящая шина первого уровня и база диода; 10 - слои толстого (0,5-1,0 мкм) диоксида кремния; 11 - нижний электрод изолирующей щели, верхняя часть дополнительного проводящего элемента (слой нитрида титана); 12 - изолирующая подложка; 13 - проводящая металлическая шина третьего уровня; 14 - области омического контакта между шинами первого и третьего уровней; 21 - проводящая дорожка, электрически соединяющая прилегающий к диэлектрику слой (нижний электрод изолирующей щели) и область кремния n+-типа.

Изолирующая щель (фиг.1) выполнена в виде открытой «сэндвич»-структуры, т.е. поверхность изолирующей щели 3 образована открытым торцом слоя диэлектрика 2, расположенного между верхним 1 и нижним 4 электродами. Элемент памяти, т.е. изолирующий зазор 6 переменной ширины h, образуется в процессе электроформовки и является одинаковым и для аналога, и для прототипа, и для предлагаемой ячейки памяти. Электроформовка состоит в подаче на открытую «сэндвич»-структуру напряжения в диапазоне от 0 до 10 B по определенному алгоритму. Поскольку ширина изолирующей щели мала (она определяется толщиной d слоя диэлектрика), в структуре достигаются высокие электрические поля, и по ее поверхности начинает протекать ток, приводящий к деструкции поверхностных молекул диэлектрика (диоксида кремния) при электронном ударе и образованию ЧПФ (атомов кремния), кислород при этом удаляется в газовую среду 7. Накопление ЧПФ приводит к образованию проводящей среды 5, увеличению тока через структуру, разогреву ее поверхности и самоформированию затем изолирующего зазора за счет баланса процессов возникновения ЧПФ при электронном ударе и их термически активируемого исчезновения (окисления кислородом газовой среды, т.е. «выгорания»). Равновесная ширина h изолирующего зазора зависит от приложенного напряжения, но в любом случае она лежит в диапазоне нескольких нанометров и остается постоянной после отключения напряжения, она и определяет проводимость структуры после электроформовки. Поскольку ширину изолирующего зазора можно менять путем подачи импульсов напряжения различной амплитуды и длительности, а проводимость структуры при этом меняется на несколько порядков (механизмом проводимости является туннелирование через нанометровый изолирующий зазор), такой зазор может служить элементом энергонезависимой электрически перепрограммируемой памяти, переключаемым между высоко- и низкопроводящими состояниями. Неразрушающее считывание информации о состоянии такого элемента памяти можно выполнить путем измерения его проводимости при подаче импульса напряжения с амплитудой меньше порогового значения образования ЧПФ (3-4 B), в этом случае проводимость структуры не меняется и переключения состояния не происходит.

В прототипе (фиг.2) открытая «сэндвич»-структура n+Si-SiO2-W с элементом памяти встроена в эмиттер биполярного n-p-n-транзистора, а ее нижним электродом является полупроводник (кремний) n+-типа эмиттерной области 4, электрофизические характеристики которого жестко определены и могут незначительно варьироваться только за счет изменения концентрации донорной примеси в кремнии. Слой 2 тонкого (20 нм) диоксида кремния располагается только над эмиттерной областью, над остальными областями ячейки находится слой толстого (0,5 мкм) диоксида кремния, что позволяет исключить образование инверсных проводящих слоев на поверхности слабо легированных областей полупроводника при подаче управляющих импульсов напряжения, которые могли бы привести к паразитному закорачиванию элементов ячейки памяти. Биполярный n-p-n-транзистор используется для электрической развязки ячеек в матрице, эту функцию выполняет его эмиттерный p-n-переход. Проводящими шинами первого уровня являются области кремния p-типа 8, участки которых под эмиттерами выполняют одновременно функцию базы биполярных транзисторов. Проводящие шины второго уровня 1 перекрещиваются с шинами первого уровня и выполнены из вольфрама. Электрическая изоляция шин p-кремния 8 в матрице друг от друга и от подложки кремния n-типа 9 осуществляется обратно смещенными коллекторными p-n-переходами транзисторов.

В предлагаемой ячейке (фиг.3) под изолирующей щелью между слоем диэлектрика 2 и областью кремния n+-типа введен дополнительный проводящий элемент в виде слоя из нитрида титана 11, который в плане находится полностью внутри эмиттерной области n+-типа, и поэтому электрически изолирован от других элементов ячейки памяти. Кроме функции электрического соединения проводящей среды (материала с переменной проводимостью) в изолирующей щели с n+-областью он выполняет функцию нижнего электрода изолирующей щели, представляющей собой теперь открытую «сэндвич»-структуру TiN-SiO2-W и тем самым определяет новые свойства ячейки памяти.

Ячейки памяти обеих конструкций (фиг.2 и 3) изготавливались параллельно, причем большая часть технологического маршрута и режимов выполнения операций для них совпадали. В качестве подложки 9 использовались пластины монокристаллического кремния n-типа, легированного фосфором до удельного сопротивления 4,5 Ом·см, диаметром 100 мм. Области p-кремния и n+-кремния формировались последовательным локальным легированием исходной подложки сначала бором до слоевого сопротивления 500-700 Ом/□, а затем фосфором до слоевого сопротивления 20 Ом/□. Слой 10 толстого диоксида кремния выращивался термическим окислением подложки. Для конструкции фиг.2 слой 2 тонкого диоксида кремния тоже создавался термическим окислением нижележащего кремния. Для конструкции фиг.3 сначала формировался слой нитрида титана толщиной около 0,1 мкм методом реактивного магнетронного распыления титана в атмосфере азота и в нем методом фотолитографии создавался необходимый рисунок, а затем слой 2 тонкого диоксида кремния получался с помощью низкотемпературного плазмо-химического осаждения. Далее для обеих конструкций технологии изготовления образцов вновь совпадали. Открытые торцы 3 слоя диэлектрика 2 толщиной 20 нм формировались прецизионным жидкостным травлением диоксида кремния с контролем момента окончания процесса емкостным методом, что обеспечивало воспроизводимое получение нужного профиля травления в нанометровом масштабе. Проводящие шины 1 второго уровня создавались из пленки сплава вольфрам-титан (10% титана) толщиной 0,1 мкм. Для обеспечения омического контакта к подложке n-типа при легировании пластин фосфором формировались и соответствующие n+-области. В качестве токоподвода как к шинам обоих уровней, так и к n-подложке использовались тонкопленочные проводники из сплава алюминий-кремний (1% кремния). Рисунок во всех слоях создавался методами контактной фотолитографии. По этой технологии были изготовлены чипы с матрицей памяти размерностью 3×3 ячейки с обоими вариантами конструкции (фиг.2 и 3).

В качестве полупроводниковой структуры, обеспечивающей электрическую развязку ячеек в матрице, можно было использовать и биполярный p-n-p-транзистор, тогда исходная подложка должна была бы быть p-типа, шина первого уровня представляла бы собой область кремния n-типа, а изолирующая щель с элементом памяти встраивалась бы в область кремния p+-типа, которая являлась бы эмиттером транзистора. Однако технология изготовления p-n-p-транзистора более сложна, а его характеристики хуже, чем для n-p-n-транзистора.

Чипы с матрицами памяти разваривались в металлостеклянные корпуса, которые герметизировались в контролируемом вакууме, содержащем кислород. Газовая среда в корпусе с давлением около 100 Па и была той средой, которая контактировала с поверхностью изолирующей щели и обеспечивала обмен частицами материала с переменной проводимостью.

Для варианта конструкции фиг.3 тонкий слой 2 диэлектрика принципиально не мог получаться тем же способом, как и для варианта фиг.2, т.е. термическим окислением нижележащего кремния. Поэтому должно было использоваться низкотемпературное (чтобы не повредить нижний слой нитрида титана) осаждение слоя диэлектрика. Поскольку в предыдущих вариантах ячеек памяти диоксид кремния хорошо зарекомендовал себя как материал поверхности изолирующей щели, который подвергается деструкции при электроформовке с образованием проводящей среды 5, формируя при этом элемент памяти с удовлетворительными свойствами, целесообразно и в предлагаемой ячейке осаждать именно диоксид кремния. С другой стороны, низкотемпературное плазмохимическое осаждение диоксида кремния - это хорошо отработанный и широко применяемый процесс в кремниевой технологии. Поэтому выполнение слоя диэлектрика 2 из осажденного диоксида кремния является оптимальным.

Предлагаемая ячейка памяти продемонстрировала новые улучшенные электрические характеристики. На фиг.4 приведены квазистатические ВАХ ячеек, выполненных в соответствии с фиг.2 и 3. В исходном состоянии ячейки находились в низкопроводящем состоянии (OFF). Полярность напряжения U между шинами (минус на вольфрамовой шине) соответствует открытому состоянию ячейки, поэтому ток J определяется элементом памяти (а не эмиттерным переходом транзистора, как в закрытом состоянии ячейки). При достижении напряжения Uth, физически соответствующего пороговому значению для образования ЧПФ, ячейки быстро переключаются в высокпроводящее состояние (ON) и в дальнейшем остаются в этом состоянии. Первое существенное отличие состоит в том, что величина Uth для ячейки на базе открытой «сэндвич»-структуры TiN-SiO2-W заметно (приблизительно на 0,8 В) меньше, чем для ячейки на базе структуры n+Si-SiO2-W. Поскольку пороговое значение образования ЧПФ определяется величиной потенциального барьера на аноде (нижнем электроде изолирующей щели), это может быть связано с уменьшением потенциального барьера на границе раздела TiN-SiO2 для предлагаемой ячейки по сравнению с границей раздела n+Si-SiO2 для прототипа. От величины Uth зависят, прежде всего, амплитуды управляющих импульсов напряжения: для надежного переключения из состояния OFF в ON («включения») напряжение UON должно быть на 1-2 B больше значения Uth, а для надежного переключения из состояния ON в OFF («отключения») напряжение UOFF должно быть на 1-2 B больше значения UON. Таким образом, этот эффект позволяет значительно уменьшить амплитуду управляющих импульсов напряжения (см. таблицу), а значит, до 5 B может быть уменьшено напряжения питания ячейки (и матрицы) памяти.

Вторым существенным отличием ячеек являются в несколько раз большие токи высокопроводящего состояния (ON) для предлагаемой ячейки. В частности, это приводит к необходимости ограничивать ток (фиг.4б) при снятии квазистатических ВАХ, иначе в ячейке может развиться электрический пробой. Этот эффект связан, очевидно, с меньшим сопротивлением растекания от проводящей среды, расположенной в изолирующей щели и имеющей нанометровые размеры, в нижний электрод. Это сопротивление пропорционально удельному сопротивлению материала электрода, а для нитрида титана оно в 4 раза меньше, чем для n+-кремния. Увеличение тока состояния ON позволяет на порядок увеличить отношение токов высоко- и низкопроводящего состояний (см. таблицу).

Кроме указанных выше, в таблице приведены и другие сравнительные данные для электрических характеристик прототипа и предлагаемой ячейки с дополнительным проводящим элементом из нитрида титана, полученные в результате большого объема измерений, в том числе и в импульсных режимах их функционирования. При переключении из состояния OFF в состояние ON («включение») используется последовательное ячейке памяти сопротивление, ограничивающее ток (и напряжение на ячейке при больших значениях тока), его величина указана в скобках.

Помимо отмеченного выше улучшения электрических характеристик предлагаемой ячейки памяти, существуют и другие достоинства выполнения дополнительного проводящего элемента из нитрида титана. Нитрид титана обладает более высокой температурой плавления (2950°C), чем кремний (1415°C), и очень медленно окисляется кислородом вплоть до температур около 500°C, что приводит к отсутствию подвижности атомов материала нижнего электрода и окисления его частично открытой поверхности кислородом газовой фазы (среды, контактирующей с поверхностью изолирующей щели и обеспечивающей обмен частицами материала с переменной проводимостью) вблизи изолирующей щели, где повышение температуры при переключениях элемента памяти могут достигать нескольких сотен градусов. Это обуславливает более высокую термическую стабильность структуры материала нижнего электрода (в сравнении с кремнием в прототипе) в области, где реализуется электрический контакт к проводящей среде изолирующей щели, а значит, должно приводить к большей стабильности характеристик памяти.

Кроме того, как показали испытания, для предлагаемой ячейки резко увеличивается радиационная стойкость. Ячейка памяти фиг.2 (прототип) обеспечивает нормальное функционирование при накопленных дозах облучения ионизирующей радиацией вплоть до 106 усл.ед. во всех режимах и состояниях, кроме режима невыбранной ячейки матрицы (в нем она оказывается под запирающим напряжением) при считывании информации, если она находится в низкопроводящем состоянии. В этом случае при накопленных дозах уже 105 усл.ед. токи через ячейку увеличиваются на несколько порядков, и ее состояние может стать неотличимым от высокопроводящего, т.е. записанная информация может теряться. Это обесценивает высокую радиационную стойкость ячейки во всех других режимах. Для предлагаемой ячейки (фиг.3) и в этом режиме ее состояние не меняется вплоть до накопленных доз облучения 106 усл.ед. Низкая радиационная стойкость ячейки памяти по прототипу, находящейся под запирающим напряжением, связана, очевидно, с накоплением значительного положительного заряда в слое тонкого диэлектрика (диоксида кремния) при воздействии радиации. Этот заряд приводит к изменению состояния проводимости поверхности полупроводника (n+-кремния), прилегающего к слою тонкого диоксида кремния, в том числе в области вблизи изолирующей щели. Оно не может быть значительным из-за того, что нижний электрод изолирующей щели представляет собой область с высокой концентрацией носителей тока, однако, поскольку изолирующий зазор, определяющий проводимость ячейки памяти, имеет нанометровую ширину, даже небольших изменений состояния поверхности полупроводника оказывается достаточно, чтобы сильно изменить проводимость ячейки памяти. В предлагаемой ячейке изолирующая щель с нанометровым изолирующим зазором «отрывается» от поверхности полупроводника (между ними помещается дополнительный проводящий элемент), поэтому проводимость ячейки становится нечувствительной к воздействию радиации уже во всех режимах и при всех состояниях. Экспериментально этот эффект наблюдался для ячейки конструкции фиг.3 со слоем нитрида титана в качестве дополнительного проводящего элемента, однако он будет работать и в случае выполнения дополнительного элемента из любого другого проводящего материала (но не полупроводника).

В предлагаемой ячейке в качестве полупроводниковой структуры, обеспечивающей электрическую развязку ячеек в матрице, может использоваться не только биполярный транзистор, как это было реализовано в изготовленных образцах матрицы памяти, но и диод (фиг.5), и полевой транзистор (фиг.6), выполненные по любой технологии, в том числе и по технологии КНИ («кремний на изоляторе»). Для случая диода (фиг.5), чтобы уменьшить токи по относительно высокоомной шине первого уровня 8, может использоваться параллельная ей проводящая шина третьего уровня 13, которая выполнена из материала с низким удельным сопротивлением (например, из алюминия) и имеет омические контакты 14 к шине первого уровня в каждой ячейке или через несколько ячеек. Последнее позволяет заметно уменьшить среднюю площадь, занимаемую ячейкой. В случае полевого транзистора (фиг.6) параллельно шине второго уровня 1 и в том же слое проходит шина стоков 19 полевых транзисторов. В любом случае полупроводниковые структуры (диод или транзистор) содержат области полупроводника n+ (или p+)-типа 4 с высокой концентрацией носителей тока, над которой и располагается дополнительный проводящий элемент 11, а на нем уже формируется изолирующая щель с элементом памяти. В полевом транзисторе они могут располагаться как на области стока, так и на области истока. Во всех случаях в открытом состоянии полупроводниковой структуры (и ячейки памяти) ток определяется элементом памяти, а в запертом состоянии - самим полупроводниковым прибором.

Принципиальной особенностью ячейки памяти является необходимость доступа газовой среды к открытой поверхности изолирующей щели. Поскольку в современных интегральных схемах используется, как минимум, два - три слоя металлизации, в конструкциях ячейки фиг.5 и 6 необходимо формировать узкие и глубокие (минимум несколько микрометров глубиной) колодцы 20, что уменьшает плотность записи информации в матрице и сильно усложняет технологию. В то же время введение дополнительного проводящего элемента позволяет в принципе «оторвать» изолирующую щель с элементом памяти от поверхности полупроводника и - за счет формы и размеров дополнительного проводящего элемента - расположить их на любом расстоянии друг от друга. В том числе, изолирующую щель можно вынести на поверхность многослойной металлизации, предусмотрев ее электрическое соединение с поверхностью полупроводника, как это показано на фиг.7 для варианта ячейки памяти с диодом в качестве полупроводниковой структуры, обеспечивающей электрическую развязку ячеек в матрице. Это исключает проблемы, связанные с необходимостью формировать узкие и глубокие колодцы. Поскольку дополнительный проводящий элемент выполняет две функции: является нижним электродом изолирующей щели и одновременно обеспечивает электрическое соединение этого электрода с областью полупроводника с высокой концентрацией носителей, целесообразно, чтобы он включал две части (11 и 21), каждая из которых обеспечивает оптимальное выполнение своей функции за счет наиболее подходящих формы и материалов. В частности, нижний электрод 11 изолирующей щели целесообразно изготовить в виде слоя из нитрида титана, а соединяющую его с поверхностью полупроводника проводящую дорожку 21 - по той же технологии, которая применяется для создания многослойной металлизации.

Таким образом, приведенные данные демонстрируют для предложенной ячейки памяти достижение всех заявленных технических задач.

Предлагаемая ячейка энергонезависимой электрически перепрограммируемой памяти апробирована в Ярославском филиале ФТИАН.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕМЕНТ ЭНЕРГОНЕЗАВИСИМОЙ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОЙ ПАМЯТИ | 2016 |

|

RU2637175C2 |

| ЯЧЕЙКА МАТРИЦЫ ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2005 |

|

RU2302058C2 |

| ЯЧЕЙКА МАТРИЦЫ ПАМЯТИ | 2004 |

|

RU2263373C1 |

| Способ электроформовки при изготовлении элемента памяти | 2020 |

|

RU2769536C1 |

| ЯЧЕЙКА ПАМЯТИ СО СТРУКТУРОЙ ПРОВОДЯЩИЙ СЛОЙ-ДИЭЛЕКТРИК-ПРОВОДЯЩИЙ СЛОЙ | 2007 |

|

RU2376677C2 |

| ВСТРАИВАЕМАЯ С СБИС ТЕХНОЛОГИИ КМОП/КНИ ПАМЯТЬ "MRAM" И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ (ВАРИАНТЫ) | 2012 |

|

RU2532589C2 |

| УСТРОЙСТВО ПАМЯТИ И СПОСОБ ИЗГОТОВЛЕНИЯ | 2001 |

|

RU2247441C2 |

| КОНСТРУКЦИЯ ЯЧЕЙКИ ПАМЯТИ С ВЕРТИКАЛЬНО РАСПОЛОЖЕННЫМИ ДРУГ НАД ДРУГОМ ПЕРЕСЕЧЕНИЯМИ | 1997 |

|

RU2156013C2 |

| УСТРОЙСТВО ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2008 |

|

RU2374704C1 |

| Ячейка оперативной памяти | 2024 |

|

RU2826859C1 |

Изобретение относится к устройствам энергонезависимой электрически перепрограммируемой памяти, реализуемым с помощью методов микро- и нанотехнологии. Сущность изобретения: ячейка энергонезависимой электрически перепрограммируемой памяти включает проводящую шину первого уровня, соединенную с ней полупроводниковую структуру (например, диод или транзистор), обеспечивающую электрическую развязку ячеек в матрице и содержащую область с высокой концентрацией носителей тока из полупроводника n+- или р+-типа, перекрещивающуюся с шиной первого уровня проводящую шину второго уровня, расположенный непосредственно под шиной второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду, контактирующую с поверхностью изолирующей щели и обеспечивающую обмен частицами материала с переменной проводимостью. Под изолирующей щелью между слоем диэлектрика и областью с высокой концентрацией носителей тока полупроводниковой структуры расположен дополнительный проводящий элемент из нитрида титана, электрически изолированный от всех других элементов ячейки памяти. Техническим результатом изобретения является уменьшение напряжения питания, увеличение радиационной стойкости и улучшение технологичности изготовления ячейки памяти методами традиционной кремниевой технологии. 3 з.п. ф-лы, 7 ил., 1 табл.

1. Ячейка матрицы памяти, включающая проводящую шину первого уровня, соединенную с ней полупроводниковую структуру (например диод или транзистор), обеспечивающую электрическую развязку ячеек в матрице и содержащую область с высокой концентрацией носителей тока из полупроводника n+- или р+-типа, перекрещивающуюся с шиной первого уровня проводящую шину второго уровня, расположенный непосредственно под шиной второго уровня слой диэлектрика толщиной от 3 до 100 нм, изолирующую щель в форме открытого торца слоя диэлектрика, находящийся в изолирующей щели материал с переменной проводимостью, меняющейся при прохождении через него потока электронов, и среду, контактирующую с поверхностью изолирующей щели и обеспечивающую обмен частицами материала с переменной проводимостью, отличающаяся тем, что под изолирующей щелью между слоем диэлектрика и областью с высокой концентрацией носителей тока полупроводниковой структуры расположен дополнительный проводящий элемент, а его форма и размеры таковы, что, соединяя электрически материал с переменной проводимостью в изолирующей щели и область с высокой концентрацией носителей тока, он электрически изолирован от всех других элементов ячейки памяти.

2. Ячейка матрицы памяти по п.1, отличающаяся тем, что дополнительный проводящий элемент выполнен из нитрида титана.

3. Ячейка матрицы памяти по п.1, отличающаяся тем, что дополнительный проводящий элемент включает нижний электрод изолирующей щели в виде слоя, прилегающего к диэлектрику, и дорожку, электрически соединяющую прилегающий к диэлектрику слой и область с высокой концентрацией носителей тока.

4. Ячейка матрицы памяти по любому из пп.1 и 2, отличающаяся тем, что слой диэлектрика выполнен из осажденного диоксида кремния.

| ЯЧЕЙКА МАТРИЦЫ ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ | 2005 |

|

RU2302058C2 |

| ЯЧЕЙКА МАТРИЦЫ ПАМЯТИ | 2004 |

|

RU2263373C1 |

| ЭЛЕМЕНТ УСТРОЙСТВА ПАМЯТИ СО СТРУКТУРОЙ МЕТАЛЛ - ИЗОЛЯТОР - МЕТАЛЛ | 1994 |

|

RU2072591C1 |

| Валиев К.А | |||

| и др | |||

| Память на основе нано-МИМ-диода с углеродистой активной средой | |||

| Микроэлектроника, 1997, т.26, №1, с.3-11 | |||

| Установка для вакуумного транспортирования сыпучих материалов | 1981 |

|

SU948816A1 |

Авторы

Даты

2011-12-10—Публикация

2010-04-13—Подача