Изобретение относится к вычислительной технике и необходимо для изучения программно-управляемых цифровых устройств, реализованных в матричной логике.

Известны многофункциональные электрически программируемые логические матрицы (см. например, паспорт на микросхему КМ l556 XII8, 1988), включающие последовательно соединенные логические матрицы И, НЕ-И, ИЛИ, регистры обратной связи.

Готовые изделия не позволяют наглядно изучать структуру и микропрограммы программируемых логических матриц из-за высокой интеграции элементов на монолитной полупроводниковой подложке, поэтому промышленные образцы не пригодны для создания микротренажеров и для обучения операторов архитектуре матричных структур.

Известны тренажеры на светодиодных матрицах с моделированием цифровых блоков на ЦВМ [1]

Недостатками этих технических решений являются высокая сложность, низкая эффективность и отсутствие наглядности при изучении программного управления цифровых объектов. Недостатки определяются использованием мощных ЦВМ для моделирования элементарных алгоритмов и отсутствием диалогового режима между ЦВМ и оператором.

За прототип принят тренажер комбинаторных логических схем, содержащий регистр адреса и информационные регистры, соединенные с ЦВМ дешифратор и матричный индикатор, состоящий из матрицы светодиодов, инверторов и двух групп коммутирующих гнезд [2]

Тренажер удобен при изучении аппаратных средств цифровой техники, реализованной в комбинаторной логике, но не позволяет изучать функционирование элементов и непрактичен при обучении микропрограммному управлению цифровых элементов на базе матричной логики. Это вызвано отсутствием диалогового режима между ЦВМ и обучающимся, а также конструированием матрицы индикаторов на элементах комбинаторной логики и дискретных точечных светодиодах.

Имитационное моделирование требует мощного программного обеспечения, что приводит к нерациональному использованию программных, аппаратных и интеллектуальных ресурсов. Применение мощных ЦВМ для моделирования пакета элементарных алгоритмов низкоэффективно и непроизводительно, т.к. не позволяет применить системное программирование на языках высокого уровня, а инициирует написание программ на уровне микропрограммирования. Кроме того, как бы ни был высок уровень имитационного моделирования, моделируемый объект остается лишь копией натурного образца и не позволяет преодолеть психологический барьер в процессе обучения.

Следовательно, тренажеры с использованием ЦВМ для управления светодиодными матрицами не эффективны при имитационном моделировании программируемых логических матриц на уровне аппаратных средств и микропрограммного обеспечения, т. е. известные решения имеют низкие дидактические возможности для изучения архитектуры цифровых средств, реализованных на матричной логике.

В данном изобретении достигается расширение дидактических возможностей тренажера за счет изучения архитектуры матричной логики на уровне микропрограммного управления, а также сокращение аппаратурных затрат светодиодной матрицы.

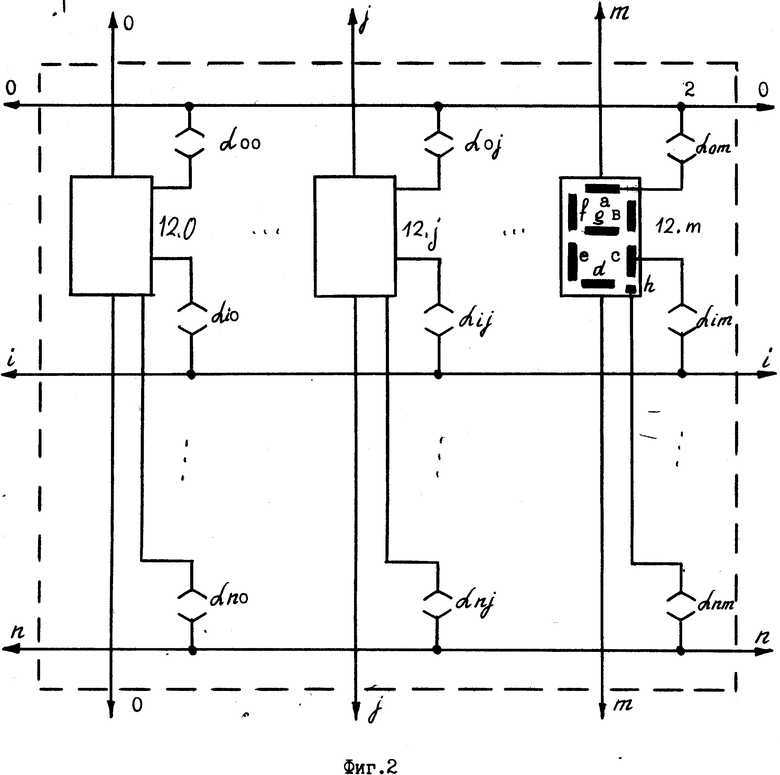

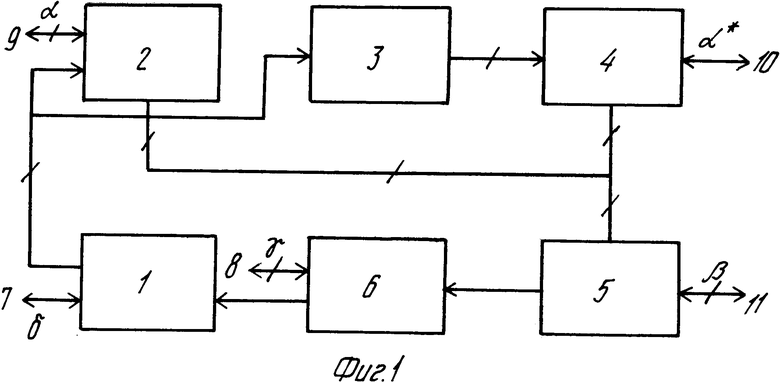

На фиг. 1 и 2 приведены структурные схемы соответственно тренажера и матричного индикатора; на фиг. 3 дан пример программирования.

Тренажер содержит первый информационный регистр 1, первый матричный блок коммутации и индикации, условно представленный в виде частей 2 и 4, реализующих каждая матрицу элементов И, группу 3 элементов НЕ, второй матричный блок 5 коммутации и индикации, собранный по схеме светодиодной матрицы ИЛИ, второй информационный регистр 6. Разрядность информационных регистров 1 и 6 определяется числом разрядов шины строк соответственно первого и второго матричных блоков 2 (4) и 5. На фиг. 1 обозначены первые и вторые группы 7, 6 адресных входов, а также группы 9-11 входов коммутации.

Матричный блок 2 (4) реализует матрицы (фиг. 2) двухкоординатного типа мощностью mxn, где n и m соответственно разрядность строк и столбцов матрицы. Каждая матрица включает по числу разрядов в столбце m сегментных индикаторов 12. Одноименные сегменты  индикаторов 12 соединены с соответствующими разрядами

индикаторов 12 соединены с соответствующими разрядами  шины строк матрицы через две группы коммутирующих гнезд αij гдеi}n иj}m i-я строка и j-й столбец матрицы. Светодиоды матрицы организуют на сегментах ij индикаторов 12, причем сегменты выполняют функцию катодов, а подложка индикаторов анодов светодиодов матричного индикатора.

шины строк матрицы через две группы коммутирующих гнезд αij гдеi}n иj}m i-я строка и j-й столбец матрицы. Светодиоды матрицы организуют на сегментах ij индикаторов 12, причем сегменты выполняют функцию катодов, а подложка индикаторов анодов светодиодов матричного индикатора.

Второй матричный блок 5 идентичен схеме первого блока 2 и имеет мощность mxl координат. Адресные входы матриц образованы двумя группами коммутирующих гнезд с номерами αij для части 2 первого блока, α

Регистр 6 служит для хранения и вывода результатов с выхода шины строк матричного блока 5, а также для коммутации выходных данных на вход тренажера при организации обратной связи. Обратная связь используется для создания и исследования последовательностных цифровых схем (триггеров, счетчиков, регистров и т.д.). При отсутствии обратной связи тренажер позволяет систематизировать и изучать комбинационные логические преобразователи (логические элементы, дешифраторы, мультиплексоры и т.п.). Коммутация информации через регистр 6 осуществляется по адресной шине {γk}

Аналогично управляется регистр 1 по адресной шине {δi}

где

Коммутация матричных блоков 2 (4) и 5 может быть электронной, электромеханической и механической. В предлагаемом техническом решении использована механическая коммутация как наиболее наглядная для развития моторной памяти. Коммутация адресных шин {αij,α

В исходном состоянии коммутационные гнезда αij,α

Тренажер позволяет синтезировать различные матричные схемы в соответствии с алгоритмом работы программируемой логической матрицы (см.Герасимов Б. И. Глинкин Е.И. Микропроцессорные аналитические приборы. М. Машиностроение, 1969, с.150)

где Ai= δiai информация в регистре 1.

Реализовать схему на тренажере можно по структурной формуле, временной диаграмме или таблице в соответствии с логической задачей. Как видно из выражения (1), можно синтезировать необходимую функцию посредством задания адреса {αij,α

Обучаемый собирает схему (например, по таблице истинности), замыкая штекеры в соответствии с мнемоническим правилом:

в матрице 2 штекеры устанавливаются по адресам αij, соответствующим значениям "I",

в матрице 4 штекеры фиксируются по адресам α

на матрице 5 штекерами коммутируют адреса βjk, соответствующие лишь значениям "I".

Матрицам И блока 2, 4 сопоставляют таблицу входных переменных {Ai}

Рассмотрим программирование тренажера на примере элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, его структурная формула:

таблица истинности приведена на фиг. За. ПеременнымA0, A1} поставлены в соответствие строкиа, в;  } матриц 2 и 4, выходные данные пусть коммутируются на разрядыf0, f1, f2} матрицы ИЛИ. По таблице истинности построена схема матрицы (фиг. 3б). Единицы на входной таблице i•j (фиг. За) заменены точками на схеме. ЗначениямA01 A03 A12 A13 1} соответствуют координатыa1, a3, b2, b3} (фиг. 3б). Для инверсных значенийA00 A02 A10 A11 0} (фиг. За) отмечены соединения с координатами

} матриц 2 и 4, выходные данные пусть коммутируются на разрядыf0, f1, f2} матрицы ИЛИ. По таблице истинности построена схема матрицы (фиг. 3б). Единицы на входной таблице i•j (фиг. За) заменены точками на схеме. ЗначениямA01 A03 A12 A13 1} соответствуют координатыa1, a3, b2, b3} (фиг. 3б). Для инверсных значенийA00 A02 A10 A11 0} (фиг. За) отмечены соединения с координатами  (фиг. 3б). На фиг. 3в приведены коммутационные колодки матрицы, со штекерами, реализующими функцию (2) согласно схеме матрицы, представленной фиг. 3б. Координатамa1, a3, b2, b3} соответствуют адреса {α01,α03,α12,α13} на матрице 2, координатам

(фиг. 3б). На фиг. 3в приведены коммутационные колодки матрицы, со штекерами, реализующими функцию (2) согласно схеме матрицы, представленной фиг. 3б. Координатамa1, a3, b2, b3} соответствуют адреса {α01,α03,α12,α13} на матрице 2, координатам  поставлены в соответствие адреса {α

поставлены в соответствие адреса {α

Для приведенного примера выражение (1) имеет вид:

а с учетом равенства указанных координат логической единице, находим

что соответствует минтермам таблицы истинности (см. фиг. 3а)

При замене Ai= δiai для δi= 1 получаем:

т. е. выражения (5) и (2) идентичны, что подтверждает соответствие между структурной формулой (1) и схемой светодиодной матрицы, реализованной на тренажере (фиг. 3в).

Обучаемый может анализировать работу скоммутированной на тренажере матричной схемы посредством задания значений входных переменных по таблице истинности. Реакцию схемы наблюдают по индикации сегментов знаковых индикаторов матрицы 2, 4 и 5. Значению "логическая единица" соответствует светящийся сегмент, темные сегменты обозначают наличие нулевого потенциала. Так как сегменты расположены согласно адресным входам матриц, обучаемый получает наглядную информацию о состоянии в межузловых соединениях программируемой матрицы для любых значений входных минтермов. При появлении положительного потенциала на выходах {fk}

Высокая наглядность и простота обращения позволяют анализировать и синтезировать цифровые устройства матричной логики на уровне схем и микропрограмм. Диалоговый режим обучаемого и микротренажера развивает моторную память и позволяет понять сущность работы цифровых матричных схем, что в итоге повышает качество обучения на порядок в отличие от известных решений.

Сравним по аппаратурным затратам предлагаемый матричный индикатор с прототипом, предполагая, что они имеют одинаковую мощность 3mn. В прототипе необходимо использовать S1 3mn светодиодов, а в предлагаемом решении S2 3m сегментных индикаторов. Из сопоставления S1 и S2 видно, что прототип содержит в n раз больше аппаратных средств, чем предлагаемая матрица.

Таким образом, использование сегментных индикаторов для реализации функций логического умножения и сложения в отличие от известных технических решений в n раз сокращает аппаратурные затраты и позволяет изучать архитектуру матричных цифровых устройств на уровне микропрограммного управления, что в итоге расширяет дидактические возможности тренажера программируемых логических матриц.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕНАЖЕР МНЕМОСХЕМ | 1990 |

|

RU2101772C1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1994 |

|

RU2116674C1 |

| СПОСОБ КОМПЛЕКСНОГО ОПРЕДЕЛЕНИЯ ТЕПЛОФИЗИЧЕСКИХ ХАРАКТЕРИСТИК МАТЕРИАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2027172C1 |

| СПОСОБ ОБМЕНА ИНФОРМАЦИИ В МИКРОКАЛЬКУЛЯТОРНОЙ СЕТИ И МИКРОКАЛЬКУЛЯТОРНАЯ СЕТЬ ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2015545C1 |

| Устройство для ввода информации | 1986 |

|

SU1376076A1 |

| Устройство для отображения информации | 1974 |

|

SU491141A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| Устройство для индикации | 1986 |

|

SU1381586A1 |

| Устройство для индикации | 1990 |

|

SU1795513A1 |

Изобретение относится к вычислительной технике. Его использование позволяет расширить дидактические возможности тренажера за счет изучения матричной логики на уровне микропрограммного управления. Тренажер содержит информационные регистры 1, 6, матричный блок коммутации и индикации, состоящий из двух частей 2 и 4. В тренажер введены группа 3 элементов НЕ и матричный блок 5 коммутации и индикации, причем в качестве элементов индикации используются сегментные индикаторы. 1 з.п. ф-лы, 3 ил.

через (i, j)-й элемент коммутации соединен с i-м разрядом шины строк блока.

через (i, j)-й элемент коммутации соединен с i-м разрядом шины строк блока.

| SU, авторское свидетельство, 430432, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| SU, авторское свидетельство, 1429150, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1998-01-20—Публикация

1990-12-25—Подача