Изобретение относится к вычислительной технике и телеавтоматике, в частности к обучающим системам, построенным на микрокалькуляторах, и предназначено для организации обучения программированию.

Целью изобретения является повышение информативности обмена информации в микрокалькуляторной сети.

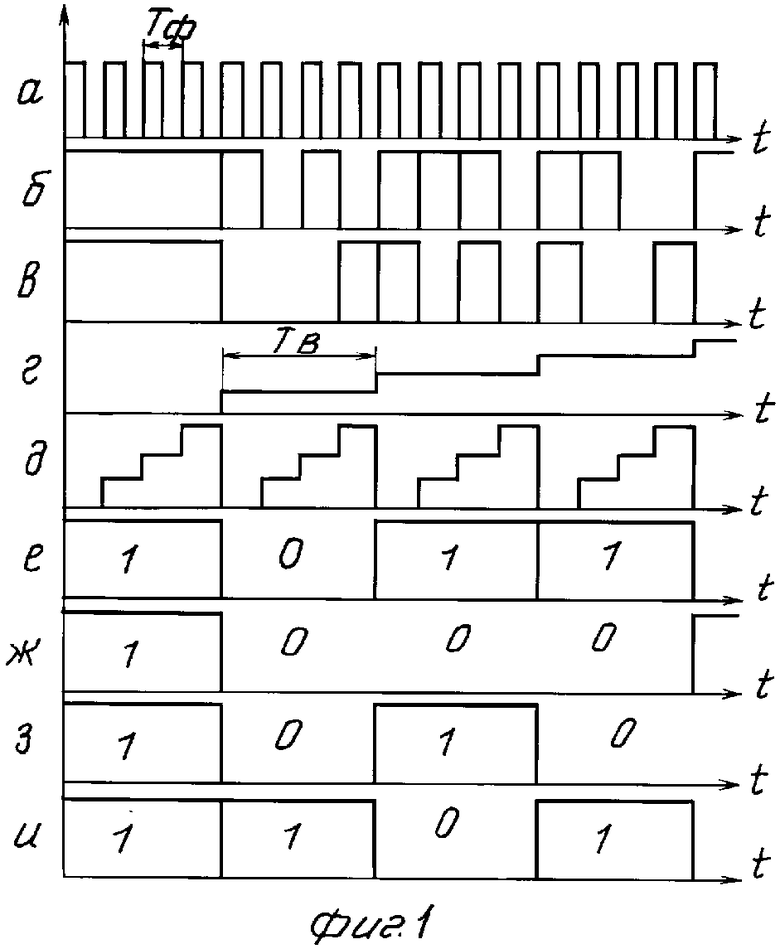

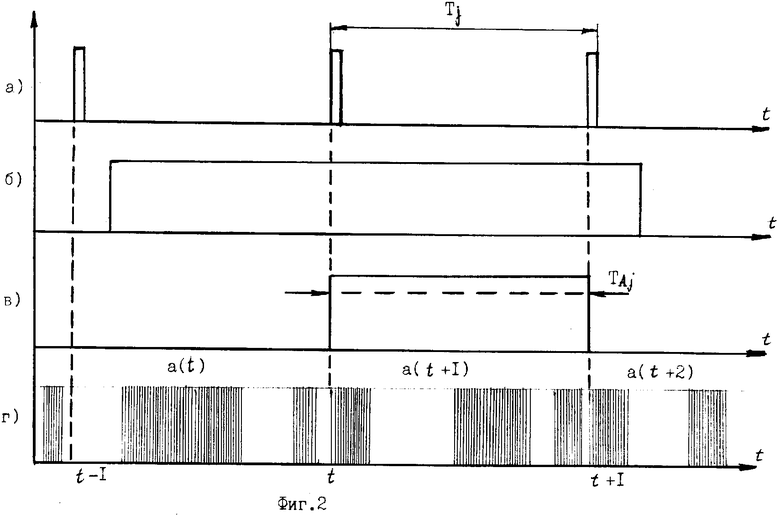

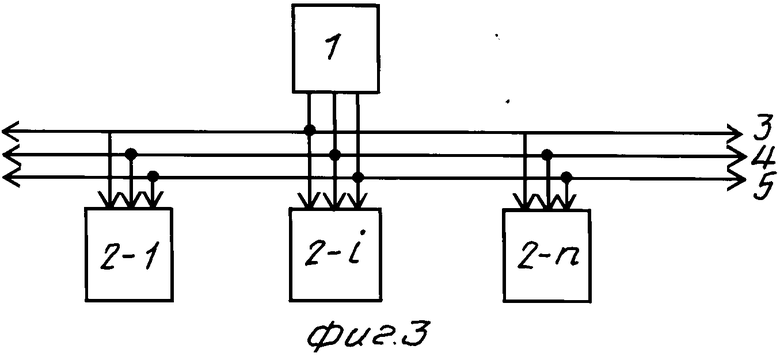

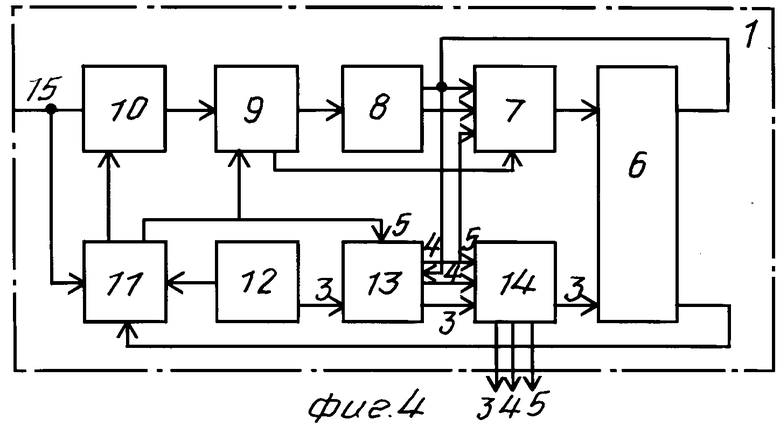

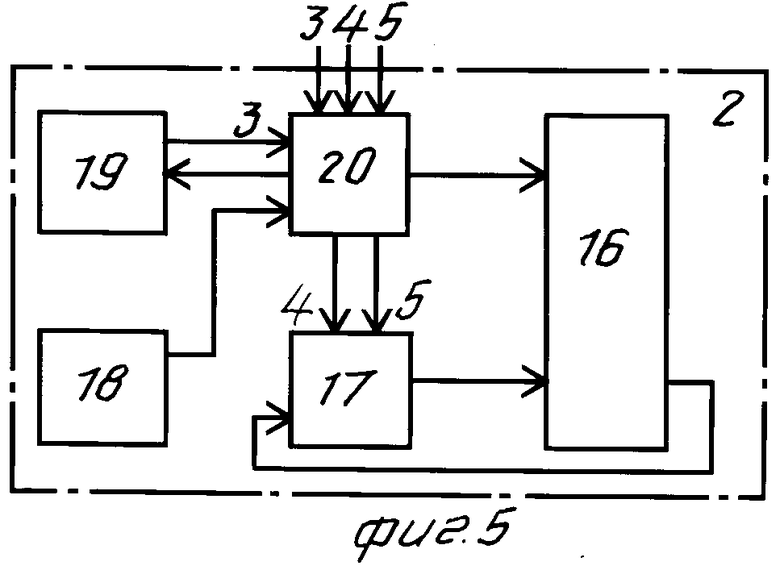

Способ обмена информацией поясняется диаграммами на фиг.1 и 2 и структурной схемой микрокалькуляторной сети на фиг. 3, организованной в виде программируемого учебного класса; на фиг.4 и 5 приведены структурные схемы центрального и периферийного пультов.

Микрокалькуляторная сеть (фиг. 3) состоит из центрального пульта 1 (пульта преподавателя) на старшем иерархическом уровне и пультов 2-1- 2-n периферии (пультов учащихся) на младшем уровне. Сеть содержит шины синхронизации 3 из четырех разрядов, информации 4 и управления 5 по одному разряду.

Центральный 1 пульт (фиг. 4) включает микрокалькулятор 6, мультиплексор 7, блок 8 памяти, счетчик 9 адреса, логический вентиль 10, формирователь 11 импульсов, генератор 12 фаз (составная часть микрокалькулятора), усилитель 13 мощности и шинный разъем 14 для подключения к шинам 3-5, а также вход 15 записи информации.

Периферийный пульт 2 (фиг. 5) организован на микрокалькуляторе 16, мультиплексоре 17, генераторе 18 фаз (составной части микрокалькулятора 16), коммутационный 19 и шинный 20 разъемы одного типа. Через шинный разъем 20 пульты 2-1 - 2-n связаны с шинами 3-5 в микрокалькуляторную сеть.

Сущность предлагаемого способа обмена информацией в микрокалькуляторной сети состоит в формировании последовательности адресных импульсов соответственно временным интервалам (фиг. 1г, д) периода ТAj (фиг. 2в) полного перемещения исходной информационной последовательности а(t) импульсов (фиг. 2г, 1б). На фиг. 1а показана одна из фазовых частот тетрады фаз с периодом Тф тактирования последовательности адресных импульсов Вn (фиг. 2г) и исходной информационной последовательности импульсов в момент времени (t+0), циркулирующей в кольце оперативной памяти периферийных 2 и центрального 1 пультов калькуляторов 6 и 16. Во время t+j осуществляют замещение исходной а(t) на заданную (оригинальную) а(t+j) информационную последовательность (фиг. 1в и 2г). При этом числоимпульсная последовательность а(t+j) замещает исходную а(t) по тетраде с оригинала N(A), представленного в параллельном коде (фиг. 1е-и) 1-2-4-8 в двоично-десятичной форме. Перемещение исходной а(t) и заданной а(t+j) информационной последовательности импульсов осуществляют синхронно импульсам тетрады Ф14 фазовых частот. Одной из фазовых частот (например, второй Ф2) организуют последовательность адресных импульсов, которой управляют по программе в течение управляющего импульса ТAj. Длительность импульса ТAj выбирают равной времени заданного периода Тj (фиг. 2а) полного перемещения информационной последовательности импульсов, соответствующему периоду одного машинного цикла.

Управляющий импульс ТAj формируется на старшем иерархическом уровне пультом 1 преподавателем и по одноразрядной шине 5 управления поступает на соответствующие входы пультов 2-1-2-n учащихся младшего иерархического уровня (фиг. 3). В течение импульса ТAj осуществляется замещение информационной последовательности импульсов а(t) на заданную последовательность а(t+j), поступающую по информационной шине 4 с центрального 1 на периферийные 2 пульты. Смещение информационной последовательности в интервалы времени t+i для i ≠ j, i=0, 1, 2, ..., и в момент t+j ее замещения при i=j осуществляется тетрадой Ф14 фазовых импульсов, поступающих из центрального пульта 1 на периферийные пульты 2 по четырехразрядной шине 3 синхронизации.

Фазовые импульсы формируются генератором 12 микрокалькулятора 6 пульта 1 (фиг.4). Эти импульсы после усилителя 13 мощности через шинный разъем 14 тактируют смещение информационной последовательности в микрокалькуляторе 6 пульта 1. Одновременно фазовые импульсы поступают через шину 3 синхронизации и шинный разъем 20 на соответствующие входы микрокалькулятора 16 пультов 2 и осуществляют в них смещение информационной последовательности синхронно центральному пульту 1.

В пульте 1 информационная последовательность импульсов циркулирует по информационной одноразрядной шине с выхода микрокалькулятора 6 через первый информационный вход мультиплексора 7 на вход микрокалькулятора 6 (в периферийных пультах соответственно через блоки 16 и 17). В исходном режиме на входе разрешения мультиплексоров 7 и 17 присутствует нулевой потенциал (фиг. 2в), по которому на выход мультиплексоров коммутируется первый канал. Кроме того, на входе 15 записи присутствует нулевой потенциал (фиг. 2б), закрывающий логический вентиль 10 и формирователь 11 импульсов. Счетчик 9 адреса и блок 8 памяти отключены, а микрокалькуляторы 6 и 16 функционируют автономно.

Принудительный режим замещения информационной последовательности инициируется оператором центрального пульта 1 подачей импульса положительной полярности (фиг. 2б) на вход 15. При этом формирователь 11 из импульсов с периодом Тj (фиг. 2а) генерирует управляющий импульс ТAj(фиг. 2в). На первом выходе формирователя 11 появляются импульсы Ф2генератора 12, которые через вентиль 10 поступают на счетный вход счетчика 9 адреса в течение времени ТAj. Фронтом управляющего импульса счетчик 9 обнуляется (фиг. 1г, д) и формирует на выходных шинах последовательность адресных импульсов синхронно интервалам A(j) времени. Из блока 8 памяти информация в параллельном четырехразрядном коде (фиг. 1е-и) преобразуется потетрадно в числоимпульсную заданную информационную последовательность a(t+j) копии (фиг. 1в). Соответственно интервалам Aj времени в динамической памяти микрокалькулятора 6 через мультиплексор 7 замещается исходная на заданную информационная последовательность за время действия управляющего импульса. Замещение информационной последовательности в периферийных пультах осуществляется аналогично посредством блоков 16 и 17.

Блок 8 памяти может быть выполнен на постоянных, репрограммируемых и оперативных запоминающих устройствах с возможностью обмена информации между блоками 6 и 8.

При отключении от сети шинный разъем 20 замыкается коммутационным разъемом 19, соединяющим шины генератора 18 фаз с входами синхронизации микрокалькулятора 16, а вход мультиплексатора 17 с корпусом. Это позволяет эксплуатировать каждый микрокалькулятор по штатному расписанию. Для организации репрограммируемой памяти при отключении микрокалькуляторов из сети питания служит усилитель 13 мощности. Это исключает случайное стирание информации на переменах между занятиями и при ошибочном выключении пульта учащегося.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| СПОСОБ КОМПЛЕКСНОГО ОПРЕДЕЛЕНИЯ ТЕПЛОФИЗИЧЕСКИХ ХАРАКТЕРИСТИК МАТЕРИАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2027172C1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1990 |

|

RU2101772C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕПЛОФИЗИЧЕСКИХ ХАРАКТЕРИСТИК МАТЕРИАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1994 |

|

RU2096770C1 |

| ТРЕНАЖЕР МНЕМОСХЕМ | 1994 |

|

RU2116674C1 |

| ТРЕНАЖЕР ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ МАТРИЦ | 1990 |

|

RU2102792C1 |

| Система передачи и приема информации | 1987 |

|

SU1411795A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ КОНЦЕНТРАЦИИ ЭЛЕКТРОЛИТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2011983C1 |

| ПРОГРАММНО-ЛОГИЧЕСКОЕ ВРЕМЕННОЕ УСТРОЙСТВО | 2001 |

|

RU2199146C1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

Изобретение относится к вычислительной технике и телеавтоматике, в частности к обучающим системам, построенным на микрокалькуляторах. Целью изобретения является повышение информативности обмена информацией в микрокалькуляторной сети, для чего обмен числоимпульсной информацией между пультами абонентов осуществляется по принципу прямого доступа к оперативной памяти за один машинный цикл. Для этого микрокалькуляторы через мультиплексоры объединены в одноразрядную информационную сеть, тактируемую с центрального пульта по четырехразрядной синхронизирующей шине и одноразрядной шине управления. Микрокалькуляторная сеть функционирует в трех режимах: индивидуального обслуживания, принудительного обмена информацией и репрограммируемого хранения во времени. Центральный пульт содержит микрокалькулятор, мультиплексор, блок памяти, счетчик адреса, элемент И, генератор фаз, усилитель мощности, шинный разъем. Периферийный пульт содержит микрокалькулятор, генератор фаз, мультиплексор, шинный разъем, коммутационный разъем. 2 с.п.ф-лы, 5 ил.

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1994-06-30—Публикация

1990-12-04—Подача