Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно устройство для программного управления (см. авторское свидетельство СССР 1080120 от 16.12.84, МКИ: G 05 В 19/08 "Устройство для программного управления", В.А. Сечкин и В.И. Юлдашев, опубл. 15.03.84, БИ 10), содержащее генератор импульсов, выход которого соединен со входом счетчика импульсов, выходы каждого разряда которого соединены с первыми входами цифрового компаратора, выход которого подключен к первому входу первого элемента И, выход которого соединен с входом блока команд. Выходы блока команд соединены с соответствующими входами блока формирования данных, соединенного первым и вторым выходами с входами соответственно первого и второго задатчиков времени, выходы которых соединены с первыми входами соответственно блоков вторых и третьих элементов И, соединенных выходами со входами блока элементов ИЛИ, выходы которого соединены со вторыми входами цифрового компаратора. Вторые входы блока вторых элементов И соединены с инверсным выходом RS-триггера, S-вход которого соединен с выходом цифрового компаратора, а прямой выход RS-триггера соединен со вторыми входами блока третьих элементов И, со вторым входом первого элемента И и с первым выходом устройства. Выходы блока команд являются вторыми выходами устройства.

Недостатком данного устройства является его низкая помехоустойчивость в условиях воздействия мощных электрических помех.

Известно программное реле времени (ПРВ, см. книгу В.А. Шполянского, А.М. Курицкого "Программно-временные задатчики", "Машиностроение", М., 1984, стр. 269, рис. 5.3 в), которое является наиболее близким по технической сущности и выбрано в качестве прототипа. ПРВ содержит хронизатор, счетчик импульсов, цифровой компаратор, запоминающее устройство, адресный коммутатор, усилитель-формирователь команд. Выход хронизатора соединен со входом счетчика импульсов, разрядные выходы которого соединены с соответствующими первыми входами цифрового компаратора, вторые входы которого соединены с соответствующими выходами запоминающего устройства. Адресные входы запоминающего устройства соединены с соответствующими выходами адресного коммутатора, вход которого соединен с выходом цифрового компаратора, с входом сброса счетчика импульсов и с входом усилителя-формирователя команд, выход которого является выходом программного реле времени. Задание уставок в запоминающее устройство осуществляется с выходов блока ввода уставок.

Недостатком прототипа является низкая помехоустойчивость в условиях воздействия мощных электрических помех.

Задачей, решаемой заявляемым изобретением, является создание программного таймера, обладающего повышенной помехоустойчивостью в условиях мощных электрических помех и более простой схемной реализацией при формировании временных интервалов, лежащих в широком диапазоне.

Указанный технический результат достигается тем, что в программном таймере, содержащем хронизатор, счетчик импульсов, первые выходы которого соединены соответственно с первыми входами цифрового компаратора, запоминающее устройство, первые выходы которого соединены соответственно со вторыми входами цифрового компаратора, выход которого является выходом устройства. Новым является введение коммутатора, первые входы которого соединены соответственно с выходами хронизатора, выход соединен с входом счетчика импульсов, вторые входы соединены с соответствующими вторыми выходами запоминающего устройства, входы которого соединены соответственно со вторыми выходами счетчика импульсов, при этом запоминающее устройство выполнено в виде постоянного запоминающего устройства (ПЗУ), а счетчик импульсов выполнен в виде счетчика в отраженном двоичном коде.

Для упрощения схемы программного таймера при формировании уставок в широком временном диапазоне третий выход запоминающего устройства соединен с третьим входом цифрового компаратора.

Указанная совокупность существенных признаков позволяет повысить помехоустойчивость программного таймера за счет управления цифровым компаратором и адресами ПЗУ от единого счетчика импульсов, работающего в отраженном двоичном коде. При этом при формировании уставок в широком временном диапазоне достигается упрощение схемы за счет возможности коммутации тактовых сигналов с разной частотой следования с выхода хронизатора на вход счетчика импульсов, а также за счет управления цифровым компаратором с выхода дополнительного разряда ПЗУ.

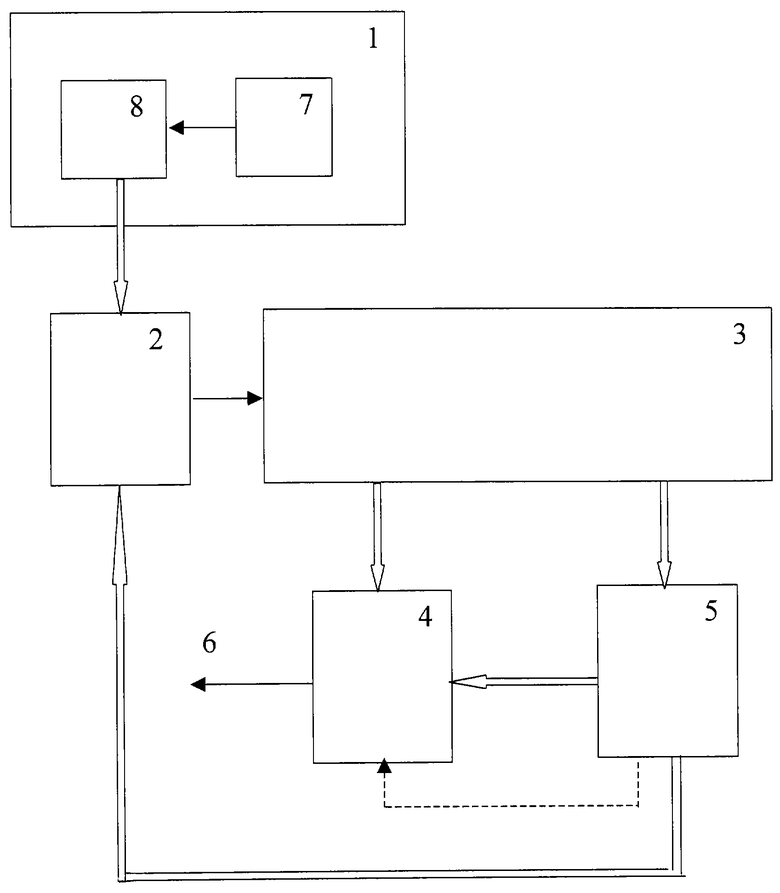

На чертеже приведена электрическая структурная схема программного таймера. Программный таймер содержит хронизатор 1, коммутатор 2, счетчик 3 импульсов в отраженном двоичном коде, цифровой компаратор 4, постоянное запоминающее устройство 5, выходную шину 6. Хронизатор 1 содержит генератор 7 импульсов и делитель 8 частоты. Выход генератора 7 соединен с входом делителя 8 частоты, выходы которого соединены соответственно с первыми входами коммутатора 2. Выход коммутатора 2 соединен со входом счетчика 3 импульсов, первые выходы которого соединены соответственно с первыми входами цифрового компаратора 4 и с входами ПЗУ 5, первые выходы которого соединены соответственно со вторыми входами цифрового компаратора 4. Выход компаратора 4 соединен с выходной шиной 6. Вторые выходы ПЗУ 5 соединены соответственно со вторыми входами коммутатора 2. При формировании программным таймером уставок, лежащих в широком временном диапазоне, третий выход ПЗУ 5 соединен с третьим входом цифрового компаратора 4.

Пример выполнения счетчика 3 импульсов в отраженном двоичном коде приведен в описании к патенту РФ 2063658 от 18.11.91, МКИ: Н 03 К 21/40, 23/00 "Счетчик импульсов в коде Грея", Дикарев И.И., Егоров Л.Б., Шишкин Г. И., опубл. 10.07.96, БИ 19. В качестве первых и вторых выходов счетчика 3 в указанном техническом решении могут быть использованы выходы элементов 24 "Исключающее ИЛИ ". В этом случае информация с выходов счетчика 3 снимается в позиционном двоичном коде, что подтверждается схемой преобразования, представленной в книге Э.И. Гитиса "Преобразователи Информации для электронных цифровых вычислительных устройств", "Энергия". М., 1975, стр. 160, рис. 4-3.

Программный таймер работает следующим образом. В исходном состоянии после подачи напряжения питания на схему счетчик 3 обнулен (цепь обнуления счетчика 3 на фиг. не показана), при этом в нулевом адресе ПЗУ 5 выставлен код, соответствующий требуемому значению первой уставки. Первая часть разрядов выходного кода ПЗУ 5 задает момент сравнения кодов в цифровом компараторе 4 (первые выходы ПЗУ 5), вторая часть разрядов выходного кода ПЗУ 5 задает частоту тактового сигнала на выходе коммутатора 2 (вторые выходы ПЗУ 5). С помощью генератора 7 и делителя 8 частоты на выходе хронизатора 1 формируется сетка частот, одна из частот в соответствии с кодом, заданным на вторые входы коммутатора 2, подается на вход счетчика 3. Счетчик 3 переключается под действием входных тактовых сигналов, при этом в соответствии с логикой отраженного двоичного кода при каждом переключении счетчика 3 изменяется информация только в одном из его разрядов. Благодаря этому электрическая помеха, действующая на счетчик 3 во время его переключения, может исказить информацию только в одном переключающемся разряде, то есть цена такого сбоя равна значению периода тактового сигнала на входе счетчика 3. Для повышения помехоустойчивости разрядов счетчика 3 в паузах между переключениями целесообразно защитить информацию в них с помощью RC- элементов памяти (см., например, схему, приведенную в описании к патенту 2063658). Информация с первых выходов счетчика 3 в позиционном двоичном коде подается на первые входы цифрового компаратора 4, в момент сравнения кодов на первых и вторых входах компаратора 4 на его выходе появляется сигнал "лог1", поступающий на выход 6 программного таймера. В этот момент времени заканчивается формирование первой уставки и начинается отсчет второй уставки. При достижении счетчиком 3 состояния, при котором происходит смена кода адреса на входах ПЗУ 5, изменятся коды на вторых входах коммутатора 2 и на вторых входах цифрового компаратора 4. В результате выбирается новое значение тактовой частоты на выходе коммутатора 2 и кода сравнения цифрового компаратора 2, при котором происходит формирование выходного импульса, соответствующего концу формирования второй уставки и началу формирования третьей уставки. Аналогично таймер осуществляет формирование третьей и последующих временных уставок. Количество разрядов счетчика 3 импульсов, задействованных для формирования кода на первые входы цифрового компаратора 4, зависит от величин формируемых временных уставок; при формировании в одном цикле работы таймера маленьких и больших временных интервалов количество первых выходов счетчика 3 определяется величиной максимального из формируемых интервалов. Количество первых выходов счетчика 3 при формировании больших временных интервалов может быть уменьшено при использовании дополнительного разряда ПЗУ 5 (третий выход ПЗУ 5); информация с этого выхода ПЗУ 5 используется для разрешения или запрета формирования сигнала на выходе компаратора 4.

Поясним это на следующем примере. Пусть период счетных сигналов на входе счетчика 3 равен 1 с. Сигнал "лог 1" на выходе первого разряда счетчика 3 в позиционном двоичном коде появится через 1 с; на выходе второго разряда - через 2 с, на выходе третьего - через 4 с, на выходе разряда с номером m - через 2m-1 с. Если необходимо сформировать уставки t1=2 c и t2=100 c, без использования третьего выхода ПЗУ 5 надо использовать 6 выходов счетчика 3, которые связаны с первыми входами компаратора 4. При этом на управление адресными входами ПЗУ 5 используются выходы старших разрядов счетчика 3, начиная с седьмого. Код уставки, формируемый по первому адресу ПЗУ 5, равен 2, после формирования первой уставки счетчик 3 сосчитает еще 62 импульса, после чего 64-м импульсом произойдет смена адреса ПЗУ 5. Примем для простоты, что во втором адресе ПЗУ 5 код управления коммутатором 2 такой же, как и в первом адресе, то есть период входной частоты остался равным 1 с. Тогда до формирования сигнала об окончании формирования второй уставки счетчик 3 сосчитает еще 32 импульса, то есть код, подаваемый на вторые входы компаратора 4 с ПЗУ 5, равен 32. При использовании третьего выхода ПЗУ 5 при формировании указанных уставок t1, t2 достаточно использовать 2 выхода счетчика 3. При этом на управление адресными входами ПЗУ 5 используются выходы старших разрядов счетчика 3, начиная с третьего. По первому адресу с третьего выхода ПЗУ 5 снимается сигнал "лог 1", разрешающий формирование сигнала сравнения на выходе компаратора 4. Код уставки t1, формируемой по первому адресу ПЗУ 5, равен 2, после выдачи уставки t1 счетчик 3 сосчитает еще 2 импульса, и 4-м импульсом произойдет смена адреса ПЗУ 5. Второй адрес удерживается с 4-го по 7-й импульсы, при этом с третьего выхода ПЗУ 5 снимается сигнал "лог 0", запрещающий формирование сигнала сравнения на выходе компаратора 4; значение кода, снимаемого с первых выходов ПЗУ 5 при этом значения не имеет. Аналогичным образом запрещается формирование сигнала сравнения при установке на входах ПЗУ 5 третьего адреса (с 8-го по 12-й импульс) и т.д. вплоть до 26-го адреса. В 26-м адресе на третьем выходе ПЗУ 5 устанавливается сигнал "лог 1", код сравнения устанавливается "01", в результате сигнал сравнения формируется на 102-м тактовом импульсе, величина уставки t2 составит 100 с. Использование дополнительного третьего выхода ПЗУ 5 сокращает схемные затраты на реализацию компаратора 4, что при определенных условиях может упростить схему программного таймера. Количество разрядов счетчика 3, задействованных для формирования адреса ПЗУ 5, определяется требуемым объемом памяти ПЗУ 5, при этом на объем памяти влияет количество формируемых временных уставок в цикле работы, диапазон формируемых уставок, использование третьего выхода ПЗУ 5. При выборе частоты следования тактовых импульсов на выходе коммутатора 2 необходимо учитывать длительность формируемого временного интервала и допустимую величину искажения уставки в условиях воздействия электрических помех.

При формировании временных уставок, лежащих в широком диапазоне, использование коммутатора 2 может сократить количество разрядов счетчика 3 импульсов. Учитывая сравнительную сложность схемной реализации разрядов счетчика 3, это приводит к упрощению схемы программного таймера.

При воздействии на программный таймер мощных электрических помеховых импульсов устойчивость его работы обеспечивается выбором соответствующей элементной базы (например, использованием КМОП-микросхем с высоким порогом срабатывания), а также принятием специальных схемных мер (защита триггерных структур счетчика 3 импульсов RC-элементами памяти, организация работы счетчика в отраженном двоичном коде, управление цифровым компаратором 4 и адресами ПЗУ 5 от единого счетчика импульсов). Так, при воздействии импульса электрической помехи в моменты времени, когда счетчик 3 находится в статическом режиме (тактовый импульс отсутствует), состояние его разрядов не изменяется, в этом случае возможно укорочение или удлинение тактового интервала за счет сбоя делителя 8 частоты. Этот сбой может привести к укорочению или удлинению формируемой уставки на величину периода тактовых сигналов (То). При воздействии импульса помехи в момент переключения счетчика в наихудшем случае возможен сбой одного переключающегося разряда, что, с учетом использования отраженного кода, приведет к удлинению формируемой уставки на величину То. Для сравнения в схеме прототипа такая помеха может привести к непереключению адреса ПЗУ и к повторному формированию временного интервала.

Таким образом, как следует из описания работы, заявляемый программный таймер обладает более высокой помехоустойчивостью и более простой схемной реализацией при формировании временных интервалов, лежащих в широком диапазоне.

Испытания лабораторного макета программного таймера подтвердили осуществимость и практическую ценность заявляемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| ТАЙМЕР | 2001 |

|

RU2199177C1 |

| КОММУТАТОР ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1995 |

|

RU2103716C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| ТАЙМЕР | 2001 |

|

RU2213366C2 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ПАРАМЕТРОВ | 1999 |

|

RU2180450C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2003 |

|

RU2239037C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМИ ЗАМКАМИ | 2001 |

|

RU2198276C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

Изобретение относится к импульсной технике. Технический результат заключается в повышении помехоустойчивости в условиях воздействия мощных однократных электрических помех. Программный таймер содержит хронизатор (1), выполненный на генераторе импульсов (7) и делителе частоты (8), коммутатор (2), счетчик импульсов в отраженном двоичном коде (3), цифровой компаратор (4), постоянное запоминающее устройство (5), выходную шину (6). 1 з.п.ф-лы, 1 ил.

| ШПОЛЯНСКИЙ В.А | |||

| и др | |||

| Программно-временные задатчики | |||

| - М.: Машиностроение, 1984, с.269, рис.5.3 в) | |||

| Устройство для программного управления | 1982 |

|

SU1080120A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1991 |

|

SU1769611A1 |

| Многоканальный таймер | 1986 |

|

SU1345326A1 |

| Многоканальный таймер | 1990 |

|

SU1737712A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| RU 2063658 С1, 10.071996 | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

2003-10-27—Публикация

2001-12-17—Подача