Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно счетное устройство (см. патент РФ 2047271 от 18.11.91, МКИ:Н 03 К 21/40. "Счетчик импульсов, сохраняющий информацию при перерывах питания",. /И. И. Дикарев, Л. Б. Егоров, Г.И. Шишкин// Опубл. 27.10.95, Бюл. 30), содержащее блок управления и n счетных ячеек, каждая из которых содержит сердечник с прямоугольной петлей гистерезиса и обмотками - выходной и записи, четыре логических элемента и два резистора, при этом первый вход блока управления является счетным входом устройства, первый вход соединен с первым входом каждой счетной ячейки, а второй выход - со вторым входом первой счетной ячейки, второй вход каждой i-й счетной ячейки, где i - 2,3..., n, соединен с первым выходом (i-1)-й ячейки, а третий вход - со вторым выходом (i-1)-й ячейки, второй выход n-й счетной ячейки является выходом устройства, четвертые входы всех счетных ячеек объединены, в каждой счетной ячейке первый вход первого логического элемента является первым входом ячейки, выход второго логического элемента соединен через первый резистор с началом обмотки записи сердечника, а первый вход - с выходом четвертого логического элемента, вход которого является вторым входом счетной ячейки, третьим входом которой является первый вход третьего логического элемента, конец выходной обмотки сердечника соединен с выводом второго резистора, блока анализа четности, контрольного сердечника с прямоугольной петлей гистерезиса и обмоткой, двух элементов И-НЕ с открытыми стоками (коллекторами), резистора и блока формирования сигнала ошибки, а в каждую счетную ячейку введен RS-триггер, причем инверсный и прямой выходы блока анализа четности соединены с первыми входами соответственно первого и второго элементов И-НЕ и соответственно с третьим и пятым входами первой счетной ячейки, n входов соединены со вторыми входами соответствующих счетных ячеек, пятый вход каждой i-й счетной ячейки (где i-2,3,... n) соединен с третьим выходом (i-1)-й счетной ячейки, второй вход блока управления соединен с шиной начальной установки, третий выход соединен с четвертыми входами счетных ячеек, четвертый выход - со вторым входом элементов И-НЕ, а пятый выход - с выходом второго элемента И-НЕ, с первым входом блока формирования сигнала ошибки и через обмотку контрольного сердечника с выходом первого элемента И-НЕ и вторым входом блока формирования сигнала ошибки, третий вход которого соединен со вторым входом блока управления, а выход является контрольным выходом устройства, средняя точка обмотки контрольного сердечника через резистор соединена с шиной питания, в каждой счетной ячейке R-вход RS-триггера является четвертым входом ячейки, S-вход соединен с другим выводом второго резистора, прямой выход соединен со вторым входом второго логического элемента и является вторым выходом ячейки, а инверсный выход является третьим выходом счетной ячейки, начало выходной обмотки сердечника соединено с общей шиной, а конец обмотки записи - с выходом первого логического элемента, второй вход которого соединен с выходом второго логического элемента, выход третьего логического элемента является первым выходом счетной ячейки, а второй вход соединен с первым входом четвертого логического элемента, второй вход которого является пятым входом счетной ячейки, первый и четвертый логические элементы выполнены в виде элементов ИЛИ-НЕ, второй логический элемент - в виде элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а третий логический элемент - в виде элемента ИЛИ.

Недостатками данного счетного устройства является сложность схемной реализации в связи с большим количеством элементов в каждом разряде и большой ток перемагничивания сердечников в связи с ограничением числа витков обмотки записи за счет наличия выходной обмотки.

Известно счетное устройство (см. патент РФ 2040113 от 08.10.92, МКИ:Н 03 К 23/76. "Счетное устройство" /И.И. Дикарев, Л.Б. Егоров, Г.И. Шишкин// Опубл. 27.07.95, Бюл. 20), которое является наиболее близким по технической сущности и взято в качестве прототипа. Устройство содержит первый счетный вход, вход начальной установки, первый элемент И-НЕ, первый формирователь и N разрядов, каждый из которых содержит две ячейки памяти и логический элемент, первый и второй входы элемента являются соответственно первым счетным входом и входом начальной установки устройства, тактовые входы первых ячеек памяти всех разрядов объединены и подключены к выходу элемента И-НЕ, тактовые входы вторых ячеек памяти всех разрядов объединены, в каждом разряде выход второй ячейки памяти соединен с одним входом логического элемента. Второй счетный вход устройства, второй формирователь импульсов, второй и третий элементы И-НЕ, N-разрядный счетчик импульсов, два дешифратора и два выхода устройства, первый вход второго элемента И-НЕ соединен с входом начальной установки, второй вход - со вторым счетным входом устройства, а выход - с тактовыми входами вторых ячеек памяти разрядов, счетные входы устройства соединены с соответствующими входами третьего элемента И-НЕ, выход которого подключен к входу первого формирователя импульсов, выход которого соединен с входом обнуления счетчика и входом второго формирователя импульсов, выход которого соединен со счетным входом счетчика, тактовые входы первого и второго дешифратора соединены с выходами соответствующих элементов И-НЕ, информационные входы - с соответствующими выходами разрядов счетчика импульсов, а выходы являются соответствующими выходами счетного устройства, прямой выход каждого разряда счетчика импульсов соединен с информационными входами первой и второй ячеек памяти соответствующего разряда устройства, в каждом разряде которого второй вход логического элемента соединен с выходом первой ячейки памяти, а выход - с входом установки соответствующего разряда счетчика импульсов, при этом логические элементы разрядов устройства выполнены в виде элементов И-НЕ.

Недостатками прототипа являются ограниченные функциональные возможности в связи с отсутствием возможности опроса состояния счетного устройства в любой необходимый момент времени, а также сложность схемной реализации даже для одноканального устройства, связанная в первую очередь с необходимостью использования логических элементов И-НЕ с открытым стоком.

Задачей, решаемой предлагаемым изобретением, является создание счетного устройства с расширенными функциональными возможностями.

Технический результат достигается тем, что в счетное устройство, содержащее счетный вход и вход начальной установки, первый логический элемент, первый вход которого соединен со счетным входом устройства, а выход соединен с входом интегрирующей RC-цепи, выход которой соединен с входом второго логического элемента, третий и четвертый логические элементы, и в каждом разряде триггер, элемент ИЛИ-НЕ, логический элемент, магнитный сердечник с прямоугольной петлей гистерезиса и обмоткой, средняя точка которой соединена с первым выводом резистора, первый вход элемента ИЛИ-НЕ первого разряда соединен с выходом четвертого логического элемента, R-входы триггеров всех разрядов объединены. Новым является то, что дополнительно введены вход опроса устройства и в каждый разряд - элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, логический элемент каждого разряда выполнен в виде элемента И, первый и четвертый логические элементы выполнены в виде элементов ИЛИ-НЕ, а второй и третий логические элементы - в виде инверторов, выход первого инвертора соединен с тактовым входом триггеров всех разрядов, первый вход второго элемента ИЛИ-НЕ соединен с входом начальной установки устройства, второй вход - с выходом второго инвертора, вход которого соединен с R-входами триггеров всех разрядов и выходом первого элемента ИЛИ-НЕ, второй вход которого соединен с входом опроса устройства, счетный вход устройства соединен с первыми входами элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда, первые входы элементов ИЛИ-НЕ всех разрядов объединены, выход элемента ИЛИ-НЕ каждого разряда соединен со вторым выводом резистора, а второй вход - с прямым выходом триггера и с началом обмотки магнитного сердечника, конец которой соединен со вторыми входами элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ каждого разряда, выход которого соединен с информационным входом триггера, выход элемента И каждого предыдущего разряда соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и И последующего разряда, выходы триггеров разрядов являются выходами счетного устройства.

Указанная совокупность признаков позволяет расширить функциональные возможности за счет реализации опроса состояния устройства в любой момент времени путем организации входа опроса устройства.

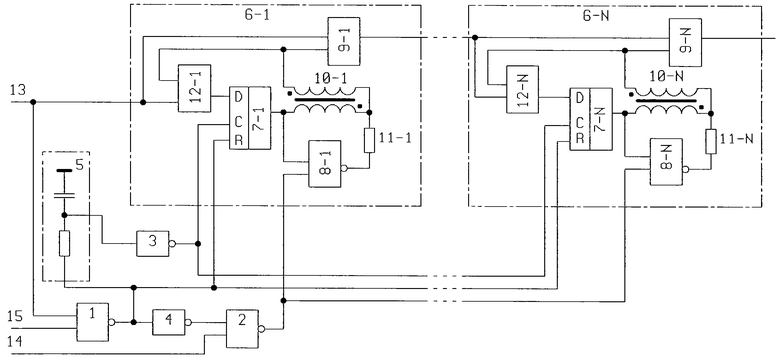

На чертеже приведена принципиальная схема счетного устройства.

Счетное устройство содержит элементы ИЛИ-ИЕ 1 и 2, инверторы 3 и 4, интегрирующую RC-цепь 5 и N разрядов 6-1,...6-N, каждый из которых содержит триггер 7-i, элемент ИЛИ-НЕ 8-i, элемент И 9-i, магнитный сердечник 10-i с прямоугольной петлей гистерезиса и обмоткой, резистор 11-i и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12-i (где i=1,...N). Счетное устройство имеет счетный вход 13, вход 14 начальной установки и вход опроса 15.

Первый и второй входы элемента ИЛИ-НЕ 1 являются соответственно счетным входом 13 и входом опроса 15 устройства. Первый вход второго элемента ИЛИ-НЕ 2 является входом 14 начальной установки устройства, а второй вход соединен с выходом второго инвертора 4, вход которого соединен с выходом элемента ИЛИ-НЕ 1, входом интегрирующей RC-цепи 5 и R-входами триггеров 7-i разрядов 6-1, ...6-N, тактовые входы которых соединены с выходом первого инвертора 3, вход которого соединен с выходом интегрирующей RC-цепи 5. Первые входы элементов ИЛИ-НЕ 8-i разрядов 6-1,...6-N соединены с выходом второго элемента ИЛИ-НЕ 2, а первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12-1 первого разряда соединен со счетным входом устройства. В каждом разряде второй вход элемента ИЛИ-НЕ 8-i подключен к выходу триггера 7-i, информационный вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12-i, первый и второй входы которого соединены соответственно с первым и вторым входами элемента И 9-i. В каждом разряде второй вывод резистора 11-i соединен с выходом элемента ИЛИ-НЕ 8-i, а второй вывод - со средней точкой обмотки магнитного сердечника 10-i с прямоугольной петлей гистерезиса, начало которой подключено к выходу триггера 7-i, а конец - ко второму входу элемента И 9-i. Выход элемента И 9-(j-1) каждого предыдущего разряда (гдe j=2,...N) соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 12-j и И 12-j последующего разряда. Выходы триггера 7-i каждого разряда являются выходами счетного устройства.

Счетное устройство работает следующим образом.

На вход 14 начальной установки поступает импульс логической "1", который инвертируется элементом ИЛИ-НЕ 2 и поступает на входы элементов 8-i N ИЛИ-НЕ каждого разряда 6-1, ..., 6-N. На счетном входе 13 и входе опроса 15 в это время присутствуют уровни логического "0", которые поступают на входы элемента ИЛИ-НЕ 1. Уровень логической "1" с его выхода поступает на вход интегрирующей RC-цепи 5 и на входы сброса триггеров 7-1,..., 7-N, устанавливая на их выходе уровни логического "0". При этом на выходе элементов 8-1,..., 8-N формируются уровни логической "1", а магнитные сердечники с прямоугольной петлей гистерезиса и обмоткой 10-1,..., 10-N перемагничиваются в нулевое состояние. По окончании импульса начальной установки на счетный вход 13 устройства начинают поступать счетные импульсы.

Первый счетный импульс поступает на счетный 13 вход в виде уровня логической "1" и вызывает появление на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12-1 первого разряда уровня логической "1", а на выходе элемента ИЛИ-НЕ 1 - уровня логического "0". При этом на вход интегрирующей RC-цепи 5 подается уровень логического "0", снимаются сигналы обнуления с входов сброса триггеров 7-i всех разрядов, а на выходе инвертора 4 формируется уровень логической "1", вызывающий появление уровня логического "0" на выходе элемента ИЛИ-НЕ 2. На оба входа элементов ИЛИ-НЕ 8-i всех разрядов поступают уровни логического "0", что приводит к перемагничиванию магнитных сердечников с прямоугольной петлей гистерезиса и обмоткой 10-1,..., 10-N в нулевое состояние. Но, так как они были перемагничены в нулевое состояние во время поступления импульса начальной установки, то на их выходах формируются лишь короткие импульсы помех, связанные с непрямоугольностью петли гистерезиса данных магнитных сердечников с обмоткой 10-1,..., 10-N. Данные импульсы не приводят к переключению триггеров 7-1,..., 7-N, так как на их тактовых входах удерживается уровень логического "0" с выхода инвертора 3, на входе которого подается уровень логической "1" с выхода интегрирующей RC-цепи 5. Через время задержки, определяемое постоянной времени интегрирующей RC-цепи 5 и превышающей длительность импульса помехи от непрямоугольности петли гистерезиса, на выходе инвертора 3 происходит формирование уровня логической "1". При этом триггер 7-1 первого разряда устройства переходит в состояние логической "1", что приводит к перемагничиванию магнитного сердечника с обмоткой 10-1. На выходах элементов И 9-1,...,9-N формируется уровень логического "0". По окончании первого счетного импульса на первых входах элементов ИЛИ-НЕ 8-1, ..., 8-N и на входах сброса триггеров 7-1,..., 7-N устанавливается уровень логической "1", после чего обесточиваются обмотки магнитных сердечников 10-1,..., 10-N.

Второй счетный импульс поступает на счетный вход 13 и вызывает появление уровня логической "1" на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12-1 первого разряда и уровня логического "0" на выходе элемента ИЛИ-НЕ 1. При этом на вход интегрирующей RC-цепи 5 подается уровень логического "0", снимаются сигналы обнуления с входов сброса триггеров 7-i всех разрядов, а на выходе элемента ИЛИ-НЕ 2 формируется уровень логического "0". На оба входа элементов ИЛИ-НЕ 8-i всех разрядов поступают уровни логического "0", что приводит к перемагничиванию магнитных сердечников 10-1,..., 10-N в нулевое состояние. Так как сердечники 10-2,..., 10-N уже намагничены в нулевое состояние, то на их выходах формируются короткие импульсы помех, связанные с непрямоугольностью петли гистерезиса, а на выходе магнитного сердечника 10-1, намагниченного в единичное состояние во время предыдущего счетного импульса, формируется импульс, длительность которого, если не прерывать процесс перемагничивания, равнялась бы времени перемагничивания магнитного сердечника.

Данный импульс вызывает появление на выходе элемента И 9-1 уровня логической "1", который поступает на информационный вход триггера 7-2 второго разряда через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12-2. На информационный вход триггера 7-1 первого разряда в это время подается уровень логического "0". Через время задержки, определяемое постоянной времени интегрирующей RC-цепи 5, которая превышает длительность импульса помехи от непрямоугольности петли гистерезиса, но меньше времени перемагничивания магнитного сердечника, на выходе инвертора 3 происходит формирование уровня логической "1". Это приводит к установке триггера 7-2 в единичное состояние, а триггеров 7-1, 7-3,..., 7-N в нулевое состояние. Соответствующим образом перемагничиваются магнитные сердечники разрядов 6-1, . .., 6-N. По окончании второго счетного импульса триггеры 7-1, . .., 7-N устанавливается в нулевое состояние, а обмотки магнитных сердечников 10-1,..., 10-N обесточиваются.

Определить состояние счетного устройства можно, подавая опросный импульс на вход опроса 15 уровень логической "1". Это вызывает снятие сигнала сброса с триггеров 7-i всех разрядов, а также появление уровня логического "0" на входе интегрирующей RC-цепи 5 и на выходе элемента ИЛИ-НЕ 2, что активизирует процесс перемагничивания магнитных сердечников 10-i N всех разрядов в нулевое состояние. Так как сердечники 10-1, 10-3,..., 10-N уже намагничены в нулевое состояние, то на их выходах формируются короткие импульсы помех, связанные с непрямоугольностью петли гистерезиса. На выходе магнитного сердечника 10-2, намагниченного в единичное состояние во время предыдущего счетного импульса, формируется импульс, длительность которого, если не прерывать процесс перемагничивания, равнялась бы времени перемагничивания магнитного сердечника. Данный импульс вызывает появление на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12-2 и на информационном входе триггера 7-2 уровня логической "1". На информационных входах триггеров 7-1, 7-3,..., 7-N присутствует уровень логического "0". Через время задержки, определяемое постоянной времени интегрирующей RC-цепи 5, происходит появление уровня логической "1" на входах триггеров 7-i всех разрядов, что приводит к установке триггера 7-2 в единичное состояние, а триггеров 7-1, 7-3,..., 7-N в нулевое состояние. При этом происходит восстановление состояний магнитных сердечников 10-1,..., 10-N в состояние, в которых они находились до прихода импульса опроса. По окончании импульса опроса триггеры 7-1,..., 7-N устанавливаются в нулевое состояние, а обмотки магнитных сердечников 10-1,..., 10-N обесточиваются.

Далее устройство работает аналогично.

Изготовлен лабораторный макет счетного устройства, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта. Макет был выполнен на микросхемах серии 564 и на сердечниках из сплава АМАГ183. Время перемагмичивания использованных сердечников 20 мкс, а время задержки, определяемое постоянной времени интегрирующей RC-цепи, 5 мкс.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 2001 |

|

RU2212096C2 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 2002 |

|

RU2208902C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2230427C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1997 |

|

RU2129331C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 2003 |

|

RU2237355C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 2003 |

|

RU2234801C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1999 |

|

RU2180985C2 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления. Техническим результатом является расширение функциональных возможностей. Устройство содержит два элемента ИЛИ-НЕ, два инвертора, интегрирующую RC-цепь, N разрядов, каждый из которых содержит триггер, элемент ИЛИ-НЕ, элемент И, магнитный сердечник с прямоугольной петлей гистерезиса и обмоткой, резистор и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. 1ил.

Счетное устройство, содержащее счетный вход и вход начальной установки, первый логический элемент, первый вход которого соединен со счетным входом устройства, а выход соединен с входом интегрирующей RC-цепи, выход которой соединен с входом второго логического элемента, третий и четвертый логические элементы и в каждом разряде триггер, элемент ИЛИ-НЕ, логический элемент, магнитный сердечник с прямоугольной петлей гистерезиса и обмоткой, средняя точка которой соединена с первым выводом резистора, первый вход элемента ИЛИ-НЕ первого разряда соединен с выходом четвертого логического элемента, R-входы триггеров всех разрядов объединены, отличающееся тем, что дополнительно введены вход опроса устройства и в каждый разряд элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, логический элемент каждого разряда выполнен в виде элемента И, первый и четвертый логические элементы выполнены в виде элементов ИЛИ-НЕ, а второй и третий логические элементы - в виде инверторов, выход первого инвертора соединен с тактовым входом триггеров всех разрядов, первый вход второго элемента ИЛИ-НЕ соединен с входом начальной установки устройства, второй вход - с выходом второго инвертора, вход которого соединен с R-входами триггеров всех разрядов и выходом первого элемента ИЛИ-НЕ, второй вход которого соединен с входом опроса устройства, счетный вход устройства соединен с первыми входами элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда, первые входы элементов ИЛИ-НЕ всех разрядов объединены, выход элемента ИЛИ-НЕ каждого разряда соединен с вторым выводом резистора, а второй вход - с прямым выходом триггера и с началом обмотки магнитного сердечника, конец которой соединен с вторыми входами элементов И и ИСКЛЮЧАЮЩЕЕ ИЛИ каждого разряда, выход которого соединен с информационным входом триггера, выход элемента И каждого предыдущего разряда соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и И последующего разряда, выходы триггеров разрядов являются выходами счетного устройства.

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| СЧЕТЧИК ИМПУЛЬСОВ, СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1991 |

|

RU2047271C1 |

| ПОМЕХОУСТОЙЧИВЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1991 |

|

RU2038692C1 |

| Счетное устройство сохраняющее информацию при перерывах питания | 1981 |

|

SU1051734A1 |

| SU 1764501 А1, 27.08.2001 | |||

| US 4741006 А, 26.04.1988 | |||

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

Авторы

Даты

2003-06-27—Публикация

2001-09-07—Подача