Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен многоканальный таймер (см. авторское свидетельство СССР 1345326 от 07.04.86, МКИ Н 03 К 5/13. Многоканальный таймер / Г.А. Пыко и Г. Г. Кравцов. Опубл. 15.10.87, БИ 38), содержащий дискретную линию задержки (ДЛЗ), запоминающее устройство (ЗУ), счетчик управления, N JK-триггеров, (N+3) логических элемента И, логический элемент ИЛИ, вход тактовых импульсов, вход старта, шину управления и N выходов, причем вход тактовых импульсов подключен к тактовому входу ДЗЛ и тактовым входам JK-триггеров, выходы которых являются выходами устройства, вход старта соединен с первым входом элемента ИЛИ, выход которого соединен с тактовым входом счетчика управления и со входом управления ДЗЛ, информационный вход которой соединен с выходом ЗУ, а выход соединен с первыми входами элементов И, вторые входы которых соединены с выходами ЗУ, выходы N элементов И соединены с J-входами соответствующих JK-триггеров, К-входы которых соединены с выходом (N+1) элемента И, выход (N+3) элемента И соединен со вторым входом элемента ИЛИ, выход (N+2) элемента И соединен с R-входом счетчика управления, выходы которого соединены с адресными входами ЗУ, управляющий вход которого подключен к шине управления.

Недостатком данного таймера является сложность его реализации в случае, когда необходимо формировать несколько интервалов, лежащих в широком временном диапазоне.

Известно устройство для программного управления (см. авторское свидетельство СССР 1080120 от 16.12.84, МКИ G 05 В 19/08. Устройство для программного управления / В.А. Сечкин и В.И. Юлдашев. Опубл. 15.03.84, БИ 10), взятое в качестве прототипа, содержащее генератор импульсов, выход которого соединен с входом счетчика импульсов, выходы каждого разряда которого соединены с первыми входами блока сравнения, выход которого подключен к первому входу первого элемента И, выход которого соединен с входом блока команд, выходы которого подключены ко второму выходу устройства и к входу блока формирования данных, соединенного первым и вторым выходами с входами соответственно первого и второго задатчиков времени, выходы которых соединены с первыми входами соответственно второго и третьего блоков элементов И, соединенных выходами к входам блока элементов ИЛИ, выходы которого соединены со вторыми входами блока сравнения, вторые входы второго блока элементов И соединены с инверсным выходом RS-триггера, S-вход которого соединен с выходом блока сравнения, а прямой выход RS-триггера соединен со вторыми входами третьего блока элементов И, с вторым входом первого элемента И и с первым выходом устройства.

Недостатком данного устройства является сложность его реализации в случае, когда необходимо формировать несколько интервалов, лежащих в широком временном диапазоне.

Техническим результатом заявляемого устройства является упрощение схемы при последовательном формировании временных интервалов, длительности которых находятся в широком диапазоне. Это достигается тем, что таймер содержит генератор импульсов, выход которого соединен со входом счетчика импульсов, блок сравнения, блок формирования команд, выходы которого соединены со входами блока формирования данных и являются выходами устройства. Новым является то, что дополнительно введен коммутатор, входы которого подключены к выходам счетчика импульсов соответственно, управляющие входы коммутатора соединены с первыми выходами блока формирования данных, выходы коммутатора соединены с первыми входами блока сравнения, вторые входы которого соединены со вторыми выходами блока формирования данных, а выход блока сравнения соединен с входом блока команд.

Указанная совокупность признаков позволяет упростить схему таймера, особенно при последовательном формировании временных интервалов, длительности которых находятся в широком диапазоне. Упрощение схемы достигается за счет возможности коммутировать с выхода счетчика импульсов на вход блока сравнения сигналы, период следования которых может находиться в широком временном диапазоне, что позволяет сократить разрядность блока сравнения и блока формирования данных.

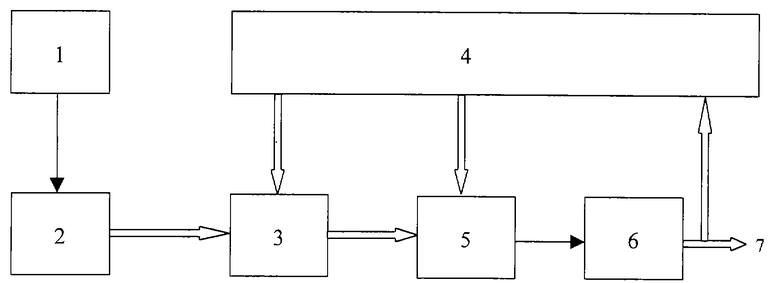

На чертеже приведена структурная схема таймера.

Таймер содержит генератор 1 импульсов, счетчик 2 импульсов, коммутатор 3, блок 4 формирования данных, блок 5 сравнения, блок 6 команд, выходы 7 устройства.

Выход генератора 1 импульсов соединен с входом счетчика 2 импульсов, выходы разрядов которого соединены с входами коммутатора 3, выходы которого соединены с первыми входами блока 5 сравнения. Управляющие входы коммутатора 3 соединены с первыми выходами блока 4 формирования данных, вторые выходы которого соединены с вторыми входами блока 5 сравнения соответственно. Выход блока 5 сравнения соединен с входом блока 6 команд, выходы которого соединены с входами блока 4 формирования данных и с выходами 7 устройства.

Примеры конкретного выполнения генератора 1 импульсов представлены в книге Альтшуллер Г.Б. и др. Кварцевые генераторы. - М.: Радио и связь, 1984, с. 63, рис. 5.6 а, б. Счетчик 2 импульсов может быть выполнен на основе четырехразрядных двоичных счетчиков-делителей К561ИЕ10, представленных в книге Шило В.Л. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, с.241, рис. 2.42. В качестве входа счетчика 2 импульсов может использоваться, например, С-вход счетчика-делителя, а выходы микросхемы следует использовать, как выходы разрядов счетчика 2 импульсов. Коммутатор 3 может быть выполнен на базе демультиплексора К561КП1, представленного в книге Шило В.Л. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, с.223, рис. 2.29. В качестве входов и выхода коммутатора 3 могут использоваться соответственно входы и выходы демультиплексора, а его входы управления А и В следует использовать как управляющие входы коммутатора 3. Блок 5 сравнения может быть выполнен на базе цифрового компаратора К561ИП2, представленного в книге Шило В. Л. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, с.266, рис. 2.67. В качестве первых входов блока 5 сравнения могут использоваться, например, входы А0...A3 микросхемы, в качестве вторых входов блока 5 сравнения - входы В0...В3, на вход А=В при этом следует подать напряжение высокого уровня, на входы А<В, А>В - напряжение низкого уровня. Блок 4 формирования данных может быть таким же, как в прототипе, при этом в блоке памяти, кроме кода времени выдачи команды, должен храниться также управляющий код для коммутатора. Блок 6 команд можно выполнить таким же, как в прототипе.

Устройство работает следующим образом. В исходном положении счетчик 2 импульсов находится в нулевом состоянии (цепь обнуления для простоты не показана). Блок 4 формирования данных находится в нулевом адресе, при этом на его выходах выставлен код, соответствующий времени выдачи первой команды и код управления коммутатором, с помощью которого требуемые выходы счетчика 2 импульсов через коммутатор 3 подключены к входу блока 5 сравнения. Тактовые импульсы, формируемые генератором 1 импульсов, поступают на вход счетчика 2 импульсов, который после снятия сигнала обнуления начинает отсчет времени формирования первой команды. При совпадении кодов с выходов счетчика 2 импульсов и кода времени выдачи первой команды с выхода блока 4 формирования данных срабатывает блок 5 сравнения, выходной сигнал которого поступает на вход блока 6 команд, где формируется первая команда, поступающая на выход 7 устройства и на вход блока 4 формирования данных. По срезу импульса первой команды происходит обнуление счетчика 2 импульсов (цепь обнуления для простоты не показана) и переключение блока 4 формирования данных в следующий адрес. В результате этого на выходах блока 4 формирования данных выставляется новый код, соответствующий времени выдачи второй команды и необходимый для этого код управления коммутатором 3. Далее начинается процесс отсчета времени формирования второй команды, где на вход блока 5 сравнения через коммутатор 3, в зависимости от длительности второго временного интервала, могут быть подключены уже другие выходы счетчика 2 импульсов. Дальнейшие процессы, протекающие в таймере при формировании второй и последующих команд, происходят аналогично. При выборе выходов, коммутируемых со счетчика 2 на блок 5 сравнения, следует учитывать длительность формируемого временного интервала, заданную точность, разрядность блока сравнения и блока формирования данных.

В целях подтверждения осуществимости заявляемого объекта и достижения технического результата изготовлен и испытан лабораторный макет таймера, выполненный по приведенной на чертеже схеме. Проведенные испытания показали осуществимость заявляемого таймера и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТАЙМЕР | 2001 |

|

RU2213366C2 |

| ПРОГРАММНЫЙ ТАЙМЕР | 2001 |

|

RU2215367C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМИ ЗАМКАМИ | 2001 |

|

RU2198276C1 |

| ЭЛЕКТРОННЫЙ КОДОВЫЙ ЗАМОК | 2001 |

|

RU2191241C1 |

| ЭЛЕКТРОННЫЙ КОДОВЫЙ ЗАМОК | 2001 |

|

RU2215107C2 |

| КОММУТАТОР ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1995 |

|

RU2103716C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КОДОВЫМ ЗАМКОМ | 2001 |

|

RU2191878C1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

Использование: в устройствах вычислительной техники и систем управления. Технический результат заключается в упрощении схемы при последовательном формировании временных интервалов, длительности которых находятся в широком диапазоне. Таймер содержит генератор импульсов, выход которого соединен со входом счетчика импульсов, блок сравнения, блок формирования команд, выходы которого соединены со входами блока формирования данных и являются выходами таймера, дополнительно введен коммутатор, входы которого подключены к выходам счетчика импульсов соответственно, управляющие входы коммутатора соединены с первыми выходами блока формирования данных, выходы коммутатора соединены с первыми входами блока сравнения, вторые входы которого соединены со вторыми выходами блока формирования данных, а выход блока сравнения соединен с входом блока формирования команд. 1 ил.

Таймер, содержащий генератор импульсов, выход которого соединен со входом счетчика импульсов, блок сравнения, блок формирования команд, выходы которого соединены со входами блока формирования данных и являются выходами таймера, отличающийся тем, что дополнительно введен коммутатор, входы которого подключены к выходам счетчика импульсов соответственно, управляющие входы коммутатора соединены с первыми выходами блока формирования данных, выходы коммутатора соединены с первыми входами блока сравнения, вторые входы которого соединены со вторыми выходами блока формирования данных, а выход блока сравнения соединен с входом блока формирования команд.

| SU 10801120 A, 15.03.1984 | |||

| ТАЙМЕР | 1996 |

|

RU2100901C1 |

| Многоканальный таймер | 1986 |

|

SU1345326A1 |

| ТАЙМЕР | 1997 |

|

RU2130692C1 |

| US 4001698 A, 04.01.1977. | |||

Авторы

Даты

2003-02-20—Публикация

2001-10-08—Подача