Изобретение относится к технике электросвязи и предназначено, в частности для приема сигналов управления и взаимодействия, передаваемых в составе группового 8-ми канального цифрового потока 256 кБит/с с адаптивной дифференциально импульсно-кодовой модуляцией (АДИКМ).

Универсальный цифровой групповой приемник осуществляет обработку двухчастотных сигналов набора номера в коде "2 из 6",а также одночастотных сигналов типа "Ответ станции", "Контроль сети", "Автоматическое обнаружение номера" (АОН) в каждом из 8-ми каналов. Эти сигналы используются для управления коммутационным оборудованием цифровых электронных АТС с адаптивной дифференциальной ИКМ.

Известен цифровой обнаружитель гармонических составляющих для сигналов с адаптивной дельта-модуляцией (АДМ) [1], содержащий операционное и решающее устройство. Операционное устройство состоит из гребенки полосовых цифровых фильтров, блоков для вычисления модуля и сумматоров кодов, предназначенных для нахождения амплитуд гармонических составляющих.

Решающее устройство содержит группу из N пороговых блоков, в каждом из которых по результатам сравнения амплитуды K-ой гармонической состоящей с некоторым постоянным порогом принимается решение о наличии или отсутствии данной частотой компоненты в составе дельта-потока.

Недостатком этого обнаружителя является невысокая помехоустойчивость при различении безынтервального "пакета" двухчастотных знаков набора номера из-за большой вероятности приема ложных двухчастотных комбинаций, образованных концом предыдущей и началом последующей "посылок" на интервале анализа сигнала.

Другой недостаток связан с применением фиксированных порогов приема в решающем устройстве в условиях широкого динамического диапазона амплитуд и частот сигналов набора номера, а также "перекоса" уровней частотных составляющих двухчастотного сигнала. Это снижает помехоустойчивость приема компоненты сигнала с меньшей крутизной из-за подавления ее в нелинейном кодере, шаг квантования которого адаптируется к компоненте сигнала с большей крутизной.

К недостаткам цифрового обнаружителя можно отнести также его схемотехническую сложность в многоканальном варианте, постольку мультиплексирование М каналов потребует почти М-кратного увеличения объема оборудования.

Наиболее близким техническим решением является групповой приемник сигналов управления и взаимодействия с адаптивной импульсно-кодовой модуляцией [2] , содержащий задающий генератор, коммутатор адресов, блок оперативной памяти, формирователь опорных последовательностей, сумматоры синусной и косинусной составляющих сигналов, компаратор кода порога, регистр сдвига и вычислительный блок и решающий блок.

Недостатком приемника является невысокая помехоустойчивость приема частотной компоненты меньшей крутизны на фоне более мощной в составе двухчастотного сигнала.

Другим недостатком приемника является узкий динамический диапазон уровней принимаемых сигналов и зависимость ширины полосы пропускания приемника от уровня входного сигнала.

Целью изобретения является повышение помехоустойчивости, расширение динамического диапазона уровня приема и стабилизация полосы пропускания устройства за счет коррекции исходного АДИКМ-потока на входе приемника и адаптации порогов приема к уровню сигнала.

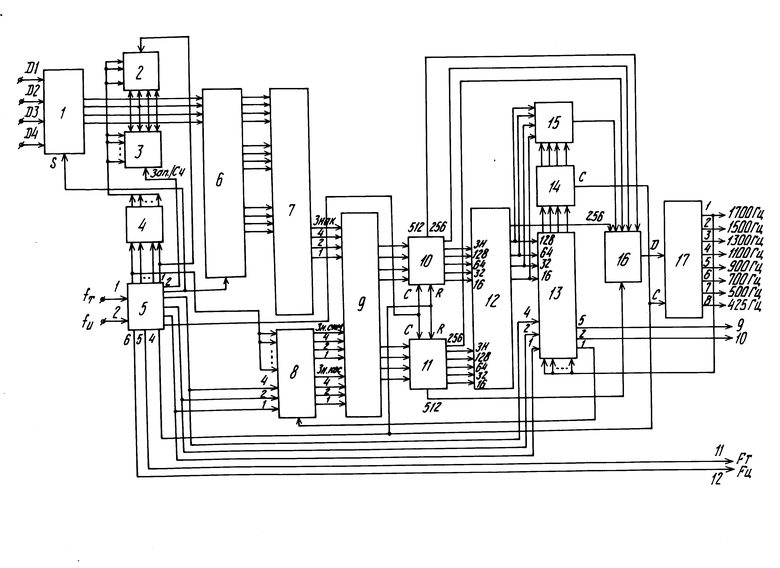

На чертеже изображена функциональная схема цифрового группового приемника сигналов управления и взаимодействия с адаптивной дифференциальной импульсно-кодовой модуляцией (АДИКМ).

Цифровой групповой приемник сигналов управления и взаимодействия с адаптивной дифференциальной импульсно-кодовой модуляцией содержит согласующий блок 1, первый и второй блоки оперативной памяти 2, 3, коммутатор 4 адресов, задающий генератор 5, формирователь 8 опорных последовательностей, коррелометр 9, сумматор 10 синусной составляющей сигнала, сумматор 11 косинусной составляющей сигнала, вычислительный блок 12, решающий блок 13, регистр 14 адаптивного кода, компаратор 15 кода порога, элемент 16 ИЛИ и выходной регистр 17, при этом выходы согласующего блока 1 соединены с сигнальными входами первого 2 и второго 3 блоков оперативной памяти, задающий генератор 5 и коммутатор 4 адресов соединены последовательно, выходы коммутатора 4 адресов соединены с адресными входами первого 2 и второго 3 блоков оперативной памяти, адресные выходы задающего генератора 5 соединены с первой группой входов решающего блока 13 и через формирователь 8 опорных последовательностей соединены с опорными синусными и косинусными входами коррелометра 9, синусные и косинусные кодовые выходы которого соединены соответственно со входами сумматоров 10 и 11 синусной и косинусной составляющих сигнала, выходы старших разрядов выходных кодов которых соединены соответственно с первыми и вторыми входами элемента 16 ИЛИ, а выходы знакового разряда и выходы группы младших разрядов выходных кодов - с соответствующими входами вычислительного блока 12, выходы младших разрядов выходного кода которого соединены со второй группой входов решающего блока 13 и первой группой входов компаратора 15 кода порога, выход которого и выход старшего разряда выходного кода вычислительного блока 12 через элемент 16 ИЛИ соединены с входом данных выходного регистра 17, выходы которого соединены с третьей группой входов решающего блока 13, причем первый и второй выходы задающего генератора 5 соединены соответственно с входами записи/считывания первого 2 и второго 3 блоков оперативной памяти, входы синхронизации и сброса сумматоров синусной 10 и косинусной 11 составляющих сигнала соединены соответственно между собой и подключены соответственно к третьему и четвертому выходам задающего генератора 5, четвертый выход которого соединен также с тактовым входом выходного регистра 17, первый выход решающего блока 13 соединен с опорным входом формирователя 8 опорных последовательностей, первая группа адресных входов которого соединена с соответствующими входами коммутатора 4 адресов, входы данных согласующего блока 1 являются входами четырехразрядного кода отсчета сигнала очередного канала, входы задающего генератора 5 - соответственно входами последовательности импульсов тактовой и цикловой синхронизации устройства, выходами которого являются выходы выходного регистра 17, второй и третий выходы решающего блока 13 и выходы сигналов тактовой и цикловой синхронизации соответственно с пятого и шестого выходов задающего генератора 5, введены дополнительно последовательно соединенные входной регистр 6 и интегратор 7 АДИКМ-потока, а также регистр 14 адаптивного кода, при этом выходы согласующего блока 1 соединены со входами данных входного регистра 6, выходы интегратора 7 АДИКМ-потока соединены с сигнальными входами коррелометра 9, кодовые выходы решающего блока 13 через регистр 14 адаптивного кода соединены со второй группой входов компаратора 15 кода порога, причем тактовый вход входного регистра 6 соединен с управляющим входом согласующего блока 1 и с третьим выходом задающего генератора 5, а тактовый вход регистра 14 адаптивного кода соединен с тактовым входом выходного регистра 17.

Цифровой групповой приемник сигналов управления и взаимодействия с АДИКМ работает следующим образом.

Групповой цифровой поток 256 кБит/с, образованный при объединении 8-ми индивидуальных АДИКМ-потоков 32 кБит/с поступает на входы данных (Д1 - Д4) согласующего блока 1 в параллельном 4-х разрядном двоичном коде, отображающем значение текущего отсчета сигнала очередного канала.

Квантованные АДИКМ-отсчеты каждого канала пропорциональны величине производной (крутизне) сигнала в момент взятия "пробы" с частотой дискретизации fкв = 8 кГц. При этом первый (старший) разряд "слова" (Д1 - Д4) отображает знак производной, а три младших разряда пропорциональны модулю в коде (4-2-1). Вес H младшего разряда, или шаг квантования производной, автоматически устанавливается в АДИКМ-кодере пропорциональным максимальной крутизне сигнала. Благодаря адаптации шага квантования H, число двоичных разрядов на отсчет сигнала удается сократить вдвое по сравнению с 8-ми разрядным нелинейным ИКМ-кодом. Соответственно вдвое снижается скорость передачи и полоса частот сигнала (32 кБит/с для АДИКМ, 64 кБит/с на канал - для ИКМ) при сохранении высокого качества передачи речи.

Сигналы набора номера передаются суммой двух гармонических колебаний кодом "2 из 6" из ряда частот 700, 900, 1100, 1300, 1500 и 1700 Гц. Кроме двухчастотных сигналов, необходимо распознавать одночастотные сигналы типа "Ответ станции" (зуммер) - 425 Гц, "Автоматическое обнаружение номера" (АОН) - 500 Гц. "Контроль сети" - 700 Гц, а также любой одночастотный сигнал из ряда (700 - 1700) Гц. Все эти сигналы могут иметь отклонения частот от номинала в пределах ± 15 Гц ("зуммер" в пределах ± 25 Гц) и колебаться по уровню в диапазоне (от -26 до -6) дБмО. Перекос уровней двухчастотных сигналов набора номера может достигать p = 5 дБ. Длительность "знака" набора номера может изменяться в пределах Тзн = (38 - 70) мс, причем соседние "знаки" могут следовать как с интервалом Ти ≈ Тзн, так и безынтервальным "пакетом", моменты смены "знаков" случайны и неизвестны на приеме.

Поскольку в АДИКМ-кодере сигналы подвергаются операции дифференцирования, в выходном цифровом потоке сигнала меньшей крутизны Y1= A1ω1 подавляются на фоне сигналов большей крутизны Y2= A2ω2 в соотношении частот  даже при равенстве амплитуд (A1 = A2) на входе кодера. С учетом возможного "перекоса" уровней p = 5 дБ на входе АДИКМ-кодера в пользу составляющей сигнала высшей частоты (A2/A1 ≈ 1,8), ожидается ослабление низкочастотной компоненты в худшем случае более, чем в 4 раза (12 дБ). Степень этого ослабления существенно зависит от того, каков разнос частот ΔF = (Fв - Fн) низкочастотного сигнала Fн по отношению к высокочастотному Fв в составе двухчастотного знака набора номера. Если разнос мал - ΔF =(200 - 400) Гц, подавление составляющей Fн АДИКМ-кодером относительно невелико и порог приема сигнала Fн может быть повышен. В противном случае, при

даже при равенстве амплитуд (A1 = A2) на входе кодера. С учетом возможного "перекоса" уровней p = 5 дБ на входе АДИКМ-кодера в пользу составляющей сигнала высшей частоты (A2/A1 ≈ 1,8), ожидается ослабление низкочастотной компоненты в худшем случае более, чем в 4 раза (12 дБ). Степень этого ослабления существенно зависит от того, каков разнос частот ΔF = (Fв - Fн) низкочастотного сигнала Fн по отношению к высокочастотному Fв в составе двухчастотного знака набора номера. Если разнос мал - ΔF =(200 - 400) Гц, подавление составляющей Fн АДИКМ-кодером относительно невелико и порог приема сигнала Fн может быть повышен. В противном случае, при  = (600 - 1000) Гц, порог приема Fн нужно понизить.

= (600 - 1000) Гц, порог приема Fн нужно понизить.

Таким образом к моменту обработки НЧ компоненты Fн сигнала необходимо иметь информацию о приеме (неприеме) всех ранее обработанных ВЧ составляющих на частотах F > Fн, что позволяет адаптировать порог приема составляющей Fн по результатам анализа предшествующих компонент сигнала.

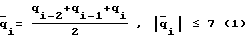

Для коррекции частотной характеристики АДИКМ-кодера необходимо обеспечить подъем уровня нижних частот сигнала. С этой целью нужно подвергнуть поток операции цифрового интегрирования, компенсирующей дифференцирование сигнала в АДИКМ-кодере. В интеграторе 7 АДИКМ-потока, построенном на основе постоянного запоминающего устройства (ПЗУ), реализуется операция вида:

где qi - 4-х разрядный код текущего i-го АДИКМ-отсчета, соответственно qi-1 и qi-2-кода двух предшествующих АДИКМ-отсчетов.

Задержка кодов qi на два отсчета реализуется во входном регистре 6, с выходов которого 12-ти разрядный код трех АДИКМ-отсчетов qi-2, qi-1 и qi подается на адресные входы ПЗУ интегратора 7 АДИКМ-потока. Обработке подвергается отсчет qi-1, расположенный в середине 12-ти разрядной группы. В формуле (1) предполагается алгебраическое сложение кодов отсчетов с учетом их знаков. Предварительно, перед выполнением операции по формуле (1) в ПЗУ интегратора 7 АДИКМ-потока устраняется знакочередование отсчетов, вызванное помехой fn = fкв/2 = 4 кГц, возникающей в АДИКМ-кодере при подаче на его вход сигналов малой крутизны. Если знак отсчета qi-1 отличается одновременно от знаков qi-2 и qi, то в уравнении (1) знак qi-1 изменяется на противоположный. В противном случае, при совпадении знака qi-1 хотя бы с одним из знаков соседних отсчетов, знак qi-1 сохраняется неизменным. Поскольку частоты сигналов (0,425 - 1,7) кГц ниже fn = fкв/2 = 4 кГц, знакочередование отсчетов сигнала в отсутствие помехи невозможно и никакого исправления знаков отсчетов не происходит. В присутствии же fn = 4 кГц на фоне слабого по уровню сигнала, исправление знаков отсчетов способствует частичному подавлению помехи на выходе интегратора 7 АДИКМ-потока. Операция интегрирования по формуле (1) дополнительно снижает уровень помехи в два раза.

Цифровой интегратор 7 АДИКМ-потока обеспечивает подъем уровня сигналов нижних частот Fн = (425 - 500) Гц примерно на 3 дБ и "завал" уровня сигнала верхней частоты Fв = 1700 Гц около 3 дБ. Преобладание сигнала Fн = 700 Гц над сигналом Fв = 1700 Гц на выходе интегратора 7 составляет порядка 5 дБ, что в значительной мере компенсирует "перекос" уровней на выходе АДИКМ-кодере в Fв/Fн ≈ 2,43 раза (7,8 дБ) из-за дифференцирования сигнала.

Дополнительная коррекция частотной характеристики АДИКМ-кодера, направленная на подъем уровня сигналов нижних частот, достигается в приемнике за счет выбора формы последовательностей, поступающих на опорные синусные и косинусные входы коррелометра 9 с выходов формирователя 8 опорных последовательностей.

Последовательности прямоугольного синуса и косинуса (знаковые функции) обрабатываемых частот (425 - 1700)Гц обеспечивают максимальный полезный эффект на выходе коррелометра 9, однако одновременно растут уровни перекрестных помех на частотах  при передаче двухчастотного сигнала Fi,Fк. Если ΔF = (600 - 1000) Гц, перекрестные помехи выходят за пределы спектра двухчастотного сигнала и не представляют опасности. В то же время при τ ≥ 600 Гц НЧ компонента сильно ослабляется на фоне Вч компоненты, и применение прямоугольной опоры при обработке НЧ составляющей сигнала обеспечивает ее подъем на выходе коррелометра 9. Этот подъем пропорционален эффективному значению опорной функции и составляет порядка 3 дБ по сравнению с опорой трапецеидальной (почти синусоидальной) формы. Достоинством трапецеидальной опорной функции является минимум перекрестных помех, благодаря близости формы трапеции к синусоиде. Построив формирователь 8 опорных последовательностей на основе РПЗУ, несложно запрограммировать его по нужному закону для каждой из восьми обрабатываемых частотных составляющих сигнала.

при передаче двухчастотного сигнала Fi,Fк. Если ΔF = (600 - 1000) Гц, перекрестные помехи выходят за пределы спектра двухчастотного сигнала и не представляют опасности. В то же время при τ ≥ 600 Гц НЧ компонента сильно ослабляется на фоне Вч компоненты, и применение прямоугольной опоры при обработке НЧ составляющей сигнала обеспечивает ее подъем на выходе коррелометра 9. Этот подъем пропорционален эффективному значению опорной функции и составляет порядка 3 дБ по сравнению с опорой трапецеидальной (почти синусоидальной) формы. Достоинством трапецеидальной опорной функции является минимум перекрестных помех, благодаря близости формы трапеции к синусоиде. Построив формирователь 8 опорных последовательностей на основе РПЗУ, несложно запрограммировать его по нужному закону для каждой из восьми обрабатываемых частотных составляющих сигнала.

Выбор вида опоры осуществляется с первого выхода решающего блока 13 по результатам последовательного анализа предшествующих частотных составляющих сигнала.

Для синхронизации устройства на входы задающего генератора 5 подаются импульсы тактовой fт = 2048 кГц и цикловой fц = 8 кГц синхронизации.

Время существования четверки данных (Д1 - Д4) на входах согласующего блока 1 составляет τ = Tц/8 ≈ 15,6 мкс, всего за время цикла Tц = 1/fц = 125 мкс проходит по одной четверке данных по каждому из 8-ми каналов.

За время  информация о величине АДИКМ-отсчета данного канала записывается по соответствующему адресу первого 2 либо второго 3 блоков оперативной памяти, работающего на данном интервале времени в режиме записи. Одновременно из другого блока оперативной памяти совершается считывание ранее записанной туда информации на входы данных входного регистра 6, продвигаемого с тактовой частотой fсч = 512 кГц с третьего выхода задающего генератора 5. Противофазная смена режимов записи/считывания первого 2 и второго 3 блоков оперативной памяти обеспечивается соответственно с первого и второго выходов задающего генератора 5.

информация о величине АДИКМ-отсчета данного канала записывается по соответствующему адресу первого 2 либо второго 3 блоков оперативной памяти, работающего на данном интервале времени в режиме записи. Одновременно из другого блока оперативной памяти совершается считывание ранее записанной туда информации на входы данных входного регистра 6, продвигаемого с тактовой частотой fсч = 512 кГц с третьего выхода задающего генератора 5. Противофазная смена режимов записи/считывания первого 2 и второго 3 блоков оперативной памяти обеспечивается соответственно с первого и второго выходов задающего генератора 5.

Совмещенные входы/выходы данных первого 2 и второго 3 блоков оперативной памяти обслуживаются с помощью шинного формирователя с третьим Z - состоянием в составе согласующего блока 1.

Коммутатор 4 адресов, управляемый с первого выхода задающего генератора 5 синхронно со сменой режимов записи/считывания обоих блоков оперативной памяти, обеспечивает нужную последовательность смены кодов на адресных входах блоков оперативной памяти 2 и 3. При этом запись четверок данных (Д1 - Д4) в выбранное ОЗУ происходит в реальном масштабе времени по мере поступления информации т.е. первые отсчеты сигналов всех М = 8 каналов записываются в первые М адресов ОЗУ второе отсчеты - в следующие М адресов и т.д.

Считывание же информации из другого ОЗУ (блока оперативной памяти 2 или 3 на входы данных входного регистра 6 происходит в другой последовательности. Сначала N раз (N = 8 - число частотных составляющих сигнала) считываются все ранее записанные К = (fц•Ta) отсчетов сигнала первого канала, затем K отсчетов второго канала и т.д., где Тa - время анализа, или продолжительность записанного в ОЗУ отрезка группового цифрового АДИКМ-потока. Если запись отсчетов данного канала происходит с частотой fц, то считывание идет с частотой fсч = (M • N)fц, т.е. в (M • N) раз более высокой. При M = N = 8, fсч = 512 кГц.

Подобная организация режимов работы первого и второго блоков оперативной памяти 2,3 позволяет при многоканальной записи информации вести последовательную одноканальную обработку сигнала в режиме считывания. Этим достигается упрощение схемы устройства ценой повышения скорости обработки информации в (M • N) раз. Последовательная обработка каждой из частот сигнала позволяет в N раз сократить количество блоков (8 - 16), т.е. почти в N раз снизить объем оборудования. Кроме того последовательная обработка N частот позволяет повысить помехоустойчивость приема низкочастотных компонент сигнала благодаря использованию предшествующих результатов анализа высокочастотных компонент, что недостаточно при одновременной параллельной обработке всех N частот.

M - канальная запись и одноканальное считывание информации упрощает алгоритм работы устройства, которое превращается по существу в одноканальное с увеличенной в M раз скоростью обработки информации.

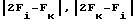

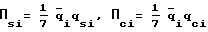

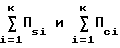

В коррелометре 9 происходит перемножение (с весом 1/7) с учетом знака двоичных 4-х разрядных кодов qi с выходов интегратора 7 АДИКМ-потока на двоичные 4-х разрядные коды синусных qsi и косинусных qci последовательностей с выходов формирователя 8 опорных последовательностей:

Накопление  путем алгебраического суммирования (К) 4-х разрядных кодов Пsi и Пci соответственно в сумматоре 10 синусной составляющей сигнала и сумматоре 11 косинусной составляющей сигнала в течение времени анализа Ta позволяет получить на входах вычислительного блока 12 оценку взаимной корреляции сигнала с опорными функциями на данной частоте:

путем алгебраического суммирования (К) 4-х разрядных кодов Пsi и Пci соответственно в сумматоре 10 синусной составляющей сигнала и сумматоре 11 косинусной составляющей сигнала в течение времени анализа Ta позволяет получить на входах вычислительного блока 12 оценку взаимной корреляции сигнала с опорными функциями на данной частоте:

ϕ

где ϕ - фазовый сдвиг между сигналом и синусной опорной функцией;

Um - амплитуда входного синусоидального сигнала.

Фактически вместо амплитуды сигнала Um выражения для Rs, Rc следует подставлять модуль максимального АДИКМ-кода qi, изменяющегося в пределах ±7. Благодаря адаптации шага кодера к крутизне сигнала в широком диапазоне значений y =  Um, независимо от частоты и уровня одночастотного сигнала, имеем для трапецеидальных опорных функций qsi и qci;

Um, независимо от частоты и уровня одночастотного сигнала, имеем для трапецеидальных опорных функций qsi и qci;

Для прямоугольных опорных последовательностей

ϕ

Неравенства 2, 3 превращаются в равенства при перегрузках АДИКМ-кодера, когда сигнал на его выходе становится трапецеидальным с амплитудой Um = 7. Поскольку фаза  случайна и неизвестна на приеме, необходима обработка как синусной, так и косинусной составляющих сигнала.

случайна и неизвестна на приеме, необходима обработка как синусной, так и косинусной составляющих сигнала.

Вычислительный блок 12 на основе РПЗУ выполняет операцию вида:

ϕ

Код R на выходе вычислительного блока 12 не зависит от фазы ϕ сигнала и определяется только взаимной корреляцией сигнала с опорными функциями. При несовпадении частот сигнала и опорных функций, значения Rs, Rc и R стремятся к нулю при условии, что в интервале анализа Ta укладывается целое число периодов сигнала. Если это условие не выполняется, на соседних частотах возникают помехи, составляющие ориентировочно (1/2F • Ta) часть уровня полезного сигнала.

В середине интервала анализа данного канала, после обработки (К/2) АДИКМ-отсчетов сигнала, накопленный код R поступает с выходов вычислительного блока 12 на четыре первых входа решающего блока 13. На три последующих входа решающего блока 13 подается трехразрядный код порядкового номера обрабатываемой частоты с соответствующих выходов решающего блока 13, построенного на основе РПЗУ, поступает по цепи обратной связи с выходного регистра 17 информация о результатах обработки предшествующих частотных составляющих сигнала, начиная с F1 = 1700 Гц и кончая F8 = 425 Гц.

В решающем блоке 13 вырабатывается адаптивный код порога, пропорциональный коду сигнала, накопленному за первую половину интервала анализа. Адаптивный код порога вырабатывается с учетом номинала обрабатываемой частоты, а также на основе информации о значениях ранее принятых более высокочастотных составляющих сигнала. На основе этой информации в решающем блоке 13 вырабатывается также решение о виде опорной функции, которое с первого выхода решающего блока 13 поступает на вход формирователя 8 опорных последовательностей.

Для хранения адаптивного кода порога используется регистр 14 адаптивного кода, тактируемый в середине интервала обработки импульсов с четвертого выхода задающего генератора 5.

В конце интервала обработки данной частотной составляющей сигнала по очередному каналу адаптивный код порога с выходов регистра 14 адаптивного кода сравнивается в компараторе 15 кода порога с кодом R с выходов младших разрядов вычислительного блока 12. Если порог превышен, с выхода компаратора 15 кода порога на вход элемента 16 ИЛИ поступает импульс, свидетельствующий о приеме данной частотной компоненты сигнала.

Если код Rs с выхода сумматора 10 синусной составляющей сигнала или код Rc с выхода сумматора 11 косинусной составляющей сигнала, либо код R с выхода вычислительного блока 12 имеют единицу в разрядах 256 или 512, то с помощью элемента 16 ИЛИ по его первым, либо вторым входам принимается решение о приеме данной частотной компоненты сигнала. Информация записывается в выходной регистр 17 и поступает по цепи обратной связи на восемь информационных входов решающего блока 13.

К моменту начала обработки очередной частотной составляющей сигнала на опорном входе формирователя 8 опорных последовательностей подготавливается информация о форме опорных последовательностей (например, 1-прямоугольная, 0-трапецеидальная). На выходах формирователя 8 опорных последовательностей возникают потоки четырехразрядных кодов qsi синусной и qci косинусной компонент очередной обрабатываемой гармонической составляющей сигнала "при смене i = 1, 2... К кодов на входах формирователя 8 опорных последовательностей с адресных выходов задающего генератора 5.

В идентичных накапливающих сумматорах синусной 10 и косинусной 11 составляющих сигнала происходит суммирование К = (fц • Ta) четырехразрядных двоичных кодов с учетом их знака (первый разряд) и модуля (три младших разряда).

Каждый из сумматоров 10 и 11, построенный по стандартной схеме, содержит 4-х разрядный сумматор кода, параллельный 4-х разрядный регистр и счетчик импульсов с выхода переполнения p1 сумматора. С целью формирования дополнительных кодов nдоп = (16 - n) при суммировании отрицательных чисел, каждый из сумматоров 10 и 11 содержит также по четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а суммирование дополнительной единицы происходит по знаковому разряду с использованием входа P0 сумматора.

Запись кода в регистр сумматора по входу C совершается тактовыми импульсами с третьего выхода задающего генератора 5. Сброс накапливающих сумматоров 10 и 11 в нуль в момент начала обработки очередной частотной компоненты сигнала происходит с четвертого выхода задающего генератора 5, одновременно осуществляется запись предшествующей информации в выходной регистр 17.

В момент окончания обработки всех восьми частотных составляющих сигнала, на втором и третьем выходах решающего блока 13 появляется информация в двоичном коде о количестве принятых частотных компонент (00 - нет приема, 01 - одночастотный, 10 - двухчастотный, 11 - трех - и более частотный прием). Эта информация по девятой и десятой выходным шинам устройства поступает в сопряженную с приемником специализированную ЭВМ, которая управляет коммутационным оборудованием электронной АТС.

Одновременно по первым восьми выходным шинам устройства в ЭВМ подается информация о принятых сигналах управления и взаимодействия в составе АДИКМ-потока данного канала. Информация по каждой из восьми шин выдается в виде "Лог.1" - есть прием данной частотной составляющей, "Лог.0" - нет приема.

Сигналы готовности к выдаче информации и номера канала, по которому она принята, передаются в ЭВМ импульсами тактовой Fт и цикловой Fц синхронизации по одиннадцатой и двенадцатой выходным шинам соответственно с пятого и шестого выходов задающего генератора 5.

По окончании интервала обработки Tа вся ранее записанная во втором блоке оперативной памяти 3 информации оказывается считанной, а в первый блок оперативной памяти 2 за это время записывается отрезок Tа новой информации. По входам записи/считывания с первого и второго выходов задающего генератора 5 режимы работы обоих ОЗУ меняются на противоположные.

Одновременно с выходов коммутатора 4 адресов сетки частот на адресных входах блоков оперативной памяти 2 и 3 меняются местами так, что в блок оперативной памяти 3 начинается многоканальная запись, а из блока оперативной памяти 2 - одноканальное считывание информации. Необходимые сетки частот, начиная от fмакс = (M • N) fц и кончая fмин = 1/2Tа, вырабатываются в задающем генераторе 5 путем синхронного деления частоты тактовых импульсов fт = 2048 кГц на его первом входе. Цикловая синхронизация устройства достигается за счет импульсов fц = 8 кГц на втором входе задающего генератора 5 путем сброса в нуль с периодом Tц = 1/fц счетчиков импульсов (f ≥ fц) в составе задающего генератора 5.

На последующих интервалах Tа все вышеописанные процессы в схеме приемника повторяются аналогично предыдущему.

1. Брунченко А. В. , Охинченко В.П., Седов А.Е., Цифровые обнаружители гармонических составляющих для сигналов с адаптивной дельта-модуляцией. Электросвязь, N 10, 1987. \\\ 2. Авторское свидетельство N 1640742, кл. Н 04 Q 1/457, 1991.

Использование: в технике электросвязи и предназначено, в частности для приема сигналов управления и взаимодействия, передаваемых в составе группового 8-ми канального цифрового потока 256 кБит/с с адаптивной дифференциальной импульсно-кодовой модуляцией (АДИКМ). Сущность изобретения: цифровой групповой приемник сигналов управления и взаимодействия с АДИКМ содержит согласующий блок 1, первый и второй блоки оперативной памяти 2, 3, коммутатор 4 адресов, задающий генератор 5, формирователь 8 опорных последовательностей, коррелометр 9, сумматор 10 синусной составляющей сигнала, сумматор 11 косинусной составляющей сигнала, вычислительный блок 12, решающий блок 13, регистр 14 адаптивного кода, компаратор 15 кода порога, элемент ИЛИ 16 и выходной регистр 17. Данный приемник обеспечивает повышение помехоустойчивости расширение динамического диапазона уровней приема и стабилизация полосы пропускания устройства. 1 ил.

Цифровой групповой приемник сигналов управления и взаимодействия с адаптивной дифференциальной импульсно-кодовой модуляцией, содержащий последовательно соединенные задающий генератор, коммутатор адресов и первый блок оперативной памяти, а также сумматоры синусной и косинусной составляющих сигналов, компаратор кода порога, регистр адаптивного кода, вычислительный блок, отличающийся тем, что в него введены последовательно соединенные согласующий блок, входной регистр, интегратор потока с адаптивной дифференциальной импульсно-кодовой модуляцией и коррелометр, а также второй блок оперативной памяти, формирователь опорных последовательностей, решающий блок, элемент ИЛИ и выходной регистр, при этом выходы согласующего блока соединены с сигнальными входами/выходами первого блока оперативной памяти и второго блока оперативной памяти, к адресным входам которого подключены соответствующие выходы коммутатора адресов, адресные выходы задающего генератора соединены с первой группой входов решающего блока и через формирователь опорных последовательностей с опорными синусными и косинусными входами коррелометра, синусные и косинусные кодовые выходы которого соединены соответственно с входами сумматоров синусной и косинусной составляющих сигнала, выходы двух старших разрядов выходных кодов соединены с соответствующими входами элемента ИЛИ, а выход знакового разряда и выходы группы младших разрядов выходных кодов с соответствующими входами вычислительного блока, выходы младших разрядов выходного кода которого соединены с второй группой входов решающего блока и с первой группой входов компаратора кода порога, выход которого и выход старшего разряда выходного кода вычислительного блока через элемент ИЛИ соединены с входом данных выходного регистра, выходы которого соединены с третьей группой входов решающего блока, кодовые выходы которого через регистр адаптивного кода соединены с второй группой входов компаратора кода порога, причем первый и второй выходы задающего генератора соединены соответственно с входами записи/считывания первого и второго блоков оперативной памяти, третий выход задающего генератора соединен с управляющим входом согласующего блока и с тактовым входом входного регистра, четвертый выход задающего генератора соединен с входом синхронизации сумматоров синусной и косинусной составляющих сигнала, входы сбора которых соединены с тактовыми входами регистра адаптивного кода и выходного регистра и с пятым выходом задающего генератора, первый выход решающего блока соединен с опорным входом формирователя опорных последовательностей, другая группа адресных входов которого соединена с соответствующими входами коммутатора адресов, входы данных согласующего блока являются входами четырехразрядного кода отсчета сигнала очередного канала устройства, входы задающего генератора соответственно входами последовательности импульсов тактовой и цикловой синхронизации устройства, выходами и выходами сигналов тактового и цикловой синхронизации которого являются соответственно выходы выходного регистра, второй и третий выходы решающего блока и выходы сигналов тактовой и цикловой синхронизации задающего генератора.

| SU, авторское свидетельство, 16407426, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-01-27—Публикация

1993-02-01—Подача