Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и системах управления.

Известен сдвигающий регистр (см. книгу: И.С. Потемкин. Функциональные узлы цифровой автоматики. М.: Энергоатомиздат, 1988, с. 277, рис. 10.1а), содержащий D-триггеры по количеству разрядов. Информационный вход D-триггера первого разряда соединен с входной шиной, информационные входы D-триггеров остальных разрядов подключены к прямым выходам D-триггеров предыдущих разрядов. Тактовые входы D-триггеров всех разрядов объединены и соединены с тактовой шиной. Прямой выход D-триггера последнего разряда соединен с выходной шиной.

Недостатком сдвигающего регистра является низкая достоверность результатов ввода и сдвига информации, обусловленная отсутствием у него способности самостоятельно обнаруживать в процессе работы отказы и сбои D-триггеров (например, при воздействии помех по входной или тактовой шинам или шинам питания).

Известен сдвигающий регистр (см. книгу: И.С. Потемкин. Функциональные узлы цифровой автоматики. М.: Энергоатомиздат, 1988, с. 277, рис. 10.1в), который является прототипом и содержит в каждом разряде два тактируемых уровнем D-триггера. Информационный вход первого D-триггера первого разряда соединен с входной шиной, информационные входы первых D-триггеров остальных разрядов соединены с прямыми выходами вторых D-триггеров предыдущих разрядов. Прямой выход второго D-триггера последнего разряда соединен с выходной шиной. Тактовые входы первых D-триггеров всех разрядов соединены с первой тактовой шиной, прямые выходы - с информационными входами вторых D-триггеров соответствующих разрядов, тактовые входы вторых D-триггеров всех разрядов соединены с второй тактовой шиной.

Недостатком данного сдвигающего регистра является низкая достоверность результатов ввода и сдвига информации, обусловленная отсутствием у него способности самостоятельно обнаруживать в процессе работы отказы и сбои D-триггеров, входящих в его состав (например, из-за несанкционированных переключений RS-триггеров, входящих в состав этих D-триггеров, при воздействии помех по цепям питания, импульсных ионизирующих излучений и т.д.).

Достигаемым техническим результатом является повышение достоверности результатов ввода и сдвига информации за счет обеспечения постоянного автоматического самоконтроля правильности функционирования в процессе работы.

Указанный технический результат достигается тем, что в сдвигающий регистр, содержащий в каждом разряде два тактируемых уровнем D-триггера, информационный вход первого D-триггера первого разряда соединен с входной шиной, информационные входы первых D-триггеров остальных разрядов соединены с прямыми выходами вторых D-триггеров предыдущих разрядов, прямой выход второго D-триггера последнего разряда соединен с выходной шиной, тактовые входы первых D-триггеров разрядов соединены с тактовой шиной, прямые выходы - с информационными входами вторых D-триггеров соответствующих разрядов, тактовые входы вторых D-триггеров разрядов объединены, введены две контрольные шины, две схемы сравнения кодов, два формирователя одиночного импульса, три элемента ИЛИ-НЕ, два элемента И-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и инвертор, вход которого соединен с тактовой шиной, выход - с точкой соединения тактовых входов вторых D-триггеров разрядов, информационный вход и прямой выход первого D-триггера каждого разряда соединены соответственно с первым и вторым входами соответствующего разряда первой схемы сравнения кодов, информационный вход и прямой выход второго D-триггера каждого разряда соединены соответственно с первым и вторым входами соответствующего разряда второй схемы сравнения кодов, выходы первой и второй схем сравнения кодов соединены с первыми входами соответственно первого и второго элементов ИЛИ-НЕ, выходы которых соединены с соответствующими входами третьего элемента ИЛИ-НЕ, выход которого соединен с первой контрольной шиной и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы первого и второго формирователей одиночного импульса соединены соответственно с тактовой шиной и выходом инвертора, выход первого формирователя одиночного импульса соединен с вторым входом первого элемента ИЛИ-НЕ и с первым входом первого элемента И-НЕ, второй вход которого соединен с тактовой шиной, выход - с первым входом второго элемента И-НЕ, второй вход которого соединен с прямым выходом первого D-триггера первого разряда, выход - с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с второй контрольной шиной, выход второго формирователя одиночного импульса соединен с вторым входом второго элемента ИЛИ-НЕ.

Кроме того, тактируемый уровнем D-триггер выполнен в виде D-триггера типа "прозрачная защелка" с повышенной инерционностью, который содержит два элемента И, элемент ИЛИ-НЕ, триггер Шмитта, резистор, конденсатор и два инвертора, причем вход первого инвертора объединен с первым входом первого элемента И и является тактовым входом D-триггера, второй вход первого элемента И является информационным входом D-триггера, выход первого инвертора соединен с первым входом второго элемента И, второй вход которого соединен с выходом второго инвертора, являющимся прямым выходом D-триггера, выходы элементов И соединены с соответствующими входами элемента ИЛИ-НЕ, выход которого через резистор соединен с первым выводом конденсатора и входом триггера Шмитта, выход которого соединен с входом второго инвертора, второй вывод конденсатора соединен с общей шиной.

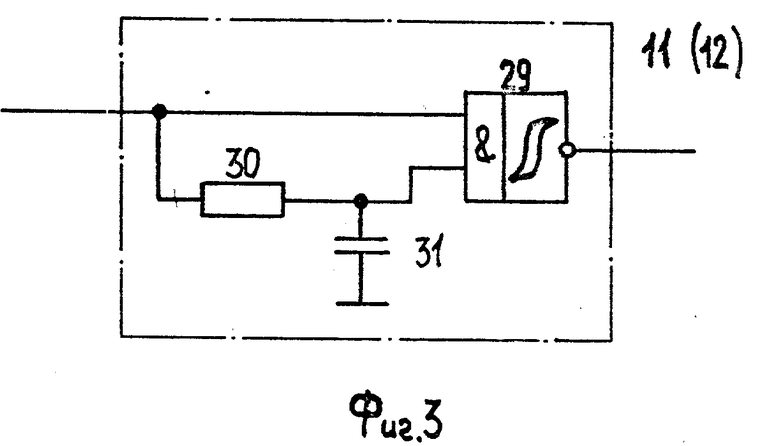

Кроме того, формирователь одиночного импульса содержит элемент И, триггер Шмитта, инвертор, резистор и конденсатор, причем первый вход элемента И соединен через резистор с его вторым входом и первым выводом конденсатора и является входом формирователя, второй вывод конденсатора соединен с общей шиной, выход элемента И через триггер Шмитта соединен с входом инвертора, выход которого является выходом формирователя.

Указанная совокупность признаков позволяет повысить достоверность результатов ввода и сдвига информации в сдвигающем регистре за счет осуществления постоянного самоконтроля правильности функционирования с выдачей соответствующих сигналов о фактах сбоев (или отказа) в процессе работы и о факте ввода в первый разряд каждого единичного символа кода вводимой информации.

На фиг. 1 приведена схема сдвигающего регистра в четырехразрядном исполнении, на фиг. 2 и фиг. 3 - схемы возможных вариантов реализаций D-триггера и формирователя одиночного импульса соответственно, на фиг. 4 - временные диаграммы работы отдельных элементов устройства, где Vi - выходной сигнал i-го элемента устройства на фиг. 1.

Устройство содержит тактируемые уровнем D-триггеры 1...8 (1, 3, 5, 7 - первые D-триггеры разрядов, а 2, 4, 6, 8 - вторые D-триггеры), первую 9 и вторую 10 схемы сравнения кодов, первый 11 и второй 12 формирователи одиночного импульса, инвертор 13, первый 14, второй 15 и третий 16 элементы ИЛИ-НЕ, первый 17 и второй 18 элементы И-НЕ и элемент 19 ИСКЛЮЧАЮЩЕЕ ИЛИ. Информационный вход D-триггера 1 соединен с входной шиной 20, прямой выход D-триггера 8 соединен с выходной шиной 21. Информационные входы D-триггеров 2...8 подключены к прямым выходам D-триггеров 1...7 соответственно. Тактовые входы D-триггеров 1, 3, 5, 7 соединены с тактовой шиной 22, тактовые входы D-триггеров 2, 4, 6, 8 - с выходом инвертора 13, вход которого соединен с тактовой шиной 22. Информационные входы и прямые выходы D-триггеров 1, 3, 5, 7 соединены соответственно с первыми и вторыми входами соответствующих разрядов схемы сравнения кодов 9, а информационные входы и прямые выходы D-триггеров 2, 4, 6, 8 соединены соответственно с первыми и вторыми входами соответствующих разрядов схемы сравнения кодов 10. Выходы схем сравнения кодов 9, 10 соединены с первыми входами элементов 14, 15 ИЛИ-НЕ соответственно. Входы формирователей 11 и 12 соединены с тактовой шиной 22 и выходом инвертора 13 соответственно. Выход формирователя 11 соединен с вторым входом элемента 14 ИЛИ-НЕ и первым входом элемента 17 И-НЕ, выход формирователя 12 соединен с вторым входом элемента 15 ИЛИ-НЕ. Второй вход элемента 17 И-НЕ соединен с тактовой шиной 22, выход - с первым входом элемента 18 И-НЕ, второй вход которого соединен с прямым выходом D-триггера 1. Выходы элементов 14, 15 ИЛИ-НЕ соединены с соответствующими входами элемента 16 ИЛИ-НЕ, выход которого соединен с первой контрольной шиной 23 и первым входом элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом элемента 18 И-НЕ, выход - с второй контрольной шиной 24.

Каждый из D-триггеров 1...8 выполнен в виде D-триггера типа "прозрачная защелка" с повышенной инерционностью (фиг. 2), который содержит элемент 25 И-ИЛИ-НЕ, триггер Шмитта 26, резистор 27 и конденсатор 28. Первый вход первого элемента И и первый (инверсный) вход второго элемента И элемента 25 И-ИЛИ-НЕ объединены и являются тактовым входом D-триггера. Второй вход первого элемента И элемента 25 И-ИЛИ-НЕ является информационным входом D-триггера. Инверсный выход триггера Шмитта 26 соединен с вторым входом второго элемента И элемента 25 И-ИЛИ-НЕ и является прямым выходом D-триггера. Выход элемента 25 И-ИЛИ-НЕ через резистор 27 соединен с первым выводом конденсатора 28 и входом триггера Шмитта 26. Второй вывод конденсатора 28 соединен с общей шиной.

Каждый из формирователей одиночного импульса 11, 12 выполнен по схеме, приведенной на фиг. 3, и содержит триггер Шмитта 29 с элементом И на входе, резистор 30 и конденсатор 31. Первый вход элемента И триггера Шмитта 29 через резистор 30 соединен с его вторым входом и первым выводом конденсатора 31 и является входом формирователя. Второй вывод конденсатора 31 соединен с общей шиной. Инверсный выход триггера Шмитта 29 является выходом формирователя.

Устройство работает следующим образом.

В исходном состоянии на входной шине 20 и на тактовой шине 22 устройства поддерживаются уровни логического нуля (здесь и далее в тексте уровни сигналов соответствуют положительной логике), D-триггеры 1...8 находятся в исходном (нулевом) состоянии, на их прямых выходах - уровни логического нуля, следовательно, на выходах схем сравнения кодов 9, 10 - уровни логической единицы. На выходе инвертора 13 - уровень логической единицы, на выходе формирователя 11 - уровень логической единицы, на выходе формирователя 12 - уровень логического нуля. На выходной шине 21 и на контрольной шине 24 - уровни логического нуля, а на контрольной шине 23 - уровень логической единицы. Конденсаторы D-триггеров 1...8 (фиг. 3, конденсатор 28) в исходном состоянии заряжены, конденсатор формирователя 11 (фиг. 4) разряжен, а конденсатор формирователя 12 заряжен до уровня логической единицы. Такое исходное состояние устройства сохраняется до подачи соответствующих сигналов по входной шине 20 и тактовой шине 22. В указанное исходное состояние устройство может быть установлено путем подачи по входной шине 20 уровня логического нуля и тактовых импульсов по тактовой шине 22 или (при необходимости) путем подачи импульса сброса на входы сброса D-триггеров 1...8 (входы сброса указанных триггеров на фиг. 1 и фиг. 2 не показаны).

Работа устройства начинается при подаче по входной шине 20 первого символа двоичного кода вводимой информации и тактового импульса. При этом нет необходимости в жесткой синхронизации фронтов тактового импульса и символа (единичного) вводимого кода, поскольку D-триггеры 1...8 устройства тактируются уровнем сигнала на тактовых входах, а единичный символ кода вводимой информации может быть снят как одновременно с тактовым импульсом, так и после него. Рассмотрим работу устройства (фиг. 1) в течение первых трех тактов на примере ввода и сдвига первых трех символов (например, символов 1, 0, 1) вводимого в устройство кода.

После подачи по входной шине 20 первого символа (1) кода с уровнем логической единицы (фиг. 4, V20, момент t1) и тактового импульса (фиг. 4, V22, момент t1) через время, необходимое для разряда до уровня логического нуля конденсатора, входящего в состав D-триггера 1 - первого D-триггера первого разряда устройства (фиг. 3, конденсатор 28), D-триггер 1 принимает единичное состояние. При этом на его прямом выходе появляется уровень логической единицы (фиг. 4, V1, момент t2). После окончания первого тактового импульса D-триггер 1 остается в единичном состоянии, а на выходе инвертора 13 устанавливается уровень логической единицы (фиг. 4, V13, момент t4). Через время, необходимое для разряда конденсатора D-триггера 2 - второго D-триггера первого разряда устройства (фиг. 3; конденсатор 28), D-триггер 2 также принимает единичное состояние (фиг. 4, V12, момент t4). Таким образом, в интервале после первого тактового импульса в D-триггер 2 записывается состояние D-триггера 1, которое последний принял в течение первого тактового импульса.

Для ввода в устройство второго символа (0) кода и сдвига первого его символа (1), введенного в первом такте в первый разряд устройства, в следующий его разряд по входной шине 20 нужно подать уровень логического нуля и по тактовой шине 22 - следующий (второй) тактовый импульс (фиг. 4, V22, момент t7). При этом через время, необходимое для заряда до уровня логической единицы конденсатора D-триггера 1 (фиг. 3, конденсатор С 28), последний принимает состояние логического нуля (фиг. 4, V1, момент t8). Одновременно D-триггер 3 переключается (аналогично D-триггеру 1 по первому тактовому импульсу) в единичное состояние (фиг. 4, V3, момент t8), то есть он принимает единичное состояние D-триггера 2, в которое тот переключился после первого тактового импульса (в интервале между первым и вторым тактовыми импульсами). После окончания второго тактового импульса D-триггер 1 остается в новом состоянии логического нуля, D-триггер 3 - в новом состоянии логической единицы, в D-триггер 2 (через время, необходимое для заряда его конденсатора до уровня логической единицы) переписывается новое (нулевое) состояние логического нуля D-триггера 1 (фиг. 4, V2, момент t11), а в D-триггер 4 (через время, необходимое для разряда его конденсатора до уровня логического нуля) - новое (единичное) состояние D-триггера 3 (фиг. 4, V4, момент t11).

Необходимо здесь отметить, что на фиг. 4 задержки переключения D-триггеров устройства относительно фронта и среза тактовых импульсов, то есть постоянные заряда и разряда конденсаторов D-триггеров приняты одинаковыми.

Для ввода в устройство третьего символа (1) кода и сдвига его первых двух символов, уже находящихся в первых двух разрядах устройства, по входной шине 20 нужно подать уровень логической единицы и по тактовой шине 22 - следующий (третий) тактовый импульс (фиг. 4, V22, момент t13). При этом через время, необходимое для перезаряда конденсаторов, D-триггеры 1, 5 переключаются в единичное состояние, D-триггер 3 - в нулевое (фиг. 4, V1, V3, V5, момент t14), а D-триггеры 2, 4, 6 пока сохраняют свои состояния, принятые ими в интервале между вторым и третьим тактовыми импульсами. После окончания третьего тактового импульса D-триггеры 1, 3, 5 сохраняют свои указанные новые состояния (фиг. 4, V1, V3, V5, момент t16), а в D-триггеры 2, 4, 6 (через время, необходимое для перезаряда их конденсаторов) записываются новые состояния D-триггеров 1, 3, 5 соответственно (фиг. 4, V2, V4, V6, момент t17).

Таким образом, после трех тактовых импульсов в D-триггерах 5, 6 третьего разряда устройства оказывается записанным первый символ (1) вводимого кода, в D-триггерах 3, 4 второго разряда - второй символ (0), а в D-триггерах 1, 2 первого разряда - третий символ (1). При этом по каждому тактовому импульсу D-триггер 1 принимает состояние, соответствующее уровню сигнала на входной шине 20, а остальные D-триггеры с нечетными номерами - состояние предыдущих D-триггеров. После тактовых импульсов (в интервале между тактовыми импульсами) все D-триггеры с четными номерами принимают состояния предыдущих D-триггеров.

При подаче по входной шине 20 последующих символов кода и соответствующих им тактовых импульсов устройство работает аналогично. После подачи по входной шине 20 количества символов кода, равного количеству разрядов устройства (в нашем случае - равного 4), и соответствующего количества тактовых импульсов первый символ кода, потактно сдвигаясь вправо, оказывается записанным в D-триггерах 7, 8 и поступает на выходную шину 21. При подаче (при необходимости) по входной шине 20 последующих символов вводимого кода и соответствующих им тактовых импульсов по тактовой шине 22 или подаче одних только тактовых импульсов первый и последующие символы кода последовательно потактно будут "выталкиваться" из устройства по выходной шине 21.

Одновременно с вводом и сдвигом символов вводимого кода устройство осуществляет постоянный автоматический самоконтроль правильности своего функционирования. Результаты самоконтроля периодически выдаются в течение тактовых импульсов по контрольным шинам 23 и 24. При этом по контрольной шине 23 выдается факт отказов и сбоев устройства, а по контрольной шине 24 - факт ввода в устройство (записи в первый D-триггер 1 первого разряда устройства) очередного единичного символа кода. Происходят указанный самоконтроль функционирования устройства и формирование его результатов следующим образом.

Схемы сравнения кодов 9 и 10 осуществляют непрерывный контроль за состояниями информационных входов и прямых выходов D-триггеров 1, 3, 5, 7 и 2, 4, 6, 8 соответственно. При этом любые отличия (несовпадения) логических уровней сигналов на указанных выходах соответствующих D-триггеров схемами сравнения кодов 10, 11 обнаруживаются, чему соответствуют уровни логического нуля на их выходах (фиг. 4, V9, интервалы t2 - t1, t8 - t4, t14 - t11; V10, интервалы t5 - t2, t11 - t8, t17 - t14). Однако при нормальной работе устройства эти несовпадения во времени уровней сигналов на информационных входах и прямых выходах D-триггеров 1...8, обусловленные алгоритмом работы и параметрами элементов устройства, завершаются до момента появления импульсных сигналов с уровнем логического нуля (импульсов опроса) на выходах формирователей 11, 12. При этом указанные несовпадения уровней сигналов на информационных входах и прямых выходах D-триггеров 1, 3, 5, 7 с нечетными номерами завершаются до появления импульсов опроса с выхода формирователя 11 (фиг. 4, V11, моменты t3, t9, t15 и т.д.), а у D-триггеров 2, 4, 6, 8 с четными номерами - до появления импульсов опроса с выхода формирователя 12 (фиг. 4, V12, моменты t6, t12 и т.д.). Поэтому при нормальной работе устройства в процессе ввода и сдвига символов кода совпадения во времени сигналов с уровнем логического нуля на входах элементов 14, 15 ИЛИ-НЕ не будет, следовательно, на их выходах постоянно будут сохраняться уровни логического нуля, а на выходе элемента 16 ИЛИ-НЕ - уровень логической единицы, что означает отсутствие сбоев (отказов). При наличии несовпадения уровней сигналов на упомянутых выводах D-триггеров 1...8 (из-за сбоев или отказов последних) в течение импульсов опроса на выходах формирователей 11, 12 на входах элемента 14 ИЛИ-НЕ и (или) на входах элемента 15 ИЛИ-НЕ совпадут уровни логического нуля, что приведет к появлению на выходе элемента 16 ИЛИ-НЕ (и на контрольной шине 23) уровня логического нуля (в течение соответствующего импульса опроса) - сигнала сбоя (отказа).

Кроме того, элементы 17 И-НЕ и 18 И-НЕ устройства контролируют состояние прямого выхода D-триггера 1 - первого D-триггера первого разряда устройства в течение тактового импульса на тактовой шине 22, то есть тогда, когда очередной символ кода вводится в устройство. Если к моменту поступления импульса опроса с выхода формирователя 11 на соответствующий вход элемента 17 И-НЕ (фиг. 4, V11, моменты t3, t9,15 и т.д.) на другом входе последнего будет уровень логической единицы, то это приведет к появлению в течение указанного импульса опроса уровня логической единицы на выходе элемента 24 ИСКЛЮЧАЮЩЕЕ ИЛИ - "квитанции" о вводе в устройство очередного единичного символа кода (фиг. 4, V24, интервалы t4 - t3, t16 - t15 и т.д.). При вводе нулевого символа кода уровень логического нуля на выходе элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ в течение указанного импульса опроса сохраняется (фиг. 4, V24, интервал t10 - t9).

Таким образом, устройство в процессе работы осуществляет постоянный самоконтроль за правильностью ввода и сдвига символов кода вводимой информации с выдачей контрольных сигналов о наличии сбоев (отказов) в D-триггерах 1. ..8 разрядов и о факте приема (записи) в первый разряд устройства каждого единичного символа кода, что существенно повышает достоверность результатов ввода и сдвига информации.

Кроме того, выполнение D-триггеров 1...8 устройства на D-триггерах типа "прозрачная защелка" с повышенной инерционностью обеспечивает устойчивость устройства к воздействию помех по входной шине 20, по тактовой шине 22 и по шинам питания, поскольку для несанкционированного изменения текущих состояний D-триггеров 1...8 устройства эти помехи должны иметь длительность, достаточную для перезаряда конденсаторов указанных D-триггеров до соответствующих логических уровней.

В целях подтверждения осуществимости заявляемого объекта и достигнутого технического результата в институте был изготовлен и испытан в диапазоне температур окружающей среды от минус 50oC до 50oC лабораторный макет устройства, реализованный по схеме фиг. 1 (фиг. 2, фиг. 3) на базе микросхем серии 564, дискретных резисторов типа С2-33Н и конденсаторов типа К10-17. При этом схемы сравнения кодов 9, 10 были реализованы на микросхеме 564ИП2, триггеры Шмитта 26, входящие в состав D-триггеров 1...8, - на элементах микросхемы 564ТЛ1 с объединенными входами, а остальные логические элементы - на базе стандартных логических элементов И-НЕ, ИЛИ-НЕ указанной серии микросхем. Проведенные испытания показали осуществимость заявляемого сдвигающего регистра и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1999 |

|

RU2173938C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| МНОГОКАНАЛЬНЫЙ ДАТЧИК ОДИНОЧНЫХ ИМПУЛЬСОВ | 1996 |

|

RU2118042C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИНАРНОГО КОДА В ФАЗОМАНИПУЛИРОВАННЫЙ КОД | 1999 |

|

RU2159988C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1999 |

|

RU2180985C2 |

| КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2184825C2 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1997 |

|

RU2129332C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и системах управления. Достигаемый технический результат - повышение достоверности результатов ввода и сдвига информации. Сдвигающий регистр содержит тактируемые уровнем D-триггеры 1...8, схемы сравнения 9, 10, формирователи одиночного импульса 11, 12, инвертор 13, элементы 14, 15, 16 ИЛИ-НЕ, элементы 17, 18 И-НЕ, элемент 19 ИСКЛЮЧАЮЩЕЕ ИЛИ, входную 20, выходную 21 и тактовую 22 шины, контрольные шины 23, 24. Технический результат достигнут введением схем сравнения кодов 9, 10, формирователей 11, 12, инвертора 13, элементов 14, 15, 16 ИЛИ-НЕ, элементов 17, 18 И-НЕ, элемента 19 ИСКЛЮЧАЮЩЕЕ ИЛИ, контрольных шин 23, 24 и новых функциональных связей между элементами. 2 з.п. ф-лы, 4 ил.

| Потемкин И.С | |||

| Функциональные узлы цифровой автоматики | |||

| - М.: Энергоатомиздат, 1988, с.276 и 277, рис.10.1а,в. |

Авторы

Даты

1998-02-20—Публикация

1995-08-16—Подача