Изобретение относится к автоматике и вычислительной технике и может быть использовано для формирования импульсов, свободных от влияния дребезга контактов в устройствах с механическими контактами, и для формирования коротких одиночных импульсов по фронту длинных импульсных или потенциальных сигналов.

Известен формирователь одиночных импульсов (см. авт. св. СССР N 928625, кл. H 03 K 5/01, 5/153, 27.08.80 "Формирователь одиночных импульсов с защитой от дребезга контактов", авторы Н.Н. Ведерников и Л.А. Мальщукова, опубл. в БИ N 18, 1982), содержащий переключатели, средние контакты которых подключены к общей шине, инверторы и элементы И-НЕ по количеству переключателей, триггер памяти, многовходовой элемент ИЛИ-НЕ, подключенный к нулевому входу триггера памяти, элемент И, дополнительный инвертор, дополнительный элемент И-НЕ и счетный триггер. Выход триггера памяти соединен с нулевым входом счетного триггера и с одним из входов элемента И, другие входы которого соединены с нулевым выходом счетного триггера и с шиной инверсии синхроимпульсов, а выход - со счетным входом счетного триггера и с первыми входами элементов И-НЕ. Вторые входы элементов И-НЕ подключены к нормально замкнутым контактам переключателей и через соответствующие инверторы соединены с входами многовходового элемента ИЛИ-НЕ. Нормально разомкнутые контакты переключателей объединены между собой и через дополнительный инвертор соединены с первым входом дополнительного элемента И-НЕ, второй вход которого подключен к шине синхроимпульсов, а выход - единичному входу триггера памяти.

Недостатками этого формирования являются

отсутствие возможности обеспечения гарантированной задержки и регулирования времени задержки формирования выходного импульса относительно момента замыкания нормально разомкнутых контактов переключателей;

отсутствие возможности регулирования длительности выходного импульса без изменения периода следования синхроимпульсов;

отсутствие возможности формирования импульсов разной длительности для разных переключателей (датчиков);

возможность укорочения выходных импульсов при несанкционированных переключениях счетного триггера от внутренних помех (например, от помех по шинам питания) после замыкания нормально разомкнутых контактов переключателей.

Указанные недостатки формирователя ограничивают область его применения.

Известен многоканальный датчик одиночных импульсов (см. авт.св. СССР N 902232, кл. H 03 K 5/01, 5/06, 04.06.80 "Многоканальный датчик одиночных импульсов", автор М.Т. Юревич, опубл. в БИ N 4, 1982), который выбран в качестве прототипа и содержит блок ключей в виде кнопок с нормально разомкнутыми контактами, счетный триггер, два элемента И, инвертор, выходные шины и устройство задержки, состоящий из двух последовательно включенных элементов задержки. Вход устройства задержки соединен с выходом счетного триггера, первый выход - непосредственно, а второй через инвертор - с входами первого элемента И. Счетный вход счетного триггера подключен к выходу второго элемента И, между входами которого и выходом первого элемента И включены кнопки блока ключей. Входы второго элемента И соединены с выходными шинами.

Данное устройство выгодно отличается от предыдущего тем, что в нем задержка выходных импульсов относительно момента замыкания контактов кнопок и длительность выходных импульсов могут, в принципе, регулироваться (путем изменения параметров элементов задержки), и это заметно расширяет область его применения.

Недостатками данного многоканального датчика одиночных импульсов являются

сложность структуры выходных сигналов, заключающаяся в том, что при замыкании контактов какой-либо кнопка на соответствующем выходе датчика сначала устанавливается уровень логического нуля, затем на время длительности формируемого импульса на этом выходе устанавливается уровень логической единицы, потом до размыкания замкнутых контактов кнопки - уровень логического нуля, а после их размыкания - снова исходный уровень логической единицы; выделение формируемого датчиком импульса в нагрузке требует усложнения последней;

искажение указанного и без того достаточно сложного по структуре выходного сигнала датчика дребезгом контактов кнопок при их замыкании и размыкании, поскольку в эти моменты на контактах кнопок присутствуют разные уровни напряжения, а контакты кнопок имеют непосредственную связь с выходами датчика;

возможность искажения формируемого выходного импульса датчика при несанкционированных переключениях счетного триггера от помех (например, от помех по шинам питания) после начала формирования выходного импульса);

отсутствие возможности формирования неодинаковых задержек выходных импульсов для разных выходов датчика относительно момента замыкания контактов соответствующих кнопок и неодинаковых длительностей импульсов на выходах;

отсутствие синхронизации выходных импульсов устройства внешними тактовыми импульсами.

Указанные недостатки устройства ограничивают область его применения.

Задачей, решаемой предлагаемым техническим решением, является создание многоканального датчика одиночных импульсов, обладающего расширенной областью применения за счет упрощения структуры выходного сигнала, исключения влияния дребезга контактов ключей и помех на структуру и длительность формируемого сигнала, возможности формирования в каналах выходных импульсов неодинаковой длительности и неодинаковых задержек выходных импульсов относительно моментов включения соответствующих ключей, а также за счет синхронизации формируемых выходных импульсов внешними тактовыми импульсами.

Технический результат, заключающийся в расширении области применения, достигается тем, что в многоканальный датчик одиночных импульсов, содержащий блок ключей, инвертор, выходные шины и два элемента задержки, введены постоянное запоминающее устройство, двухканальный n-разрядный мультиплексор, 2n-2 элементов задержки и шина тактовых импульсов, при этом один адресный вход постоянного запоминающего устройства подключен к шине тактовых импульсов и входу инвертора, n следующих адресных входов - к соответствующим выходам мультиплексора, m следующих адресных входов - к соответствующим выходам блока ключей, n выходов через первые n элементов задержки - к соответствующим входам первого канала мультиплексора, а m следующих выходов соединены с соответствующими выходными шинами, выходы мультиплексора через вторые n элементов задержки соединены с соответствующими входами его второго канала, а первый и второй управляющие входы подключены соответственно к выходу и входу инвертора.

Указанная совокупность признаков позволяет расширить область применения многоканального датчика одиночных импульсов за счет упрощения структуры выходного сигнала, исключения влияния дребезга контактов ключей и помех на структуру и длительность выходного сигнала, возможности формирования в каналах выходных импульсов неодинаковой длительности и неодинаковых задержек выходных импульсов относительно моментов включения соответствующих ключей, а также за счет синхронизации выходных импульсов внешними тактовыми импульсами.

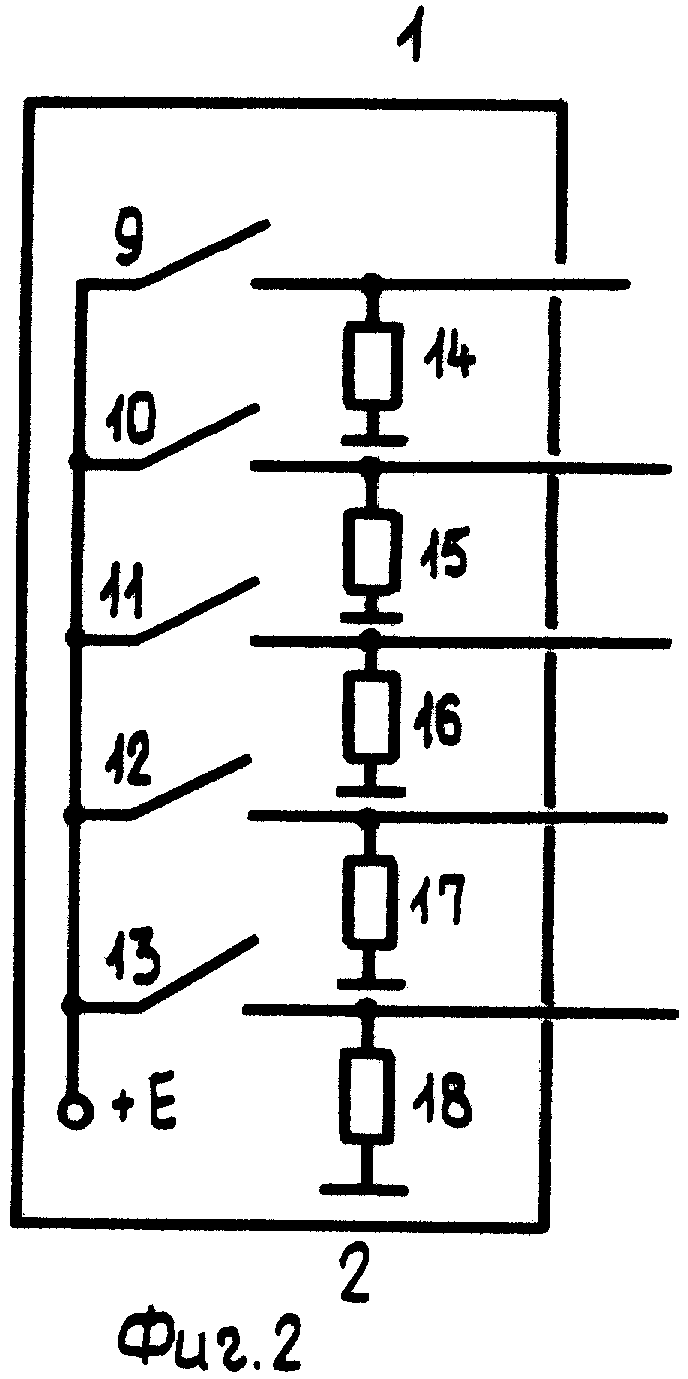

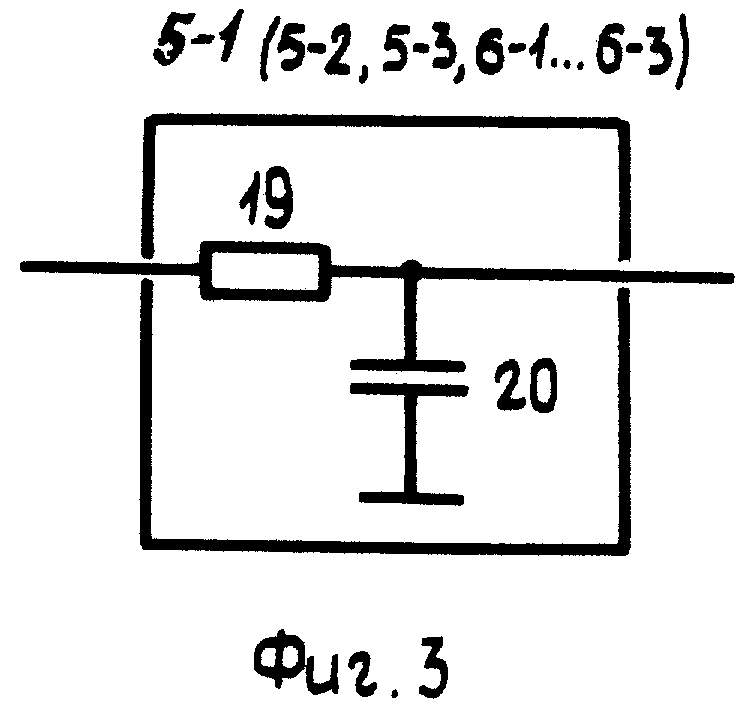

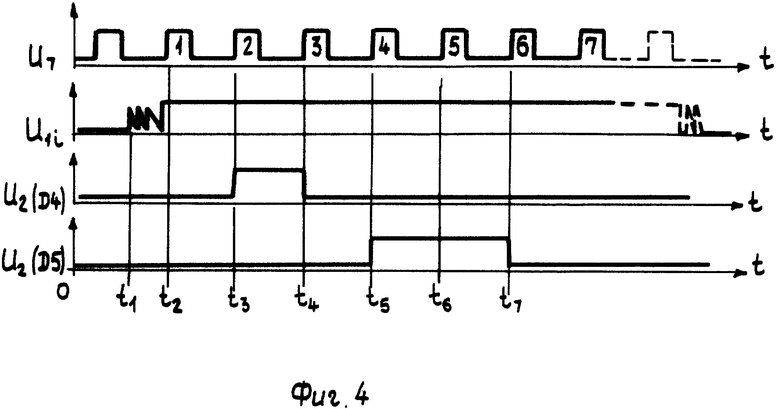

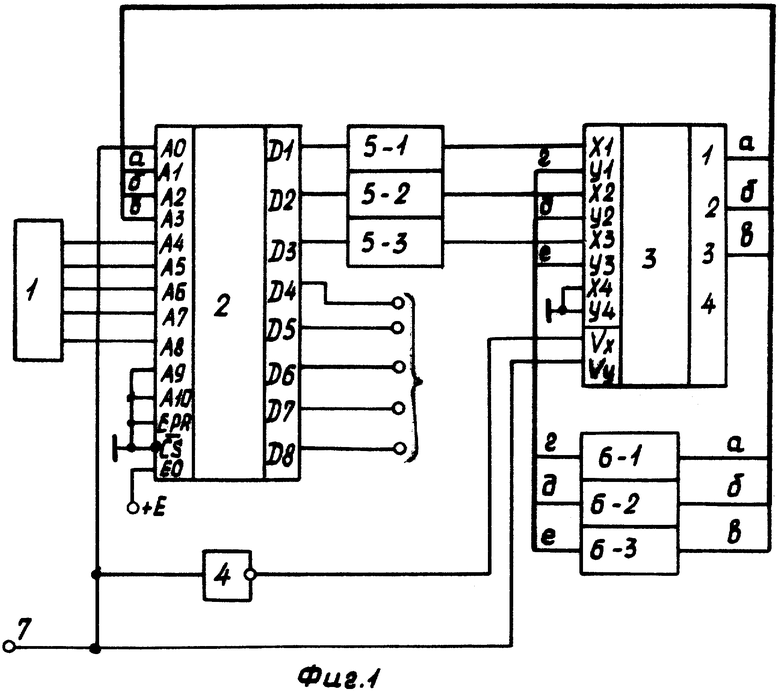

На фиг. 1 приведена схема многоканального датчика одиночных импульсов при n = 3 и m = 5; на фиг. 2 - схема варианта реализации блока ключей; на фиг. 3 - схема элементов задержки; на фиг. 4 - временные диаграммы сигналов на шине тактовых импульсов, на адресных входах и выходах постоянного запоминающего устройства в процессе работы.

Многоканальный датчик одиночных импульсов содержит блок 1 ключей, постоянное запоминающее устройство 2 (ПЗУ2), двухканальный трехразрядный (n = 3) мультиплексор 3, инвертор 4, первые три 5-1...5-3 (n = 3) элемента задержки и вторые три 6-1...6-3 элемента задержки. Один адресный вход (АО) ПЗУ2 подключен к шине 7 тактовых импульсов, три адресных входа А1, А2, А3 подключены к соответствующим выходам мультиплексора 3, пять (А4...А8) адресных входов - к соответствующим выходам блока 1 ключей, неиспользуемые адресные входы (А9, А10) - к общей шине, три выхода (D1...D3) через элементы задержки 5-1. . . 5-3 соединены с соответствующими входами (Х1...Х3) первого канала мультиплексора 3, а пять выходов (D4...D8) - с соответствующими выходными шинами 8. Выходы мультиплексора 3 через элементы задержки 6-1...6-3 соединены с соответствующими входами (Y1...Y3) его второго канала, первый управляющий вход (Vx) подключен к выходу инвертора 4, второй управляющий вход (Vy) - к шине 7 тактовых импульсов, соединенной с входом инвертора 4.

Блок 1 ключей выполнен по схеме фиг. 2 на ключах в виде кнопок 9...13 с резисторами привязки 14...18. Может быть выполнен на базе отдельных электронных датчиков потенциальных или относительно длинных импульсных сигналов, не содержащих механических контактов. Тогда устройство будет выполнять функцию формирования коротких одиночных импульсов по фронту входных сигналов (с требуемыми задержкой и длительностью для каждого датчика).

Каждый из элементов задержки 5-1...5-3, 6-1...6-3 выполнен по одинаковой схеме, приведенной на фиг. 3, содержащей резистор 19 и конденсатор 20 и представляющей собой интегрирующую RC-цепь. В отдельных случаях, например, при реализации устройства на базе КМОП-микросхем, указанные RC-цепи могут содержать на выходах дополнительные токоограничивающие резисторы. Количество RC-цепей (элементов задержки) устройства зависит от длительности (тактов) задержки одиночных импульсов и длительности этих импульсов, а постоянная RC-цепей выбирается исходя из требуемого уровня помехоустойчивости устройства. Например, ее можно выбрать такой, чтобы конденсаторы 20 элементов задержки 5-1. . .5-3 успели зарядиться или разрядиться до соответствующих логических уровней за время длительности тактовых импульсов и не успели зарядиться или разрядиться до соответствующих логических уровней от помех, а конденсаторы 20 элементов задержки 6-1...6-3 - успели зарядиться или разрядиться до соответствующих логических уровней в принятом интервале между тактовыми импульсами и не успели зарядиться или разрядиться до соответствующих логических уровней при более коротких интервалах между импульсами на шине тактовых импульсов (например, при дроблении тактового импульса помехой или при поступлении по шине тактовых импульсов помех). При выборе одинаковой постоянной для всех RC-цепей всех элементов задержки скважность тактовых импульсов принимается равной двум.

Построение устройства с количеством каналов больше, чем показано на фиг. 1, осуществляется путем увеличения количества ключей в блоке 1 ключей и соответствующего увеличения количества выходов блока 1 ключей, количества адресных входов ПЗУ2 и выходов ПЗУ2, соединенных с выходными шинами 8 при соответствующем программировании ПЗУ2. Программой ПЗУ2 также обеспечиваются длительности задержек выходных импульсов в каждом канале устройства относительно моментов замыкания соответствующих ключей блока 1 ключей и длительности этих импульсов в каждом из каналов. При этом длительность задержки выходного импульса в конкретном канале устройства должна быть не менее максимального времени дребезга контактов соответствующего ключа блока 1 ключей.

Многоканальный датчик одиночных импульсов работает следующим образом.

В исходном состоянии ключи 9...13 блока 1 ключей (фиг. 2) разомкнуты, поэтому на всех выходах последнего и на соответствующих адресных входах (А4. . . А8) ПЗУ2 (см. фиг. 1) уровни логического нуля. На шине 7 тактовых импульсов поддерживается уровень логического нуля, который присутствует также на адресном входе младшего разряда (АО) ПЗУ2, на входе инвертора 4 и на втором управляющем входе (Vy) мультиплексора 3, на первом управляющем входе (Vx) которого поддерживается уровень логической единицы с выхода инвертора. При таком сочетании уровней сигналов на управляющих входах мультиплексора 3 на его выходы выдаются уровни сигналов, присутствующие на входах его первого канала (X1, X2, X3). Так как в исходном состоянии конденсаторы 20 элементов задержки 5-1...5-3 (как и элементов задержки 6-1...6-3) разряжены (например, в обесточенном состоянии устройства), то на выходы мультиплексора 3 выдаются уровни логического нуля, которые поступают на соответствующие адресные входы (А1...А3) ПЗУ2. Следовательно, ко всем адресным входам ПЗУ2 оказываются приложенными уровни логического нуля (неиспользуемые адресные входы старших разрядов А9, А10 ПЗУ2 подключены к общей шине устройства), то есть у ПЗУ2 оказывается выбранным нулевой адрес. При этом на все выходы ПЗУ2 выдаются, в соответствии с записанной программой, уровни логического нуля, поэтому на выходных шинах 8 поддерживаются уровни логического нуля, а уровни логического нуля с соответствующих выходов ПЗУ2 (D1...D3) поддерживают разряженное состояние конденсаторов 20 элементов задержки 5-1...5-3. В результате разряженное состояние конденсаторов 20 указанных элементов задержки поддерживается по замкнутым цепям: выходы элементов задержки 5-1...5-3 - входы первого канала и выходы мультиплексора 3 - адресные входы (А1...А3) и выходы (D1... D3) ПЗУ2 - входы элементов задержки 5-1...5-3. Указанное исходное состояние устройства сохраняется до подачи последовательности тактовых импульсов по шине 7 или включения какого-либо из ключей блока 1 ключей.

При подаче по шине 7 тактовых импульсов с уровнем логической единицы (до включения указанных ключей) в течение каждого тактового импульса на адресном входе АО младшего разряда ПЗУ2, на входе инвертора 4 и на втором управляющем входе мультиплексора 3 присутствует уровень логической единицы, на первом управляющем входе мультиплексора 3 - уровень логического нуля. При таком сочетании сигналов на управляющих входах мультиплексора 3 на его выходы выдаются уровни сигналов, присутствующие на входах его второго канала, поэтому на адресные входы А1...А3 ПЗУ2 подаются уровни логического нуля с разряженных в исходном состоянии устройства конденсаторов 20 элементов задержки 6-1. . . 6-3. В результате в течение каждого тактового импульса, поступающего по шине 7 до включения ключей блока 1 ключей, к адресным входам ПЗУ2 оказывается приложенным двоичный код числа 1, то есть выбирается адрес 1. В этом адресе на выходы D1...D3 ПЗУ2 выдаются, в соответствии с записанной программой, уровни логического нуля, которые поддерживают разряженное состояние конденсаторов 20 элементов задержки 5-1...5-3. Поэтому после окончания каждого тактового импульса устройство возвращается в описанное выше исходное состояние. Аналогично реагирует устройство и на импульсные помехи, поступающие по шине 7 тактовых импульсов.

Рассмотрим работу устройства при формировании одиночного импульса по одному каналу на примере, когда включается ключ 9 блока 1 ключей и при этом формируется одиночный импульс с длительностью (tu), равной одному периоду следования тактовых импульсов (Tт), и с задержкой (tз) относительно момента включения ключа 9, равной одному периоду следования тактовых импульсов (фактическое значение tз может находиться, из-за ассинхронности моментов включения ключей блока 1 ключей и тактовых импульсов с длительностью tт, в пределах от 1Т до 2Тт - tт). Комбинации уровней сигналов на адресных входах и выходах ПЗУ2 для этого случая приведены в табл. 1.

При включении ключа 9 на адресный вход А4 пятого разряда ПЗУ2 сначала поступает "пачка" коротких импульсов (амплитуда которых может достигать уровня логической единицы), обусловленных дребезгом контактов ключа (см. фиг. 4, U1i), момент t1). При этом в течение каждого импульса дребезга оказывается выбранным один и тот же адрес 16 - начальный адрес зоны ячеек памяти ПЗУ2, где записана программа для формирования единичного импульса по факту включения ключа 9 (в данном случае это - зона адресов с 16-го по 31-й). В этом адресе на выходы ПЗУ2 выдаются, в соответствии с записанной программой, уровни логического нуля, поэтому в течение импульсов дребезга поддерживаются исходные разряженные состояния конденсаторов 20 элементов задержки 5-1... 5-3, а после каждого из импульсов дребезга ПЗУ2 оказывается установленным в нулевой адрес. Аналогичная ситуация получается и при поступлении на адресный вход А4 ПЗУ2 помех, наводимых на соответствующей линии связи ПЗУ2 с ключом 9, в особенности в случае дистанционного размещения блока 2 ключей.

Если во время дребезга контактов включаемого ключа 9 по ступает тактовый импульс, то при совпадении уровней логической единицы на адресных входах А0 и А4 ПЗУ2 каждый раз оказывается выбранным адрес 17 ПЗУ2 (табл. 1, строка третья), где на выход D1 ПЗУ2 выдается, в соответствии с записанной программой, уровень логической единицы. Однако за короткое время импульса дребезга конденсатор 20 элемента задержки 5-1 не успевает зарядиться до уровня логической единицы, а между импульсами дребезга при наличии тактового импульса оказывается выбранным адрес 1 ПЗУ2, где на выходы ПЗУ2 выдаются, в соответствии с записанной программой, уровни логического нуля, и заряженный в течение предыдущего импульса дребезга до определенного уровня конденсатор 20 элемента задержки 5-1 разряжается.

При поступлении очередного (первого после установления постоянного уровня логической единицы на адресном входе А4 ПЗУ2 при включении ключа 9) тактового импульса по шине 7 (см. фиг. 4, U7, момент t2) уровень логической единицы устанавливается (на время длительности этого импульса) также на адресном входе А0 младшего разряда ПЗУ2. В результате к адресным входам ПЗУ2 оказывается приложенным двоичный код числа 17 (табл. 1, третья строка), то есть выбирается адрес 17 ПЗУ2. В этом адресе на выход D1 ПЗУ2 выдается, в соответствии с записанной программой, уровень логической единицы, который поступает на вход элемента задержки 5-1. При этом начинается процесс заряда конденсатора 20 этого элемента задержки через соответствующий резистор 19 (заряд указанного конденсатора до уровня логической единицы должен завершиться до окончания первого тактового импульса). Одновременно в течение тактового импульса на втором управляющем входе мультиплексора 3 будет присутствовать уровень логической единицы, а на первом управляющем входе - уровень логического нуля с выхода инвертора 4. При таком сочетании сигналов на управляющих входах на выходы мультиплексора 3 выдаются уровни сигналов, присутствующие на входах его второго канала, то есть, в данном случае, уровни логического нуля с разряженных конденсаторов 20 элементов задержки 6-1... 6-3. Эти уровни логического нуля поступают на адресные входы А1....А3 ПЗУ2 и обеспечивают сохранение на адресных входах ПЗУ2 выбранного адреса 17 до окончания первого тактового импульса.

Аналогично работает устройство и при поступлении первого тактового импульса одновременно с поступлением уровня логической единицы на адресный вход А4 ПЗУ2 от ключа 9 блока 1 ключей, а также при поступлении сигнала на вход А4 ПЗУ2 с задержкой относительно фронта первого тактового импульса. Некоторое отличие будет состоять только в том, что в первом случае на адресные входы ПЗУ сразу поступает код адреса 17, а во втором случае сначала устанавливается код адреса 1, затем (после поступления сигнала от ключа 9) - код адреса 17. При этом если во втором случае времени нахождения ПЗУ2 в адресе 17 не хватит для заряда конденсатора 20 элемента задержки 5-1, то на адресных входах ПЗУ2 после окончания первого тактового импульса установится код нулевого адреса, то есть привязка к тактовому импульсу в данном случае не произойдет.

После окончания первого тактового импульса на шине 7 и на адресном входе А0 ПЗУ2 восстанавливается исходный уровень логического нуля, на первом и втором управляющих входах мультиплексора 3 восстанавливаются исходные уровни логической единицы и логического нуля соответственно. Это приводит к тому, что на выходы мультиплексора 3 выдаются уровни сигналов, присутствующие на входах его первого канала. В рассматриваемом случае на выходы 2 и 3 мультиплексора 3 выдаются уровни логического нуля с разряженных конденсаторов 20 элементов задержки 5-2 и 5-3, а на выход 1 - уровень логической единицы с заряженного в течение первого тактового импульса конденсатора 20 элемента задержки 5-1. В результате после окончания первого тактового импульса, привязка к которому состоялась, на адресных входах ПЗУ2 устанавливается двоичный код числа 18 (см. табл. 1, четвертая строка сверху), то есть адрес 18. В данном случае на выход D1 ПЗУ2 выдается так же, как и в адрес 17, уровень логической единицы, а на выходах D2, D3 ПЗУ2 сохраняются уровни логического нуля. Указанные уровни сигналов на выходах ПЗУ2 поддерживают заряженное состояние конденсатора 20 элемента задержки 5-1 и разряженное состояние конденсаторов 20 элементов задержки 5-2, 5-3. Таким образом, после первого тактового импульса (в интервале между первым и вторым тактовыми импульсами) заряженное состояние конденсатора 20 элемента задержки 5-1 разряженное состояние конденсаторов 20 элементов задержки 5-2, 5-3 поддерживаются по замкнутым цепям: выходы элементов задержки 5-1...5-3 - входы первого канала и выходы мультиплексора 3 - адресные входы А1...А3 и выходы D1...D3 ПЗУ2 - входы элементов задержки 5-1...5-3.

Одновременно идет процесс заряда конденсатора 20 элемента задержки 6-1, который должен завершиться до поступления следующего (второго) тактового импульса. При этом уровни логического нуля с выходов 2, 3 мультиплексора 3 поддерживают разряженное состояние конденсаторов 20 элементов задержки 6-2, 6-3.

До первого тактового импульса, в течение этого тактового импульса и после него на выходах D4...D8 ПЗУ2, следовательно, и на выходных шинах 8 сохраняются, в соответствии с записанной программой, исходные уровни логического нуля.

Если бы первый тактовый импульс был коротким (например, длительность его уменьшилась из-за помехи или перед тактовым импульсом по шине 7 поступила помеха), то в течение такого короткого тактового импульса конденсатор 20 элемента задержки 5-1 не успел бы зарядиться до уровня логической единицы и после окончания такого импульса (или помехи) на адресных входах ПЗУ2 оказался бы установленным двоичный код числа 16 (см. табл. 1, вторая строка), то есть устройство после короткого тактового импульса (или помехи) возвращается в состояние, в котором находилось до этого.

При поступлении второго тактового импульса по шине 7 (фиг. 4, U7, момент t3) к адресному входу А0 младшего разряда ПЗУ2 вновь оказывается приложенным (на время длительности этого импульса) уровень логической единицы. Одновременно на первом и втором управляющих входах мультиплексора 3 устанавливаются уровни логического нуля и логической единицы соответственно. В результате в течение второго тактового импульса на выходы мультиплексора 3 выдаются логические уровни, присутствующие на входах его второго канала, то есть логические уровни с конденсаторов 20 элементов задержки 6-1...6-3. В рассматриваемом случае на выход 1 мультиплексора выдается уровень логической единицы, а на выходы 2, 3 - уровни логического нуля. В результате в течение второго тактового импульса на адресных входах ПЗУ2 оказываются установленным двоичный код числа 19 (табл. 1, пятая строка), то есть выбирается адрес 19 ПЗУ2. В этом адресе на выход D2 ПЗУ выдается, в соответствии с записанной программой, уровень логической единицы, на выходы D1 и D3 - уровни логического нуля (табл. 1, пятая строка). При этом начинается заряд конденсатора 20 элемента задержки 5-2, разряд конденсатора 20 элемента задержки 5-1 и сохраняется (поддерживается) разряженное состояние конденсатора 20 элемента задержки 6-3. Процессы перезаряда указанных конденсаторов до соответствующих логических уровней завершаются до окончания второго тактового импульса.

Одновременно после поступления второго тактового импульса, то есть когда выбирается адрес 19 ПЗУ2, на выходе D4 последнего появляется, в соответствии с записанной программой, уровень логической единицы - фронт одиночного импульса, формируемого при включении ключа 9 блока 1 ключей (фиг. 4, U2 (D4), момент t3).

После окончания второго тактового импульса на шине 7 и на адресном входе А0 ПЗУ2 восстанавливается исходный уровень логического нуля, на первом и втором управляющем входах мультиплексора 3 восстанавливаются исходные уровни логической единицы и логического нуля соответственно. Это приводит к тому, что на выходы мультиплексора 3 выдаются, как и после первого тактового импульса, уровни сигналов, присутствующие на входах его первого канала. В данном случае на выход 2 мультиплексора 3 выдается уровень логической единицы с заряженного в течение второго тактового импульса конденсатора 20 элемента задержки 5-2, а на выходы 1 и 3 - уровни логического нуля с разряженных конденсаторов 20 элементов задержки 5-1 и 5-3. В результате после окончания второго тактового импульса на адресных входах ПЗУ2 устанавливается двоичный код числа 20 (см. табл. 1, шестая строка), то есть адрес 20. В данном адресе на выход D2 ПЗУ2 выдается, как и в адресе 19, уровень логической единицы, а на выходе D1 и D3 - уровни логического нуля. Указанные уровни сигналов на выходах ПЗУ2 поддерживают заряженное состояние конденсатора 20 элемента задержки 5-2 и разряженное состояние конденсаторов 20 элементов задержки 5-1 и 5-3, и эти состояния конденсаторов 20 элементов задержки 5-1...5-3 поддерживаются, как и после первого тактового импульса, по замкнутым цепям, выходы элементов задержки 5-1...5-3 - входы первого канала и выходы мультиплексора 3 - адресные входы А1...А3 и выходы D1...D3 ПЗУ2 - входы элементов задержки 5-1. . . 5-3. Одновременно идет процесс перезаряда конденсатора 20 элементов задержки 6-1, 6-2 и сохраняется (поддерживается) разряженное состояние конденсатора 20 элемента задержки 6-3. Уровень логической единицы на выходе D4 ПЗУ2 после снятия второго тактового импульса сохраняется.

При поступлении третьего тактового импульса по шине 7 к адресному входу А0 младшего разряда ПЗУ2 снова оказывается приложенным (на время длительности тактового импульса) уровень логической единицы. Одновременно с выходов мультиплексора 3 на соответствующие адресные входы ПЗУ2 поступают логические уровни, соответствующие состояниям конденсаторов 20 элементов задержки 6-1.. . 6-3. В результате в течение третьего тактового импульса на адресных входах ПЗУ2 оказывается установленным двоичный код числа 21 (табл. 1, седьмая строка), то есть выбирается адрес 21 ПЗУ2. В этом адресе на выходы D1, D2 ПЗУ2 выдаются, в соответствии с записанной программой, уровни логической единицы, на выходе D3 сохраняется уровень логического нуля. При этом начинается заряд конденсатора 20 элемента задержки 5-1, сохраняются заряженное состояние конденсатора 20 элемента задержки 5-2 и разряженное состояние конденсатора 20 элемента задержки 5-3, процесс заряда конденсатора 20 элемента задержки 5-1 завершается до окончания третьего тактового импульса.

В момент установления адреса 21 на адресных входах ПЗУ2 (при поступлении третьего тактового импульса) на выходе D4 ПЗУ2 восстанавливается исходный уровень логического нуля (фиг. 4, U2 (D4), момент t4), то есть формируется срез одиночного импульса устройства, формируемого при включении ключа 9 блока 1 ключей 1.

После окончания третьего тактового импульса на шине и на адресном входе А0 ПЗУ2 восстанавливается исходный уровень логического нуля, на первом и втором управляющих входах мультиплексора 3 - уровень логической единицы и логического нуля соответственно. При этом на выходы мультиплексора выдаются, как было изложено выше, уровни сигналов с конденсаторов 20 элементов задержки 5-1. ..5-3. В результате после окончания третьего тактового импульса на адресных входах ПЗУ2 устанавливается адрес 22 (табл. 1, восьмая строка). В указанном адресе как выходы D1, D2 ПЗУ2 выдаются, как и в адресе 21, уровни логической единицы, на выход D3 - уровень логического нуля, которые поддерживают заряженное состояние конденсаторов 20 элементов задержки 5-1, 5-2 и разряженное состояние конденсатора 20 элемента задержки 5-3, и указанные состояния конденсаторов 20 элементов задержки 5-1...5-3 поддерживаются до поступления четвертого тактового импульса по замкнутым цепям: выходы элементов задержки 5-1...5-3 - входы первого канала и выходы мультиплексора 3 - адресные входы А1...А3 и выходы D1...D3 ПЗУ2 - входы элементов задержки 5-1...5-3. Одновременно идет процесс заряда конденсатора 20 элемента задержки 6-1 при сохранении заряженного и разряженного состояния конденсаторов 20 элементов задержки 6-2 и 6-3 соответственно.

При поступлении четвертого тактового импульса функциональные элементы устройства работают аналогично (как и при поступлении предыдущих тактовых импульсов). При этом в течение четвертого тактового импульса на адресных входах ПЗУ2 устанавливается адрес 23, а после окончания этого тактового импульса - снова адрес 22 (табл. 1, десятая строка), то есть адрес предшествовавший четвертому тактовому импульсу. При поступлении последующих тактовых импульсов устройство работает аналогично, при этом в течение каждого тактового импульса на адресных входах ПЗУ2 устанавливается адрес 23, после окончания тактового импульса - адрес 22, то есть устройство как бы блокируется. Из указанного состояния устройство выходит после выключения включенного ключа 9 блока 1 ключей, то есть после снятия уровня логической единицы с адресного входа А4 ПЗУ2. Если ключ 9 выключается между тактовыми импульсами, то на адресных входах ПЗУ2 сразу устанавливается адрес 6 (см. табл. 1, строка девятая), а если ключ 9 выключается при наличии тактового импульса на шине 7 - адрес 7 (см. табл. 1, строка десятая). В адрес 6 на выходы D1, D2 ПЗУ2 выдаются, в соответствии с программой, уровни логической единицы, которые поддерживают заряженное состояние конденсатора 20 элементов задержки 5-1, 5-2, а на выход D3 выдается уровень логического нуля, который поддерживает разряженное состояние конденсатора 20 элемента задержки 5-3.

В адрес 7 на выходы D1...D3 ПЗУ2 выводятся, в соответствии с записанной программой, уровня логического нуля, поэтому в течение указанного тактового импульса разряжаются конденсаторы 20 элементов задержки 5-1, 5-2 и поддерживается разряженное состояние конденсатора 20 элемента задержки 5-3. Ввиду того, что при выключении ключа 9 уровень логического нуля на адресном входе А4 ПЗУ2 из-за дребезга контактов ключа 9 устанавливается не сразу, то при отсутствии тактового импульса на адресных входах ПЗУ2 попеременно будут устанавливаться адреса 6 и 22 (при наличии импульса дребезга), а при наличии тактового импульса - адреса 7 и 23 (при наличии импульса дребезга).

После окончания указанного тактового импульса и дребезга контактов ключа 9 на адресных входах ПЗУ2 устанавливается нулевой адрес. В этом адресе на выходы D1. . .D3 ПЗУ2 выдаются уровни логического нуля (см. табл. 1, первая строка), которые поддерживают разряженное состояние конденсаторов 20 элементов задержки 5-1...5-3. Одновременно разряжаются конденсаторы 20 элементов задержки 6-1 и 6-2, после чего устройству возвращается описанное выше исходное состояние.

При включении какого-либо другого ключа блока 1 ключей устройство работает аналогично. При этом каждым из этих ключей выбирается начальный адрес соответствующей зоны адресов ПЗУ2, например для ключа 10 это адрес 32 (зона адресов 32...47), для ключа 11-64 (зона адресов 64...79) и т.д. Для примера в табл. 2 приведены логические уровни сигналов на адресных входах и выходах ПЗУ2 для формирования на выходе второго канала устройства импульса с tu = 2Т и tз = 3Т при включении ключа 10 блока 1 ключей (см. фиг. 4, U2 (D5)).

При необходимости путем соответствующего программирования ПЗУ2 параметры (tu, tз) формируемых в каналах устройства одиночных импульсов могут быть изменены произвольным образом. При этом для варианта реализации устройства (с n = 3), приведенного на фиг. 1, общее количество тактов в каждом канале для формирования длительности импульса и его задержки относительно момента включения соответствующего ключа не должно превышать восьми, для варианта реализации с n = 4 не должно превышать шестнадцати, для варианта реализации с n = 5 не должно превышать тридцати двух и т.д.

Таким образом, предлагаемый многоканальный датчик одиночных импульсов при включении того или иного ключа блока 1 ключей формирует (после окончания дребезга контактов ключа) и выдает на выход соответствующего канала простой по структуре выходной сигнал - синхронизированный тактовыми импульсами одиночный импульс с временными параметрами (tu, tз), определяемыми программой, записанной в ПЗУ2. Устройство осуществляет допусковый контроль (по минимуму) длительности присутствия и длительности отсутствия сигналов, поступающих от блока 1 ключей и по шине 7 тактовых импульсов, и запускается на формирование требуемых длительности задержки выходного сигнала относительно момента включения соответствующего ключа n длительности самого импульса, если указанные параметры управляющих сигналов больше минимальных допустимых значений, которые определяются постоянной RC-цепей элементов задержки 5-1... 5-3 и 6-1...6-3, и легко могут регулироваться путем изменения сопротивлений резисторов или (и) емкостей конденсаторов указанных элементов задержки. Длительности задержек выходных одиночных импульсов в каналах устройства относительно моментов замыкания соответствующих ключей блока 1 ключей и длительности самих импульсов могут быть одинаковыми или различными, что задается программой, записанной в ПЗУ2. При необходимости может быть повышена устойчивость устройства при запуске к многократным помехам ("качкам" помех), поступающим на адресные входы ПЗУ2 от блока 1 ключей или по шине 7 тактовых импульсов, путем использования первых нескольких тактов работы устройства (при соответствующем программировании ПЗУ) после запуска для задержки формирования выходного одиночного сигнала.

Преимуществами заявляемого многоканального датчика одиночных импульсов перед прототипом являются простая структура выходного сигнала, наличие защиты искажения структуры и длительности выходного импульса от дребезга контактов ключей и от помех (как внешних, так и от внутренних), возможность формирования неодинаковых длительностей выходных импульсов в каналах и неодинаковых задержек этих импульсов относительно моментов включения соответствующих ключей блока 1 ключей, а также наличие синхронизации выходных импульсов тактовыми импульсами. Кроме того, заявляемое устройство, в отличие от прототипа, может быть использовано также для формирования одиночных импульсов по фронту потенциальных сигналов.

Указанные преимущества заявляемого многоканального датчика одиночных импульсов перед прототипом расширяют область его применения.

В целях подтверждения осуществимости заявляемого объекта и достигнутого технического результата в институте построен и испытан в диапазоне температур от - 50 до 50oC лабораторный макет, выполненный по схеме фиг. 1 на базе интегральных микросхем серии 564, резисторов С2-33Н, кнопок ПКн-105 и конденсаторов К10-17. При этом ПЗУ2 был реализован на ППЗУ М1623 РТ1А, мультиплексор 3 - на микросхеме 564ЛС2. Проведенные испытания показали осуществимость заявляемого многоканального датчика одиночных импульсов и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| СДВИГАЮЩИЙ РЕГИСТР | 1995 |

|

RU2105357C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2184825C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| ПОМЕХОСТОЙКОЕ ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106056C1 |

| МНОГОКАНАЛЬНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1999 |

|

RU2152685C1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 2001 |

|

RU2210181C2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для формирования импульсов, свободных от влияния дребезга контактов в устройствах с механическими контактами и для формирования коротких одиночных импульсов по фронту длинных импульсных или потенциальных сигналов. Достигаемый технический результат - расширение области применения. Технический результат достигается тем, что в многоканальный датчик одиночных импульсов, содержащий блок ключей, инвертор, выходные шины и два элемента задержки, введены постоянное запоминающее устройство, двухканальный n-разрядный мультиплексор, 2n - 2 элементов задержки, шина тактовых импульсов и новые связи между функциональными элементами. 4 ил., 2 табл.

Многоканальный датчик одиночных импульсов, содержащий блок ключей, инвертор, выходные шины и два элемента задержки, отличающийся тем, что в него введены постоянное запоминающее устройство, двухканальный n-разрядный мультиплексор, 2n-2 элементов задержки и шина тактовых импульсов, при этом один адресный вход постоянного запоминающего устройства подключен к шине тактовых импульсов и входу инвертора, n следующих адресных входов - к соответствующим выходам двухканального n-разрядного мультиплексора, m следующих адресных входов - к соответствующим выходам блока ключей, n выходов через первые n элементов задержки - к соответствующим входам первого канала двухканального n-разрядного мультиплексора, а m следующих выходов соединены с соответствующими выходными шинами, выходы двухканального n-разрядного мультиплексора через вторые n элементов задержки соединены с соответствующими входами его второго канала, а первый и второй управляющие входы двухканального n-разрядного мультиплексора подключены соответственно к выходу и входу инвертора.

| SU, авторское свидетельство, 928625, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| SU, авторское свидетельство, 902232, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-08-20—Публикация

1996-03-11—Подача