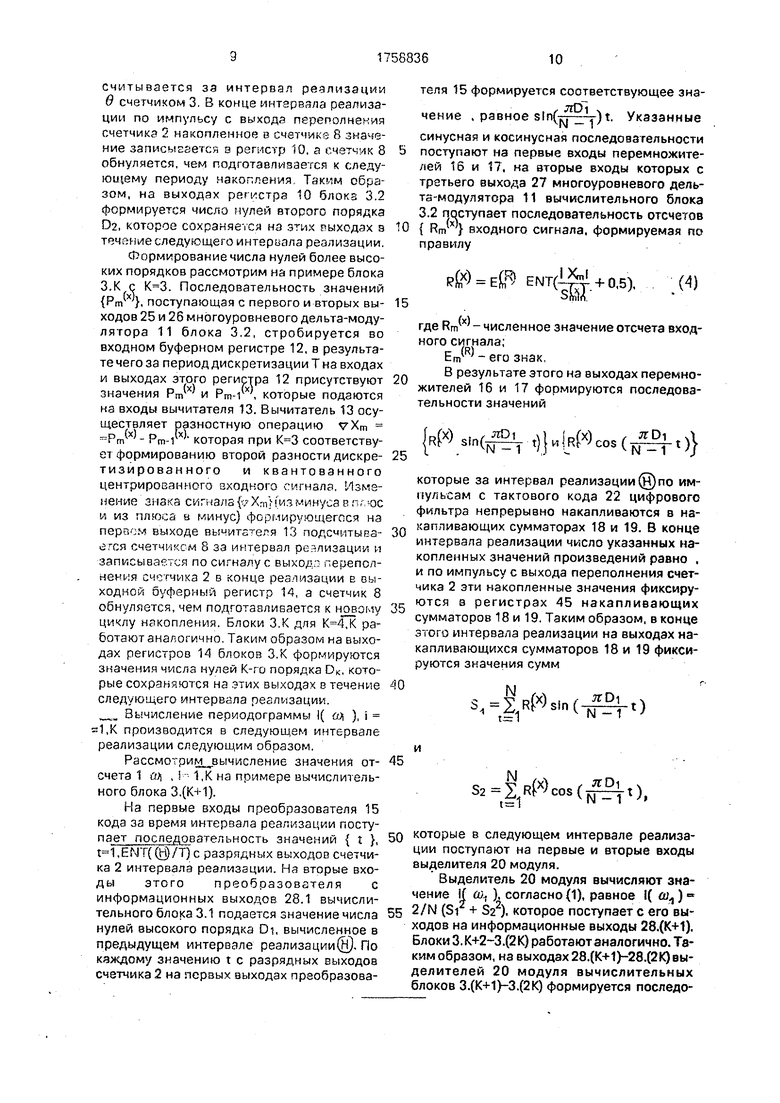

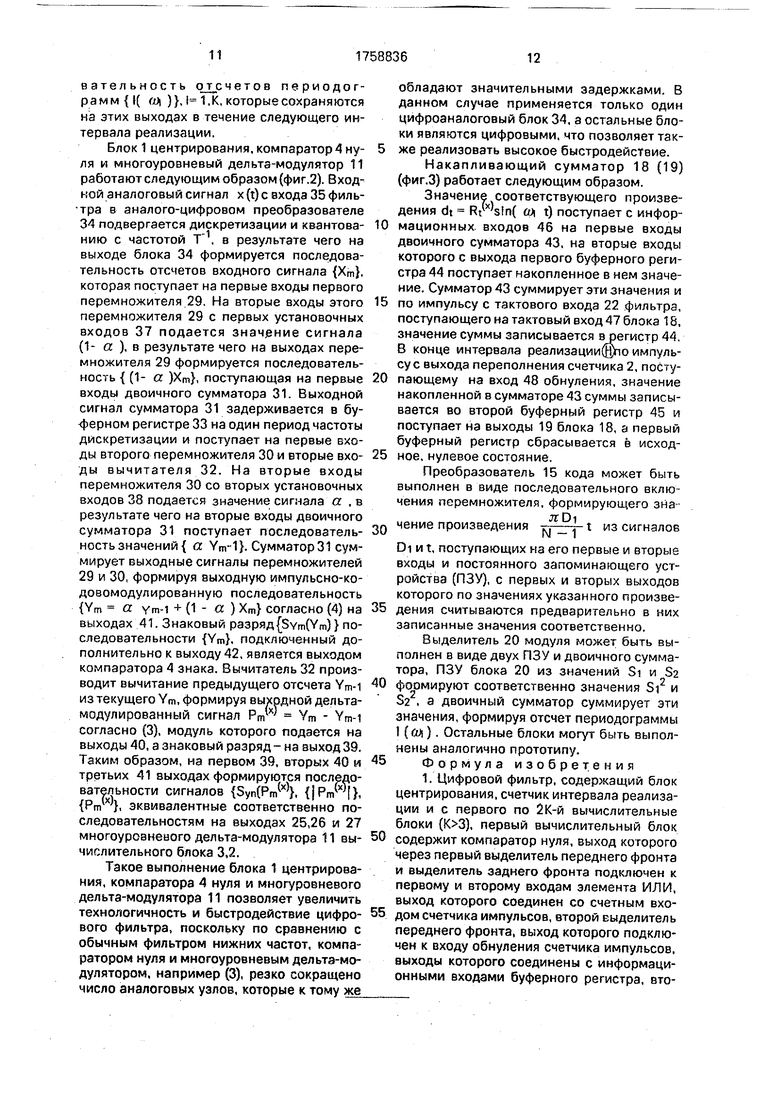

ный блок 3.2 содержит многоуровневый дельта-модулятор 11, первый выделитель 5 переднего фронта, выделитель б заднего фронта, элемент 7 ИЛИ, счетчик 8 импульсов, второй выделитель 9 переднего фронта, буферньлй регистр 10. Вычислительный блок 3.I, I 3,к содержит входной буферный регистр 12, вычислитель 13, первый выделитель 5 переднего фронта, выделитель 6 заднего фронта, элемент 7 ИЛИ, счетчик 8 импульсов, второй выделитель 9 переднего фронта выходной буферный регистр 14. Вычислительный блок 3.J, j k+1,2K содержит преобразователь 15 кода, первый м второй перемножители 16 и 17, первый и второй накапливающие сумматоры 18 и 19, выделитель 20 модуля.

На фиг,1 обозначены информационный вход 21 фильтра, тактовый вход 22, первый и второй установочные входы 23 и 24, первый 25, вторые 26 и третьи 27 выходы многоуровневого дельта-модулятора 11, первые - (2К)-е информационные выходы 28.1-28,(2К) фильтра.

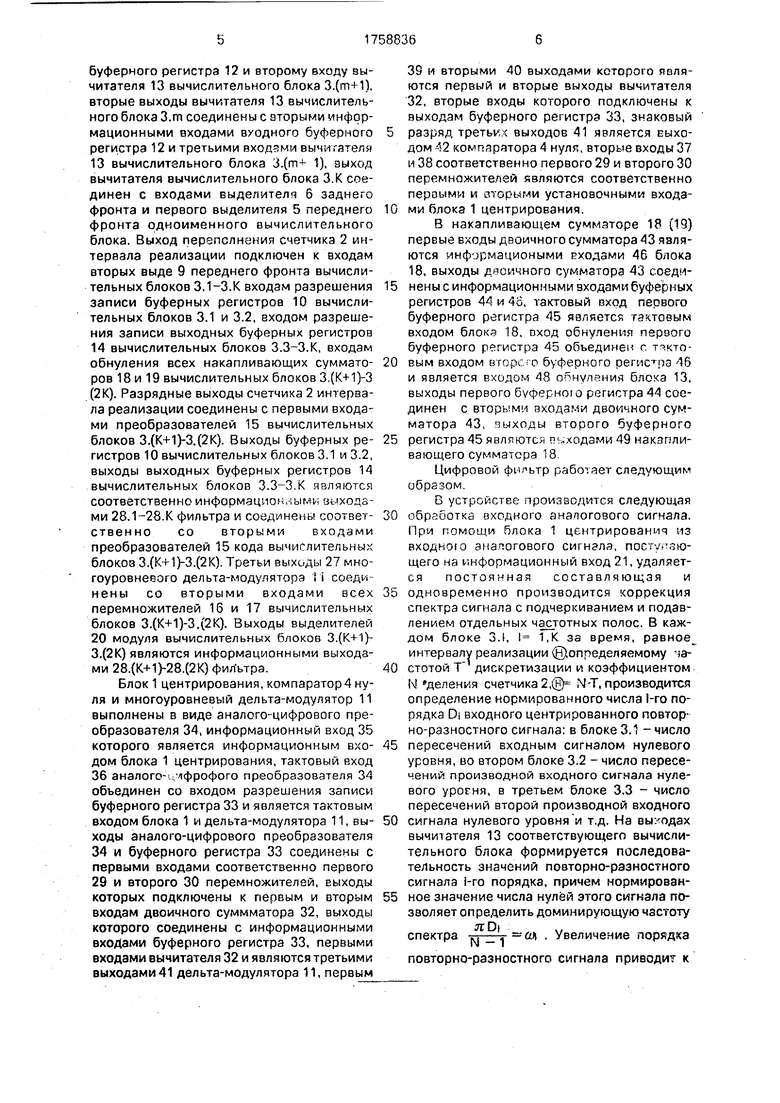

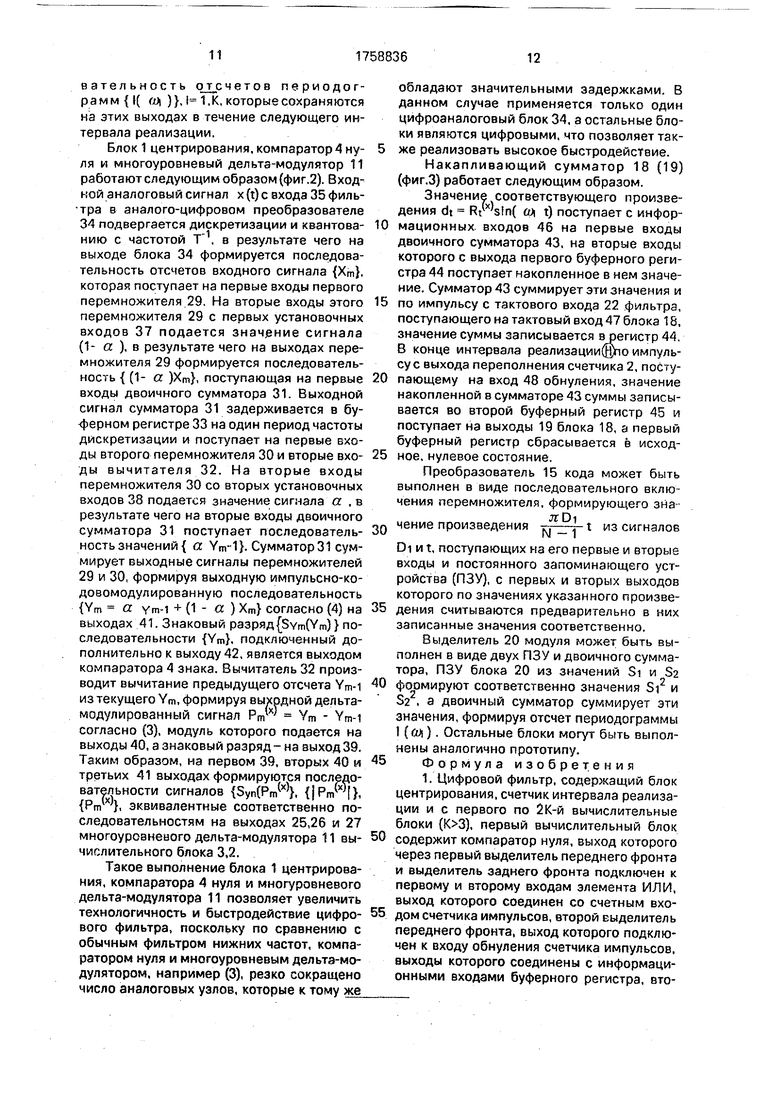

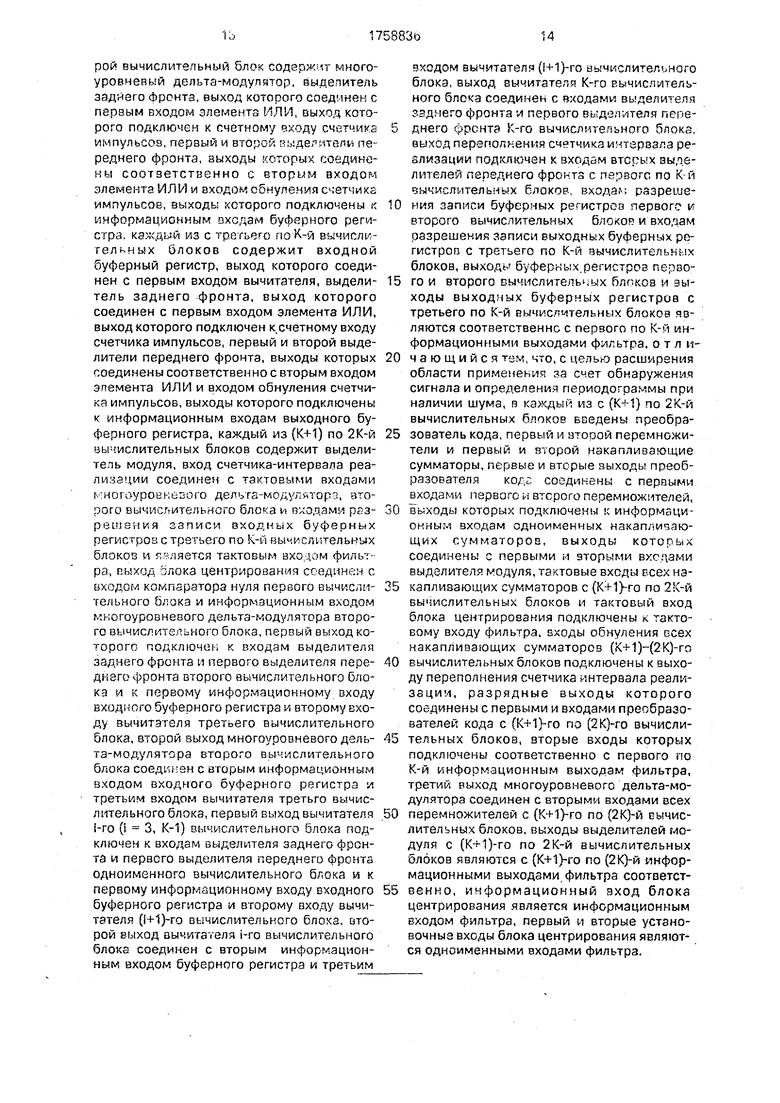

Совокупность блока 1 центрирования, компаратора 4 нуля и многоуровневого дельта-модулятора 11 содержит (фиг.2) первый 29 и второй 30 перемножители, двоичный сумматор 31, вычитатель 32, буферный регистр 33, аналого-цифровой преобразователь 34, информационный вход 35, тактовый вход 36, первые 37 и вторые 38 установочные входы, первый 39 и вторые 40 выходы дельта-модулятора, третьи выходы дельта- модулятора 41, выход 42 компаратора нуля.

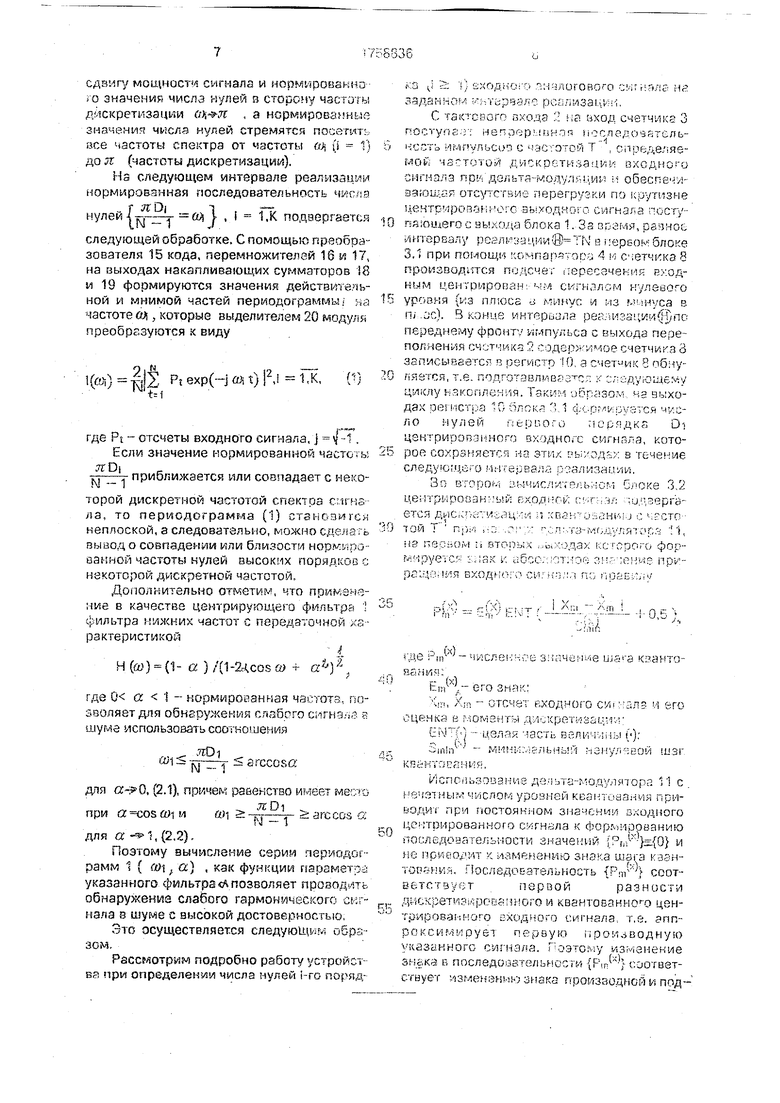

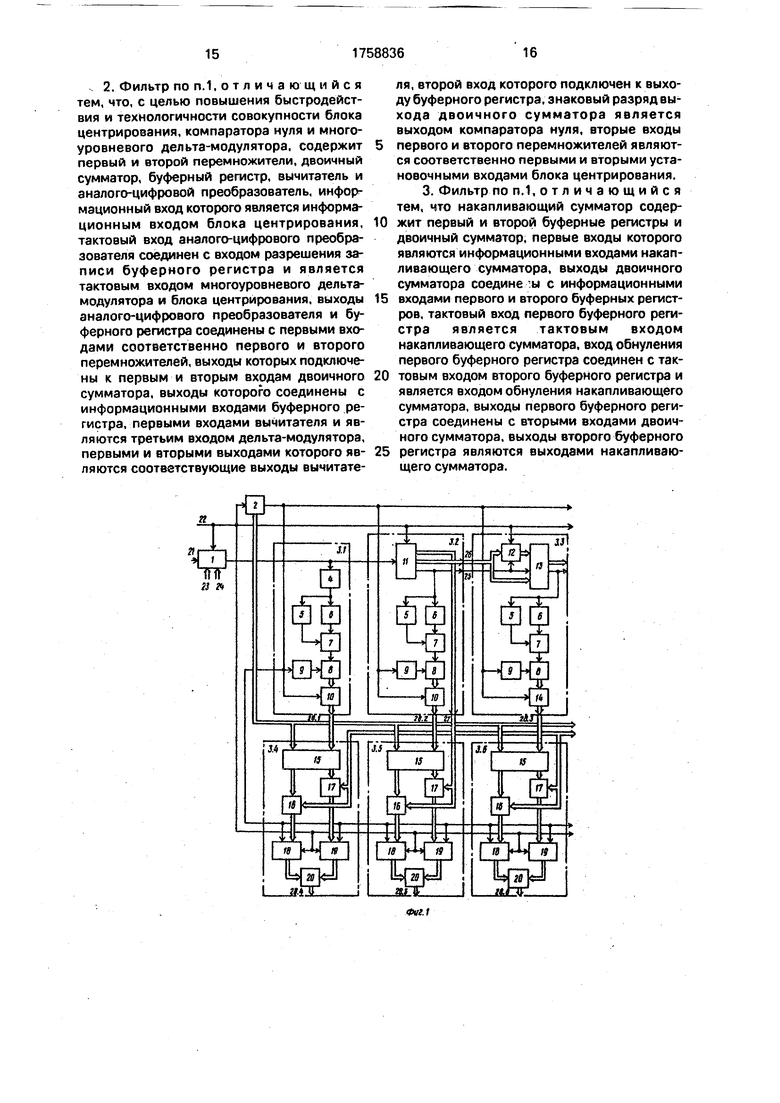

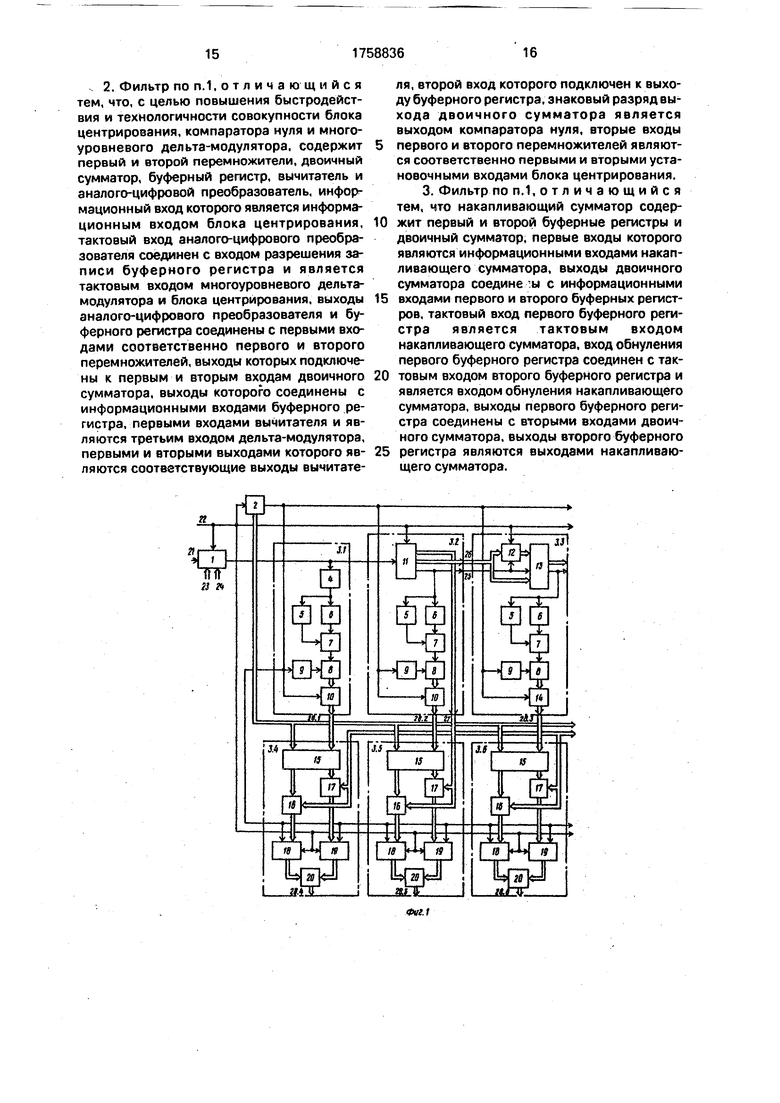

Накапливающий сумматор 18(19}содержит двоичный сумматор 43, первый 44 и второй 45 буферные регистры, информационные входы 46, тактовый вход 47, вход 48 обнуления, выходы 49.

В вычислительном блоке 31 выход компаратора 4 нуля через первый выделитель 5 переднего фронта и выделитель 6 заднего фронта подключен к первому и второму входам элемента 7 ИЛИ, выход которого соединен со счетным входом счетчика 8 импульсов, выход второго выделителя 9 переднего фронта подключен ко входуобнуле- ния счетчика 8 импульсов, выходы которого соединены с информационными входами буферного регистра 10. В вычислительном блоке 3.2 выход выделителя 6 заднего фронта соединен с первым входом элемента 7 ИЛИ, выход которого подключен к счетному входу счетчика 8 импульсов, выходы первого 5 и второго 9 выделителей переднего фронта соединены соответственно со вторым входом элемента 7 ИЛИ и входом обнуления счетчика 8 импульсов, выходы которого подключены к информационным

входам буферного регистра 10. В каждом 3.1 вычислительном блоке (I 37R) выхода входного буферного регистра 12 соединены с первыми входами вычитателя 13, выход выделителя 6 заднего фронта соединен с первым входом элемента 7 ИЛИ, выход которого подключен к счетному входу счетчика 8 импульсов, выходы первого 5 и второго 9 выделителей переднего фронта

0 соединены соответственно со вторым входом элемента 7 ИЛИ и входом обнуления счетчика 8 импульсов, выход которого подключены к информационным входам выходного буферного ре лстра 14. В каждом 3.j

5 вычислительном блоке (j К + 1,2К) первые я вторые выходы преобразователя 15 кода соединены с первыми входами первого 16 и второго 17 перемножителей, выходы которых подключены к информационным вхо0 дам накапливающих сумматоров 18 и 19 соответственно, выходы которых соединены с первыми и вторыми входами выделителя 20 модуля.

Тактовые входы всех накапливающих

5 сумматоров 18 и 19 вычислительных блоков 3.(К+1)-3.(2К), тактовый вход блока 1 центрирования, вход счетчика 2 интервала реализации, тактовый вход многоуровневого дельта-модулятора 11 вычислительного бло0 ка 3.2, входы разрешения записи входных буферных регистров 12 вычислительных блоков 3,3-3.К объединены и являются тактовым входом 22 фильтра, информационным входом 21 которого является

5 информационный вход блока 1 центрирования, первым 23 и вторым 24 установочными входами фильтра являются соответствующие установочные входы блока 1 центрирования, выход которого соединен со входом

0 компаратора 4 нуля вычислительного блока 3.1 и информационным входом многоуров- невсго дельта-модулятора 11 вычислительного блока 3.2, первый выход 25 которого подключен ко входам выделителя 6 заднего

5 фронта и первого выделителя 5 переднего фронта, вычислительного блока 3.2 и к первому информационному входу входного буферного регистра 12 и второму входу вычитателя 13 вычислительного блока 3.3.

0 Вторые выходы 26 многоуровневого дельта- модулятора 11 вычислительного блока 3.3 соединены со вторыми информационными входами буферного регистра 12 и третьими входами вычитателя 13 вычислительного

5 блока 3,3. Первый выход вычитателя 13 вычислительного блока З.т (т З.К-1) подключен ко входам выделителя 6 заднего фронта и первого выделителя 5 переднего фронта одноименного вычислительного блока и к первому информационному входу входного

буферного регистра 12 и второму входу вы- читателя 13 вычислительного блока 3.(т+1), вторые выходы вычитателя 13 вычислительного блока З.т соединены с аторыми информационными входами входного буферного регистра 12 и третьими входчми вымогателя

13вычислительного блока J.fm4- 1), выход вычитателя вычислительного блока З.К соединен с входами выделителя 6 заднего фронта и первого выделителя 5 переднего фронта одноименного вычислительного блока. Выход переполнения счетчика 2 интервала реализации подключен к входам вторых выде 9 переднего фронта вычислительных блоков 3.1-3.К входам разрешения записи буферных регистров 10 вычислительных блоков 3.1 и 3.2, входом разрешения записи выходных буферных регистров

14вычислительных блоков 3.3-3.К, входам обнуления всех накапливающих суммато- ров 18 и 19 вычислительных блоков 3 (К+1)-3

(2К). Разрядные выходы счетчика 2 интервала реализации соединены с первыми входами преобразователей 15 вычислительных блоков 3.(К+1)-3.(2К). Выходы буферных ре- гистров 10 вычислительных блоков 3.1 и 3.2, выходы выходных буферных регистров 14 вычислительных блоков 3.3-3 К являются соответственно информационным выходами 28..К фильтра и соединены соответ- ственно со вторыми входами преобразователей 15 кода вычислительных блоков 3.(К+1)-3.(2К). Третьи выходы 27 многоуровневого дельта-модулятора i соеди нены со вторыми входами всех перемножителей 16 и 17 вычислительных блоков 3.(К+1)-3.(2К). Выходы выделителей 20 модуля вычислительных блоков 3.(К+1)- 3.(2К) являются информационными выходами 28.(К+1)-28.(2К) фиЛьтра.

Блок 1 центрирования, компаратор4 нуля и многоуровневый дельта-модулятор 11 выполнены в виде аналого-цифрового преобразователя 34, информационный вход 35 которого является информационным вхо- дом блока 1 центрирования, тактовый вход 36 аналоге-- мфрофого преобразователя 34 объединен со входом разрешения записи буферного pei истра 33 и является тактовым входом блока 1 и дельта-модулятора 11, вы- ходы аналого-цифрового преобразователя 34 и буферного регистра 33 соединены с первыми входами соответственно первого 29 и второго 30 перемножителей, выходы которых подключены к первым и вторым входам двоичного суммматора 32, выходы которого соединены с информационными входами буферного регистра 33, первыми входами вычитателя 32 и являются третьими выходами 41 дельта-модулятора 11, первым

39 и вторыми 40 выходами которою яоля- ются первый и вторые выходы вычитагеля 32, вторые входы которого подключены к выходам буферного регистра 33, знаковый разряд третьиt выходов 41 является ЕЫХО- дом 42 компаратора 4 нуля, вторые входы 37 и 38 соответственно первого 29 и второго 30 перемножителей являются соответственно первыми и вторыми установочными входами блока 1 центрирования.

В накапливающем сумматоре 18 (19) первые входы двоичного сумматора 43 являются мнформациоными входами 46 блока 18, выходы ДРОИЧНОГО сумматора 43 соединены с информационными входами буферных регистров 44 и 46, тактовый вход пеового буферного регистра 45 является тактовым входом блокя 18, оход обнуления первого буферного регистра 45 объединен г вым входом в горе о б Ферного оегистра 16 и является входом 48 о™нупания блока 13, выходы первого буферного регистра 44 соединен с вторыми входами двоичного сумматора 43, тыходы второго буферного регистра 45 являются водами 49 накапливающего сумматора 18

Цифровой фильтр работает следующим образом

В устройстве производится следующая обработка входного аналогового сигнала. При помощи блока 1 центрирования из входною аналогового сигнала, nocrv K)- щего на информационный вход 21, удаляется постоянная составляющая и одновременно производится коррекция спектра сигнала с подчеркиванием и подавлением отдельных частотных полос. В каждом блоке 3.I, 1 1,К за время, равное интервалу реализации { определяемому частотой Т дискретизации и коэффициентом N деления счетчика 2,(н) М-Т, производится определение нормированного числа 1-го порядка DI входного центрированного повторно-разностного сигнала: в блоке 3.1 - число пересечений входным сигналом нулевого уровня, во втором блоке 3.2 - число пересе- ений производной входного сигнала нулевого урогня, в третьем блоке 3.3 - число пересечений второй производной входного сигнала нулевого уровня и т,д. На выводах вычитзтеля 13 соответствующего вычислительного блока формируется последовательность значений повторно-разностного сигнала 1-го порядка, причем нормированное значение числа нулей этого сигнала позволяет определить доминирующую частоту

ягО|..

спектра УД « - ui Увеличение порядка

повторно-разностного сигнала приводит к

мощности сигнала и норч роч&мо iO значений число н/лей п сгоосму JP 1скретгзации аъ-ъ-п а нормирована ,2на-ч чич ш- сля нулей стремятся пометит ,ice частоты спектра от эстеты см i 1 до п (част рты дискретизации).

На следующем интервале реализации нормированная последовательность ч/i з

нулей {-гр-г - Ч 1 , I 1.К поцчергаетсч

следующей обрабоч ке. С помощ&ю преобра- зовагелч 15 кода, перемножигелей 18 и 17, на выходах накапливающих сумматоров 18 и 19 формируются значения действительной и мнимой частей периодограммы ,з частотеол , которые выделителем 20 модуля преобргзуются к виду

:||Е Ptexp(

12,

1,К,

где Pt - отсчеты входного сигнала, j у 1 Если значение нормированной часто s

Т7--V приближается или совпадает с нето1м - Т

торой дискретной частой cnetcoa г иьг ла, то периодограмма (1) стангтигсл неплоской, а следоватепьио, можно сд jo t выдоцо совпадении или близости нор -- j ваиио частоты нулей высоких порялчоа с некоторой дискретной частотой

Дополнительно отметьv, то приюн - ние в качестве центрирующею viwt,ipa нижних частот с перевалочной /. рактеристико

Ч (и) (1- а } /(1-24COS о -t- a41)2.,

где 0 а. 1 - нормированная ча ftr го- З80.пя8т для обнаружения riaorro c.im л шуме использоватьсоо,но)иечмя

uDi 1 at cccso

для , (2 1), пример- равенство ииее-т ме ч

jrDi

ПРИ ( -ТГГГТ - ГССОЬ

для а -ч 1, (2 2)

Поэтому вычисление серии пер /одо рамм 1 { он ; а) , как функции иаозмет: указанного фильтра дпозволяет провод Tt обнаружение слабого гармонмчихогс СЕ - нэпа в шуме с высокой достоверностью

Это осуществляется следующ /f. U&P-. зом

Расср отрим подробно работу ус роист ва при определении числа нулей i го поряд

ti чоа i ивового „ г i с iv

S3f-Ki тГii- d г г- fK l43ai

Г га ее. Oif о млз а ЧХО/.1 ичетч.1К J

r O- V if h ic/Hiyr nL, v in /A с -« э см Г мр-ое яеt- ot ic. г iu/ г/ir-KDf Th 5a j.Ki з/одно -j

11 - 3 О I D CMV I l Mi,

34, JL 1„ i eperpvj jt и п / i j/тизне

иеЫС р.04 С ЗЬ - и 1ГНЗГЯ I

0 -й ошего чу т, i блпка 1 За , iiijopsjij ро л ч1 иЭ N 3i dpcoK 3.1 при пк иощп t inai or 4 г етч кз 8 произвид гея п С1-1 -1, рр чеьмг- р ог,НЫМ (СН.ПИрОР и г М НупеьО -&

Г уровня /з пт оса A-JHVC yi и и са и nj 1 В У }нч Hir pujPr пес передному фоонт tea с вчхода пеое

ПОЯ ГЦ Т ) v 1етЧИг)3 ЗСПИ „ЫР&9ГС- п fJ Л С t°T JH ч р пб Jy

С - е -пп -т-чвл) , Ci-tf v

«диспу j-Tcnrt, |Я г ч зо -а э хода ОГЧ1 С . Г Гг I 1 О Г /-У j - СЯ , /iO ЧУле etjLO u ир ЦКГ О-

Ц01. рИппгз | 40 П Bv }ЦНО.ч, КОТО рог ио роНяет J зг од в гые1 ie слецх, о ч j 5 i 1 a i/idi 113 в i о ,- ь N С ске S J

UP i p DOJjh U Г/-ОП Г1 f f н j pplo

CK i ц ; г н j т

J 7 ЗИ Г Г ji i J Г г я г I

i - i i i 1чт т.-ч i, ia i w фо

о с С (. т С5 i, r i C/

PC t F С СЦ / Чи г

i JC |у „ГР1 «Ј «И

i ii - С Зи i

e

i en

Tf4 °t-/, C/i

4F4t4r J O M J (-.111 CpPf „GL

i i j d°T i I ()

in i1- (iH-i M „l O /i Ш31 h.71 a f

S/iCPt io о 35i 1Я10Г 3 1 С f THtlV l iCHO V OJHCU KbjHu Л VIM i , г, постоянном 3najn-4V : одного

ЦС ГОЧрОВЗН. ОГ 1 Г/ГЧ-Л1 К ФОр ) ЗОйТН Ю

or 1с,чозаге/ „ «огти елачени/ ,0г }.{0} и ) f ьОл1 п jHiito зн а Шея а з н- (ОР н - Jot 5ьд«« этелаьость Г i/ соот йстггз тпорзойраоньсги

,,( se-rv- (ifi & ь п.о и кванюБтин гп цен- j-iVOBa Jro л од к о-э И1нрла ге эпг. or-г г 11оует первую иооиоводную i лаЗб-ннэго си нз а rj3 0v/ из viai-sei-ие ь посгедозй л1 HuCiM F - 1 t jorseT- t гнуег 1зг«ен ч „иг.га пиопзводно и подсчитывается зз интервал реализации в счетчиком 3. В конце интервала реализации по импульсу с выхода переполнения счетчика 2 накопленное в счетчик ; 8 значение запись Сйетс;я в регистр 10, а счетчик 8 обнуляется, чем подготавпизается к следующему периоду накопления Такмм образом, на выходах регистра 10 блока 3.2 формируется число пулей второго порядка Da, которое сохраняемся нз .этих выходах s течение следующего интервала реализации.

Формирование числа нулей более высоких порядков рассмотрим на примере блока З.К с . Последовательность значений {Рт }, поступающая с первого и вторых выходов 25 и 26 многоуровневого дельта-модулятора 11 блока 3.2, стробируется во входном буферном регистре 12, в результате чего за период дискретизации Т на входах и выходах этого регистра 12 присутствуют значения Рт и Рт-1 , которые подаются на входы вычитателя 13. Вычитатель 13 осуществляет разностную операцию vXm -Pm - Pm-r которая при соответствует формированию второй разности дискре- тизированного и квантованного центрированного входного сигнала, Изменение знака сигнала {/Хщ}(ич минуса в г, юс и из плюса в минус) формирующегося на первом выходе выиитг сгя 13 подсчитывался счетчичсм 8 зз интервал реализации и записывается по сигналу с выход переполнения счегчмка 2 в конце реализации в выходной буферный регистр 14, а счетчик 8 обнуляется, чем подготавливается к новому циклу накопления. Блоки З.К для ,К работают аналогично. Таким образом на выходах регистров 14 блоков З.К формируются значения числа нулей К-го порядка D. которые сохраняются на этих выходах в течение следующего интервала реализации. „ Вычисление периодограммы ( ад ), i 1,К производится в следующем интервале реализации следующим образом.

Рассмо-рим вычисление значения отсчета 1 ад , 1,К на примере вычислительного блока 3.(Ю-1).

На первые входы преобразователя 15 кода за время интервала реализации поступает последовательность значений { t }, ,((H)/T) с разрядных выходов счетчика 2 интервала реализации. Нз вторые входы этого преобразователя с информационных выходов 28.1 вычислительного блока 3.1 подается значение числа нулей высокого порядка DI, вычисленное в предыдущем интервале реализации©- По каждому значению t с разрядных выходов счетчика 2 на первых выходах преобразователя 15 формируется соответствующее зна ттТ™51

чение , равное sln()t. Указанные

синусная и косинусная последовательности поступают на первые входы перемножителей 16 и 17. на вторые входы которых с третьего выхода 27 многоуровневого дель- тз-модулятора 11 вычислительного блока 3.2 поступает последовательность отсчетов { Rm } входного сигнала, формируемая по правилу

60 ЕЙ

ENT(+0,5),

sm

(4)

,

где - численное значение отсчета входного сигнала;

Ет - его знак,

В результате этого на выходах перемножителей 16 и 17 формируются последовательности значений

НХЬК1.)(,)}

которые за интервал реализации (И)по импульсам с тактового кода 22 цифрового фильтра непрерывно накапливаются в накапливающих сумматорах 18 и 19. В конце интервала реализации число указанных накопленных значений произведений равно . и по импульсу с выхода переполнения счетчика 2 эти накопленные значения фиксируются а регистрах 45 накапливающих сумматоров 18 и 19. Таким образом, в конце этого интервала реализации на выходах накапливающихся сумматоров 18 и 19 фиксируются значения сумм

S,

45

(соа(,),

которые в следующем интервале реализации поступают на первые и вторые входы выделителя 20 модуля.

Выделитель 20 модуля вычисляют значение if ). согласно (1), равное ( щ )

2/N (Si + S22), которое поступает с его выходов на информационные выходы 28.(К+1). БлокиЗ.К+2-3.(2К) работаютаналогично. Таким образом, на выходах 28.(К+1)-28.(2К) выделителей 20 модуля вычислительных блоков 3.(К+1)-3.(2К) формируется последовательность обсчетов периодограмм (К гд )}, 1, К, которые сохраняются на этих выходах в течение следующего интервала реализации.

Блок 1 центрирования, компаратор 4 нуля и многоуровневый дельта-модулятор 11 работают следующим образом (фиг.2). Входной аналоговый сигнал х (t) с входа 35 филь- тра в аналого-цифровом преобразователе 34 подвергается дискретизации и квантованию с частотой , в результате чего на выходе блока 34 формируется последовательность отсчетов входного сигнала {Хт}, которая поступает на первые входы первого перемножителя 29. На вторые входы этого перемножителя 29 с первых установочных входов 37 подается значение сигнала (1- а ), в результате чего на выходах перемножителя 29 формируется последовательность { (1- а )Хт}, поступающая на первые входы двоичного сумматора 31. Выходной сигнал сумматора 31 задерживается в буферном регистре 33 на один период частоты дискретизации и поступает на первые входы второго перемножителя 30 и вторые входы вычитателя 32. На вторые входы перемножителя 30 со вторых установочных входов 38 подается значение сигнала а , в результате чего на вторые входы двоичного сумматора 31 поступает последовательность значений { a Ym-1}. Сумматор 31 суммирует выходные сигналы перемножителей 29 и 30, формируя выходную импульсно-ко- довомодулированную последовательность {Ym о. Ym-1 + (1 - « ) Xm} согласно (4) на выходах 41. Знаковый разряд(SYm(Ym)} последовательности {Ym}. подключенный дополнительно к выходу 42, является выходом компаратора 4 знака. Вычитатель 32 производит вычитание предыдущего отсчета Ym-i из текущего Ym, формируя выходной дельта- модулированный сигнал Pm Ym - Ym-1 согласно (3), модуль которого подается на выходы 40, а знаковый разряд - на выход 39. Таким образом, на первом 39, вторых 40 и третьих 41 выходах формируются последовательности сигналов {Syn(, {jPm }, {Pm }, эквивалентные соответственно последовательностям на выходах 25,26 и 27 многоуровневого дельта-модулятора 11 вычислительного блока 3,2.

Такое выполнение блока 1 центрирования, компаратора 4 нуля и многуровневого дельта-модулятора 11 позволяет увеличить технологичность и быстродействие цифрового фильтра, поскольку по сравнению с обычным фильтром нижних частот, компаратором нуля и многоуровневым дельта-модулятором, например (3), резко сокращено число аналоговых узлов, которые к тому же

обладают значительными задержками. В данном случае применяется только один цифроаналоговый блок 34, а остальные блоки являются цифровыми, что позволяет также реализовать высокое быстродействие.

Накапливающий сумматор 18 (19) (фиг.З) работает следующим образом.

Значение соответствующего произведения dt Rr sin( wi t) поступает с информационных входов 46 на первые входы двоичного сумматора 43, на вторые входы которого с выхода первого буферного регистра 44 поступает накопленное в нем значение. Сумматор 43 суммирует эти значения и

по импульсу с тактового входа 22 фильтра, поступающего на тактовый вход 47 блока 18, значение суммы записывается в регистр 44, В конце интервала реализации(ц)по импульсу с выхода переполнения счетчика 2, постулающему на вход 48 обнуления, значение накопленной в сумматоре 43 суммы записывается во второй буферный регистр 45 и поступает на выходы 19 блока 18, а первый буферный регистр сбрасывается в исходное, нулевое состояние.

Преобразователь 15 кода может быть выполнен в виде последовательного включения перемножителя, формирующего знаjrDiчение произведения тгрзт 1 из сигналов

DI и t, поступающих на его первые и вторые входы и постоянного запоминающего устройства (ПЗУ), с первых и вторых выходов которого по значениях указанного произведения считываются предварительно в них записанные значения соответственно.

Выделитель 20 модуля может быть выполнен в виде двух ПЗУ и двоичного сумматора, ПЗУ блока 20 из значений Si и За

формируют соответственно значения Si2 и Sa , а двоичный сумматор суммирует эти значения, формируя отсчет периодограммы 1 (ад). Остальные блоки могут быть выполнены аналогично прототипу.

Формула изобретения

1. Цифровой фильтр, содержащий блок центрирования, счетчик интервала реализации и с первого по 2К-й вычислительные блоки (), первый вычислительный блок

содержит компаратор нуля, выход которого через первый выделитель переднего фронта и выделитель заднего фронта подключен к первому и второму входам элемента ИЛИ, выход которого соединен со счетным входом счетчика импульсов, второй выделитель переднего фронта, выход которого подключен к входу обнуления счетчика импульсов, выходы которого соединены с информационными входами буферного регистра, второй вычислительный блок содержит многоуровневый депьта-модупятор, выделитель заднего Фронта, выход которого соединен с первым входом элемента ИЛИ, выход которого подключен к счетному входу счетчика импульсов, первый и второй выделители переднего фронта, выходы которых, соединены соответственно с вторым входом элемента ИЛИ и входом обнуления счетчика импульсов, выходы которого подключены к информационным входам буферного регистра, каждый из с третьего поК-й вычисли- гелкных блоков содержит входной буферный регистр, выход которого соединен с первым входом вычитателя, выдели- тель заднего фронта, выход которого соединен с первым входом элемента ИЛИ, выход которого подключен к счетному входу счетчика импульсов, первый и второй выделители переднего фронта, выходы которых соединены соответственно с вторым входом эгтемента ИЛИ и входом обнуления счетчика импульсов, выходы которого подключены к информационным входам выходного буферного регистра, каждый из (К+1) по 2К-й вычислительных блоков содерхсит выделитель модуля, вход счетчика-интервала реализации соединен с тактовыми входами гногоуровкьзого дельга-модулйторэ, второго вычислительного блока и входами рез- решения записи входных буферных регистров с третьего по К-й вычислительных блоков и является тактовым входом фильтра, пыход Ълока центрирования соединил с входом компаратора нуля первого вычисли- тельного блока и информационным входом многоуровневого дельта-модулятора второго вычислительного блока, первый выход которого подключи ; к входам выделителя заднего фронта и первого выделитепя пере- днего фронта второго вычислительного блока и к первому информационному входу входного буферного регистра и второму входу вычитателя третьего вычислительного блока, второй выход многоуровневого дель- та-модулятора второго вычислительного блока соединен с вторым информационным входом входного буферного регистра и третьим входом вычитателя третьго вычислительного блока, первый выход вычитателя i-ro (I 3, К-1) вычислительного блока подключен к входам выделителя заднего фронта и первого выделителя переднего фронта одноименного вычислительного блока и к первому информационному входу входного буферного регистра и второму входу вычи- тэтеля (i+1)-ro вычислительного блока, второй выход аычитагеля i-ro вычислительного блока соединен с вторым информационным входом буферного регистра и третьим

входом вычитателя (-И)-го вычислительного блока, выход вычитателя К-го вычислительного блока соединен с входами выделителя заднего фронта и первого выделителя переднего фронта К-го вычислительного блока, выход переполнения счетчика интервала реализации подключен к входам вторых выделителей переднего фронта с первого по К- и вычислительных блоков, входам разрешения записи буферных регистров первого v второго вычислительных блоков и входам разрешения записи выходных буферных регистров с третьего по К-й вычислительных блоков, выходы буферных.регистров первого и второго вычислительных блоков и выходы выходных буферных регистров с третьего по К-й вычислительных блоков являются соответственно с первого по К-й информационными выходами фильтра, отличающийся тем, что, с целью расширения области применения за счет обнаружения сигнала и определения периодограммы при наличии шума, в каждый из с (К+1) по 2К-й вычислительных блоков введены преобразователь кода, первый и зтооой перемножители и первый и второй накапливающие сумматоры, первые и вторые выходы преобразователя ко/-.г соединены с первыми входами первого и второго перемножителей, выходы которых подключены к информационным входам одноименных накапливающих сумматоров, выходы которых соединены с первыми и зторыми входами выделителя модуля, тактовые входы всех накапливающих сумматоров с (К+1)-го по 2К-й вычислительных блоков и тактовый вход блока центрирования подключены к. тактовому входу фильтра, входы обнуления всех накапливающих сумматоров (К+1)-(2К)-го вычислительных блоков подключены к выходу переполнения счетчика интервала реали- зацим, разрядные выходы которого соединены с первыми и входами преобразователей кода с (К+1}-го по (2К)-го вычислительных блоков, вторые входы которых подключены соответственно с первого по К-й информационным выходам фильтра, третий выход многоуровневого дельта-модулятора соединен с вторыми входами всех перемножителей с (К+1}-го по (2К)-й вычислительных блоков, выходы выделителей модуля с (К-М)-го по 2К-й вычислительных блоков являются с (К+1)-го по (2К)-й информационными выходами фильтра соответственно, информационный эход блока центрирования является информационным входом фильтра, первый и вторые установочные входы блока центрирования являются одноименными входами фильтра.

2. Фильтр по п.1. о т л и ч а ю щ и и с я тем, что, с целью повышения быстродействия и технологичности совокупности блока центрирования, компаратора нуля и многоуровневого дельта-модулятора, содержит первый и второй перемножители, двоичный сумматор, буферный регистр, вычитатель и аналого-цифровой преобразователь, информационный вход которого является информационным входом блока центрирования, тактовый вход аналого-цифрового преобразователя соединен с входом разрешения записи буферного регистра и является тактовым входом многоуровневого дельта- модулятора и блока центрирования, выходы аналого-цифрового преобразователя и буферного регистра соединены с первыми входами соответственно первого и второго перемножителей, выходы которых подключены к первым и вторым входам двоичного сумматора, выходы которого соединены с информационными входами буферного регистра, первыми входами вычитателя и являются третьим входом дельта-модулятора, первыми и вторыми выходами которого являются соответствующие выходы вычитатеЛЯ, ВТОРОЙ ВХОД КОТОРОГО ПОДКЛЮЧеН К ВЫХОДУ буферного регистра, знаковый разряд выхода двоичного сумматора является выходом компаратора нуля, вторые входы первого и второго перемножителей являются соответственно первыми и вторыми установочными входами блока центрирования. 3. Фильтр по п.1, отличающийся тем, что накапливающий сумматор содер- жит первый и второй буферные регистры и двоичный сумматор, первые входы которого являются информационными входами накапливающего сумматора, выходы двоичного сумматора соедине ы с информационными входами первого и второго буферных регистров, тактовый вход первого буферного регистра является тактовым входом накапливающего сумматора, вход обнуления первого буферного регистра соединен с так- товым входом второго буферного регистра и является входом обнуления накапливающего сумматора, выходы первого буферного регистра соединены с вторыми входами двоичного сумматора, выходы второго буферного регистра являются выходами накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр | 1990 |

|

SU1815797A1 |

| Цифровой фильтр | 1990 |

|

SU1736002A2 |

| Цифровой фильтр | 1989 |

|

SU1695493A2 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр | 1989 |

|

SU1695492A2 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1990 |

|

SU1716607A1 |

| Цифровой фильтр с симметричной импульсной характеристикой | 1987 |

|

SU1495979A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1510091A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

Изобретение относится к области автоматики и вычислительной техник и может быть использовано в системах обпаботки изображений, корреляционного и спектрального анализа и т.п. Цель изобретения - расширение области применения за счет обнаружения сигнала и определения периодограммы при наличии шума. Цифровой фильтр содержит блок центрирования, счетчик интервала реализации, вычислительные блоки, первый вычислительный блок содерИзобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки изображений, корреляционного и спектрального анализа и т.п. Цель изобретения - расширение области применения, за счет обнаружения сигнала и определения периодограммы при наличии шума. На фиг.1 приведена структурная схема цифрового фильтра; на фиг.2 - выполнение совокупности блока центрирования, компажит компаратор нуля, первый выделитель переднего фронта выделитель заднего фронта, элемент ИЛИ, счетчик импульсов, второй выделитель переднего фронта, буферный регистр . Второй вычислительный блок содержит многоуровневый дельта-модулятор, первый выделитель переднего фронта, выделитель заднего фронта, элемент ИЛИ, счетчик импульсов, второй выделитель переднего фронта, буферный регистр; i-й вычислительный блок содержит входной буферный регистр, вычитатель, первый выделитель переднего фронта, выделитель заднего фронта, элемент ИЛИ, счетчик импульсов, второй выделитель переднего фронта, выходной буферный регистр; j-й вычислительный блок содержит преобразователь кода, первый и второй перемножители первый и второй накапливающие сумматоры, выделитель модуля. Указанная совокупность признаков позволяет достигнуть указанной цели. 2 з.п.ф-лы, Зил. ратора нуля и многоуровневого дельта-модулятора; на фиг.З - выполнение накапливающих сумматоров. Цифровой фильтр содержит (фиг.1) блок 1 центрирования, счетчик 2 интервала реализации, вычислительные блоки 3.1-3.(2К), , (на фиг.1 ), вычислительный блок 3.1 содержит компартор 4 нуля, певый выделитель 6 переднего фронта, выделитель 6 заднего фронта, элемент 7 ИЛИ. счетчик 8 импульсов, второй выделитель 9 переднего фронта, буферный регистр 10. ВычислительXI ся 00 00 со о

п

ТЫ

IайСI

3§

34

29

J

37

Фаг.2

31

42

4/

30

33

k

д2 Кя

ттмтшмЛ

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фильтр | 1989 |

|

SU1695493A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-30—Публикация

1990-12-13—Подача