Изобретение относится к вычислительной технике и может быть использовано для цифровой фильтрации случайных процес- - сов, в частности, в спектроанализаторах параллельного действия с использованием формата многоуровневой дельта-модуляции (МДМ) для представления входного сигнала.

Цель изобретения - повышение разрешающей способности, быстродействия и упрощение фильтра.;

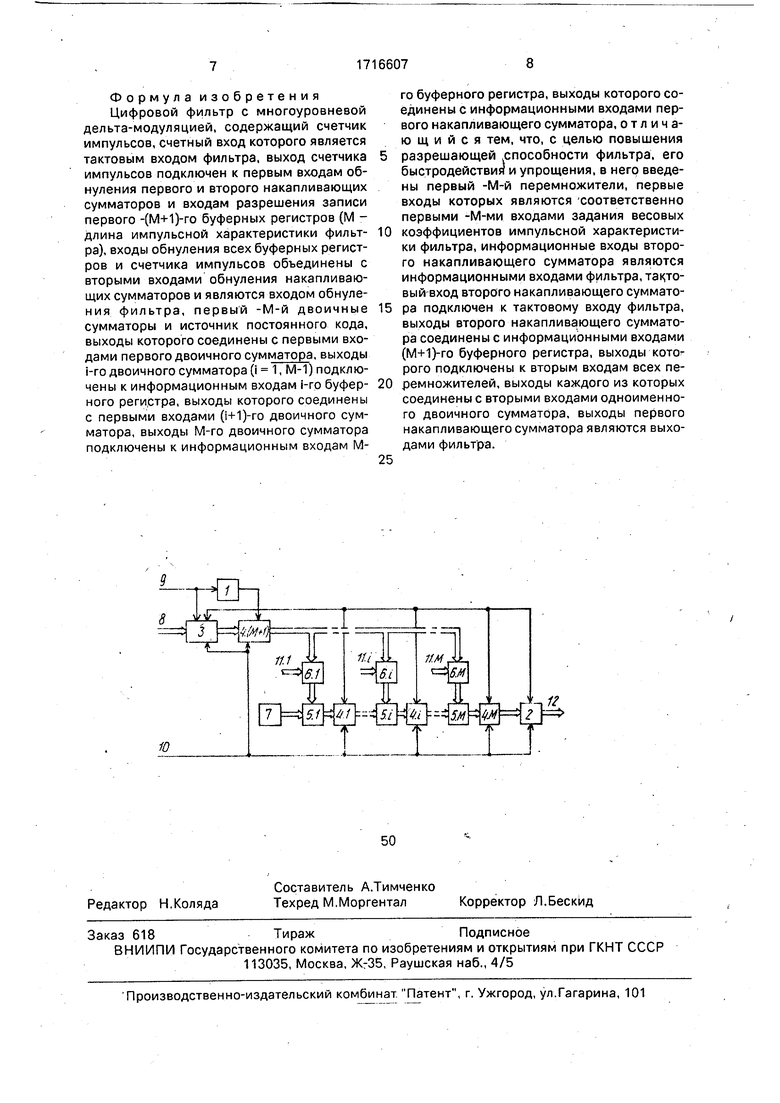

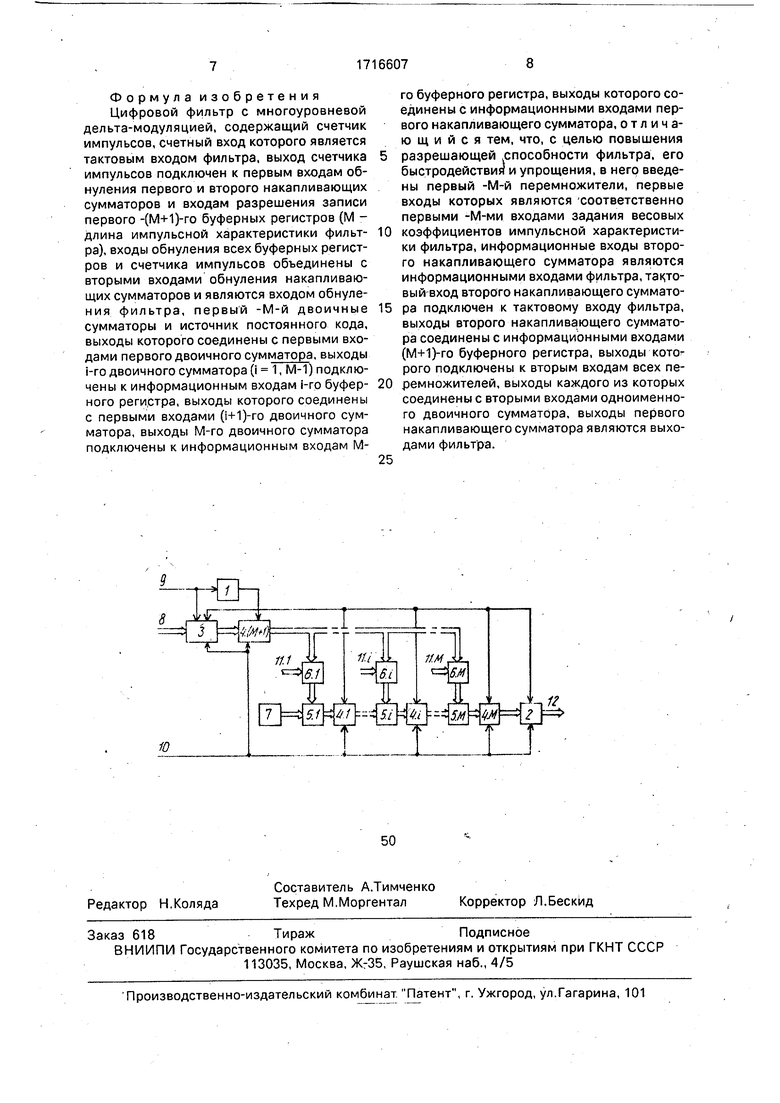

На чертеже приведена структурная схема цифрового фильтра с многоуровневой дельта-модуляцией.

Цифровой фильтр с многоуровневой дельта-модуляцией содержит счетчик 1 им-: пульсов, первый и второй накапливающие сумматоры 2 и 3, буферные регистры 4.1...4.(М+1), двоичные сумматоры 5.1...5.М, перемножители-6.1...6.М, где М -длина им- - пульсной характеристики фильтра, источ- ник.7 постоянного кода, информационные

входы 8 фильтра, тактовый вход 9, вход 10 обнуления фильтра, входы 11.1...1.М задания весовых коэффициентов импульсной характеристики фильтра, выходы 12 фильтра. Счетный вход счетчика 1 импульсов объединен с входом разрешения записи второго накапливающего сумматора 3 и является тактовым входом 9 фильтра, информационными входами 8 которого являются информационные входы второго накапливающего сумматора 3, выходы которого подключены к информационным входам буферного регистра 4.(М+1). Входы обнуления счетчика 1 импульсов, буферных регистров 4.1...4.(М+1), накапливающих сумматоров 2 и 3 объединены и являются входом 10 обнуления фильтра. Выходы источника 7 постоянного кода соединены с первыми входами двоичного сумматора 5.1, выходы двоичного сумматора 5.i, i 1,М подключены к информационным входам буферного регистра 4.I. выходы буферного регистра 4:j, j 1. М-1 сосо

С

С О О VJ

единены с первыми входами двоичного сумматора 5.0+1), выходы буферного регистра 4.М подключены к информационным входам первого накапливающего сумматора 2, вход разрешения записи которого объединен с одноименными входами блоков 4.1...4.(М+1), вторым входом обнуления второго накапливающего сумматора 3 и подключен к выходу счетчика 1 импульсов. Первые входы перемножителя 6.1...6.М являются входами 11.1...11.М задания весовых коэффициентов импульсной характеристики, выходы буферного регистра 4.(М+1) подключены к вторым входам всех перемножителей 6, выходы каждого из которых соединены с вторыми входами одноименного двоичного сумматора, выходы .первого накапливающего сумматора 2 являются выходами 12 фильтра.

Цифровой фильтр с многоуровневой дельта-модуляцией работает следующим образом.

В предлагаемом устройстве производится обработка входного МДМ-сигнала с использованием ИКМ-формата импульсной характеристики, с частотой дискретизации, характерной для этого вида модуляции. Выходной сигнал этого фильтра представлен в привычном ИКМ-формате с частотой дискретизации, в q раз меньшей частоты дискретизации входного сигнала. Причем по сравнению с прототипом сняты всякие ограничения на коэффициент прореживания q выходного сигнала, что позволило увеличить быстродействие фильтра путем соответствующего увеличения частоты дискретизации входного сигнала и упростить фильтр за счет уменьшения объема используемой памяти. Последнее достигается за счет существенно меньшей разрядности суммы q шагов квантования входного сигнала по сравнению с разрядностью последовательности из q последовательных шагов, рост разрядности имеет не линейный, как в прототипе, а логарифмический характер, поэтому выигрыш в объеме памяти значительный даже при сравнительно низких значениях коэффициента прореживания q. Кроме того, входной сигнал в формате МДМ и импульсная характеристика в формате ИКМ позволяют получить высокую, наперед заданную разрешающую спосрбность фильтра путем увеличения их разрядностей, что было невозможно в прототипе.

Работа фильтра начинается с прихода установочного импульса на вход 10 обнуления фильтра. В результате воздействия этого импульса на входы обнуления счетчика 1 импульсов, буферных регистров

4.1...4.(М+1), накапливающего сумматора 2 и вход обнуления накапливающего сумматора 3 на выходах указанных блоков и на выходе 12 фильтра устанавливается нулевое значение сигнала независимо от сигналов на других входах указанных блоков.

На информационный вход 8 фильтра поступает входной сигнал в формате МДМ, обладающий спектром, ограниченг-1

ным частотой Т , в виде {snv }, п О, который сопровождается импульсами с частотой дискретизации на тактовом входе 9, Тд . Сигнал sn(x в блоке 3 суммируется с его содержимым по импульсам на тактовом входе 9. Одновременно тактовые импульсы поступают на счетный вход счетчика 1 с коэффициентом пересчета, равным коэффициенту прореживания q выходного ригнала фильтра. Импульс с выхода

счетчика 1 поступает на входы разрешения записи блоков 4.1...4.(М+1), накапливающего сумматора 2 и второй вход обнуления блока 3. В результате воздействия этого импульса в буферном регистре 4.(М+1) фиксируется значение сигнала Yn, образованное суммой из q последовательных значений входного сигнала {sn-q+r }, г 1, q:

Yn

г 1

Sn-q+r

r.x)

а блок 3 сбрасывается в исходное нулевое состояние.

Значение Yn поступает на вторые входы всех перемножителей 6., i 1 ,М. На первый вход перемножителя 6.I с входа 11.1 подано значение весового коэффициента ИХ в формате ИКМ: Ьм-i. На выходе перемножителя 6.i формируется произведение YnhM-i, которое складывается в сумматоре 5.i со значением Sk-HM-(i-i) . вычисленным в блоке 5.(Ы) в (k-1)-OM такте времени Tn qTA, .

С учетом того, что на первые входы двоичного сумматора 5.1 подан сигнал нулевого значения с источника 7 кода, на выходе буферного регистра 4,i формируется значение сигнала

50

Sk-Ki-1)W 2 Yn-mhM-n

m 1

Для i-M-ro регистра 4 число слагаемых этой суммы равно М, а значение S/M уг,

м -1 где 7Ук X hmYn-m - первая разность,

m 0

формируемая на выходе блока 4.М из последовательно сти произведений Ynhiyi-j. Учитывая выражение для {Yn}, можно записать

М-1 -о

V Yk 2 nm 2, Sn-q+r. r 1

Таким образом, на выходе буферного регистра 4.М формируется последовательность значений fyyk}, к 0, которая поступает на накапливающий сумматор 2, формируя на выходе последнего прореженный в q раз выходной сигнал цифрового фильтра с многоуровневой дельта-модуляцией в формате И КМ с частотой дискретизации V1 Г1:

М -1q -1

yn+q-1 yn+- Ј hm E SrvH-mW

m 0

i - о

n + q - 1 M - 1

2E hmSr-mW.

r 1 m 0

При случайных сбоях, например по питанию, нормальная работа цифрового фильтра с многоуровневой дельта-модуляцией восстанавливается подачей сигнала на вход 10 обнуления фильтра.

Затраты времени на вычисление одного значения первой разности7Ук равны t tn + tc, где tn и tc - время выполнения операций умножения в блоке 6 и суммирования в блоке 5 соответственно. Период частоты дискретизации входного сигнала

соответствует периоду Тд -- - , что

позволяет обрабатывать сигнал с соответствующим спектром.

Перемножитель 6.i для одного заданного значения весового коэффициента hw-i может быть выполнен на постоянном запоминающем устройстве (ПЗУ), число адресных входов которого соответствует разрядности значений {Yn}. При разрядности входного сигнала bi, разрядность значений {Yn} равна b2 bi+ logaq, а требуемый в этом случае собьем памяти одного ПЗУ равен QI

. Суммарный объем исполь

I- - - VJA - j - - - - (.т

зуемой памяти составляет Q MQi Mq2 4 ячеек.

Сравнивая этот обьем памяти с объемом памяти преобразователей кода

прототипа Qj - 2Р. где Р - коэффициент прореживания входного сигнала в формате линейной дельта-модул яции (ЛДМ) известного устройства, получим

м р

2Р/М 2bl Hcq24 2p bVpq. При

одинаковой частоте следования входных и выходных сигналов сравниваемых устройств р q, тогда соотношение QC/QЈ 1 при типовом значении bi 4 уже для q 11. Отметим, что сравнение производилось для входного сигнала в формате ЛДМ устройства-прототипа и входного МДМ0 сигнала предлагаемого устройства с разрядностью bi 4, что сразу же предопределяет за счет уменьшения разрядности не только выигрыш в объеме используемой памяти и соответственном упрощении филь5 тра, но и существенном увеличении разрешающей способности за счет увеличения разрядности входного сигнала.

Одновременно за счет нелинейной (логарифмической) зависимости роста разряд0 ности b2 bi + logaq от коэффициента прореживания q практически сняты ограничения на величину q поскольку например, при и ограничении 02 13 (выполнении блока 6.i на ПЗУ типа КР556 РТ17) значение

5 коэффициента прореживания может достигать q 512, в то время как в фильтре-прототипе при использовании ЛДМ формата такое значение q требует построения преобразователя кода с 512 входами, что нереали0 зуемо. Поэтому снятие этого ограчения позволяет дополнительно значительно увеличить частоту дискретизации Тд , а значит соответственно увеличить .быстродействие фильтра.

5 Отметим, что наличие в фильтре входов 11,Г, i 1,М, задания значений весовых коэффициентов позволяет использовать предлагаемое устройство в системах с быстрой перенастройкой передаточной

0 характеристики, например, при осуществлении адаптивной фильтрации, в то время как в устройстве-прототипе для осуществления перенастройки фильтра необходимо полностью заменить запи5 санную в преобразователях кода информацию, что требует значительно большего времени.

Поэтому введением в известное устройство перемножителей 6.1 ...6.М с соот0 ветствующими связями достигнута поставленная цель - повышена разреша- . ющая способность фильтра, его быстродействие и упрощена конструкция за счет снятия всяких ограничений на увели5 чение коэффициента прореживания q выходного сигнала и логарифмической зависимости роста разрядности входных сигналов перемножителей 6 от значения q.

Формула изобретения Цифровой фильтр с многоуровневой дельта-модуляцией, содержащий счетчик импульсов, счетный вход которого является тактовым входом фильтра, выход счетчика импульсов подключен к первым входам обнуления первого и второго накапливающих сумматоров и входам разрешения записи первого -(М+1)-го буферных регистров (М - длина импульсной характеристики фильтра), входы обнуления всех буферных регистров и счетчика импульсов объединены с вторыми входами обнуления накапливающих сумматоров и являются входом обнуле- ния фильтра, первый -М-й двоичные сумматоры и источник постоянного кода, выходы которого соединены с первыми входами первого двоичного сумматора, выходы i-ro двоичного сумматора (i 1, М-1) подключены к информационным входам i-rp буферного регистра, выходы которого соединены с первыми входами (i+1)-ro двоичного сумматора, выходы М-го двоичного сумматора подключены к информационным входам М0

5

0

5

го буферного регистра, выходы которого соединены с информационными входами первого накапливающего сумматора, отличающийся тем, что, с целью повышения разрешающей способности фильтра, его быстродействия и упрощения, в негр введены первый -М-й перемножители, первые входы которых являются соответственно первыми -М-ми входами задания весовых коэффициентов импульсной характеристики фильтра, информационные входы второго накапливающего сумматора являются информационными входами фильтра, тактовый вход второго накапливающего сумматора подключен к тактовому входу фильтра, выходы второго накапливающего сумматора соединены с информационными входами (М+1)-го буферного регистра, выходы кото рого подключены к вторым входам всех перемножителей, выходы каждого из которых соединены с вторыми входами одноименного двоичного сумматора, выходы первого накапливающего сумматора являются выходами фильтра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фильтр с линейной дельта-модуляцией | 1990 |

|

SU1716606A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр | 1990 |

|

SU1758836A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1683172A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661969A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1510091A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661968A1 |

Изобретение относится к вычислительной технике. Его использование для цифро-2 вой фильтрации случайных процессов позволяет повысить разрешающую способность и быстродействие фильтра и упростить его. Фильтр содержит счетчик 1 импульсов, накапливающие сумматоры 2, 3 буферные регистры 4.1...4.(М+1), двоичные сумматоры 5.1...5.М(М -длина импульсной характеристики фильтра) и источник 7 постоянного кода. Положительный эффект достигается благодаря введению перемножителей 6.1...6.М и соответствующему включению накапливающего сумматора 3. 1 ил.

| Цифровой фильтр с симметричной импульсной характеристикой | 1987 |

|

SU1495979A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-02-28—Публикация

1990-03-21—Подача