Изобретение относится к вычислительной технике и может быть использовано в различных цифровых устройствах, работающих в условиях воздействия помех.

Известен регистр памяти (Гольденберг Л.М. Импульсные и цифровые устройства. Учебник для ВУЗов. М.: Связь, 1973, с. 448, рис. 10.3а), содержащий триггеры и две группы элементов И с количеством элементов в каждой группе, равным количеству триггеров. Первые входы первой группы элементов И соединены с соответствующими входными шинами, вторые входы объединены и соединены с шиной сигнала ввода информации, выходы соединены с входами установки соответствующих триггеров. Входы сброса триггеров объединены и соединены с шиной сброса, прямые выходы соединены с первыми входами соответствующих элементов И второй группы, вторые входы которых объединены и соединены с шиной сигнала вывода информации, а выходы соединены с соответствующими выходными шинами.

Недостатками данного регистра с параллельным вводом и выводом информации являются низкая помехоустойчивость и отсутствие возможности вывода информации в обратном (инверсном) коде.

Известен регистр памяти (Основы импульсной и цифровой техники. Учебное пособие для ВУЗов. М.: Сов. радио, 1975, с. 382, рис. 14.24), который является прототипом и содержит триггеры и две группы элементов И с количеством элементов в каждой группе, равным количеству триггеров. Первые входы первой группы элементов И соединены с соответствующими входными шинами, вторые входы объединены и соединены с шиной сигнала ввода информации, выходы соединены с входами установки соответствующих триггеров. Входы сброса триггеров объединены и соединены с шиной сброса, счетные входы соединены с шиной обращения кода, прямые выходы соединены с первыми входами соответствующих элементов И второй группы, вторые входы которых объединены и соединены с шиной сигнала вывода информации, выходы соединены с соответствующими выходными шинами.

Недостатками данного регистра памяти являются

низкая помехоустойчивость, определяемая помехоустойчивостью незащищенных триггеров;

относительная сложность управления им, обусловленная необходимостью лишнего такта управления для предварительной инверсии кода введенной информации при выводе информации в обратном коде.

Техническим результатом изобретения является повышение помехоустойчивости регистра памяти и сокращение времени вывода информации из него в обратном коде.

Технический результат достигается тем, что в регистр памяти, содержащий n триггеров, четыре шины управления, входные шины, выходные шины, первую группу n элементов И, первые входы которых соединены с соответствующими входными шинами, вторые входы объединены, вторую группу n элементов И, первые входы которых подключены к прямым выходам соответствующих триггеров, вторые входы соединены с первой шиной управления, введены третья и четвертая группы n элементов И, две группы элементов ИЛИ по n элементов в каждой, n RC-элементов и два элемента ИЛИ-НЕ, каждый из триггеров выполнен в виде тактируемого уровнем одноступенчатого D-триггера, первый входы элементов ИЛИ-НЕ соединены с второй шиной управления, второй вход первого элемента ИЛИ-НЕ соединен с третьей шиной управления, выход соединен с вторым входом второго элемента ИЛИ-НЕ, с первыми входами элементов И третьей группы и с тактовыми входами триггеров, выход второго элемента ИЛИ-НЕ соединен с вторыми входами элементов И первой группы, вторые входы элементов И третьей группы подключены к прямым выходам соответствующих триггеров, выходы одноименных элементов И первой и третьей групп соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ первой группы, выходы которых через соответствующие RC-элементы соединены с информационными входами соответствующих триггеров, инверсные выходы которых соединены с первыми входами соответствующих элементов И четвертой группы, вторые входы которых соединены с четвертой шиной управления, выходы одноименных элементов И второй и четвертой групп соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с соответствующими выходными шинами.

Указанная совокупность признаков позволяет повысить помехоустойчивость регистра памяти за счет порогового контроля длительности импульсов ввода и сброса на шинах управления и символов информации на входных шинах перед записью их в тактируемые уровнем D-триггеры регистра и позволяет сократить время вывода из регистра информации в обратном коде за счет исключения обязательного промежуточного этапа обращения (инверсии) ее кода.

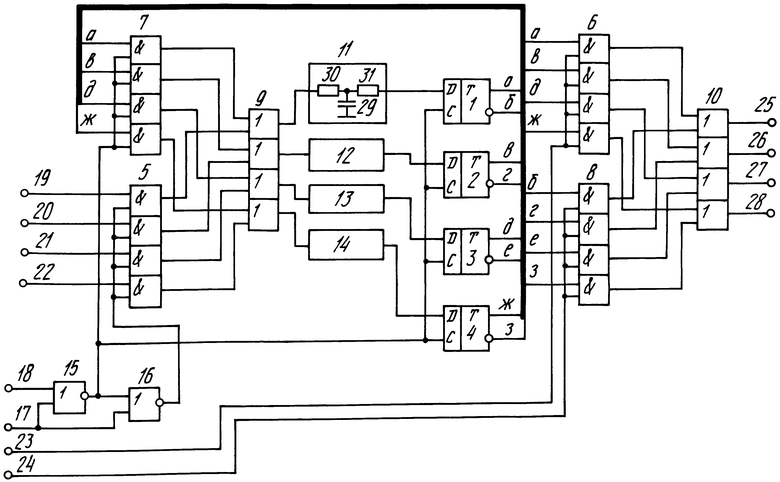

На чертеже приведена функциональная схема регистра памяти в четырехразрядном исполнении.

Регистр памяти содержит четыре D-триггера 1 - 4, первую 5, вторую 7 группы элементов И по четыре элемента в каждой, элементы И групп 6 и 8 и элементы ИЛИ группы 10 образуют коммутатор, группы элементов ИЛИ 9, 10 содержат по четыре элемента ИЛИ в каждой группе, RC-элементы 11 - 14, первый 15, второй 16 элементы ИЛИ-НЕ, первую 17, вторую 18, третью 19 и четвертую 20 шины управления, четыре входные шины 21-24 и выходные шины 25-28. Первые входы элементов ИЛИ-НЕ 15 и 16 соединены с первой 17 шиной управления. Второй вход элемента ИЛИ-НЕ 15 соединен с второй 18 шиной управления, выход соединен с вторым входом элемента ИЛИ-НЕ 16, с первым входами группы 7 элементов И и с тактовыми входами D-триггеров 1 - 4. Выход элемента ИЛИ-НЕ 16 соединен с вторыми входами группы 5 элементов И, первые входы которых соединены с входными шинами 19 - 22. Вторые входы группы 7 элементов И подключены к прямым выходам D-триггеров 1 - 4. Выходы одноименных И групп 5 и 7 соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ группы 9, выходы которых через RC-элементы 11 - 14 соединены с информационными входами D-триггеров 1-4 соответственно. Прямые выходы D-триггеров 1-4 соединены с первым входами соответствующих элементов И группы 6, вторые входы которых соединены с третьей 3 шиной 23 управления. Инверсные выходы D-триггеров 1 - 4 соединены с первыми входами соответствующих элементов И группы 8, вторые входы которых соединены с четвертой шиной 24 управления. Выходы одноименных элементов И групп 6 и 8 соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ группы 10, выходы которых соединены с выходными шинами 25-28.

D-триггеры 1 - 4 представляют собой тактируемые уровнем одноступенчатые D-триггеры, при этом информация в триггеры записывается высоким уровнем сигнала на их тактовых входах.

RC-элементы 11 - 14 выполнены по одинаковой схеме, показанной на чертеже, при этом требуемый уровень помехоустойчивости регистра памяти устанавливается выбором постоянной заряда (и разряда) конденсатора 29 RC-элементов через резистор 30. Резистор 31 указанных RC-элементов не является обязательным элементом последних: его наличие обязательно лишь при необходимости защиты информационных входов D-триггеров 1 - 4 по входному току (например, при выключении питания регистра памяти) в случаях реализации устройства на базе интегральных микросхем, изготовленных по КМОП-технологии. Информация в регистр памяти вводится в двоичном коде 8421 параллельно, каждый символ кода записывается в конденсатор 29 RC-элемента и в D-триггер соответствующего разряда. Каждый разряд регистра состоит из одинаковых функциональных элементов. Например, разряд регистра, связанный с входной шиной 19 и выходной шиной 25 (назовем его первым разрядом), содержит верхние элементы И групп 5, 7, 6 и 8, верхние элементы ИЛИ групп 9 и 10, RC-элемент 11 и D-триггер 1. Элементы ИЛИ-НЕ 15, 16 и шины 17, 18, 23 и 24 управления являются общими для всех разрядов. Символ старшего разряда кода вводимой в регистр информации может подаваться на входную шину 19 или 22, поскольку разряды регистра независимы между собой. Работает регистр памяти следующим образом.

В исходном состоянии на входных шинах 19-22 и шинах 17, 18, 23 и 24 управления присутствуют уровни логического "0", конденсаторы 29 RC-элементов 11 - 14 разряжены, D-триггеры 1 - 4 находятся в нулевом состоянии, поэтому на их прямых выходах - уровни логического "0", а на инверсных выходах - уровни логической "1". На выходе элемента ИЛИ-НЕ 15 - уровень логической "1", а на выходе элемента ИЛИ-НЕ 16 - уровень логического "0". Уровень логической "1", поступающий на первые входы элементов И группы 7, разрешает прохождение через эти элементы уровней логического "0", поступающих на вторые входы этих элементов с прямых выходов D-триггеров 1-4. Поскольку на первых и вторых входах элементов И группы 5 присутствуют уровни логического "0", то на выходах этих элементов - также уровни логического "0". В результате на обоих входах элементов ИЛИ группы 9 присутствуют уровни логического "0", поэтому на их выходах - также уровни логического "0", которые поддерживают разряженное состояние конденсаторов 29 RC-элементов 11-14. Присутствие на вторых входах элементов И групп 6 и 8 уровня логического "0" обеспечивает поддержание уровней логического "0" на выходах этих элементов и на выходах элементов ИЛИ группы 10, то есть на выходных шинах 25-28.

В указанное исходное состояние регистр памяти самостоятельно устанавливается при включении питания, и происходит это следующим образом.

В выключенном состоянии регистра памяти конденсаторы 29 RC-элементов 11-14 разряжены. При включении питания на входных шинах 19-22 и на шинах 17, 18, 23 и 24 управления сигналов пока нет (уровни логического "0"), поэтому на выходе элемента ИЛИ-НЕ 15 устанавливается уровень логической "1", а на выходе элемента ИЛИ-НЕ 16 - уровень логического "0". Уровнем логической "1", поступающим с выхода элемента ИЛИ-НЕ 15 на тактовые входы D-триггеров 1-4, последние устанавливаются в нулевое состояние, на их прямых выходах устанавливаются уровни логического "0", которые поступают на вторые входы элементов И группы 7 и проходят через них на вторые входы элементов ИЛИ группы 9. На первых входах этих элементов ИЛИ также присутствуют уровни логического "0" (поскольку на обоих входах элементов И группы 5 присутствуют уровни логического "0"), поэтому на их выходах также устанавливаются уровни логического "0", чем поддерживается разряженное состояние конденсаторов 29 RC-элементов 11-14. Наличие уровней логического "0" на шинах 23 и 24 управления обеспечивает уровни логического "0" на выходах элементов И групп 6, 8 и элементов ИЛИ группы 10.

В указанное исходное состояние регистр памяти может быть установлен также путем подачи по шине 17 управления импульсного сигнала с уровнем логической "1" (сигнал сброса) при произвольных состояниях D-триггеров 1-4, конденсаторов 29 RC-элементов 11-14 и уровней сигналов на входных шинах 19-22 и остальных шинах управления. При этом в течение указанного сигнала сброса на выходах элементов ИЛИ-НЕ 15 и 16 поддерживается уровень логического "0", чем поддерживается уровень логического "0" на выходах элементов И групп 5, 7 и элементов ИЛИ группы 9, и разряжаются (если они были до этого заряжены) конденсаторы 29 RC-элементов 11-14. Постоянная разряда (и заряда) конденсаторов 29 RC-элементов 11-14 выбирается с учетом требуемого уровня помехоустойчивости регистра памяти таким образом, чтобы в течение сигнала сброса (или сигнала ввода информации, подаваемого по шине 18 управления) конденсаторы указанных RC-элементов успели разрядиться до уровня логического "0" (или зарядиться до уровня логической "1"). После окончания сигнала сброса на выходе элемента ИЛИ-НЕ 15 восстанавливается исходный уровень логической "1", а на выходе элемента ИЛИ-НЕ 16 уровень логического "0" сохраняется. Это приводит к тому, что на первые элементы И группы 7 поступает "разрешение", на вторых входах элементов И группы 5 сохраняется запрет. Уровнем логической "1", поступающим на тактовые входы D-триггеров 1-4, последние переключаются в нулевое состояние, то есть в состояние, соответствующее состояниям конденсаторов 29 RC-элементов 11-14, которые последние приняли в течение сигнала сброса. Уровни логического "0" с прямых выходов D-тригггеров 1-4, проходя через вторые входы элементов И группы 7 на их выходы и далее на выходы элементов ИЛИ 9, поступают на входы RC-элементов 11-14 и поддерживают их разряженное состояние.

Рассмотрим теперь работу регистра памяти в режимах ввода и вывода информации на примере двоичного кода числа 5-0101 (здесь и далее в тексте старшие разряды кодов - слева), предполагая, что старший разряд кода подается по выходной шине 22.

Для ввода в регистр памяти информации ее код предварительно подается на входные шины 19-22, затем по шине 18 управления подается импульсный сигнал ввода с уровнем логической "1". При подаче сигнала ввода на выходе элемента ИЛИ-НЕ 15 появляется уровень логического "0", а на выходе элемента ИЛИ-НЕ 16 - уровень логической "1". Такая комбинация сигналов на выходах элементов ИЛИ-НЕ 15 и 16 приводит к тому, что D-триггеры 1-4 становятся нечувствительными к уровням сигналов на своих информационных входах и сохраняют свое нулевое состояние, элементы И группы 7 "закрываются" по первым входам, и на их выходах поддерживаются уровни логического "0". Одновременно "открываются" элементы И группы 5, на их выходы и далее на выходы элементов ИЛИ группы 9 и на выходе RC-элементов 11-14 проходят символы кода, установленного на входных шинах 19-22. В рассматриваемом случае на входы RC-элементов 11-14 поступает код 0101, при этом символ старшего разряда вводимого кода поступает на вход RC-элемента 14. Следовательно, начинается заряд конденсаторов 29 RC-элементов 11 и 13, а конденсаторы RC-элементов 12 и 14 сохраняют свое разряженное состояние. До окончания сигнала ввода конденсаторы 29 RC-элементов 11 и 13 успевают зарядиться до уровня логической "1", то есть вводимый код "запоминается" конденсаторами 29 RC-элементов 11 - 14. После окончания сигнала ввода на выходе элемента ИЛИ-НЕ 15 восстанавливается исходный уровень логической "1", на выходе элемента ИЛИ-НЕ 16 - уровень логического "0". Это приводит к тому, что элементы И группы 5 "закрываются", элементы И группы 7 "открываются", а в D-триггеры 1-4 записывается запомненная в течение сигнала ввода конденсаторами 29 RC-элементов 11-14 информация. Эта информация с прямых выходов D-триггеров 1-4 поступает на вторые входы "открытых" элементов И группы 7 и, проходя через них и элементы ИЛИ группы 9, поступает на входы RC-элементов, поддерживая тем самым состояния конденсаторов, которые последние приняли в течение сигнала ввода информации. В рассматриваемом случае будут поддерживаться заряженное состояние конденсаторов 29 RC-элементов 11 и 13 и разряженное состояние конденсаторов 29 RC-элементов 12 и 14.

Если длительность сигнала ввода на шине 18 управления или сигнала сброса на шине 17 управления окажется короче требуемой из-за воздействия помех на эти шины или же при поступлении по этим шинам помех, то конденсаторы 29 RC-элементов 11-14 не успевают перезарядиться в течение этих коротких сигналов, и после их окончания D-тригерры 1-4 сохраняют свои состояния, которые они имели перед поступлением указанных коротких сигналов (помех), то есть регистр памяти сохраняет свое состояние. Аналогично регистр памяти сохраняет свое состояние при поступлении помех по входным шинам 19-22 в течение сигналов ввода информации и сброса по шинам 23 и 24 управления.

Состояние D-триггеров 1-4, в которых хранится код введенной в регистр памяти информации, поступает с разных плеч этих D-триггеров на первые входы элементов И групп 6 и 8. При этом прямой код введенной информации поступает на входы элементов И группы 6, обратный код - на входы элементов И группы 8, которые при необходимости могут быть выведены из регистра памяти на выходные шины 25 - 28 путем подачи соответствующей комбинации сигналов на шины 23 и 34 управления. Например, при выводе информации в прямом коде на шине 24 управления поддерживается уровень логического "0", а на шину 23 управления подается сигнал вывода (импульсный или постоянный) с уровнем логической "1". При этом на выходах элементов И группы 8 и на вторых входах элементов ИЛИ группы 10 поддерживаются уровни логического "0", а на выходы элементов И группы 6 и на первые входы элементов ИЛИ группы 10 проходят символы разрядов прямого кода хранящейся в D-триггерах 1-4 информации. Проходя через элементы ИЛИ группы 10, прямой код указанной информации поступает на выходные шины 25-28.

Для вывода хранящейся в регистре памяти информации в обратном коде необходимо на шине 23 управления поддерживать уровень логического "0", а на шину 24 управления подать сигнал вывода (импульсный или постоянный) с уровнем логической "1". При этом элементы регистра, участвующие в выводе информации, работают аналогично предыдущему случаю, и на выходные шины 25-28 выдается обратный код хранящейся в регистре информации.

Таким образом, информация в регистр памяти вводится, и он сбрасывается в нулевое состояние только в случае, если длительность сигналов на шинах 17 и 18 управления и входных шинах 19-22 превышает заданное значение. Введенная в регистр памяти информация запоминается тактируемым уровнем D-триггерами 1-4 и конденсаторами 29 RC-элементов, и состояния этих конденсаторов после окончания сигналов на шинах 17 и 18 управления поддерживаются по цепям обратной связи: прямые выходы D-триггеров - вторые входы и выходы элементов И группы 7 - входы и выходы элементов ИЛИ группы 9 - входы RC-элементов 11-14. Сокращено время вывода из регистра памяти информации в обратном коде. Информация из регистра выводится как в прямом коде, так и в обратном коде за один такт подачей комбинации сигналов по двум цепям управления.

В целях подтверждения осуществимости предлагаемого объекта и достигнутого технического результата в институте был изготовлен и испытан в нормальных условиях и в диапазоне температур окружающей среды от - 50 до 50oC лабораторный макет, выполненный по схеме, приведенной на чертеже, на базе микросхем серии 564 и дискретных конденсаторов и резисторов. Проведенные испытания показали осуществимость предлагаемого помехоустойчивого регистра памяти и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕГИСТР СДВИГА | 1993 |

|

RU2110099C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1992 |

|

RU2022463C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1990 |

|

RU2036556C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2110146C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2042268C1 |

| ДВОИЧНЫЙ СЧЕТЧИК | 1990 |

|

RU2040855C1 |

| ЯЧЕЙКА ПАМЯТИ | 2001 |

|

RU2214037C2 |

Изобретение относится к вычислительной технике и может быть использовано в различных цифровых устройствах, работающих в условиях воздействия помех. Достигаемый технический результат - повышение помехоустойчивости и сокращение времени вывода информации в обратном коде. Регистр памяти содержит D-триггеры 1 - 4, группы 5, 7 элементов И, шины 17 - 20 управления, входные шины 21 - 24 и выходные шины 25 - 28. Технический результат достигнут введением коммутатора, построенного на элементах И 6, 8 групп и группы элементов ИЛИ 10, а также группы элементов ИЛИ 9, RC - элементов 11 - 14, элементов ИЛИ - НЕ 15, 16 новых функциональных связей между элементами и выполнением D-триггеров в виде тактируемых уровнем D-триггеров. 1 ил.

Регистр памяти, содержащий n триггеров, коммутатор, первую группу n элементов И, первые входы которых соединены с соответствующими входными шинами регистра, вторые входы элементов И первый группы объединены, выходы коммутатора соединены с соответствующими выходными шинами регистра, первые и вторые информационные входы коммутатора соединены соответственно с прямыми и инверсными выходами соответствующих триггеров, первый и второй управляющие входы коммутатора соединены соответственно с первой и второй управляющими шинами регистра, отличающийся тем, что в него введены вторая группа n элементов И, n RC-элементов, два элемента ИЛИ - НЕ, группа элементов ИЛИ и каждый триггер выполнен в виде одноступенчатого D-триггера, первые входы элементов ИЛИ - НЕ соединены с третьей шиной управления регистра, второй вход первого элемента ИЛИ - НЕ соединен с четвертой шиной управления регистра, выход первого элемента ИЛИ - НЕ соединен с вторым входом второго элемента ИЛИ - НЕ, с первыми входами элементов И второй группы и с тактовыми входами триггеров, выход второго элемента ИЛИ - НЕ соединен с объединенными вторыми входами элементов И первой группы, выходы элементов И первой и второй групп соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ группы, выходы которых через соответствующие RC-элементы соединены с информационными входами соответствующих триггеров, прямые выходы которых соединены с вторыми входами соответствующих элементов И второй группы.

| Горбунов В.Л | |||

| и др | |||

| Справочное пособие по микропроцессорам и микроЭВМ | |||

| - М.: Высшая школа, 1988, с.30, рис.2.7. |

Авторы

Даты

1998-03-10—Публикация

1993-11-02—Подача