Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и системах управления.

Целью изобретения является обеспечение полноты контроля счетчика импульсов.

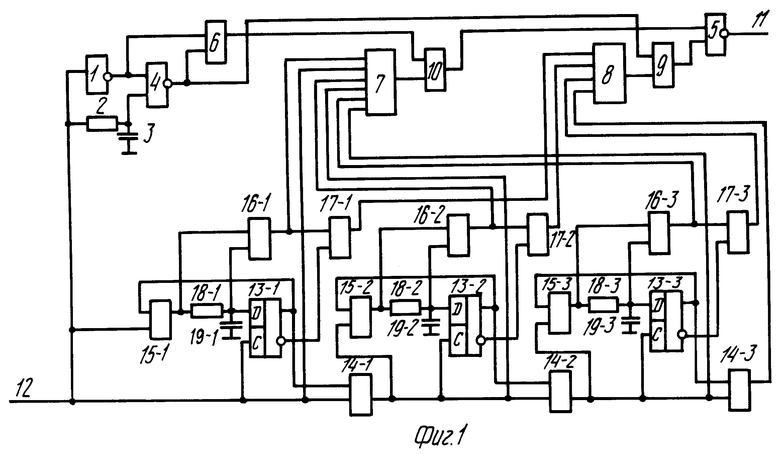

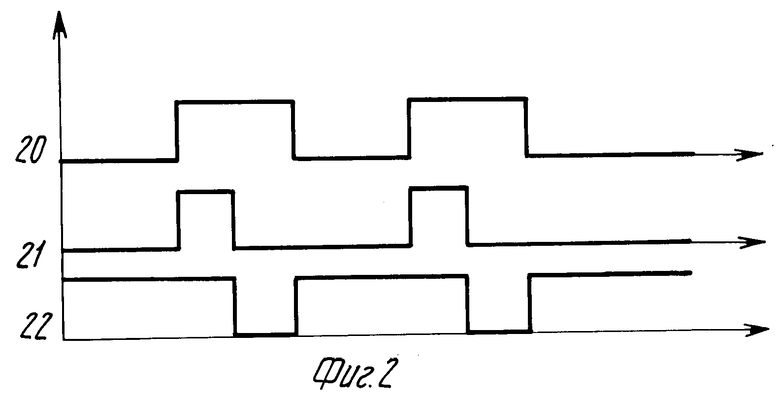

На фиг. 1 приведена схема двоичного счетчика (трехразрядного); на фиг. 2 временные диаграммы работы счетчика.

Двоичный счетчик содержит элемент НЕ 1, интегрирующую RC-цепь, состоящую из резистора 2 и конденсатора 3, первый 4 и второй 5 элементы ИЛИ-НЕ, элемент Исключающее ИЛИ 6, шестивходовую схему 7 четности, четырехвходовую схему 8 нечетности, элемент И 9 и дополнительный элемент И 10, шину 11 анализа результатов контроля, шину 12 входных импульсов и в каждом разряде триггер 13-1 (13-2, 13-3), первый 14-1 (14-2, 14-3) и второй 17-1 (17-2, 17-3) элементы И, первый 15-1 (15-2, 15-3) и второй 16-1 (16-2, 16-3) элементы Исключающее ИЛИ и интегрирующую RC-цепь, состоящую из резистора 18-1 (18-2, 18-3) и конденсатора 19-1 (19-2, 19-3). Триггеры 13-1, 13-2, 13-3 выполнены каждый в виде тактируемого D-триггера.

В каждом разряде счетчика первый и второй входы элемента И 14-1 (14-2, 14-3) соединены соответственно с прямым выходом и тактовым входом триггера 13-1 (13-2, 13-3), прямой выход которого подключен к первому входу элемента Исключающее ИЛИ 15-1 (15-2,15-3), второй вход которого объединен с тактовым входом триггера 13-1 (13-2, 13-3) и с соответствующим входом схемы 7 четности, а выход подключен к одному из входов второго элемента Исключающее ИЛИ 16-1 (16-2, 16-3) и к первому выводы резистора 18-1 (18-2, 18-3), второй вывод которого соединен с D-входом триггера 13-1 (13-2, 13-3), другим входом элемента Исключающее ИЛИ 16-1 (16-2, 16-3) и с первым выводом конденсатора 19-1 (19-2, 19-3), второй вывод которого подключен к общей шине. Выход элемента Исключающее ИЛИ 16-1 (16-2, 16-3) подключен к соответствующему входу схемы 7 четности и к одному из входов элемента И 17-1 (17-2, 17-3), другой вход которого соединен с инверсным выходом триггера 13-1 (13-2, 13-3), а выход подключен к соответствующему входу схемы 8 нечетности. Четвертый вход схемы 8 нечетности подключен к выходу элемента И 14-3, а выход соединен с первым входом элемента И 9. Входная шина 12 подключена к входу элемента НЕ 1 и к первому выводу резистора 2, второй вывод которого соединен с первым выводом конденсатора 3, второй вывод которого подключен к общей шине. Выход элемента НЕ 1 и второй вывод резистора 2 соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ 4, первый вход и выход которого подключены соответственно к первому и второму входам элемента Исключающее ИЛИ 6, выход и второй вход которого соединены соответственно с первым входом элемента И 10 и вторым входом элемента И 9, выход которого соединен с первым входом элемента ИЛИ-НЕ 5, выход которого подключен к шине 11 анализа результатов контроля, а второй вход соединен с выходом элемента И 10, второй вход которого соединен с выходом схемы 7 четности. Выходы элементов И 14-1, 14-2 соединены со вторыми входами соответственно элементов И 14-2, 14-3. Тактовый вход триггера 13-1 подключен к входной шине 12.

Постоянная времени RC-цепей в составе триггерных устройств (элементы 13, 15, 18, 19) счетчика выбирается, исходя из необходимой помехоустойчивости. Чем больше постоянная времени, тем большей длительности помеха допускается на шине 12 входных импульсов счетчика. Постоянная времени RC-цепи резистора 2 и конденсатора 3 должна быть меньше постоянной времени любой из RC-цепей в разрядах счетчика.

Двоичный счетчик работает следующим образом.

Допустим, что триггеры 13-1, 13-2, 13-3 счетчика находятся в нулевом состоянии, на шине 12 уровень логического "0". Триггер 13-1 (13-2, 13-3) тактируется уровнем логического "0" и с его прямого выхода логический уровень через кольцо обратной связи, состоящее из элемента Исключающее ИЛИ 15-1 (15-2, 15-3) и резистора 18-1 (18-2, 18-3), передается на D-вход триггера 13-1 (13-2, 13-3). Конденсатор 19-1 (19-2, 19-3) разряжен.

При поступлении первого импульса положительной полярности на шину 12 триггер 13-1 сохранит свое состояние, на выходе элемента Исключающее ИЛИ 15-1 появляется уровень логической "1" и конденсатор 19-1 заряжается через резистор 18-1. Так как триггер 13-1 находится в нулевом состоянии, на выходе элемента И 14-1 (14-2, 14-3) также уровень логического "0", и импульс на шине 12 не проходит на тактовые входы триггеров 13-2, 13-3. По окончании импульса на шине 12 триггер 13-1 переключится в единичное состояние уровнем логического нуля на его тактовом входе, и на выходе элемента Исключающее ИЛИ 15-1 сохранится уровень логической "1". Конденсатор 19-1 заряжен и удерживает триггер 13-1 в единичном состоянии.

Второй импульс на шине 12 поступает на тактовый вход триггера 13-1 и через элемент И 14-1 на тактовый вход триггера 13-2. На выходах элементов Исключающее ИЛИ 15-1 и 15-2 появляется соответственно уровень логического "0" и уровень логической "1". Конденсатор 19-1 разряжается через резистор 18-1, а конденсатор 19-2 заряжается через резистор 18-2. По окончании импульса на шине 12 триггер 13-1 переключится в нулевое состояние, а триггер 13-2 в единичное.

Аналогичным образом переключается и триггер 13-3, когда на его тактовый вход проходит импульс с шины 12 через элементы И 14-1, 14-2. Счетчик работает в двоичном позиционном коде.

При появлении импульса на шине 12 в переключающемся разряде на выходе элемента Исключающее ИЛИ 15-1 (15-2,15-3) изменяется уровень логического сигнала на противоположный. Конденсатор в этом разряде перезаряжается, и на выходе элемента Исключающее ИЛИ 16-1 (16-2, 16-3) формируется импульс, длительность которого определяется постоянной времени RC-цепи соответствующего разряда.

При нормальной работе переключаться должен только тот триггер, на тактовый вход которого поступает импульс, поэтому на входе схемы 7 контроля четности будет четное количество логических единиц, а на выходе уровень логического "0". При поступлении на шину 12 счетного импульса только в одном разряде счетчика триггер переключается в единичное состояние, а при переполнении счетчика триггер 13-3 последнего разряда переходит в нулевое состояние. Поэтому на выходе только одного из элементов И (17-1, 17-2, 17-3), 14-3 появляется уровень логической "1". При этом на выходе схемы 8 нечетности будет появляться логический "0".

По переднему фронту импульса на входной шине 12 (фиг. 2, 20) с помощью элементов НЕ 1 и ИЛИ-НЕ 4 формируется импульс опроса (фиг. 2, 21), который поступает на элемент И 9 и длительность которого определяется постоянной времени RC-цепи, состоящей из резистора 2 и конденсатора 3. Во время отсутствия импульса на входной шине 12 и на время действия импульса опроса на выходе элемента И 4 на выходе элемента Исключающее ИЛИ 6 присутствует уровень логической "1" (фиг. 2, 22), который поступает на вход элемента И 10. Сбой в работе счетчика приведет к формированию на выходе схемы 7 четности и (или) схемы 8 нечетности уровня логической "1", который, пройдя через элемент И 10 и (или) элемент И 9, поступает на вход элемента ИЛИ-НЕ 5, формируя на его выходе и, соответственно, на шине 11 анализа результатов контроля импульс отрицательной полярности, свидетельствующей о неисправности. Таким образом, заявляемый объект обеспечивает полноту контроля счетчика импульсов путем формирования сигнала неисправности при несанкционированном переключении помехоустойчивого триггера любого разряда.

(56) 1. Авторское свидетельство СССР N 1121781, кл. Н 03 К 21/34, 1983.

2. Ф. Селлерс Методы обнаружения ошибок в работе ЭЦВМ. М. Мир, 1972, c. 200, рис. 11-1.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1990 |

|

RU2036556C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1993 |

|

RU2040111C1 |

| СЧЕТЧИК ИМПУЛЬСОВ, СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1991 |

|

RU2047271C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2110146C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036555C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2042268C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1991 |

|

RU2036550C1 |

Изобретение относится к импульсной технике и обеспечивает контроль помехоустойчивого счетчика. Двоичный счетчик содержит элемент НЕ, интегрирующую RC-цепь, состоящую из резистора и конденсатора, два элемента ИЛИ-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, шестивходовую схему проверки четности, четырехвходовую схему проверки нечетности, два элемента И, шину анализа результатов контроля, шину входных импульсов и в каждом разряде триггер, два элемента И, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и интегрирующую RC-цепь, состоящую из резистора и конденсатора. Триггер в каждом разряде выполнен в виде тактируемого D-триггера. 2 ил.

ДВОИЧНЫЙ СЧЕТЧИК, имеющий n разрядов и содержащий n-входовую схему проверки нечетности, элемент И, шину счетных импульсов, в каждом разряде триггер и в каждом разряде, кроме последнего, первый и второй элементы И, при этом в каждом разряде, кроме последнего, тактовый вход и прямой выход триггера соединены соответственно с первым и вторым входами первого элемента И, а выход второго элемента И соединен с соответствующим входом схемы нечетности, выход которой подключен к первому входу элемента И, в каждом разряде, начиная с второго, тактовый вход триггера соединен с выходом первого элемента И предыдущего разряда, тактовый вход триггера первого разряда подключен к шине счетных импульсов, отличающийся тем, что, с целью обеспечения полноты контроля счетчика, в него введены элемент НЕ, интегрирующая RC-цепь, два элемента ИЛИ-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, 2n-входовая схема четности, дополнительный элемент И и шина анализа результатов контроля, в каждый разряд первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и интегрирующая RC-цепь, в последний разряд - первый и второй элементы И, в схему нечетности дополнительный вход, а триггеры выполнены в виде тактируемых D-триггеров, причем в каждом разряде прямой выход D-триггера подключен к первому входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого объединен с тактовым входом D-триггера и соответствующим входом схемы четности, а выход поключен к одному из входов второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к входу интегрирующей RC-цепи данного разряда, выход которой соединен с D-входом триггера и другим входом второго элемента, выход которого подключен к соответствующему входу схемы четности и к одному из входов второго элемента и, другой вход которого соединен с инверсным выходом D-триггера, в последнем разряде первый и второй входы первого элемента И соединены соответственно с тактовым входом и прямым выходом триггера, а первый вход первого элемента И с выходом первого элемента И предпоследнего разряда, выход первого элемента И последнего разряда соединен с соответствующим входом схемы нечетности, дополнительный вход которой подключен к выходу второго элемента И этого разряда, а выход к второму входу элемента И, шина счетных импульсов подключена к входам элемента НЕ и интегрирующей RC-цепи устройства, выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ-НЕ, первый вход и выход которого подключены соответственно к первому и второму входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход и второй вход которого соединены соответственно с первым входом дополнительного элемента И и вторым входом элемента И, выход которого соединен с первым входом второго элемента ИЛИ-НЕ, выход которого подключен к шине анализа результатов контроля, а второй вход к выходу дополнительного элемента И, второй вход которого соединен с выходом схемы четности.

| Селлерс Ф | |||

| методы обнаружения ошибок в работе ЭЦВМ | |||

| М.: Мир, 1972, с | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-07-25—Публикация

1990-10-05—Подача