Предлагаемое изобретение относится к области автоматики и вычислительной техники и может быть использовано для долговременного хранения и многократного оперативного обновления пакетов цифровой информации.

Известны накопители цифровой информации на магнитной ленте [1], содержащие лентопротяжный механизм, блок магнитных головок, блок записи, формирователи импульсов воспроизведения, генератор импульсов, счетчик импульсов, элементы И, ИЛИ.

Недостатком известных накопителей является их сложность, большие габариты и вес, восприимчивость к механическим перегрузкам и температуре окружающей среды, а также низкий ресурс работы, вызванные наличием электромеханических элементов (лентопротяжный механизм и блок магнитных головок).

Наиболее близким техническим решением к данному изобретению является накопитель цифровой информации [2], содержащий первый регистр, входы которого соединены с шиной входной информации, второй регистр, выходы которого через дешифратор подключены к первой группе входов блока оперативной памяти, третий и четвертый регистры, блок управления, а также первый и второй блоки сравнения, первый и второй коммутаторы, первый и второй блоки усилителей, триггер, формирователь, дополнительный блок адреса, второй дешифратор с соответствующими связями.

Такой накопитель не обеспечивает замену накопителя на магнитной ленте (НМЛ) с сохранением всей инфраструктуры обслуживания НМЛ и циклограммы его работы в комплексной системе. Кроме того, при отключении питания информация в таком накопителе стирается. Однако с появлением энергонезависимых элементов статической оперативной памяти (например, СОЗУ DS 1270 Y /АВ фирмы Dallas Semiconductor США), сохраняющих оперативно записанную информацию после отключения источников питания, стало возможным их использование для долговременного хранения и оперативного обновления пакетов цифровой информации.

При этом использование НМЛ становится нецелесообразным вследствие их сложности и низких эксплуатационных показателей.

Таким образом, необходим накопитель на элементах статической оперативной памяти с сохранением инфраструктуры НМЛ и циклограммы его работы в комплексной системе, что обеспечит взаимозаменяемость различных типов накопителей.

Для этого в накопитель цифровой информации, содержащий первый регистр, информационные входы которого соединены с шиной входной информации, второй регистр, первая группа выходов которого через дешифратор подключена к первой группе входов блока оперативной памяти, третий и четвертый регистры, блок управления, введены микроконтроллер, блок постоянной памяти, счетчик, магистральный приемопередатчик, блок коррекции, блок формирователей сигналов, открывающих выходы выбранных элементов блока оперативной памяти на вторую магистральную шину, пятый регистр, первая и вторая магистральные шины, информационные входы второго регистра соединены с первой группой выходов микроконтроллера, а вторая группа выходов второго регистра подключена к первой группе входов блока постоянной, памяти, выходы которого, информационные входы третьего регистра, вторая группа выводов микроконтроллера и первая группа выводов магистрального приемопередатчика подключены к первой магистральной шине, третья группа выходов микроконтроллера подключена к первой группе входов блока управления, выходы третьего регистра подключены к вторым группам входов блока постоянной памяти и блока управления, информационные входы четвертого регистра являются командными входами накопителя, выходы первого, четвертого регистров и блока коррекции, информационные входы пятого регистра, блока коррекции и счетчика, вторые группы выводов магистрального приемопередатчика и блока оперативной памяти подключены к второй магистральной шине, выходы счетчика подключены и третьей группе входов блока оперативной памяти, входы блока формирователей соединены с выходами дешифратора, а выходы подключены к четвертой группе входов блока оперативной памяти, ввод блока управления является тактовым входом накопителя, первая группа выходов блока управления подключена к группе входов микроконтроллера, выходы второй группы выходов блока управления подключены к соответствующим управляющим входам регистров с первого по пятый, дешифратора, блока постоянной памяти, счетчика, магистрального приемопередатчика и блока коррекции, первый выход блока управления подключен к входам блока формирователей и блока оперативной памяти, второй выход - к тактовому входу счетчика, третий выход - к второму управляющему входу пятого регистpa и является первым выходом накопителя, четвертый выход является вторим выходом накопителя, а выходы пятого регистра являются группой информационных выходов накопителя.

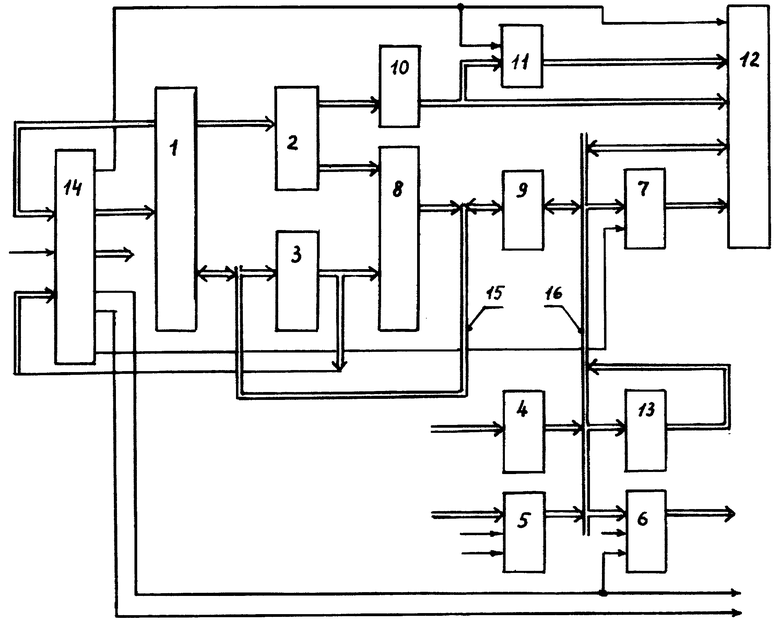

Структурная схема накопителя представлена на чертеже.

Накопитель содержит микроконтроллер 1, регистры с 2-го по 6-ой, счетчик 7 импульсов, блок 8 достоянной памяти, магистральный приемопередатчик 9, дешифратор 10, блок 11 формирователей, блок 12 оперативной памяти, блок 13 коррекции, блок 14 управления, первую 15 и вторую 16 магистральные шины.

Блок 12 состоит из нескольких корпусов энергонезависимой оперативной памяти. Подключение одного из корпусов осуществляется дешифратором 10, на вход которого поступают старшие разряды адреса. Дешифратор 10 формирует на одном из своих выходов строб-импульсы разрешения записи (чтения) для блока 12 и управляющие импульсы для включения одного из формирователей блока 11 (см., например, Применение интегральных микросхем в электронной технике. Справочник под ред. Б.Н. Файзулаева, Радио и связь, 1987, c.85, рис.4.24). Младшие разряды кода адреса блока 12 формируются счетчиком 7. В блоке 8 записывается программа работы микроконтроллера 1 и таблица коррекции информации при обнаружении ошибочного бита. Блок 13 предназначен для формирования корректирующих разрядов (например, кода Хемминга, см. У. Титце и др. Полупроводниковая электроника, М.: Мир, 1983, с.436, pис.23.8) при записи информации и признаков наличия ошибок при чтении. Магистральный приемопередатчик 9 является двунаправленным и предназначен для разгрузки магистральных шин 15 и 16. Блок 14 совместно с микропроцессором 1 вырабатывает последовательность управляющих сигналов для всех блоков накопителя (тактовые импульсы приема информации, например, в регистры, счетчик, разрешения выдачи информации в магистральные шины и т.д.). Блок 14 содержит генератор импульсов с делителем частоты, а для формирования управляющих импульсов могут быть использованы логические элементы или блок постоянной памяти. Циклограмма работы блока 14 не является жесткой и может меняться в зависимости от решаемой накопителем задачи и поэтому в материалах заявки не представлена. Блок 14 вырабатывает на первом выходе команду записи-чтения для блока 12, на втором выходе счетный импульс для счетчика 7, на третьем и четвертом выходах импульсы признаков выходной информации накопителя (синхроимпульсы СИ и импульсы признака адреса ПA), на первой группе выходов управляющие сигналы микроконтроллера 1, на второй группе выходов управляющие сигналы остальных блоков накопителя (на чертеже эти связи не обозначены).

Запись и чтение информации в блоке 12 производится пакетами позонно. В каждой зоне записывается определенное количество байтов. Каждые байт записывается по своему адресу. Младшие разряды кода адреса определяют адрес байта в зоне, а старшие разряды - номер зоны. Номер каждой подключаемой зоны запоминается в блоке 12 по определенному, заранее установленному адресу. По окончании работы с накопителем в блоке 12 будет храниться номер последней рабочей зоны. При следующем включении работа накопителя начинается с чтения информации из блока 12 по этому адресу, т.е. определяется номер последней рабочей зоны предыдущего включения и заносится в микроконтроллер 1. Адрес зоны устанавливается в старших разрядах счетчика 7 и информационных входах дешифратора 10. В младших разрядах счетчика 7 устанавливается начальный адрес первого байта информации в зоне. Номер зоны фиксируется в регистре 6 и выдается на выходные шины накопителя в сопровождении импульсов СИ и ПА.

Работа накопителя осуществляется по внешним командам, поступающим на информационные входы регистра 4. Микроконтроллер 1 циклически опрашивает состояние регистра 4. При поступлении в регистр 4 команды ДП (движение право) в микроконтроллере 1 с определенной периодичностью увеличивается на 1 номер зоны. Значение номера зоны через приемопередатчик 9 записывается в регистр 6 и в блоке 14 формируются одновременно импульсы СИ и ПА. По импульсам СИ открываются выходы регистра 6 и информация номера зоны в сопровождении СИ и ПА поступает на входы накопителя. Синхронно с изменением номера зоны в микроконтроллере 1 изменяется адрес зоны в счетчике 7 и информационных входах дешифратора 10.

Команда Зп (запись информации) поступает в регистр 4 через интервал τ1 после выдачи из регистра 6 номера зоны. Блок 14 вырабатывает на первом выходе сигнал записи для блока 12. Информация, подлежащая записи, побайтно поступает на входы регистра 5, а сопровождающие ее тактовые импульсы ТИ поступают в блок 14. ТИ, задержанные в блоке 14, фиксируют входную информацию в регистре 5. По каждому ТИ микроконтроллер 1 принимает из регистра 5 входной байт информации, в блоке 13 формируются контрольные разряды, на одном из выходов дешифратора 10 вырабатывается строй записи. Байт информации, а также контрольные разряды байта записываются в выбранные дешифратором 10 элементы блока 12 по соответствующему адресу счетчика 7, после чего код счетчика 7 и число записанных строк в микроконтроллере 1 увеличиваются на 1. После записи определенного количества байтов информации микроконтроллер 1 вырабатывает команду окончания записи в зоне и в блоке 14 формируется сигнал, снимающий в регистре 4 команду Зп. При сохранении в регистре 4 команды ДП в микроконтроллере 1 с той же периодичностью продолжается увеличение на 1 номера зоны, который запоминается в блоке 12 и выдается на выходе регистра 6 в сопровождении СИ и ПА, а адрес новой зоны формируется в старших разрядах счетчика 7 и на входах дешифратора 10. По снятию в регистре 4 команды ДП процесс изменения номеров зон прекращается.

Команда Чт (чтение информации) поступает в регистр 4 при наличии в нем команды ДП через интервал τ2 после выдачи из регистра 6 номера прочитанной зоны в сопровождении импульсов СИ и ПА. Блок 14 по сигналу микроконтроллера 1 вырабатывает на первом выходе сигнал чтения для блока 12 и сигнал разрешения формирования выходных сигналов для блока 11. Через τ3 после команды Чт в блоке 14 вырабатывается последовательность импульсов генератора ГИ. Синхронно с импульсами ГИ дешифратор 10 на одном из своих выходов в соответствии с выходным кодом регистра 2 вырабатывает строб-импульсы чтения информации для одного из элементов памяти блока 12. Одновременно на одном из выходов блока 11 вырабатывается сигнал, по которому открываются выходы выбранного элемента блока 12 на магистральную шину 16. По каждому ГИ микроконтроллер 1 принимает из блока 12 считанный байт информации, а также контрольные разряды этого байта, по адресу, заданному кодом счетчика 7. Из информационных и контрольных разрядов в блоке 13 формируется код дефектности считанного байта информации. По коду дефектности в блоке 8 формируется корректирующий код, который в микроконтроллере 1 суммируется со считанным кодом байта. Выходной скорректированный код фиксируется в регистре 6. По импульсу СИ, сформированному блоком 14, открываются выводы регистра 6 и байт информации в сопровождении СИ поступает на выход накопителя. По каждому СИ код счетчика 7 и число считанных строк в микроконтроллере 1 увеличивается на 1. После считывания определенного количества байтов, равного числу записанных байтов информации в зоне, в блоке 14 вырабатывается сигнал, снимающий в регистре 4 команду Чт. При сохранении в регистре 4 команды ДП в накопителе продолжаются процессы увеличения номеров зон и их запоминание в блоке 12 аналогично режиму записи. По снятию в регистре 4 команды ДП процесс изменения номеров зон и адресов прекращается.

При поступлении в регистр 4 команды ДЛ (движение лево) в микроконтроллере 1 с той же периодичностью, как и при команде ДП, происходит уменьшение на 1 номера зоны. Информация номера зоны записывается в регистр 6 и в сопровождении импульсов СИ и ПА поступает на выход накопителя. При наличии команды ДЛ выполнение команд Зп и Чт блокируется. По снятию в регистре 4 команды ДЛ процесс изменения номеров зон прекращается.

Таким образом, в предложенном накопителе цифровой информации используются те же команды и циклограмма диалога с центральным процессором в комплексной системе, как и в накопителе на магнитной ленте, что обеспечивает их взаимозаменяемость. Высокие эксплуатационные характеристики (габариты, вес, объем информации, ресурс работы, восприимчивость к механическим перегрузкам) и стоимость производства создает значительные преимущества предложенного накопителя по сравнению с НМЛ.

Источники информации

1. Патент РФ № 1010648, кл. G 11 B 5/008, 26.10.81 г.

2. Патент РФ № 2058603, кл. G 11 С 11/00, 30.03.94 г. - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения накопителя на магнитной ленте с вычислительной машиной | 1985 |

|

SU1242971A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

| Динамическое оперативное запоминающее устройство | 1987 |

|

SU1499401A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| СПОСОБ ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2008 |

|

RU2401454C2 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1991 |

|

SU1837303A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для долговременного хранения и многократного оперативного обновления пакетов цифровой информации. Техническим результатом является возможность осуществления взаимозаменяемости различных типов накопителей. Накопитель цифровой информации содержит пять регистров, дешифратор, шину входной информации, блок оперативной памяти, блок управления, микроконтроллер, счетчик, магистральный приемопередатчик, блок коррекции, блок формирователей сигналов, открывающих выходы выбранных элементов оперативной памяти на вторую магистральную шину, две магистральные шины, блок постоянной памяти. 1 ил.

Накопитель цифровой информации, содержащий первый регистр, информационные входы которого соединены с шиной входной информации, второй регистр, первая группа выходов которого через дешифратор подключена к первой группе входов блока оперативной памяти, третий и четвертый регистры, блок управления, отличающийся тем, что в него введены микроконтроллер, блок постоянной памяти, счетчик, магистральный приемопередатчик, блок коррекции, блок формирователей сигналов, открывающих выходы выбранных элементов оперативной памяти на вторую магистральную шину, пятый регистр, первая и вторая магистральные шины, информационные входы второго регистра соединены с первой группой выходов микроконтроллера, а вторая группа выходов второго регистра подключена к первой группе входов блока постоянной памяти, выходы которого, информационные входы третьего регистра, вторая группа выходов микроконтроллера и первая группа выходов магистрального приемопередатчика подключены к первой магистральной шине, третья группа выходов микроконтроллера подключена к первой группе входов блока управления, выходы третьего регистра подключены к вторым группам входов блока постоянной памяти и блока управления, информационные входы четвертого регистра являются командными входами накопителя, выходы первого, четвертого регистров и блока коррекции, информационные входы пятого регистра, блока коррекции и счетчика, вторые группы выходов магистрального приемопередатчика и блока оперативной памяти подключены к второй магистральной шине, выходы счетчика подключены к третьей группе входов блока оперативной памяти, входы блока формирователей сигналов, открывающих выходы выбранных элементов оперативной памяти на вторую магистральную шину, соединены с выходами дешифратора, а выходы подключены к четвертой группе входов блока оперативной памяти, вход блока управления является тактовым входом накопителя, первая группа выходов блока управления подключена к группе входов микроконтроллера, выходы второй группы выходов блока управления подключены к соответствующим управляющим входам регистров с первого по пятый, дешифратора, блока постоянной памяти, счетчика, магистрального приемопередатчика и блока коррекции, первый выход блока управления подключен к входам блока формирователей сигналов, открывающих выходы выбранных элементов оперативной памяти на вторую магистральную шину, и блока оперативной памяти, второй выход - к тактовому входу счетчика, третий выход - к второму управляющему входу пятого регистра и является первым выходом накопителя, четвертый выход является вторым выходом накопителя, а выходы пятого регистра являются группой информационных выходов накопителя.

| RU 2058603 C1, 20.04.1996 | |||

| IEEE TRANSACTIONS OF SOLID-STATE CIRCUITS, VOL 24, №4, AUGUST, 1989, p.859-867 | |||

| Устройство для магнитной записи-воспроизведения | 1981 |

|

SU1010648A1 |

| СПОСОБ МАГНИТНОЙ ЗАПИСИ ЦИФРОВОЙ ИНФОРМАЦИИ | 1999 |

|

RU2180457C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| US 4120006 А, 10.10.1978. | |||

Авторы

Даты

2004-09-20—Публикация

2002-11-18—Подача