з

4ь

to

00

ел

С

31742856

Изобретение относится к приборостроению и может быть использовано для построения долговременных запоминающих устройств на подвижном носителе, а также при передаче и приеме информации .

Целью изобретения является упрощение устройства путем упрощения формирователя признаков ошибок при воспроизведении.

Сущность изобретения состоит в формировании при записи контрольных разрядов и размещении каждого контрольного разряда после группы из (v-1) информационных разрядов. При воспроизведении контрольные разряды формируются так же, как и при записи, и сравниваются с воспроизведенными контрольными разрядами. Несравнение соответствующих контрольных разрядов сигнализирует о наличии ошибок в определенной части информации. Номер дефектного информационного разряда определяется по расстоянию между соседними не-;

совпавшими контрольными разрядами. i

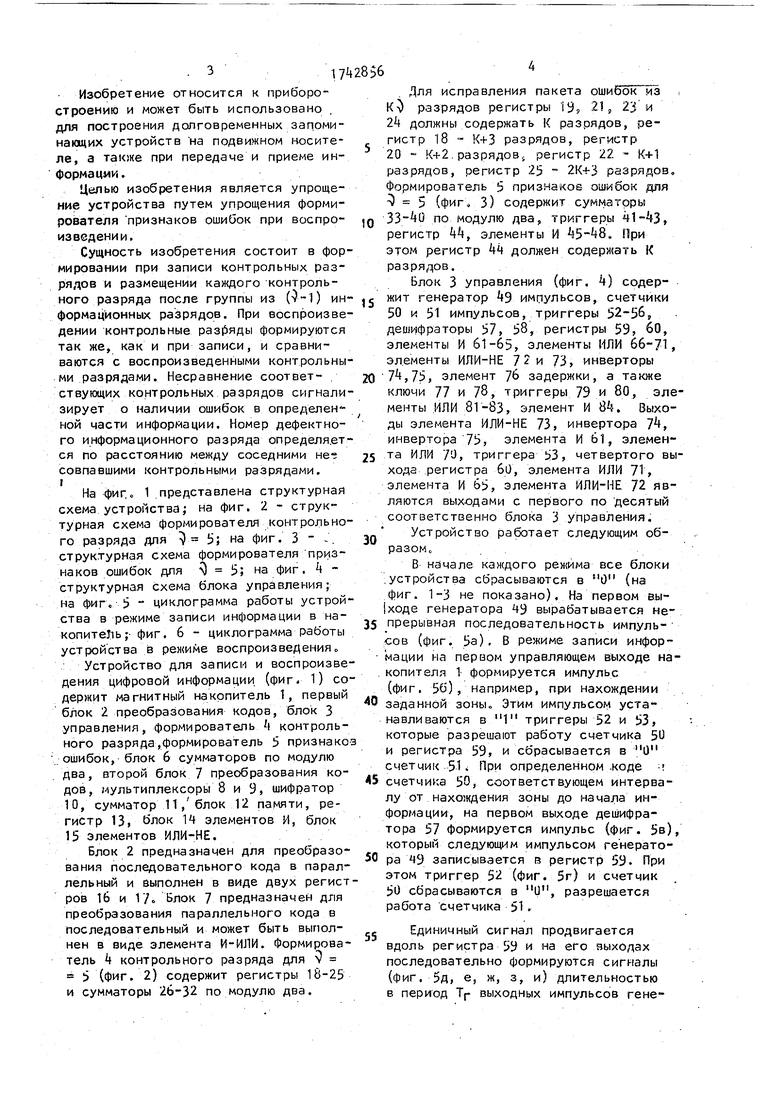

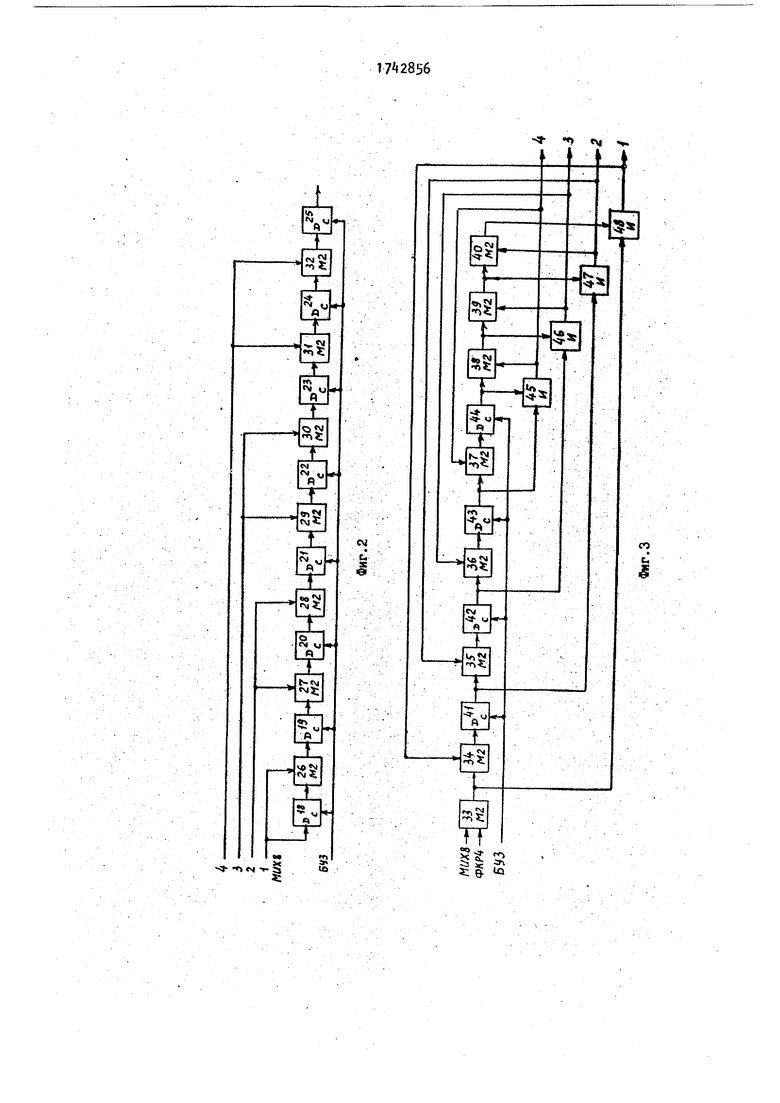

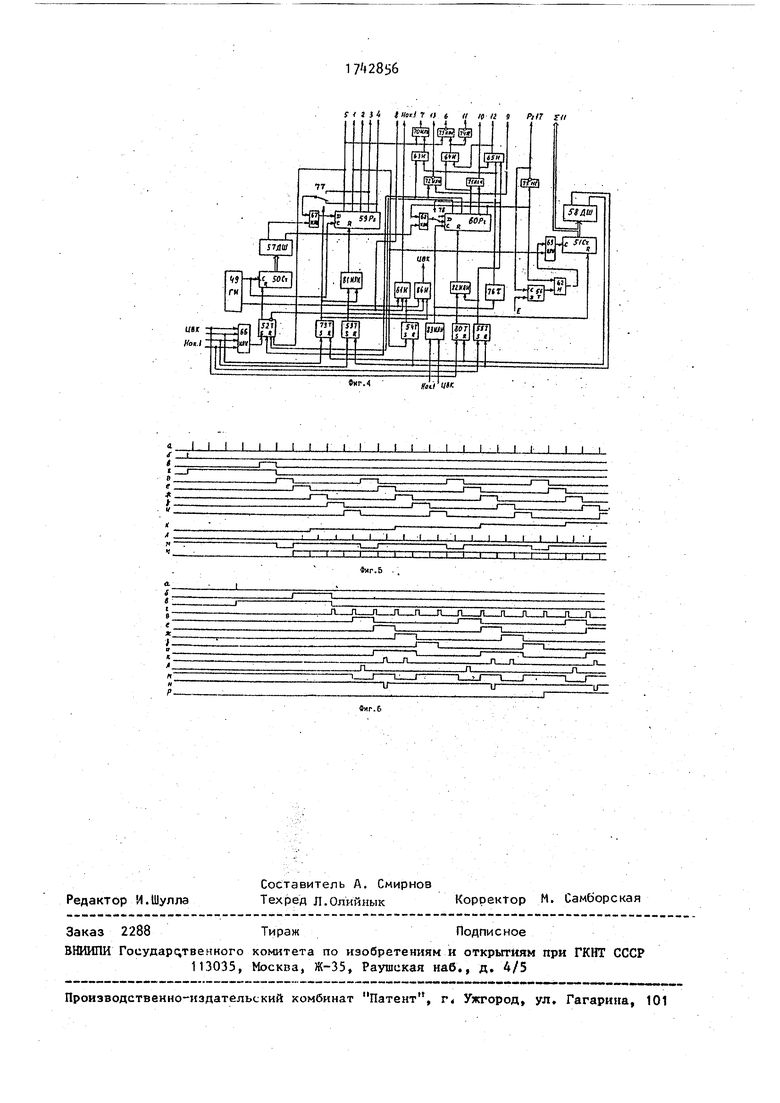

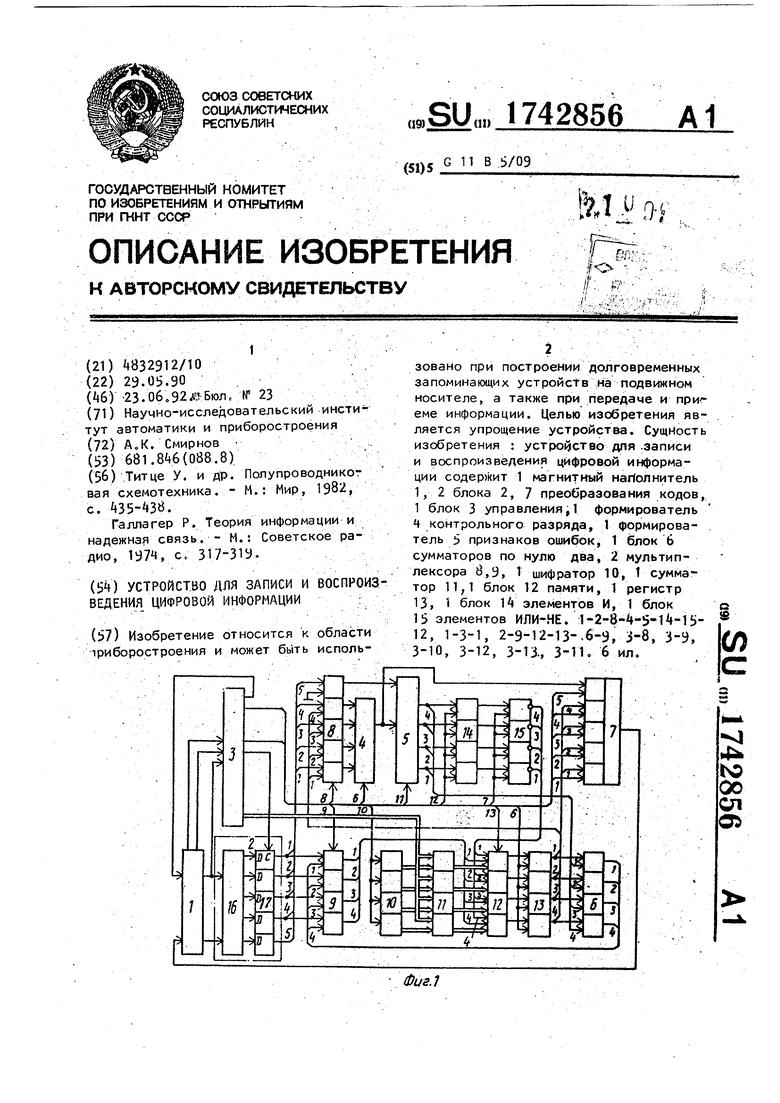

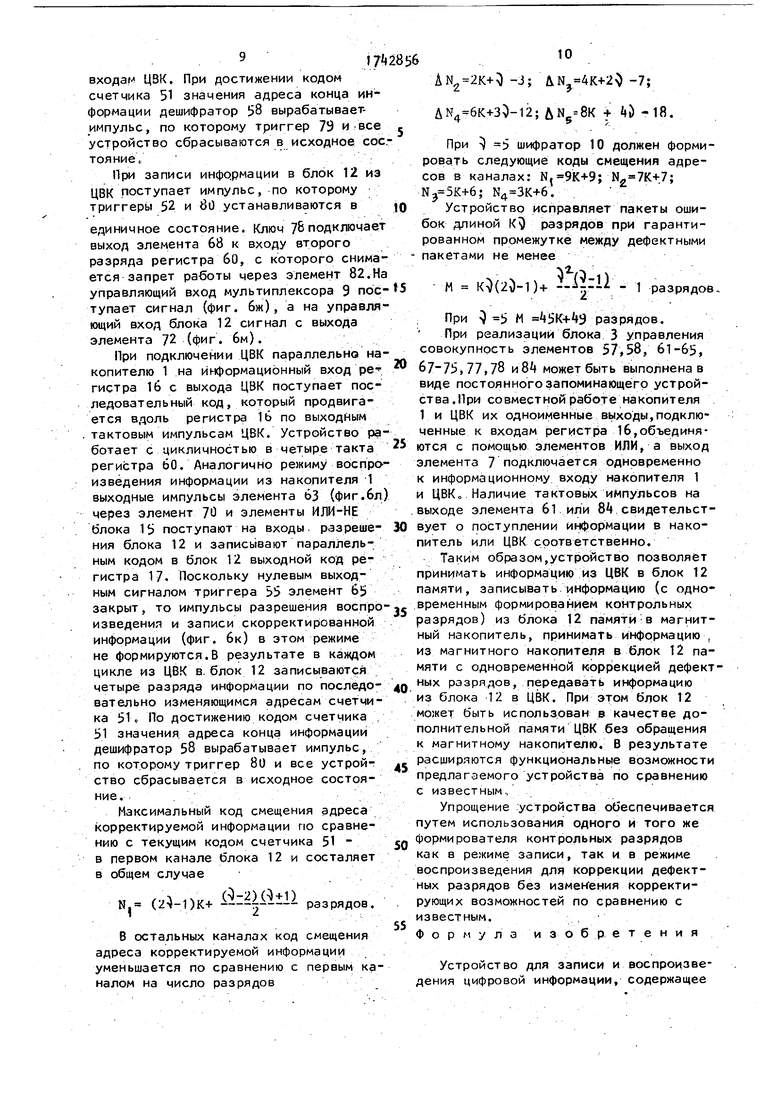

На фиг о 1 представлена структурная

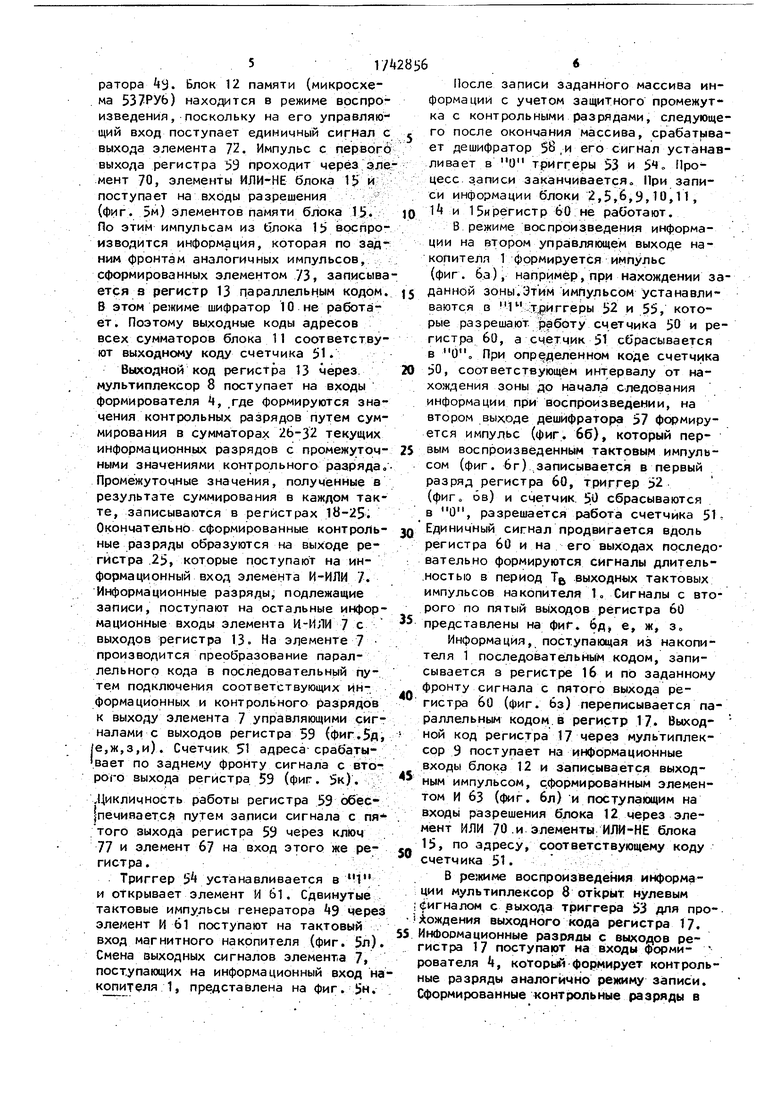

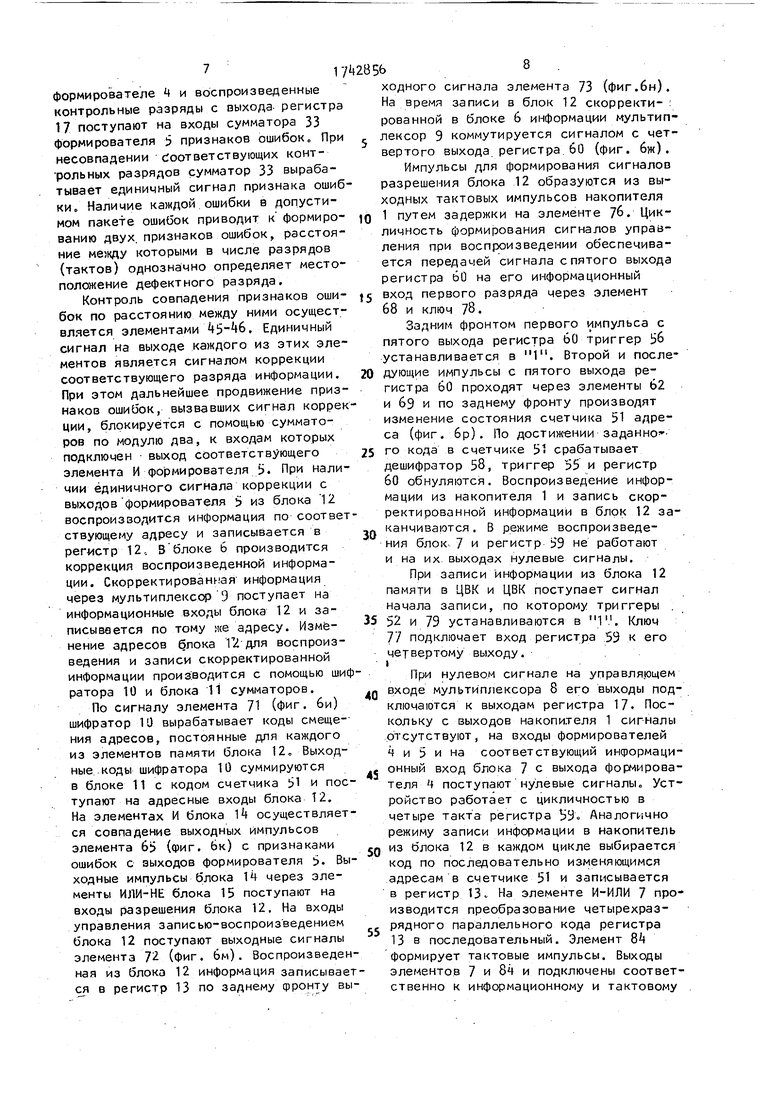

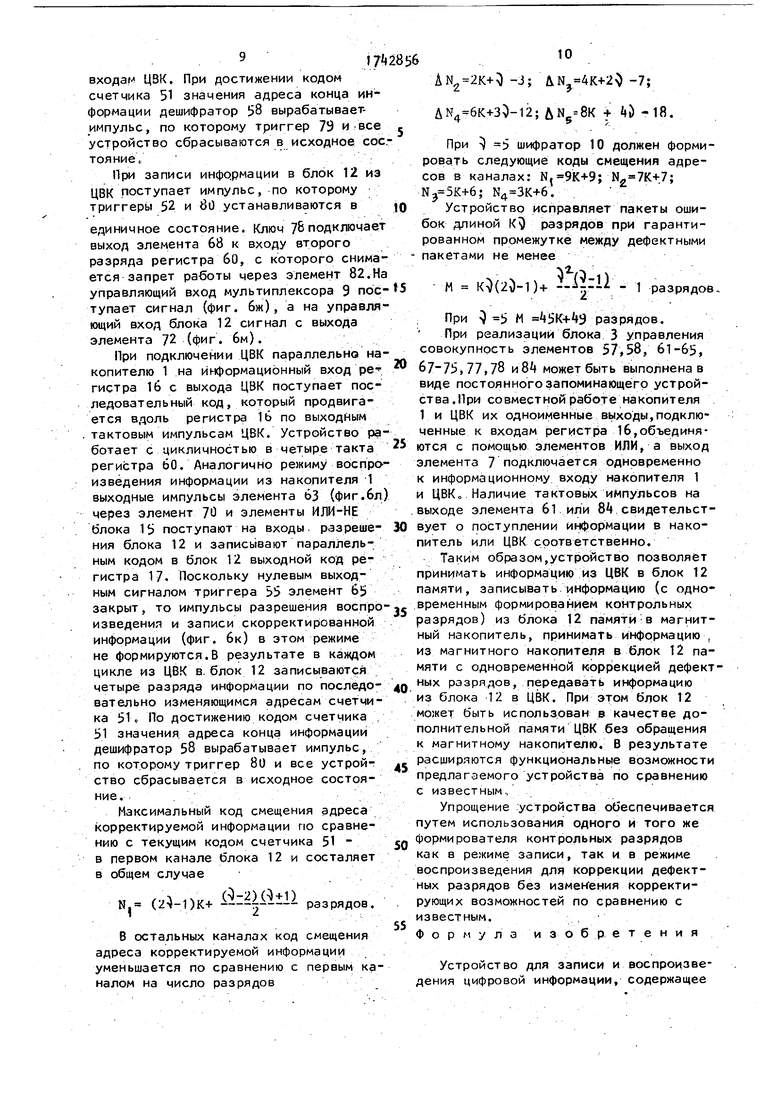

схема устройства; на фиг. 2 - структурная схема формирователя контрольного разряда для } 5; на фиг. 3 - - структурная схема формирователя признаков ошибок для 5; на фиг. А - структурная схема блока управления; на фиг. 5 циклограмма работы устройства в режиме записи информации в накопитель; фиг, 6 - циклограмма работы устройства в режиме воспроизведения,,

Устройство для записи и воспроизведения цифровой информации (фиг. 1) содержит магнитный накопитель 1, первый блок 2 преобразования кодов, блок 3 управления, формирователь Ц контрольного разряда,формирователь 5 признаков ошибок, блок 6 сумматоров по модулю два, второй блок 7 преобразования кодов, мультиплексоры 8 и 9, шифратор 10, сумматор 11, блок 12 памяти, регистр 13, блок 14 элементов И, блок 15 элементов ИЛИ-НЕ.

Блок 2 предназначен для преобразования последовательного кода в параллельный и выполнен в виде двух регистров 16 и 1/о Блок 7 предназначен для преобразования параллельного кода в последовательный и может быть выполнен в виде элемента И-ИЛИ. Формирователь k контрольного разряда для 3 5 (фиг. 2) содержит регистры 18-25 и сумматоры 26-32 по модулю два.

Для исправления пакета К-) разрядов регистры i9 21, 23 и 2k должны содержать К разрядов, регистр 18 - К+3 разрядов, регистр 20 - К+2 разрядовs регистр 22 - К+1 разрядов, регистр 25 - разрядов. Формирователь 5 признаков ошибок для ) 5 (фиг, 3) содержит сумматоры

33-40 по модулю два, триггеры п1-43, регистр 44, элементы И 45-48. При этом регистр 44 должен содержать К разрядов.

Блок 3 управления (фиг. 4) содер5 жит генератор 49 импульсов, счетчики 50 и 51 импульсов, триггеры 52-56, дешифраторы 57, 58, регистры 59, 60, элементы И 61-65, элементы ИЛИ 66-71, элементы ИЛИ-НЕ 7 и 73, инверторы

74,75, элемент 76 задержки, а также ключи 77 и 78, триггеры 79 и 80, элементы ИЛИ 81-83, элемент И . Выходы элемента ИЛИ-НЕ 73, инвертора 74, инвертора 75, элемента И 61, элемен5 та ИЛИ 70, триггера ЬЗ, четвертого выхода регистра 60, элемента ИЛИ 71, элемента И 65, элемента ИЛИ-НЕ 72 являются выходами с первого по десятый соответственно блока 3 управления.

Устройство работает следующим образом

В начале каждого режима все блоки устройства сбрасываются в О (на фиг. 1-3 не показано). На первом выводе генератора 49 вырабатывается не5 прерывная последовательность импульсов (фиг. 5а), В режиме записи информации на первом управляющем выходе накопителя 1 формируется импульс (фиг. 56), например, при нахождении

0 заданной зоны. Этим импульсом устанавливаются в 1 триггеры 52 и 53, которые разрешают работу счетчика 50 и регистра 59 и сбрасывается в О счетчик 51. При определенном коде

5 счетчика 50, соответствующем интервалу от нахождения зоны до начала информации, на первом выходе дешифратора 57 формируется импульс (фиг. 5в), который следующим импульсом генерато0 ра 49 записывается в регистр 59. При этом триггер 52 (фиг. 5г) и счетчик 50 сбрасываются в О, разрешается работа счетчика 51

0

Единичный сигнал продвигается вдоль регистра 59 и на его зыходах последовательно формируются сигналы (фиг. 5д, е, ж, з, и) длительностью в период Тр выходных импульсов гене51/42856

ратора 9. Блок 12 памяти (микросхе ма 537РУ6) находится в режиме воспроизведения, поскольку на его управляю- щий вход поступает единичный сигнал с j выхода элемента 12. Импульс с первого выхода регистра 59 проходит через элемент 70, элементы ИЛИ-НЕ блока 15 и поступает на входы разрешения (фиг. 5м) элементов памяти блока 15. 10 По этим импульсам из блока 15 воспроизводится информация, которая по задним фронтам аналогичных импульсов, сформированных элементом 73, записываПосле записи заданного массива информации с учетом защитного промежутка с контрольными разрядами, следующего после окончания массива, срабатывает дешифратор 5Й, и его сигнал устанавливает в О триггеры 53 и 54. Процесс записи заканчивается. При записи информации блоки 2,5,6,9,10,11, И и 15ирегистр 60 не работают.

В режиме воспроизведения информации на втором управляющем выходе накопителя 1 формируется импульс (фиг. 6а), например, при нахождении зается а регистр 13 параллельным кодом. 15 данной зоны.Этим импульсом устанавливаются в 1 триггеры 52 и 55, которые разрешают работу счетчика 50 и регистра 60, а счетчик 51 сбрасывается в О, При определенном коде счетчика 50, соответствующем интервалу от нахождения зоны до начала следования информации при воспроизведении, на втором выходе дешифратора 57 формируется импульс (фиг. 6б), который первым воспроизведенным тактовым импульсом (фиг. 6г) записывается в первый разряд регистра 60, триггер 52 (фиг о 6в) и счетчик 50 сбрасываются в О, разрешается работа счетчика 51- Единичный сигнал продвигается вдоль регистра 60 и на его выходах последовательно формируются сигналы длительностью в период Ть выходных тактовых импульсов накопителя 1„ Сигналы с второго по пятый выходов регистра 60 представлены на фиг. 6д, е, ж, з„

В этом режиме шифратор 10 не работает . Поэтому выходные коды адресов всех сумматоров блока 11 соответствуют выходному коду счетчика 51.

Выходной код регистра 13 через 20 мультиплексор 8 поступает на входы формирователя Ч, где формируются значения контрольных разрядов путем суммирования в сумматорах текущих информационных разрядов с промежуточ- 25 ными значениями контрольного разряда. Промежуточные значения, полученные в результате суммирования в каждом такте, записываются в регистрах 18-25. Окончательно сформированные контроль- jQ ные разряды образуются на выходе регистра 25, которые поступают на информационный вход элемента И-ИЛИ 7. Информационные разряды, подлежащие записи, поступают на остальные информационные входы элемента Н-ИЛИ 7 с выходов регистра 13. На элементе 7 производится преобразование параллельного кода в последовательный путем подключения соответствующих информационных и контрольного разрядов к выходу элемента 7 управляющими сигналами с выходов регистра 59 (фиг.5д, /е,ж,з,и). Счетчик 51 адреса срабаты- вает по заднему фронту сигнала с второго выхода регистра 59 (фиг. 5к).

Цикличность работы регистра 59 обес- |печинается путем записи сигнала с пя того выхода регистра 59 через ключ 77 и элемент 67 на вход этого же ре- JQ гистра.

Триггер 5 устанавливается в V1 и открывает элемент И 61. Сдвинутые тактовые импульсы генератора А9 через элемент И 61 поступают на тактовый

3S

40

ваются в 1 триггеры 52 и 55, которые разрешают работу счетчика 50 и р гистра 60, а счетчик 51 сбрасывается в О, При определенном коде счетчик 50, соответствующем интервалу от нахождения зоны до начала следования информации при воспроизведении, на втором выходе дешифратора 57 формиру ется импульс (фиг. 6б), который первым воспроизведенным тактовым импуль сом (фиг. 6г) записывается в первый разряд регистра 60, триггер 52 (фиг о 6в) и счетчик 50 сбрасываются в О, разрешается работа счетчика 5 Единичный сигнал продвигается вдоль регистра 60 и на его выходах послед вательно формируются сигналы длитель ностью в период Ть выходных тактовых импульсов накопителя 1„ Сигналы с вт рого по пятый выходов регистра 60 представлены на фиг. 6д, е, ж, з„

Информация, поступающая из накопи теля 1 последовательным кодом, записывается з регистре 16 и по заданном фронту сигнала с пятого выхода регистра 60 (фиг. 6з) переписывается п раллельным кодом в регистр 17. Выход ной код регистра 17 через мультиплек сор 9 поступает на информационные входы блока 12 и записывается выходным импульсом, сформированным элемен том И 63 (фиг. 6л) и поступающим на входы разрешения блока 12 через элемент ИЛИ 70 и элементы ИЛИ-НЕ блока 15, по адресу, соответствующему коду счетчика 51.

В режиме воспроизведения информации мультиплексор 8 открыт нулевым Сигналом с выхода триггера 53 для про хождения выходного кода регистра 17.

/, .. л 55 Информационные разряды с выходов ое- вход магнитного накопителя (фиг. 5л). ГИстра 17 поступают на входы формиСмена выходных сигналов элемента 7, поступающих на информационный вход накопителя 1, представлена на фиг. 5н.

рователя k, который формирует контрол ные разряды аналогично режиму записи. Сформированные контрольные разряды в

После записи заданного массива информации с учетом защитного промежутка с контрольными разрядами, следующего после окончания массива, срабатывает дешифратор 5Й, и его сигнал устанавливает в О триггеры 53 и 54. Процесс записи заканчивается. При записи информации блоки 2,5,6,9,10,11, И и 15ирегистр 60 не работают.

В режиме воспроизведения информации на втором управляющем выходе накопителя 1 формируется импульс (фиг. 6а), например, при нахождении заданной зоны.Этим импульсом устанавли

ваются в 1 триггеры 52 и 55, которые разрешают работу счетчика 50 и регистра 60, а счетчик 51 сбрасывается в О, При определенном коде счетчика 50, соответствующем интервалу от нахождения зоны до начала следования информации при воспроизведении, на втором выходе дешифратора 57 формируется импульс (фиг. 6б), который первым воспроизведенным тактовым импульсом (фиг. 6г) записывается в первый разряд регистра 60, триггер 52 (фиг о 6в) и счетчик 50 сбрасываются в О, разрешается работа счетчика 51- Единичный сигнал продвигается вдоль регистра 60 и на его выходах последовательно формируются сигналы длительностью в период Ть выходных тактовых импульсов накопителя 1„ Сигналы с второго по пятый выходов регистра 60 представлены на фиг. 6д, е, ж, з„

Информация, поступающая из накопителя 1 последовательным кодом, записывается з регистре 16 и по заданному фронту сигнала с пятого выхода регистра 60 (фиг. 6з) переписывается параллельным кодом в регистр 17. Выход- : ной код регистра 17 через мультиплексор 9 поступает на информационные входы блока 12 и записывается выходным импульсом, сформированным элементом И 63 (фиг. 6л) и поступающим на входы разрешения блока 12 через элемент ИЛИ 70 и элементы ИЛИ-НЕ блока 15, по адресу, соответствующему коду счетчика 51.

В режиме воспроизведения информации мультиплексор 8 открыт нулевым Сигналом с выхода триггера 53 для прохождения выходного кода регистра 17.

Информационные разряды с выходов ое- ГИстра 17 поступают на входы формирователя k, который формирует контрольные разряды аналогично режиму записи. Сформированные контрольные разряды в

формирователе 4 и воспроизведенные контрольные разряды с выхода регистра 17 поступают на входы сумматора 33 формирователя 5 признаков ошибок. При несовпадении соответствующих контрольных разрядов сумматор 33 вырабатывает единичный сигнал признака ошибки. Наличие каждой ошибки в допустимом пакете ошибок приводит к формированию двух признаков ошибок, расстояние между которыми в числе разрядов (тактов) однозначно определяет местоположение дефектного разряда.

Контроль совпадения признаков ошибок по расстоянию между ними осуществляется элементами . Единичный сигнал на выходе каждого из этих элементов является сигналом коррекции соответствующего разряда информации. При этом дальнейшее продвижение признаков ошибок, вызвавших сигнал коррекции, блокируется с помощью сумматоров по модулю два, к входам которых подключен выход соответствующего элемента И формирователя 5. При наличии единичного сигнала коррекции с выходов формирователя 5 из блока 12 воспроизводится информация по соответствующему адресу и записывается в регистр 12, В блоке 6 производится коррекция воспроизведенной информации. Скорректированная информация через мультиплексор 9 поступает на информационные входы блока 12 и записывается по тому же адресу. Изменение адресов б,лока VI для воспроизведения и записи скорректированной информации производится с помощью шифратора 10 и блока 11 сумматоров.

По сигналу элемента 71 (фиг. 6и) шифратор 11) вырабатывает коды смещения адресов, постоянные для каждого из элементов памяти блока 12„ Выходные коды шифратора 10 суммируются в блоке 11 с кодом счетчика 51 и поступают на адресные входы блока 12. На элементах И блока 14 осуществляется совпадение выходных импульсов элемента 65 (фиг. Ьк) с признаками ошибок с выходов формирователя :. Выходные импульсы блока 14 через элементы ИЛИ-НЕ блока 15 поступают на входы разрешения блока 12. На входы управления записью-воспроизведением блока 12 поступают выходные сигналы элемента 72 (фиг. 6м). Воспроизведенная из блока 12 информация записывается в регистр 13 по заднему фронту вы17428568

ходного сигнала элемента 73 (фиг.бн). На время записи в блок 12 скорректированной в блоке 6 информации мультип- , лексор 9 коммутируется сигналом с четвертого выхода регистра 60 (фиг. 6ж). Импульсы для формирования сигналов разрешения блока 12 образуются из выходных тактовых импульсов накопителя Ю 1 путем задержки на элементе 76. Цикличность формирования сигналов управления при воспроизведении обеспечивается передачей сигнала снятого выхода регистра 60 на его информационный 15 вход первого разряда через элемент 68 и ключ 78.

Задним фронтом первого импульса с пятого выхода регистра 60 триггер 56

устанавливается в 1. Второй и после20

25

30

35

дующие импульсы с пятого выхода регистра 60 проходят через элементы 62 и 69 и по заднему фронту производят изменение состояния счетчика 51 адреса (фиг. 6р). По достижении заданного кода в счетчике 51 срабатывает дешифратор 58, триггер 55 и регистр 60 обнуляются. Воспроизведение информации из накопителя 1 и запись скорректированной информации в блок 12 заканчиваются. В режиме воспроизведения блок 7 и регистр 59 не работают и на их выходах нулевые сигналы.

При записи информации из блока 12 памяти в ЦБК и ЦБК поступает сигнал начала записи, по которому триггеры 52 и 79 устанавливаются в 1. Ключ 77 подключает вход регистра 59 к его четвертому выходу.

При нулевом сигнале на управляющем дп входе мультиплексора 8 его выходы подключаются к выходам регистра 17. Поскольку с выходов накопителя 1 сигналы отсутствуют, на входы формирователей ч и 5 и на соответствующий информационный вход блока 7 с выхода формирователя 4 поступают нулевые сигналы Устройство работает с цикличностью в четыре такта регистра 59 Аналогично режиму записи информации в накопитель из блока 12 в каждом цикле выбирается код по последовательно изменяющимся адресам в счетчике 51 и записывается в регистр 13 На элементе И-ИЛИ 7 производится преобразование четырехразрядного параллельного кода регистра 13 в последовательный. Элемент 84 формирует тактовые импульсы. Выходы элементов 7 и 84 и подключены соответственно к информационному и тактовому

4S

50

55

устанавливается в 1. Второй и после

5

0

5

дующие импульсы с пятого выхода регистра 60 проходят через элементы 62 и 69 и по заднему фронту производят изменение состояния счетчика 51 адреса (фиг. 6р). По достижении заданного кода в счетчике 51 срабатывает дешифратор 58, триггер 55 и регистр 60 обнуляются. Воспроизведение информации из накопителя 1 и запись скорректированной информации в блок 12 заканчиваются. В режиме воспроизведения блок 7 и регистр 59 не работают и на их выходах нулевые сигналы.

При записи информации из блока 12 памяти в ЦБК и ЦБК поступает сигнал начала записи, по которому триггеры 52 и 79 устанавливаются в 1. Ключ 77 подключает вход регистра 59 к его четвертому выходу.

При нулевом сигнале на управляющем п входе мультиплексора 8 его выходы подключаются к выходам регистра 17. Поскольку с выходов накопителя 1 сигналы отсутствуют, на входы формирователей ч и 5 и на соответствующий информационный вход блока 7 с выхода формирователя 4 поступают нулевые сигналы Устройство работает с цикличностью в четыре такта регистра 59 Аналогично режиму записи информации в накопитель из блока 12 в каждом цикле выбирается код по последовательно изменяющимся адресам в счетчике 51 и записывается в регистр 13 На элементе И-ИЛИ 7 производится преобразование четырехразрядного параллельного кода регистра 13 в последовательный. Элемент 84 формирует тактовые импульсы. Выходы элементов 7 и 84 и подключены соответственно к информационному и тактовому

S

0

5

входам ЦБК. При достижении кодом счетчика 51 значения адреса конца информации дешифратор 58 вырабатывает- импульс, по которому триггер 79 и все устройство сбрасываются в исходное состояние

При записи информации в блок 12 из ЦВК поступает импульс, по которому триггеры 52 и 80 устанавливаются в

единичное состояние. Ключ 7& подключает выход элемента 68 к входу второго разряда регистра 60, с которого снимается запрет работы через элемент 82.На управляющий вход мультиплексора 9 поступает сигнал (фиг. 6ж), а на управляющий вход блока 12 сигнал с выхода элемента 72 (фиг. 6м).

При подключении ЦВК параллельно накопителю 1 на информационный вход ре гистра 16 с выхода ЦВК поступает последовательный код, который продвигается вдоль регистра 16 по выходным тактовым импульсам ЦВК. Устройство работает с цикличностью в четыре такта регистра 60. Аналогично режиму воспро-- изведения информации из накопителя 1 выходные импульсы элемента 63 (фиг.6л) через элемент 70 и элементы ИЛИ-НЕ блока 15 поступают на входы разрешения блока 12 и записывают параллельным кодом в блок 12 выходной код регистра 17. Поскольку нулевым выходным сигналом триггера 55 элемент 65

-

, JQ

5 20

30

10

AN 4K+2$ -7;

UN4 6K+3}-12; + O-18.

При } 5 шифратор 10 должен формировать следующие коды смещения адресов в каналах: N,9K+9; N- 7K+7; N 5K+6; .

Устройство исправляет пакеты ошибок длиной разрядов при гарантированном промежутке между дефектными пакетами не менее

М К}(2;Н) + --i-pi - 1 разрядов.

При } 5 М 45К+49 разрядов. При реализации блока 3 управления совокупность элементов 57,58, 61-65,

67-75,77,78 и8 может быть выполнена в виде постоянного запоминающего устройства. При совместной работе накопителя 1 и ЦВК их одноименные выходы,подключенные к входам регистра 16,объединяются с помощью элементов ИЛИ, а выход элемента 7 подключается одновременно к информационному входу накопителя 1 и ЦВКо Наличие тактовых импульсов на выходе элемента 61 или 8 свидетельствует о поступлении информации в накопитель или ЦВК соответственно.

Таким образом,устройство позволяет принимать информацию из ЦВК в блок 12 памяти, записывать информацию (с одно

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107334C1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1985 |

|

SU1257709A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

Изобретение относится к области приборостроения и может быть использовано при построении долговременных запоминающих устройств на подвижном носителе, а также при передаче и еме информации. Целью изобретения является упрощение устройства. Сущность изобретения : устройство для .записи и воспроизведения цифровой информации содержит 1 магнитный напЪлнитель 1, 2 блока 2, 7 преобразования кодов, 1 блок 3 управления, формирователь 4 контрольного разряда, 1 формирователь 5 признаков ошибок, 1 блок 6 сумматоров по нулю два, 2 мультиплексора 8,9, 1 шифратор 10, t сумматор 11,1 блок 12 памяти, 1 регистр 13, 1 блок 14 элементов И, 1 блок 15 элементов ИЛИ-НЕ. 1-2-8-4-5-14-15- 12, 1-3-1, 2-9-12-13--6-9, 3-8, 3-9, 3-Ю, 3-12, 3-13., 3-11. 6 ил. § (Л

закрыт, то импульсы разрешения воспро-je временным формированием контрольных

разрядов) из блока 12 памяти в магнитный накопитель, принимать информацию , из магнитного накопителя в блок 12 памяти с одновременной коррекцией дефектчетыре разряда информации по последо- до ных разрядов, передавать информацию

изведения и записи скорректированной информации (фиг. 6к) в этом режиме не формируются.В результате в каждом цикле из ЦВК в блок 12 записываются

из блока 12 в ЦВК. При этом блок 12 может быть использован в качестве дополнительной памяти ЦВК без обращения к магнитному накопителю. В результате расширяются функциональные возможности предлагаемого устройства по сравнению с известным,

вательно изменяющимся адресам счетчика 51 о По достижению кодом счетчика 51 значения адреса конца информации дешифратор 58 вырабатывает импульс, по которому триггер 80 и все устройство сбрасывается в исходное состояние.

Максимальный код смещения адреса корректируемой информации по сравнению с текущим кодом счетчика 51 в первом канале блока 12 и состаляет в общем случае

N

Г

()K+ &2Hi±ll разрядов.

В остальных каналах код смещения адреса корректируемой информации уменьшается по сравнению с первым каналом на число разрядов

ных разрядов, передавать информацию

из блока 12 в ЦВК. При этом блок 12 может быть использован в качестве дополнительной памяти ЦВК без обращения к магнитному накопителю. В результате расширяются функциональные возможности предлагаемого устройства по сравнению с известным,

Упрощение устройства обеспечивается путем использования одного и того же формирователя контрольных разрядов как в режиме записи, так и в режиме воспроизведения для коррекции дефектных разрядов без изменения корректирующих возможностей по сравнению с известным.

Формула изобретения

Устройство для записи и воспроизведения цифровой информации, содержащее

11

17А2856

магнитный накопитель, информационный и тактовый выходы которого подключены соответственно к информационному и первому тактовому входу первого блока преобразования кодов, формирователь признаков ошибок, выходы которого подключены к одной группе входов блока сумматоров по модулю два, выход формирователя контрольного разряда

подключен к одному входу второго блока преобразования кодов, выход которого подключен к информационному входу Магнитного накопителя, тактовый, первый и второй управляющие выходы маг- нитного накопителя подключены соответственно к первому, второму и третьему входам блока управления,первая группа выходов которого подключена к группе управляющих входов второго блока преобразования кодов, выходы с первого по четвертый блока управления подключены к управляющим входам соот ветственно формирователя контрольного разряда, фоомирователя признаков оши- бок, второму тактовому входу первого блока преобразования кодов и тактовому входу магнитного накопителя, о т- личающееся тем, что, с целью упрощения устройства, в него введены первый и второй мультиплексоры, шифратор, сумматор, блок памяти, регистр, блок элементов И и блок элементов ИЛИ-НЕ, выходы первого блока преобразования кодов подключены к первой группе входов первого и второго муль- типлексоров, группа выходов первого мультиплексора подключена к информационным входам формирователя контрольного разряда, выход которого и один

12

выход первого мультиплексора подключены к информационным входам формирователя признаков ошибок, выходы которого подключены к первой группе входов блока элементов И, выходы блока элементов И подключены к первой группе входов блока элементов ИЛИ-НЁ, выходы которого подключены к первой группе управляющих входов блока памяти, выхрды шифратора подключены к первой группе входов сумматора, выходы сумматора подключены к адресным входам блока памяти, выходы которого подключены к информационным входам регистра, выходы регистра подключены к другой группе входов блока сумматоров по модулю два, выходы которого подключены к второй группе входов второго мультиплексора, выходы второго мультиплексора подключены к информационным входам блока памяти, выходы регистра и общая шина подключены к второй группе входов первого мультиплексора, выходы регистра подключены к второй группе входов второго блока преобразования кодов, первый и с пятого по десятый выходы блока управления подключены соответственно к тактовому входу регистра, группе информационных входов блока элементов ИЛИ-НЕ, управляющему входу первого мультиплексора, управляющему входу второго мультиплексора, входу шифратора , второй группе входов блока элементов И и к второй группе управляющих входов блока памяти, а вторая группа выходов блока управления подключена к второй группе входов сумматора .

2

1

MUXt

a III I I I II II I III I I I I I I I I I II

/ r, ...

Фиг. 4

toil /«

| Титце У | |||

| и др | |||

| Полупроводниковая схемотехника | |||

| - М.: Мир, 1982, с | |||

| Способ получения твердых неплавких и нерастворимых продуктов уплотнения формальдегида с фонолами | 1925 |

|

SU435A1 |

| Галлагер Р | |||

| Теория информации и надежная связь | |||

| - М.: Советское радио, 1974, с, 317-319. | |||

Авторы

Даты

1992-06-23—Публикация

1990-05-29—Подача