Изобретение относится к области микропроцессорной техники, в частности, может применяться для реализации обмена информацией.

Известна микроЭВМ (Дж. Мик и др. Проектирование микропроцессорных устройств с разрядно-модульной организацией, т.1, М.: Мир, 1984, с.7, рис. 1, 2), содержащая центральный процессор, устройство ввода-вывода, оперативное запоминающее устройство.

Недостатком данной микроЭВМ является сложность устройства ввода-вывода.

Целью данного изобретения является повышение надежности за счет реализации устройства ввода-вывода.

Поставленная цель достигается тем, что микроЭВМ содержит центральный процессор, устройство ввода-вывода, оперативное запоминающее устройство, при этом центральный процессор включает устройство сопряжения с магистралью, сверхоперативное запоминающее устройство, устройство обработки данных.

Причем устройство ввода-вывода содержит узел адаптера связи, узел регистра состояния, узел селектора адреса, узел логики управления узел управления приемопередачи, узел дешифратора, узел программируемой матрицы, устройство ввода, при этом узел адаптера связи устройство ввода-вывода содержит генератор импульсов, два триггера, приемник, передатчик, мультиплексор, ограничительные элементы, узел регистра состояния содержит три мультиплексора, шесть элементов развязки, узел селектора адреса содержит пять приемопередатчиков, программируемую логическую матрицу, узел логики управления содержит три элемента ИЛИ-НЕ, два элемента И-НЕ, три передатчика, триггер, одновибратор, ограничительный элемент, накопительный элемент, узел управления приемопередачи содержит два дешифратора, мультиплексор, два элемента развязки с тремя состояниями, два элемента И, элемент И-НЕ, элемент НЕ, узел приемопередачи содержит триггер, элемент НЕ, элемент ИЛИ, программируемую логическую матрицу, асинхронный приемопередатчик, два элемента развязки на три состояния, элемент прерывания.

Причем узел адаптера связи подключен соответственно адресно-информационными входами второго и нулевого бита к одноименным выходам узла селектора адреса и узла управления приемопередачи, адресно-информационным входом/выходом нулевого бита к одноименному входу/выходу узла регистра состояния, входом установки к одноименному выходу узла приемопередачи, входом управления выходными данными к одноименному выходу узла приемопередачи, информационный вход "Прием данных" и выход "Передачи данных" узла адаптера связи образуют токовую петлю, вход "Регистр состояния выхода" которого подключен к одноименному выходу узла управления приемопередачи, узел регистра состояния подключен адресными входами с второго по четвертый бит к выходам узла логики управления, вход "Чтение узла регистра состояния" подключен к одноименному выходу узла адаптера связи, входы "Разрешение ввода", "Разрешение вывода" подключены к одноименным выходам узла управления приемопередачи, входы "Готов ввод", "Готов вывод" подключены к одноименным выходам узла приемопередачи, входы "Ошибка четности", "Ошибка стопового элемента", "Ошибка переполнения" подключены к одноименным выходам узла приемопередачи, вход "Управления входом" подключен к одноименному выходу узла управления приемопередачи, с первого по шестой входы вектора подключены к одноименным выходам узла приемопередачи, входы "Чтение третьего типа", "Запись младшего байта", "Чтение входного буфера", "Чтение регистра состояния" подключены к одноименным выходам узла логики управления, вход "Чтение четвертого типа" подключены к одноименному выходу узла приемопередачи, вход "Разрешение пульта" подключен к одноименному выходу узла приемопередачи, адресный вход первого бита подключен к одноименному выходу узла логики управления, адресно-информационные входы-выходы второго типа подключены к одноименным входам-выходам узла селектора адреса, узел логики управления подключен соответственно адресно-информационными входами-выходами с нулевого по тринадцатый бит к одноименным входам-выходам узла селектора адреса, входом "Выбор пульта" к одноименному выходу узла селектора адреса, входами "Чтение данных первого типа", "Запись данных", "Синхронизация обмена", "Выборка устройства" к одноименным выходам узла селектора адреса, входом "Ошибка стопового бита", входом шестого вектора к одноименным выходам узла приемопередачи, магистральные входы-выходы "Авария источника питания", "Ответ устройства", "Останов" подключены соответственно к одноименным входам-выходам магистрали, узел селектора адреса подключен входами с первого по шестой вектор соответственно к одноименным выходам узла приемопередачи, выходами "Чтение данных пятого типа", "Запись младшего байта", "Чтение входного буфера", "Чтение регистра состояния" к одноименным выходам узла логики управления, входом "Чтение четвертого типа" к одноименному выходу узла приемопередачи, входом "Разрешение пульта" к одноименному выходу узла приемопередачи, адресным входом первого бита и адресным входом первого и второго бита к одноименным выходам узла логики управления, узел управления приемопередачи подключен соответственно адресными входами с нулевого по четвертый бит к одноименным выходам узла логики управления, адресным входом первого бита с инверсией к одноименному выходу узла логики управления, адресно-информационными входами-выходами первого типа к одноименным выходам узла приемопередачи, входами "Запись младшего байта" и "Чтение входного буфера" к одноименным выходам узла логики управления, магистральные адресно-информационные входы-выходы, магистральные управляющие входы-выходы подключены к одноименным входам-выходам магистрали, узел приемнопередачи подключен соответственно адресным входом первого и второго бита к одноименному выходу узла логики управления, входами "Чтение данных второго типа" и "Чтение данных пятого типа" к одноименным выходам узла логики управления, адресно-информационными входами-выходами с нулевого по седьмой бит подключены к одноименным выходам управления приемопередачи, входом "Управление входными данными" к одноименному выходу адаптера связи, входы "Регистр состояния выхода", а "Разрешение буфера", "Регистр состояния входа" подключены к одноименным выходам узла управления приемопередачи, вход синхронизации подключен к одноименному выходу узла адаптера связи, магистральные входы-выходы "Запрос прерывания", "Выходной сигнал предоставления прерывания", "Входной сигнал предоставления прерывания" и "Установка" подключены к одноименным входам-выходам магистрали, устройство ввода подключено соответственно адресно-информационными входами-выходами с нулевого по пятнадцатый битами к одноименным входам-выходам селектора адреса, входы "Загрузка системного регистра старшего байта", "Чтение регистра страницы", "Чтение системного регистра", "Чтение регистра конфигурации", "Загрузка регистра страницы младшего байта, "Загрузка регистра страницы старшего байта" подключены соответственно к одноименным выходам узла дешифраторов, вход узла дешифратора "Выбор ввода" подключен к выходу узла программируемой матрицы, адресный вход первого бита узла программируемой матрицы подключен к одноименному выходу узла логики управления, адресно-информационные входы с шестого по двенадцатый битами подключены к одноименным выходам узла селектора адреса, магистральные адресно-информационные входы-выходы с восьмого по одиннадцатый битами подключены к одноименным входам-выходам селектора адреса, при этом в узле адаптера связи выход генератора импульсов подключен к выходу узла, вход приемника подключен к входу-выходу токовой петли, выход передатчика через ограничительный элемент подключен к входу-выходу токовой петли, к информационному входу первого триггера подключен адресно-информационный вход/выход нулевого бита, к тактирующему входу - вход "Регистра состояния выхода", к сбросовому входу - вход установки, прямой выход первого триггера подключен к первому входу - выходу "Останов" узла адаптера связи, инверсный выход первого триггера подключен к первому входу элемента И, ко второму входу которого подключен вход "Управление выходными данными", к первому входу передатчика подключена шина логической единицы микроЭВМ, выход приемника подключен к первому информационному входу мультиплексора, выход элемента И подключен ко второму и третьему информационным входам мультиплексора, к информационному входу второго триггера подключена адресно-информационная шина второго бита, к тактирующему входу которого подключен вход "Регистр состояния входа", сбросовый вход второго триггера подключен к входу установки, прямой выход второго триггера подключен к управляющему входу мультиплексора, выход которого подключен ко второму входу передатчика, при этом статическое запоминающее устройство включает узел магистральных приемопередатчиков, узел элементов памяти, узел адресации, узел управления памятью.

Причем узел магистральных приемопередатчиков подключен соответственно магистральными адресно-информационными, адресными и управляющими входами-выходами к магистрали, входами "Ответ устройства", "Разрешение памяти" к одноименным выходам узла управления памятью, адресно-информационными входами к одноименным выходам узла элементов памяти, узел элементов памяти подключен соответственно адресными входами к одноименным выходам узла адресации, входами "Запись старшего байта", "Выбор кристалла памяти", "Разрешение памяти" подключен к одноименным выходам узла управления памятью, входами "Выбор элементов памяти", "Выбор разрешения адреса" подключен к одноименным выходам узла адресации, узел адресации подключен соответственно адресно-информационными входами-выходами к одноименным выходам узла элементов памяти, входом "Синхронизация обмена" к одноименному выходу узла магистральных приемопередатчиков, адресным выходом третьего типа к одноименному выходу узла магистральных приемопередатчиков, узел управления памятью подключен входами "Чтение данных первого типа", "Запись данных", "Синхронизация обмена", "Признак записи байта" к одноименным выходам узла магистральных приемопередатчиков, входами "Выбор адреса" к одноименным выходам узла магистральных приемопередатчиков и к одноименным выходам узла адресации, входами "Выбор адреса" к одноименным выходам узла адресации, адресно-информационным входом третьего типа к одноименному выходу узла элементов памяти, при этом узел адресации содержит первый и второй регистры, элемент НЕ, первый и второй дешифраторы.

Причем адресно-информационные входы первого типа узла адресации подключены соответственно к информационным входам первого и второго регистров, к информационному входу второго регистра, кроме того, подключена адресная шина третьего типа, с первого по восьмой выходы первого регистра, с первого по пятый выходы второго регистра подключены через резисторную сборку к адресным выходам узла адресации, с шестого по восьмой выходы второго регистра через резисторные сборки подключены соответственно к первому по третий информационным входам первого дешифратора, седьмой и восьмой выходы второго регистра подключены соответственно к первому и второму информационным входам второго дешифратора, первый и второй входы разрешения первого дешифратора, третий информационный вход второго дешифратора подключены к шине логического нуля микроЭВМ, вход "Синхронизация обмена" узла адресации подключен через элемент НЕ к входам записи регистров, входы разрешения третьего состояния которых подключены к шине логического нуля микроЭВМ, при этом узел управления памятью содержит девять элементов И-НЕ, три элемента И, два элемента ИЛИ, два триггера, резисторную сборку, четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Причем в узле управления памятью подключены соответственно адресно-информационный вход/выход третьего типа, адресный вход пятого типа к первому и второму информационным входам триггера, вход "Синхронизация обмена с инверсией" подключен к входу защелки триггера, входы выбор адреса первого и второго типов подключены соответственно к первому и второму входам первого элемента И-НЕ, входы выбор адреса третьего и четвертого типов подключены соответственно к первому и второму входам второго элемента И-НЕ, вход "Чтение данных первого типа" подключен к первым входам первого элемента ИЛИ и третьего элемента И-НЕ, вход "Запись данных" подключен ко второму входу первого элемента И, вход "Синхронизация обмена" подключен к первому входу второго элемента И и второму входу третьего элемента И-НЕ, вход "Признак записи байта" подключен к первым входам четвертого и пятого элементов И-НЕ, входы "Запись младшего байта памяти", "Выбор кристалла памяти", "Разрешение памяти" подключены к одноименным выходам набора регистров, при этом в узле управления памятью первые прямой и инверсный выходы первого триггера подключены соответственно ко вторым входам четвертого и пятого элементов И-НЕ, вторые прямой и инверсный выходы первого триггера подключены к первому входу третьего элемента И, к второму и третьему входам которого подключены соответственно выходы первого и второго элементов И-НЕ, выход первого элемента И подключен к первым входам шестого и седьмого элементов И-НЕ, выходы которых подключены к первому и второму входам набора резисторов, вход стробирования триггера подключен к входу "Синхронизация обмена с инверсией" узла адресации, выход третьего элемента И через резисторную сборку подключен к выходу "Выбор кристалла памяти", к второму входу первого элемента И, к третьему входу которого подключен выход первого элемента ИЛИ, выход третьего элемента И-НЕ через резисторную сборку подключен к выходу "Разрешение памяти", выходы четвертого и пятого элементов И-НЕ подключены соответственно к вторым входам шестого и седьмого элементов И-НЕ, выход второго элемента И подключен к выходу "Ответ устройства" узла управления памятью, на первые выходы с первого по четвертый элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены соответственно адресные шины шестого типа, вторые входы которых соединены с шиной логического нуля микроЭВМ, выходы элементов с первого по четвертый ИСКЛЮЧАЮЩЕЕ ИЛИ подключены соответственно к первым и вторым выходам восьмого и девятого элементов И-НЕ, выходы которых подключены соответственно к первому и второму входам второго элемента ИЛИ, выход последнего подключен к первому информационному входу второго триггера, второй информационный вход которого соединен с входом "Выборка устройства", вход стробирования второго триггера соединен с входом "Синхронизация обмена с инверсией", первый прямой выход и второй инверсный выход второго триггера подключены соответственно к выходам выбора расширения адреса первого и второго типа узла управления памятью и к одноименным входам узла адресации.

Причем в узле адресации вход "Выбор расширения адреса" первого типа подключен к входам стиробирования первого и второго дешифратора, вход "Выбор расширения адреса" второго типа подключен к первому и второму входам разрешения второго дешифратора.

Узел дешифраторов содержит два дешифратора, узел программируемой матрицы содержит программируемую матрицу, приемопередатчик, два элемента И, два элемента ИЛИ, элемент НЕ, устройство ввода содержит четыре регистра, четыре формирователя на три состояния, мультиплексор, два элемента перепрограммируемой памяти, при этом в узле регистра состояния с первого по третий входы селекции мультиплексоров подключены соответственно к адресным входам третьего, четвертого и второго битов, вход "Останов" подключен к пятому и восьмому входам "Данные" первого мультиплексора, вход "Разрешение ввода" подключен к первому и четвертому входам "Данные" второго мультиплексора, к пятому и восьмому входам "Данные" которого подключен вход "Разрешение вывода", вход "Готов ввод" подключен к первому и четвертому входам "Данные" третьего мультиплексора, к пятому и восьмому входам которого подключен вход "Готов вывод", входы "Разрешение" с первого по третий мультиплексоров с первого по четвертый, шестой и седьмой входы "Данные" первого мультиплексора, второй и третий, шестой и седьмой входы "Данные" второго и третьего мультиплексоров подключены к общей шине микроЭВМ, выходы с первого по третий мультиплексоров подключены соответственно через элементы развязки на три состояния к адресно-информационным выходам нулевого, шестого и седьмого битов, к входам "Разрешение" с первого по третий элементов развязки на три состояния подключен вход "Чтение регистра состояния", входы "Ошибка четности", "Ошибка стопового бита", "Ошибка переполнения" подключены соответственно через четвертый, пятый и шестой элементы развязки на три состояния к адресно-информационным выходам с двенадцатого по четырнадцатый битов узла регистра состояния, вход "Управление входом" подключен к входам "Разрешение" с четвертого по шестой элементов развязки на три состояния.

Причем в узле селектора адреса вход первого вектора подключен к первому векторному входу первого приемопередатчика, к второму и третьему векторным входам которого подключен вход шестого вектора, вход "Разрешение выбора адреса" первого приемопередатчика подключен к входу узла селектора адреса "Запись данных", входы второго и третьего векторов подключены соответственно к первому и второму векторным входам второго приемопередатчика, к третьему векторному входу которого подключены входы четвертого и шестого векторов, с первого по третий входы выбора адресов первого и второго приемопередатчиков и вход "Разрешение выбора адреса" третьего приемопередатчика подключены к шине нулевого потенциала микроЭВМ, вход "Разрешение выбора адреса" второго приемопередатчика подключен к шине логической единицы микроЭВМ, инверсные выходы с первого по третий приемопередатчиков подключены соответственно к входам/выходам узла селектора адреса нулевого, второго, шестого, седьмого, первого, с третьего по пятый, пятнадцатый и с двенадцатого по четырнадцатый битов, прямые выходы соответственно подключены к одноименным выходам узла селектора адреса, выход "Сравнение адреса" третьего приемопередатчика через элемент НЕ, элемент развязки на три состояния подключен к адресно-информационному входу/выходу пятнадцатого бита, входы передачи четвертого и пятого приемопередатчиков и вход "Разрешение" программируемой матрицы подключены к шине нулевого потенциала микроЭВМ, входы "Разрешение кристалла" и "Разрешение передачи" четвертого и пятого приемопередатчиков подключены к шине единичного потенциала микроЭВМ, адресно-информационные входы с нулевого по двенадцатый битов подключены соответственно к первому по тринадцатый входам программируемой матрицы, к пятнадцатому входу которой подключен вход "Сигнал выбора устройства" с первого выхода пятого приемопередатчика, к шестнадцатому входу подключена шина единичного потенциала микроЭВМ, первый выход программируемой матрицы подключен к выходу "Выборка устройства" узла селектора адреса, к выходу "Выбор пульта" которого подключен второй выход программируемой матрицы, с первого по четвертый входы/выходы пятого приемопередатчика подключены соответственно к магистральным входам/выходам "Выборка устройства", "Запись данных", "Синхронизация обмена", Чтение данных" узла селектора адреса, при этом в узле логики управления адресно-информационный вход третьего бита и "Вход готов" подключены соответственно к первому и второму входам первого элемента ИЛИ, вход синхронизация обмена подключен к входу тактирования набора D-триггеров и к первому входу второго элемента ИЛИ, ко второму входу которого подключен вход "Устройство выбрано с инверсией", выход второго элемента ИЛИ подключен к входу "Сброс" набора D-триггеров, вход "Чтение данных" первого типа через первый элемент НЕ подключен в первому входу первого элемента ИЛИ-НЕ, к второму входу которого подключен вход "Устройство выбрано с инверсией", вход "Запись данных" подключен к первому входу первого элемента И, выход которого подключен к первому входу третьего элемента ИЛИ и через второй элемент НЕ к первому входу второго элемента ИЛИ-НЕ, ко второму входу которого подключен адресный вход нулевого бита, выход второго элемента ИЛИ-НЕ подключен к выходу "Запись младшего байта" узла логики управления, вход "Чтение данных третьего типа" и адресный вход второго бита подключены соответственно к первому и второму входам третьего элемента ИЛИ-НЕ, выход которого подключен к выходу "Чтение регистра состояния" узла логики управления, вход "Ошибка стопового бита" через первый передатчик подключен к выходу "Останов" узла логики управления, адресные входы первого и второго бита подключены соответственно к первому и второму входам второго элемента И-НЕ, выход которого подключен к адресному выходу второго типа узла логики управления, выход третьего элемента ИЛИ подключен к первому входу четвертого элемента ИЛИ, выход которого подключен на первый вход четвертого элемента ИЛИ-НЕ, на второй вход последнего подключена шина пятого вектора, выход четвертого элемента ИЛИ-НЕ через третий элемент НЕ подключен на первый вход второго передатчика, адресный вход первого бита через четвертый элемент НЕ подключен к адресному выходу с инверсией узла логики управления, вход "Выборка устройства", адресно-информационные входы первого и второго типа подключены соответственно к первому по третий входам набора D-триггеров, к четвертому входу которого подключен выход первого элемента ИЛИ, адресно-информационные входы четвертого и нулевого битов подключены к пятому и шестому входам набора D-триггеров, первый выход "Устройство выбрано" набора D-триггеров подключен к второму входу первого элемента И, к первому и второму входам второго передатчика и к первому информационному входу одновибратора, второй информационный вход которого подключен к шине нулевого потенциала микроЭВМ, сбросовый вход одновибратора подключен к шине логической единицы микроЭВМ, инверсный выход подключен к второму входу третьего передатчика, выход которого подключен к выходу "Ответ устройства" узла логики управления, к выходам последнего подключены адресные выходы набора D-триггеров с нулевого по четвертый битов, вход "Чтение данных третьего типа" подключен ко второму входу третьего элемента ИЛИ и через пятый элемент НЕ к выходу "Чтение пятого типа" узла логики управления.

Причем в узле дешифраторов адресные входы первого и второго битов подключены соответственно к первому и второму адресным входам первого и второго дешифратора, с первого по четвертый выходы первого дешифратора подключены соответственно к выходам "Загрузка регистра страницы старшего байта", "Загрузка системного регистра старшего байта", "Загрузка регистра страницы младшего байта", "Загрузка системного регистра младшего байта" узла дешифраторов, с первого по третий выходы второго дешифратора подключены соответственно к выходам узла дешифраторов "Чтение регистра страницы", "Чтение системного регистра", "Чтение регистра конфигурации", при этом в узле программируемой матрицы магистральные адресно-информационные входы/выходы с восьмого по одиннадцатый битами подключены с первого по четвертый магистральным входам/выходам приемопередатчика, с первого по четвертый входы/выходы которого подключены к адресно-информационным входам/выходам с восьмого по одиннадцатый битами узла программируемой матрицы, с первого по третий адресные входы приемопередатчика подключены к шине нулевого потенциала микроЭВМ.

В устройстве ввода адресно-информационные входы/выходы с нулевого по седьмой битами подключены соответственно к входу первого регистра, к входам первого и третьего формирователя на три состояния, к входам третьего регистра, выходами первого элемента перепрограммируемой памяти, второго формирователя на три состояния подключены соответственно к первому по седьмой адресным входам первого и второго элементов перепрограммируемой памяти, адресно-информационные входы-выходы второго типа с восьмого по пятнадцатый битами подключены соответственно к входам четвертого регистра, входам третьего формирователя, входам второго элемента перепрограммируемой памяти, данные регистра состояния с нулевого по седьмой битами соответственно подключены к входам первого регистра, к входам первого формирователя на три состояния, к селекторным входам мультиплексора, с первого по четвертый выходы которого подключены соответственно к восьмому по одиннадцатый адресным входам первого и второго элементов перепрограммируемой памяти, у которых входы "Разрешение обращения" подключены к нулевому потенциалу микроЭВМ, входы "Разрешение выхода" подключены к входу "Чтение памяти с инверсией", входы "Запись считывания" подключены к шине единичного потенциала микроЭВМ, вход "Чтение регистра страницы" подключен к первым и вторым входам разрешения первого и второго формирователя на три состояния, вход "Чтение регистра конфигурации" подключен к первому и второму входам разрешения третьего формирователя на три состояния и первому входу разрешения четвертого формирователя, второй вход разрешения которого подключен к общей шине микроЭВМ, вход "Загрузка страницы младшего байта" подключен к входу тактирования первого регистра, вход "Загрузка страницы старшего байта" подключен к входу тактирования второго регистра, вход "Сброс" подключен к входам сброс третьего и четвертого регистров, адресно-информационный вход первого типа восьмого бита подключен к входу разрешения мультиплексора, в узел дешифраторов включены набор D-триггеров, элемент НЕ и два элемента ИЛИ, при этом узел селектора адреса выходом "Авария источника питания" подключен к одноименному входу устройства ввода, выходами "Синхронизация обмена", "Выбор адреса устройства ввода", "Выбор устройства ввода" подключен соответственно к одноименным входам узла дешифраторов, узел логики управления входами "Сброс регистра", "Запись устройства ввода" подключены соответственно к одноименным входам узла дешифраторов, вход "Управление ответом ошибки" подключен к одноименному выходу программируемой матрицы, выход "Устройство выбрано" подключен к одноименным входам узла дешифраторов и программируемой матрицы, адресный выход первого типа подключен к одноименному входу узла дешифраторов, устройство ввода выходом "Разрешение устройства ввода с инверсией" подключено к одноименному входу дешифраторов, выходом "Управление ответом ошибки с инверсией" подключен к одноименному входу узла логики управления, узел дешифраторов выходами "Разрешение устройства ввода", "Выбор внешнего устройства" и "Разрешение адреса устройства ввода" подключены соответственно к одноименным входам узла программируемой матрицы, узел программируемой матрицы выходами "Управление ответом ошибки", "Чтение устройства ввода" подключены соответственно к одноименным входам устройства ввода, выходом "Чтение входного буфера с инверсией" подключен к одноименному входу узла селектора адреса, выходами "Управление первого типа" по "Управление шестого типа" подключен к одноименным входам узла селектора адреса, выходом "Векторная шина седьмого типа" подключен к одноименному входу узла логики управления, выход "Запись устройства ввода" подключен к одноименному входу узла дешифраторов, входами "Чтение данных первого типа", "Запись данных", "Синхронизация обмена" подключен соответственно к одноименным выходам узла селектора адреса, входами "Чтение входного буфера", "Чтение регистра состояния", "Чтение пятого типа" подключен соответственно к одноименным выходам узла логики управления, входом "Векторная шина четвертого типа" подключен к одноименному выходу приемопередачи.

Причем в устройстве ввода входы "Авария источника питания", "Чтение устройства ввода", "Управление ответом ошибки", "Управление устройством ввода" подключены соответственно к одноименным входам четвертого формирователя с тремя состояниями, выход которого "Сброс" подключен к вторым входам разрешения первого и второго регистров, выход "Чтение памяти с инверсией" подключен к третьим входам разрешения первого и второго элементов памяти, выходы "Управление ответом ошибки с инверсией" и "Разрешение устройства ввода с инверсией" подключены к одноименным выходам устройства ввода, при этом в узле дешифраторов вход "Запись устройства ввода" подключен к входу элемента НЕ и к первому входу первого элемента ИЛИ, выход которого подключен к выходу "Управление устройством ввода" узла, выход элемента НЕ подключен к первому и второму входам выбора первого дешифратора, вход "Чтение устройства ввода" подключен к информационному входу второго дешифратора и второму входу первого элемента ИЛИ, вход "Устройство выбрано" подключен к первому входу второго элемента ИЛИ, выход которого подключен к выходу "Выбор внешнего устройства" узла, вход "Разрешение устройства ввода с инверсией" подключен к входу разрешения первого дешифратора, к первому входу выбора второго дешифратора, входы "Выбор адреса устройства ввода", "Выбор устройства ввода", адресно-информационные шины первого типа с пятого по восьмой битами подключены соответственно с первого по шестой входам набора D-триггеров, входы "Синхронизация обмена" и "Сброс регистра" подключены соответственно к входам тактирования и сброса набора D-триггеров, первый выход которого подключен к выходу "Разрешение адреса устройства ввода" узла, второй выход набора D-триггеров подключен в первому информационному входу первого дешифратора, к второму входу второго элемента ИЛИ и к выходу узла "Разрешение устройства ввода", с третьего по шестой выходы набора D-триггеров подключены соответственно к адресным шинам с пятого по восьмой битами выходами узла.

Причем в узле программируемой матрицы входы "Управления седьмого" и "восьмого типов" подключены соответственно к первому и второму входам разрешения приемопередатчика, элемент программируемой матрицы с первого по четвертый адресными входами подключен соответственно к входу узла, вход "Чтение входного буфера" подключен к входу элемента НЕ, выход которого "Чтение входного буфера с инверсией" подключен к пятому адресному входу программируемой матрицы и к выходу узла, адресный вход первого бита подключен к шестому и восьмому адресным входам элемента программируемой матрицы, адресный вход второго бита подключен к седьмому адресному входу программируемой матрицы, входы узла "Чтение данных первого типа", "Запись данных", "Устройство выбрано", "Разрешение устройства ввода" подключены соответственно с восьмого по тринадцатый адресным входам элемента программируемой матрицы, с четырнадцатого по шестнадцатый входы элемента программируемой матрицы подключены к шине единичного потенциала микроЭВМ, вход разрешения элемента программируемой матрицы подключен к шине нулевого потенциала микроЭВМ, выходы элемента программируемой матрицы с "Управление первого типа" по "Управление восьмого типа" подключены соответственно к одноименным выходам узла программируемой матрицы, вход "Выбор внешнего устройства" подключен к первому входу первого элемента ИЛИ, вход "Разрешение адреса устройства ввода" подключен к второму входу первого элемента ИЛИ, выход которого "Управление ответом ошибки" подключен к выходу узла, вход "Запись данных" подключен к первому входу первого элемента И, к второму входу которого подключен вход "Разрешение устройства ввода", выход первого элемента И подключен к выходу "Запись устройства ввода" узла, вход "Векторная шина четвертого типа" подключен к первому входу второго элемента ИЛИ, выход которого подключен к выходу "Векторная шина шестого типа" узла, входы "Чтение данных первого типа", "Разрешение устройства ввода" подключены соответственно к первому и второму входам второго элемента И, выход которого подключен к выходу "Чтение устройства ввода" узла программируемой матрицы и к второму входу второго элемента ИЛИ, при этом в узле селектора адреса входы "Управление первого типа" по "Управление шестого типа" подключены соответственно к первым и вторым входам разрешения с первого по третий приемопередатчиков, вход "Чтение входного буфера с инверсией" подключен к входу разрешения элемента "Развязки", к входу которого подключен выход элемента НЕ, выход элемента развязки подключен к выходу адресно-информационной шины пятнадцатого бита, магистральные входы/выходы "Признак записи байта" и "Авария источника питания" подключены к первому и второму магистральному входу/выходу четвертого приемопередатчика, первый вход/выход которого "Признак записи байта" подключен к четырнадцатому адресному входу элемента программируемой матрицы, второй вход/выход "Авария источника питания " Четвертого приемопередатчика подключен к входу/выходу узла селектора адреса, третий и четвертый выходы программируемой матрицы подключены соответственно к выходам "Выбор адреса устройства ввода", "Выбор устройства ввода" узла селектора адреса.

Причем в узле логики управления выход третьего элемента ИЛИ подключен к первому входу четверного элемента ИЛИ, вход узла "Управление устройства ввода" подключен к второму входу четвертого элемента ИЛИ, выход которого подключен к второму входу четвертого элемента И-НЕ, вход "Управление ответа ошибки с инверсией" подключен к второму выходу второго элемента ИЛИ, выход которого подключен к выходу узла "Сброс регистра", вход "Управление ответом ошибки" подключен к входу одновибратора.

Существенным отличием является введение в узел дешифраторов набора D-триггеров, элемента НЕ, двух элементов ИЛИ и введение новых связей в узлах логики управления, селектора адреса, программируемой матрицы, дешифраторов и устройства ввода. Данное техническое решение в научно-технической и патентной литературе не выявлено.

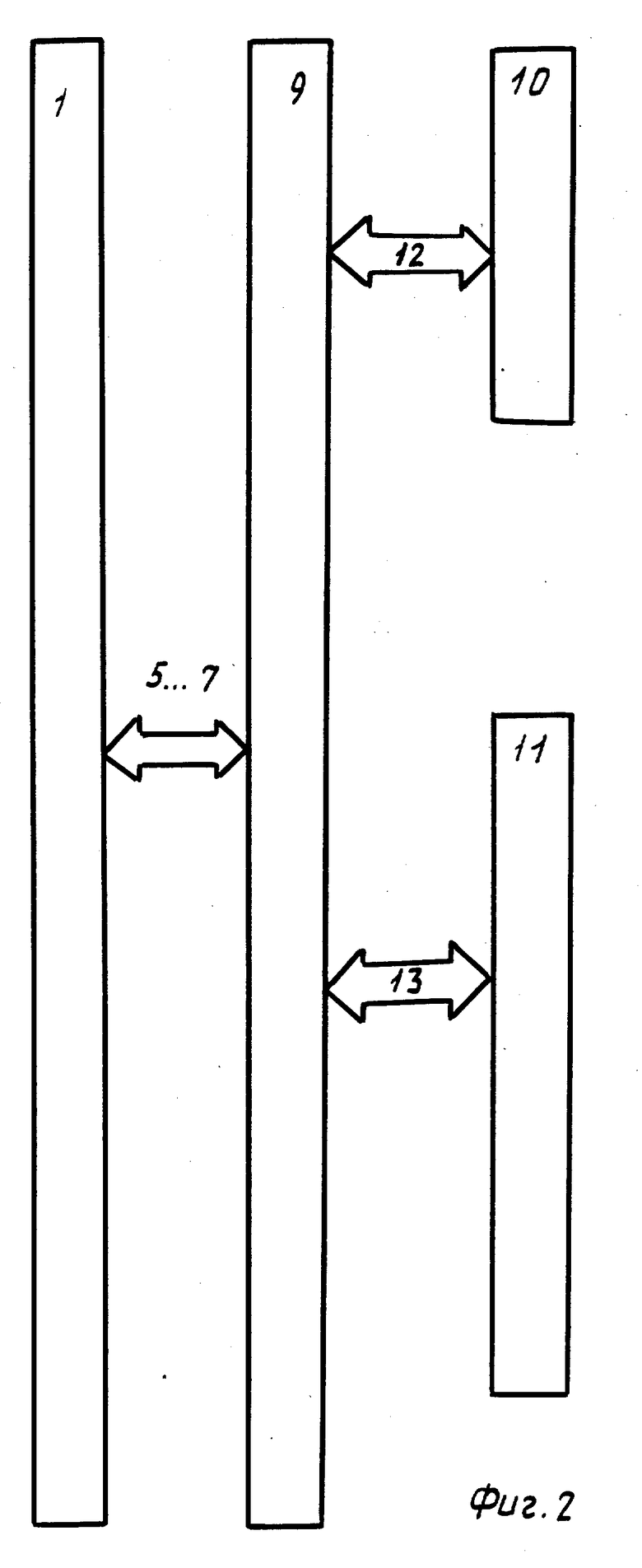

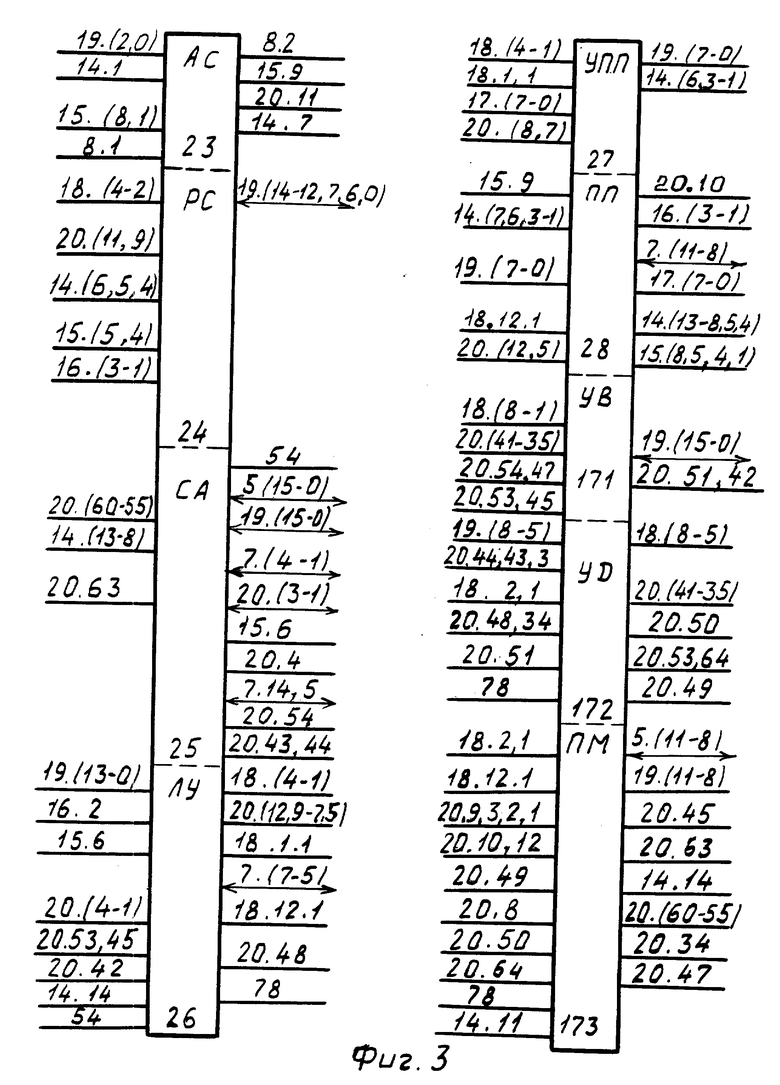

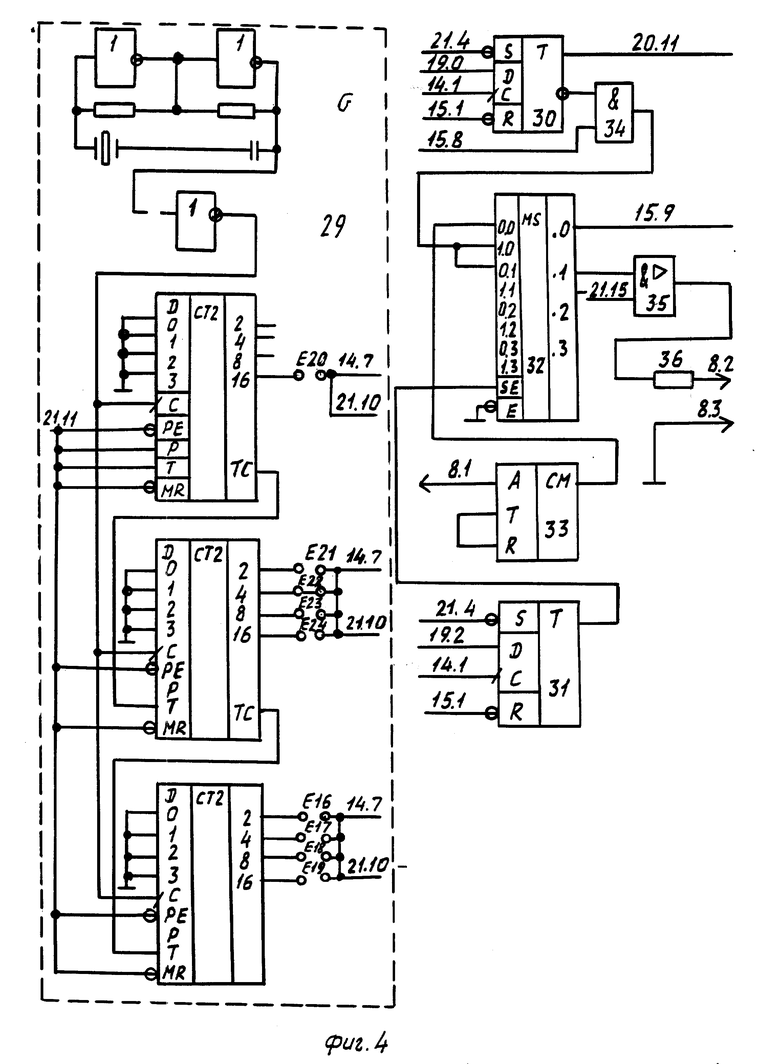

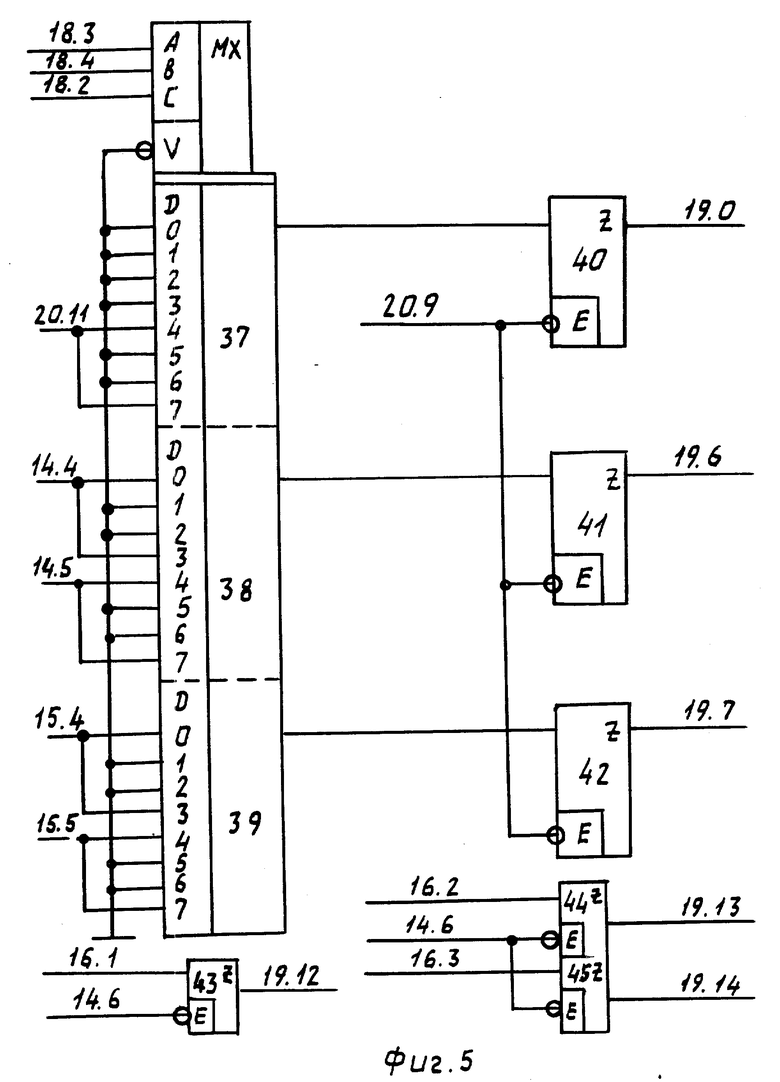

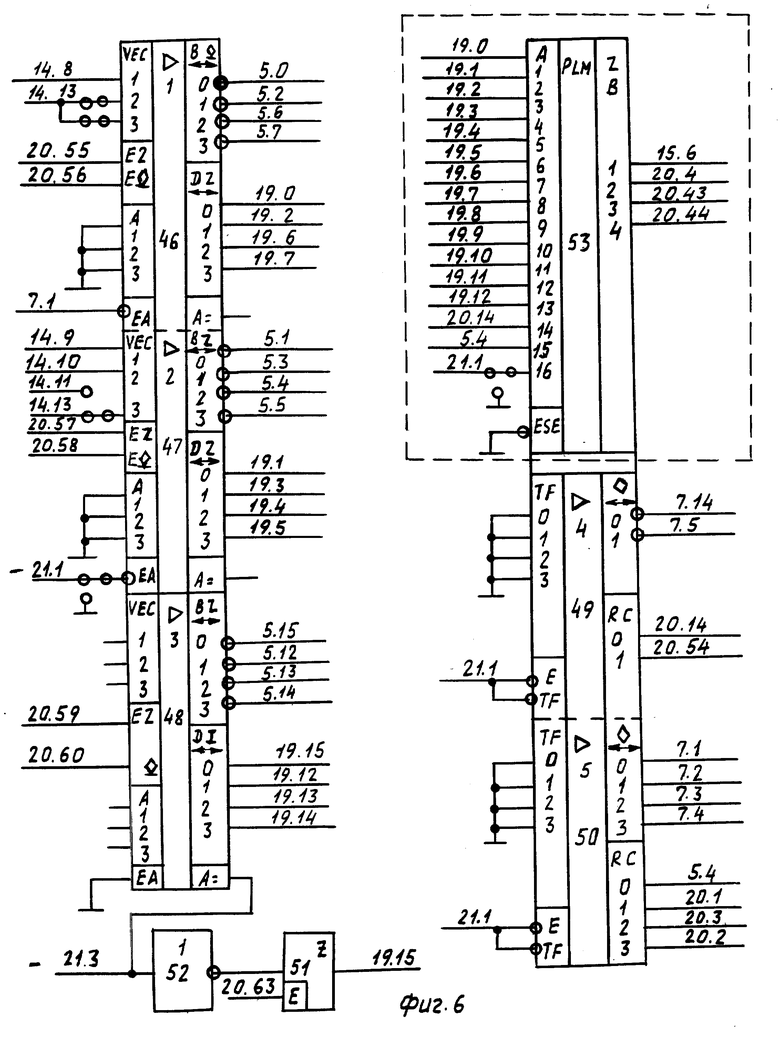

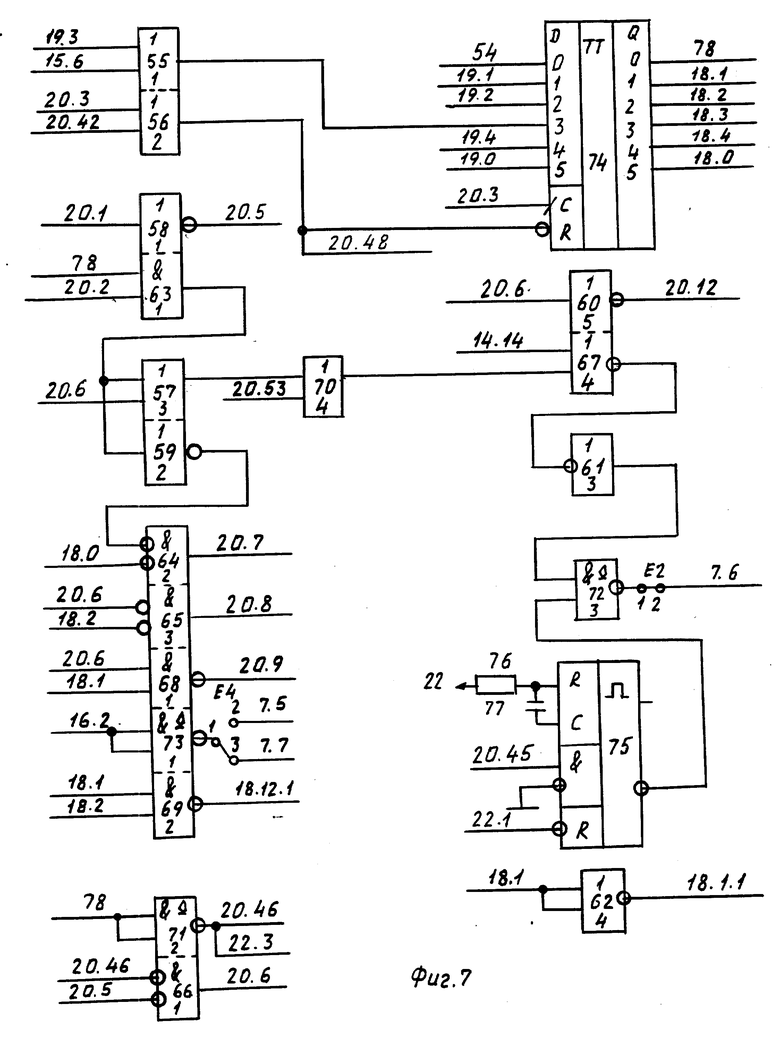

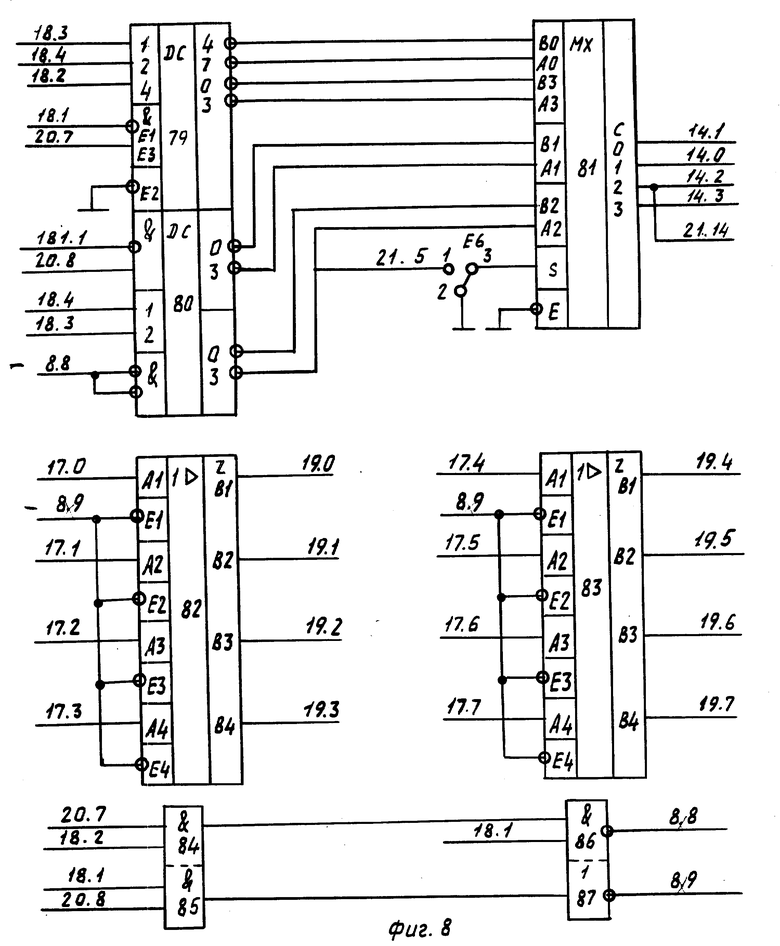

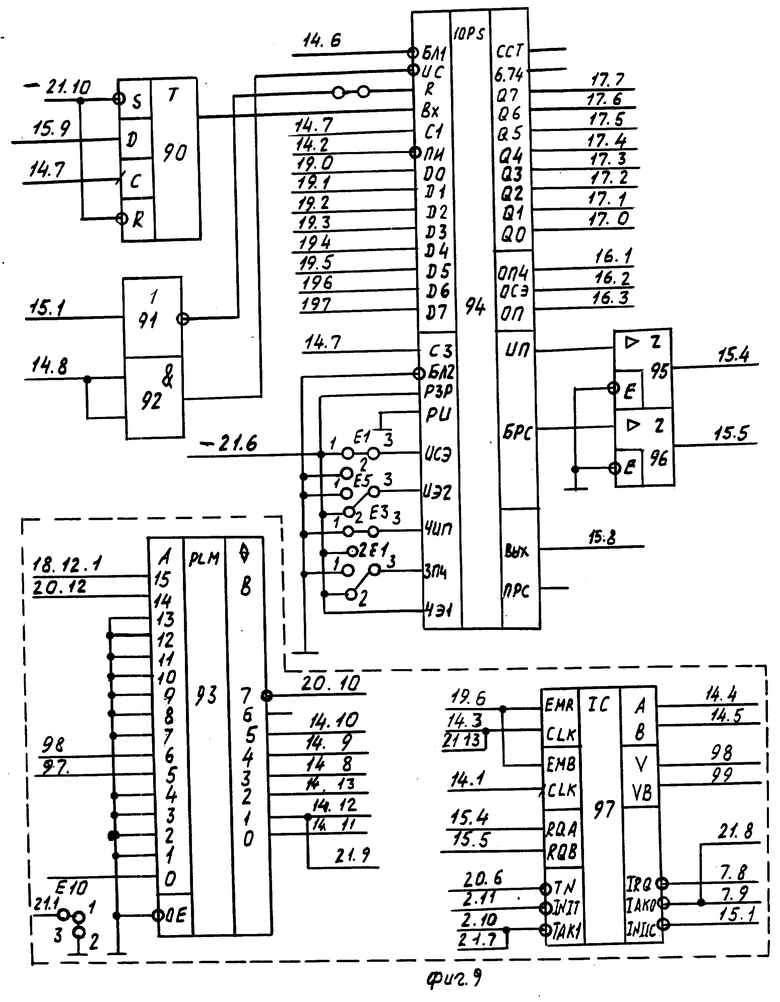

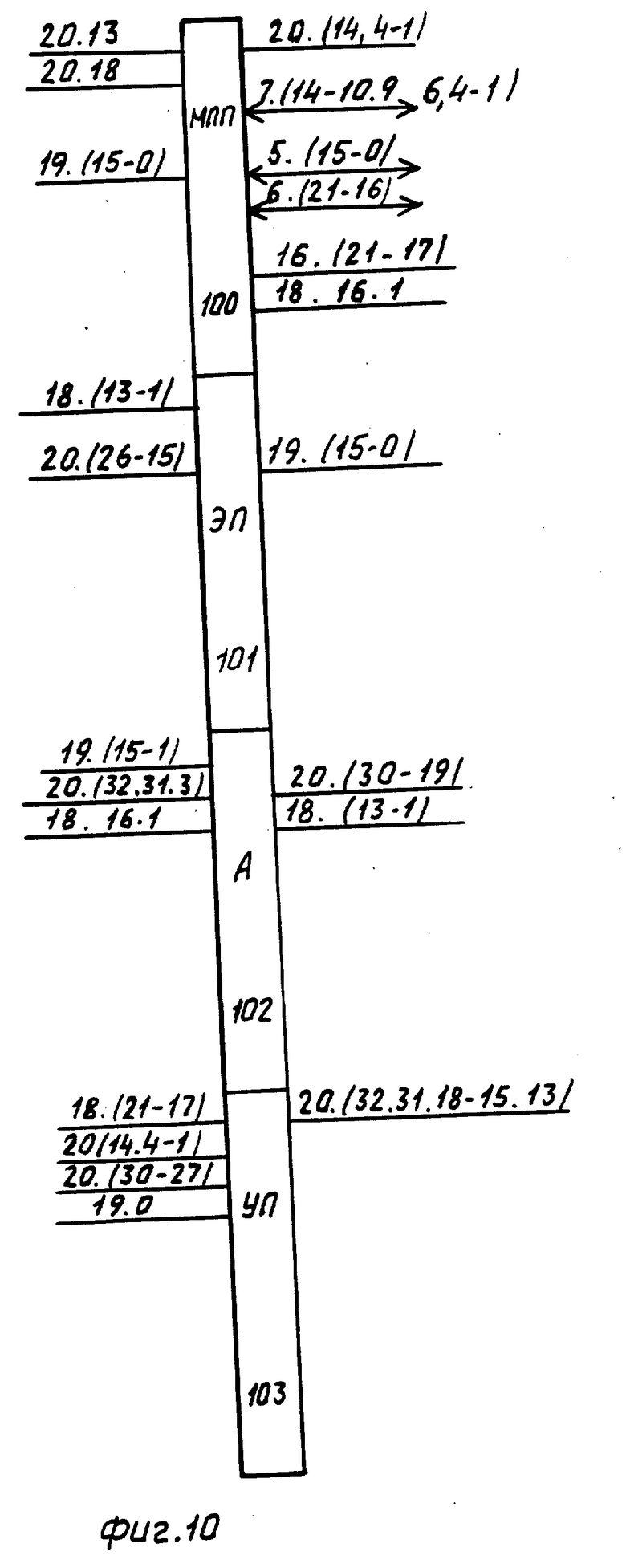

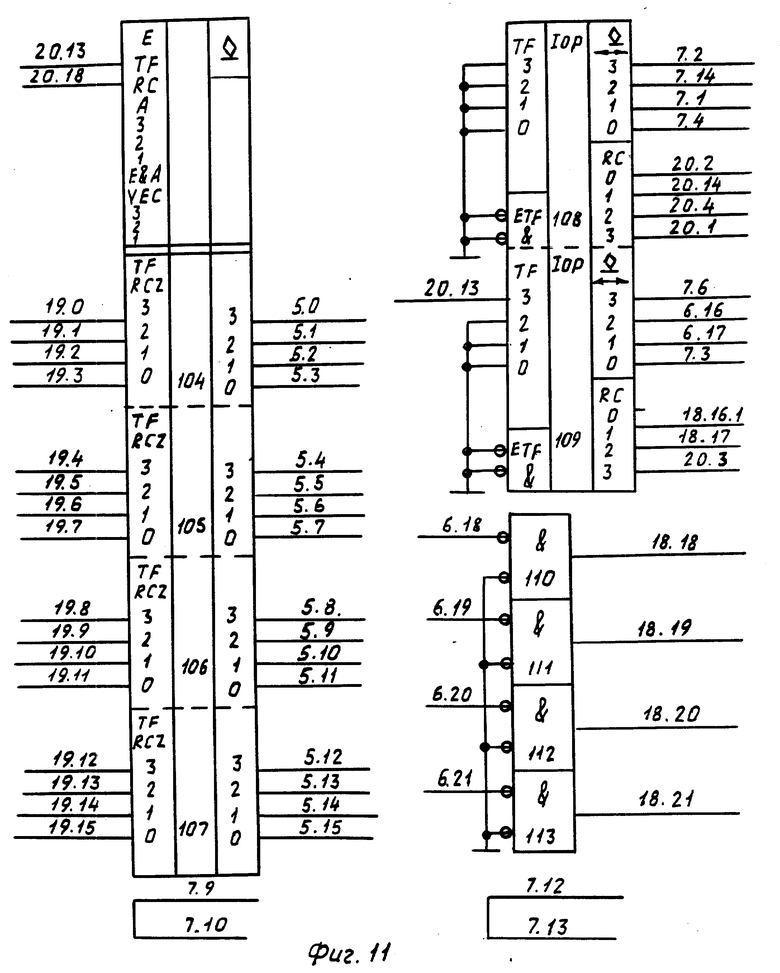

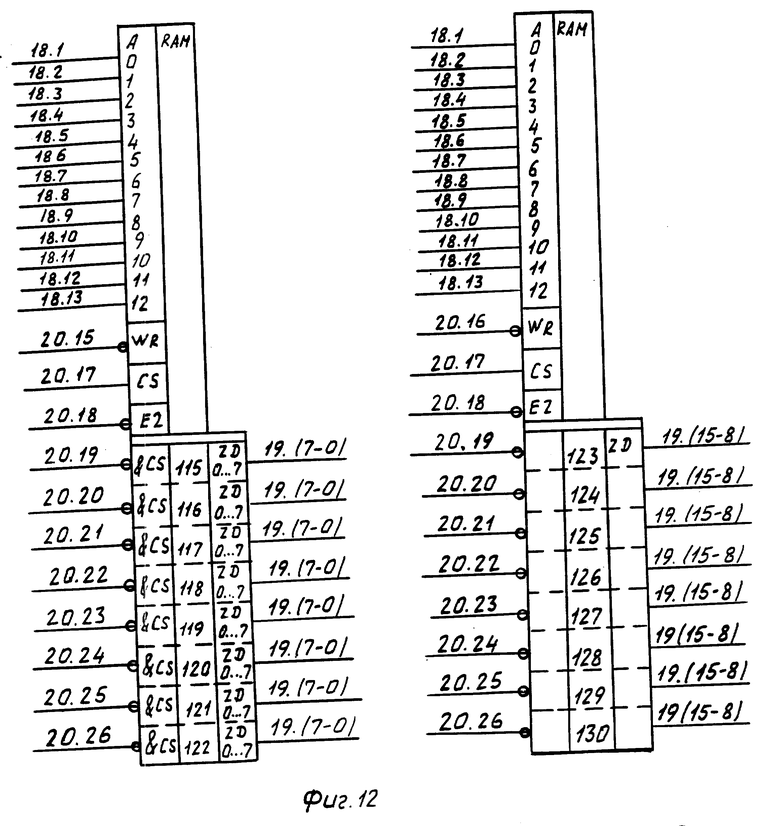

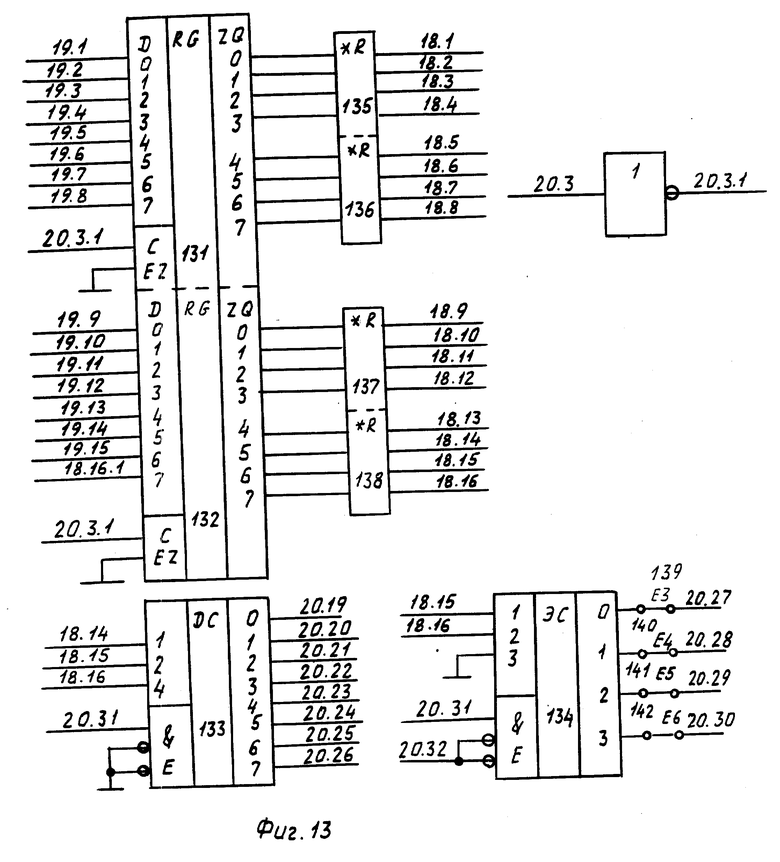

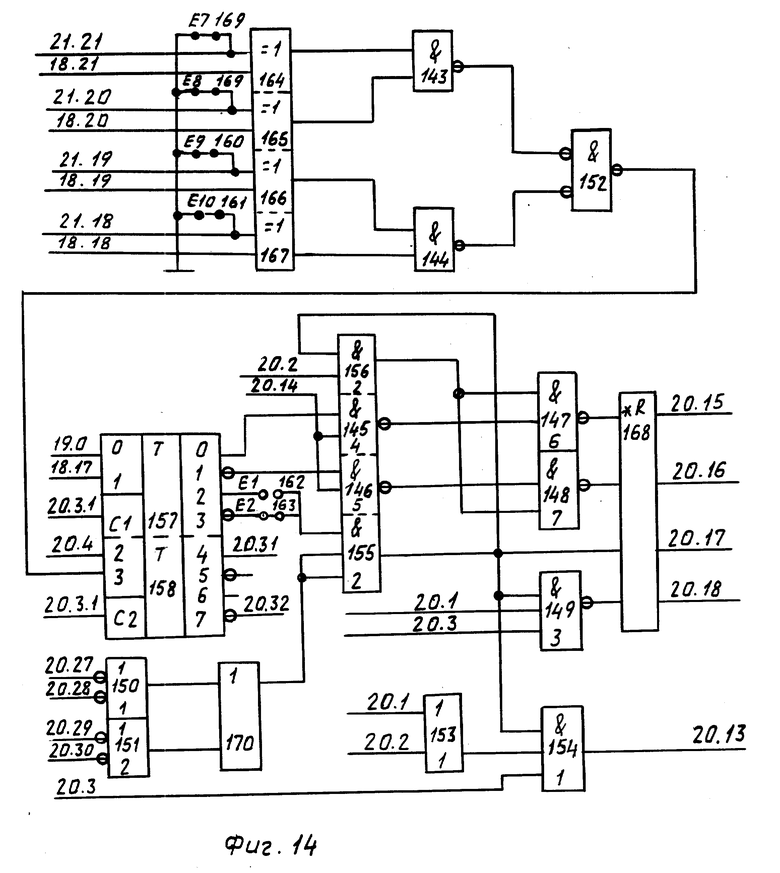

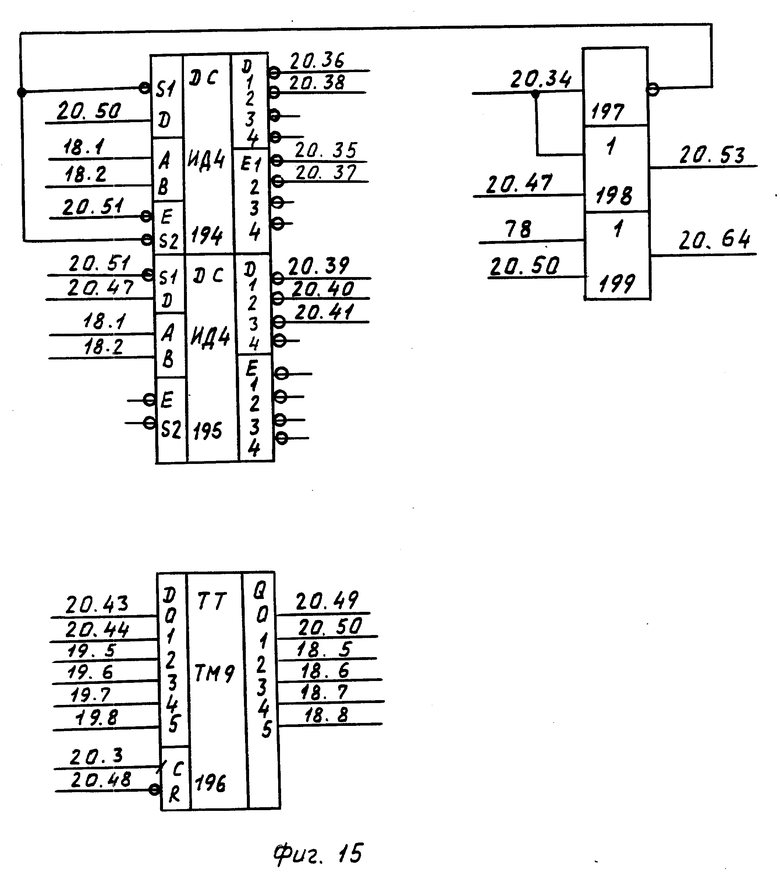

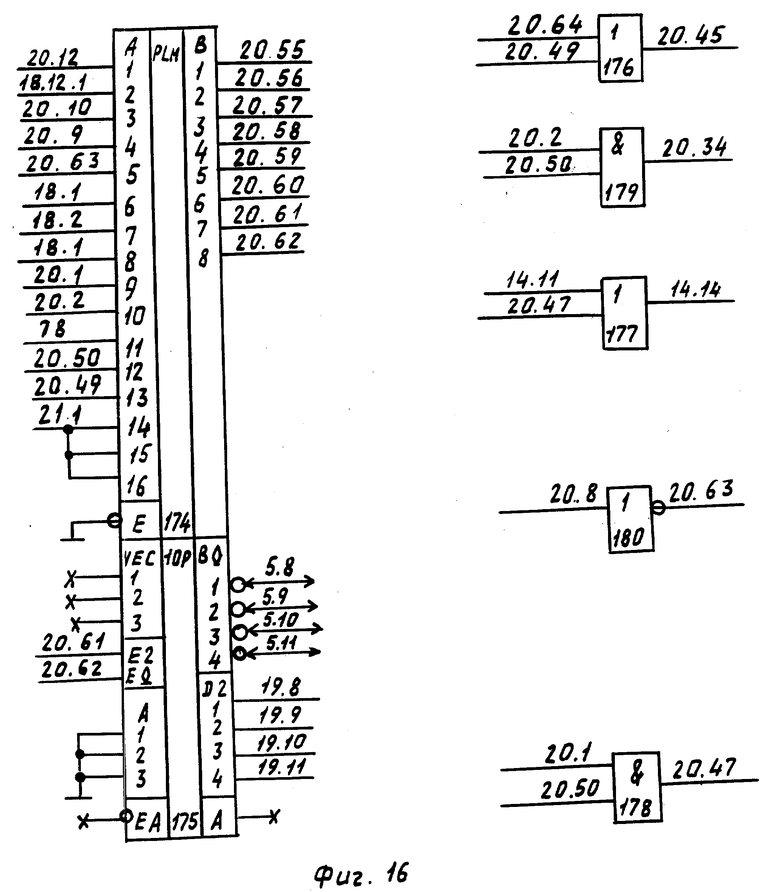

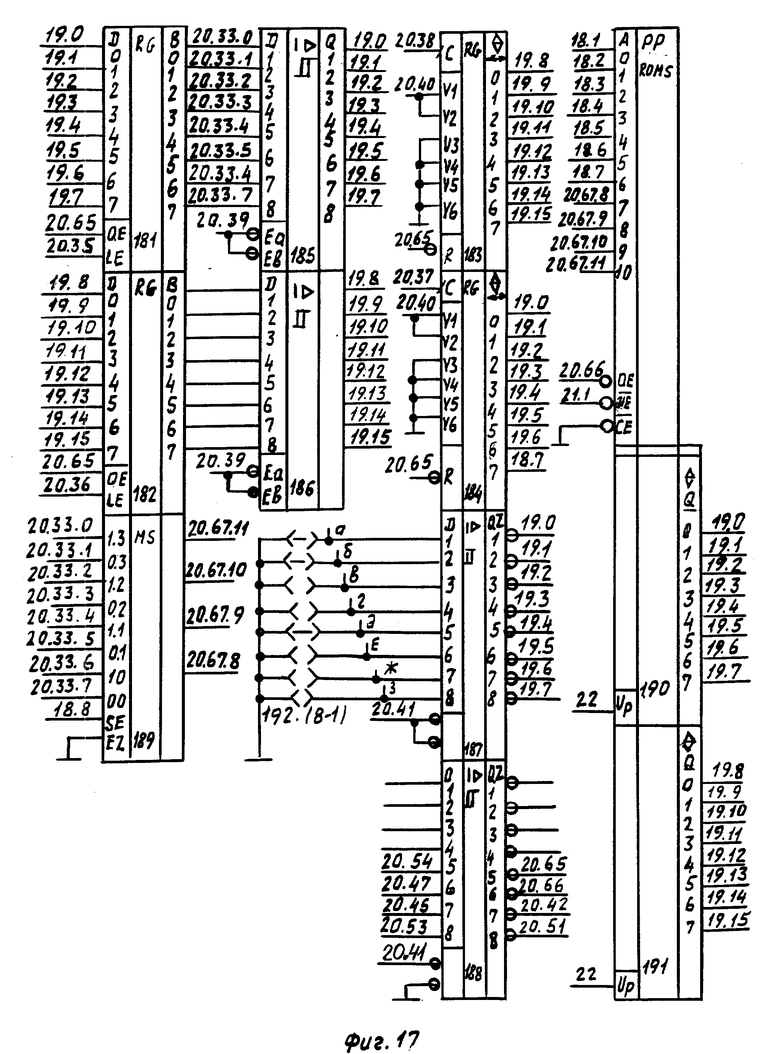

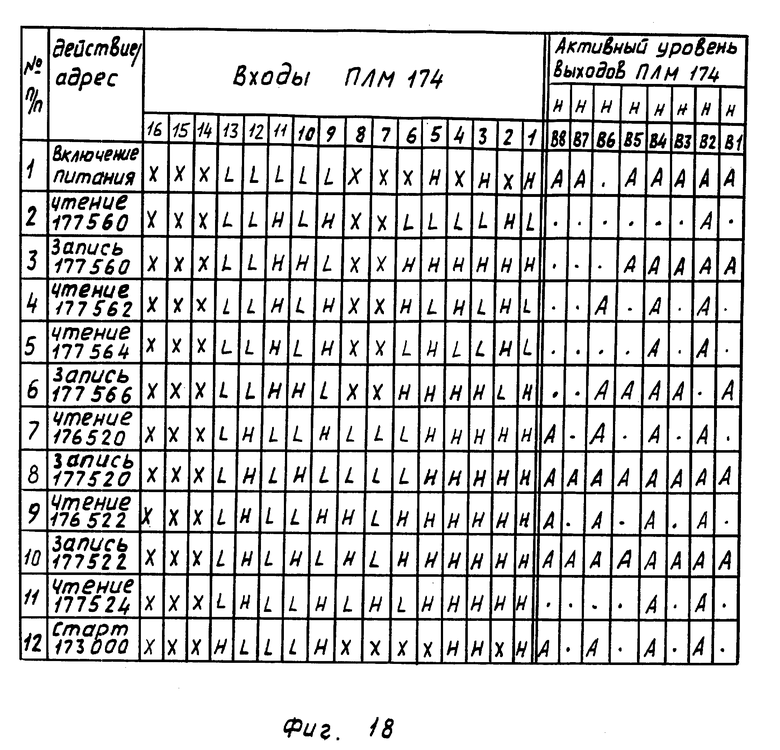

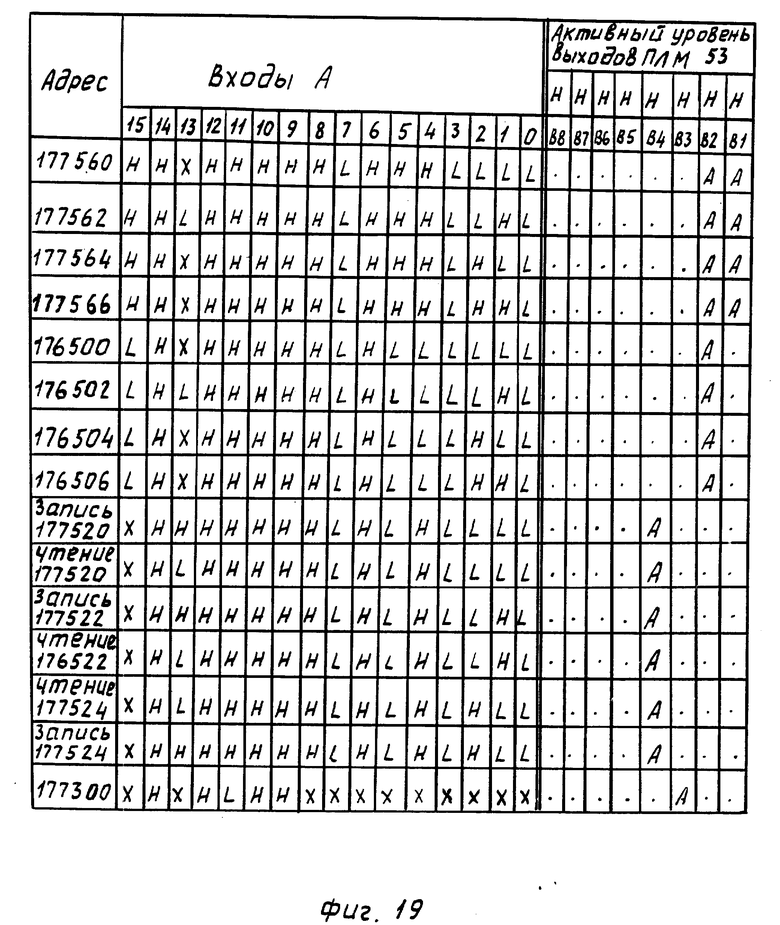

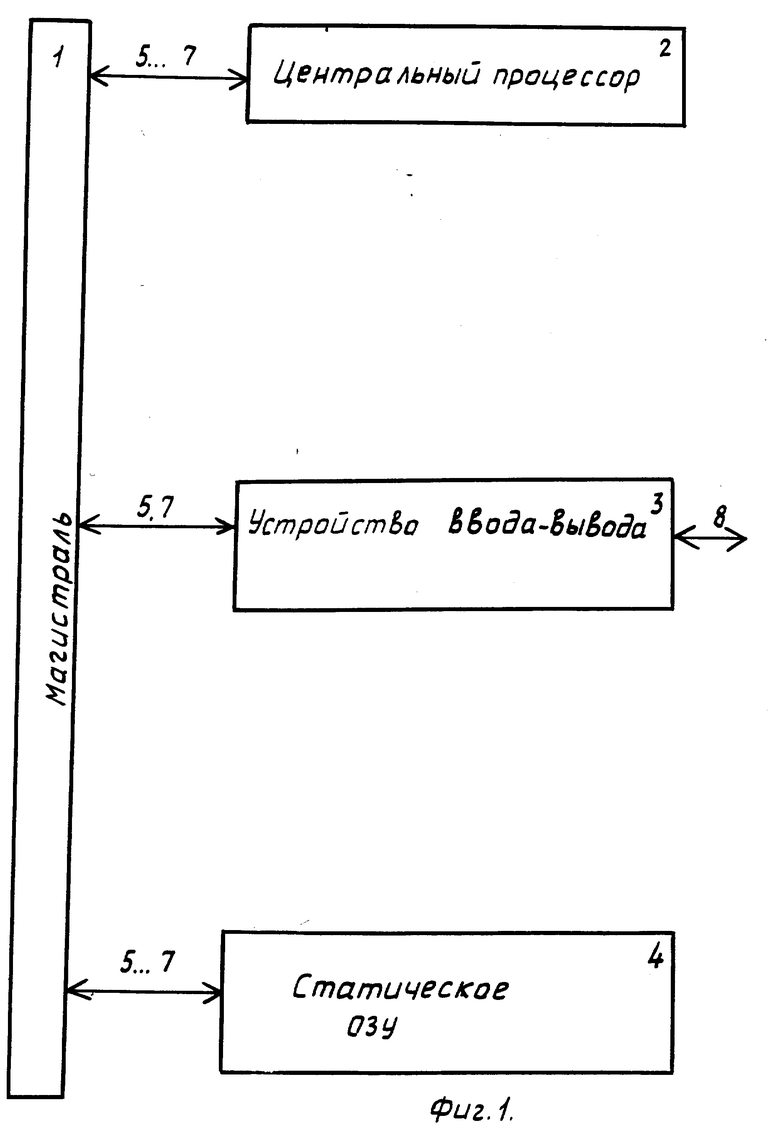

На фиг. 1 показана функциональная схема микроЭВМ; на фиг. 2 - схема центрального процессора; на фиг. 3 - схема устройства ввода-вывода; на фиг. 4 - принципиальная электрическая схема узла адаптера связи; на фиг. 5 - узла регистра состояния; на фиг. 6 - узла селектора адреса; на фиг. 7 - узла логики управления; на фиг. 8 - узла управления приемопередачей; на фиг. 9 - узла приемопередачи, на фиг. 10 - функциональная схема статического оперативного запоминающего устройства; на фиг. 11 - принципиальная электрическая схема узла магистральных приемопередатчиков; на фиг. 12 - узла элементов памяти; на фиг. 13 - узла адресации; на фиг. 14 - узла управления памятью; на фиг. 15 - узла дешифраторов; на фиг. 16 - узла программируемой матрицы; на фиг. 17 - устройство ввода; на фиг. 18, 19 - таблицы состояния элементов программируемых логических матриц 174 и 93.

МикроЭВМ (фиг. 1) содержит магистраль 1, центральный процессор 2, устройство ввода-вывода 3, статическое запоминающее устройство 4, магистральные вводы-выводы 5 - 7, шины токовой петли 8, причем центральный процессор 2 (фиг. 2) содержит устройство сопряжения с магистралью 9, сверхоперативное запоминающее устройство 10, устройство обработки данных 11, шины ввода-вывода 12, 13, при этом устройство ввода-вывода 3 содержит шины управления 14 - 16, адресно-информационные входы/выходы, 17, адресные входы 18, адресно-информационные шины 19, шины управления 20, шина логической единицы микроЭВМ 21, шина питания плюс 5 В 22, узел адаптера связи 23, узел регистра состояния 24, узел селектора адреса 25, узел логики управления 26, узел управления приемопередачей 27, узел приемопередачи 28, причем узел адаптера связи 23 (фиг. 3, 4) содержит генератор импульсов 29, триггеры 30, 31, мультиплексор 32, приемник 33, элемент И 34, передатчик 35, ограничительный элемент 36, узел регистра состояния 24 (фиг. 3, 5) содержит мультиплексоры 37 - 39, элементы развязки на три состояния 40 - 45, узел селектора адреса 25 (фиг. 3, 6) содержит приемопередатчики 46 - 50, элементы НЕ 51, элемент развязки 52, программируемую логическую матрицу 53, управляющую шину "Сигнала выбора устройства" 54, узел логики управления 26 (фиг. 3, 7) содержит элементы ИЛИ 55 - 57, элементы НЕ 58 - 62, элемент И 63, элементы ИЛИ-НЕ 64 - 67, элементы И-НЕ 68 - 69, элемент ИЛИ 70, передатчики 71 - 73, набор D-триггеров 74, одновибратор 75, ограничительный элемент 76, накопительный элемент 77, шина "Устройство выбрано" 78, узел управления приемопередачей 27 (фиг. 3, 8) содержит дешифраторы 79, 80, мультиплексор 81, элемент развязки на три состояния 82, 83, элементы И 84, 85, элемент И-НЕ 86, элемент НЕ 87, шина управления с инверсией 88, шина "Разрешение входного буфера" 89, узел приемопередачи 28 (фиг. 3, 9) содержит триггер 90, элемент НЕ 91, элемент ИЛИ 92, программируемую логическую матрицу 93, асинхронный приемопередатчик данных 94, элементы развязки на три состояния 95, 96, элемент прерывания 97, шины выбора первого и второго типа 98, 99, статическое оперативное запоминающее устройство 4 содержит узел магистральных приемопередатчиков 100, узел элементов памяти 101, узел адресации 102 и узел управления памятью 103, узел магистральных приемопередатчиков 100 (фиг. 10, 11) содержит приемопередатчики 104 - 109, приемники 110-113, элементы НЕ 114, узел элементов памяти 101 (фиг. 10-12) содержит элементы памяти 115-130, узел адресации 102 (фиг. 10, 13) содержит регистры 131, 132, дешифраторы 133, 134, элементы набора резисторов 135-138, перемычки 139-142, узел управления памятью 103 (фиг. 10, 14) содержит элементы И-НЕ 143-151, элементы ИЛИ 152, 153, элементы И 154, 156, триггеры 157, 158, перемычки 159-163, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 164-167, элемент набора резисторов 168, перемычка 169, элемент ИЛИ 170, устройство ввода 171, узел дешифраторов 172, узел программируемой матрицы 173, при этом узел программируемой матрицы 173 содержит элемент программируемой матрицы 174, приемопередатчик 175, элементы ИЛИ 176, 177, элементы И 178, 179, элемент НЕ 180, устройство ввода 171 содержит регистры 181-184, формирователи с тремя состояниями 185-188, мультиплексор 189, элементы программируемой памяти 190, 191, перемычки 192, 193, узел дешифраторов 172 содержит дешифраторы 194, 195, набор D-триггеров 196, элемент НЕ 197, элементы ИЛИ 198, 199, при этом магистральные адресно-информационные шины 5 содержат входы/выходы 5. (15-0), магистральные адресные шины 6 содержат входы/выходы 6. (21-16), магистральные адресные шины 7 содержат входы/выходы "Выборка устройства" 7.1, "Запись данных" 7.2, "Синхронизация обмена" 7.3, "Чтение данных" 7.4, "Авария источника питания" 7.5, "Ответ устройства" 7.6, "Останов" 7.7, "Запрос прерывания" 7.8, "Выходной сигнал предоставления прерывания" 7.9, "Входной сигнал предоставления прерывания" 7.10, "Установка" 7.11, "Входной сигнал разрешения захвата магистрали" 7.13, "Признак записи байта" 7.14, шины токовой петли 8 содержат вход "Прием данных" 8.1, выход "Передача данных" 8.2, шины управления 14 содержат шины входы-выходы "Регистр состояния выхода" 14.1, "Разрешение буфера" 14.2, "Регистр состояния входа" 14.3, "Разрешение ввода" 14.4, "Разрешение вывода" 14.5, "Управление входом" 14.6, "Синхронизация" 14.7, векторные шины 14. (8-14) содержат с первого по седьмой векторы, шины управления 15 содержат шины установки 15.1, "Управление с инверсией" 15.2, "Готов ввод" 15.4, "Готов вывод" 15.5, "Выбор пульта" 15.6, "Разрешение пульта" 15.7, "Управление выходными данными" 15.8, "Управление входными данными" 15.9, шина управления 16 содержит "Ошибку четности" 16.1, "Ошибку стопового бита" 16.2, "Ошибку переполнения" 16.3, адресно-информационные входы-выходы 17 содержат входы/выходы 17.(7-0), адресные шины 18 содержат адресные входы 18. (13-1), адресный вход первого типа с инверсией 18.1.1, адресный вход второго типа 18.12.1, адресный вход третьего типа 18.16.1, адресный вход пятого типа 18.17, адресно-информационные шины 19 содержат входы/выходы 19.(15-1), адресно-информационные входы-выходы второго типа 19.(14-12, 7, 6, 0), адресно-информационные входы-выходы третьего типа 19 содержат входы-выходы 19.0, шины управления 20 содержат шины "Чтение данных первого типа" 20.1, "Запись данных" 20.2, "Синхронизация обмена" 20.3, "Синхронизация обмена с инверсией" 20.3.1, выборка устройства 20.4, "Чтение данных второго типа" 20.5, "Чтение данных третьего типа" 20.6, "Запись младшего байта" 20.7, "Чтение входного буфера" 20.8, "Чтение регистра состояния" 20.9, "Чтение четвертого типа" 20.10, "Останов" 20.11, "Чтение пятого типа" 20.12, "Ответ устройства" 20.13, "Признак записи байта" 20.14, "Запись младшего байта памяти" 20.15, "Запись старшего байта памяти" 20.16, "Выбор кристалла памяти" 20.17, "Разрешение памяти" 20.18, "Выбор элемента памяти" 20.(26-19), "Выбор адреса" 20.(20-37), "Выбор расширения памяти" 20.(32-31), "Данные регистра состояния" 20.33, (7-0), "Запись устройства ввода" 20.34, "Загрузка регистра страницы младшего байта" 20.35, "Загрузка регистра страницы старшего байта" 20.36, "Загрузка системного регистра младшего байта" 20.37, "Загрузка системного регистра старшего байта" 20.38, "Чтение регистра страницы" 20.39, "Чтение системного регистра" 20.40, "Чтение регистра конфигурации" 20.41, "Управление ответом ошибки с инверсией" 20.42, "Выбор адреса устройства ввода" 20.43, "Выбор устройства ввода" 20.44, "Управление ответом ошибки" 20.45, "Устройство выбрано с инверсией" 20.46, "Чтение устройства ввода" 20.47, "Сброс регистра" 20.48, "Разрешение адреса устройства ввода" 20.49, "Разрешение устройства ввода" 20.50, "Разрешение устройства ввода с инверсией" 20.51, "Чтение памяти с инверсией" 20.52, "Управление устройством ввода" 20.53, "Авария источника питания" 20.54, "Управление первого типа" по "Управление восьмого типа" 20.(62-55), "Чтение входного буфера с инверсией" 20.63, "Выбор внешнего устройства" 20.64, "Сброс" 20.65, "Чтение памяти с инверсией" 20.66, "Адрес регистра состояния" 20.67,(11-8),

Работа микроЭВМ осуществляется по следующему алгоритму.

1. С включением питания микроЭВМ в устройстве ввода-вывода 3 осуществляется:

- чтение и запись регистра состояния 177560,

- чтение регистра данных 177562,

- чтение регистра состояния 177564,

- запись регистра данных 177566,

- чтение и запись страницы 177520,

- чтение и запись системного регистра 177522,

- чтение регистра индикации 177524.

2. Со стартового адреса 173000 осуществляется загрузка из перепрограммируемых запоминающих устройств устройства ввода-вывода 3 в статическое запоминающее устройство 4.

3. Дальнейшая работа микроЭВМ с устройством ввода-вывода 3 осуществляется в режиме вывода информации.

После установки адресной части центральным процессором 2 через магистраль 1 и приемопередатчик 50 передается сигнал "Синхронизация обмена" 20.3 и сигнал "Чтение данных первого типа" 20.1 в режиме "Чтение данных" регистра состояния приемника 177560.

Сигнал "Синхронизация обмена" 20.3 высоким потенциалом защелкивает данные адреса 177560. С выхода набора D-триггеров 74 (фиг. 7) снимаются высокими потенциалами адресные шины 18.2,1 первого и второго битов и подаются на вход программируемой матрицы 174 (фиг. 16). Сигнал "Чтение данных первого типа" 20.1 высоким потенциалом поступает на вход программируемой матрицы 174 (фиг. 16), инвертируется в узле логики управления 26 (фиг. 7) на элементе НЕ 58 и поступает на вход элемента ИЛИ-НЕ 66, а с его выхода поступает через элемент НЕ 60 низким потенциалом на вход программируемой матрицы 174 (фиг. 16) как сигнал "Чтение пятого типа" 20.12. С выхода программируемой матрицы 93 низким потенциалом сигнал "Чтение четвертого типа" 20.10 поступает на вход программируемой матрицы 174 (фиг. 16).

При совпадении названных активных сигналов на входе программируемой матрицы 174, на ее выходе "Управление второго типа" 20.56 формируется активный уровень высокого потенциала, который поступает на второй вход управления приемопередатчиком 46 в узле селектора адреса 25 (фиг. 6).

При этом данные с регистра приемника устройства ввода-вывода 3 передаются через магистраль 1 в центральный процессор (ЦП) 2 о состоянии <7, 6, 2, 0> разрядов.

Если 7 разряд установлен в высокий потенциал, т.е. "Флаг установлен", то это свидетельствует о том, что входной буфер асинхронного приемопередатчика 94 узла приемопередачи 27 (фиг. 9) готов к приему передачи.

Цикл "Чтение" заканчивается формированием сигнала "Ответ устройства" в узле логики управления 26 (фиг. 7) и пересылка его через магистраль 1 в ЦП 2.

Сигнал "Ответ устройства" формируется по цепи: элемент НЕ 58, элемент ИЛИ-НЕ 66, элементы ИЛИ 57, 70, элемент ИЛИ-НЕ 67, элемент НЕ 61 и передатчик 72, ЦП 2 осуществляет операцию "Запись" регистра состояния 177560.

При этом в адресной части сигнал "Синхронизация обмена" 20.3 защелкивает адрес регистра состояния 177560 на наборе D-триггеров 74 и через приемопередатчик 50 передается сигнал "Запись данных" 20.2. Одновременно в адресной части центральным процессором (ЦП) 2 при обращении к внешним устройствам вырабатывается магистральный сигнал "Выборка устройства" 7.1, который поступает через приемопередатчик 50 высоким потенциалом "Выбор устройства" 54 и подается на вход программируемой матрицы 53 узла селектора адреса 26 (фиг. 6).

С выхода программируемой матрицы 53 сигнал "Выборка устройства 20.4 высоким потенциалом защелкивается в наборе D-триггеров 74 узла логики управления 26 и высоким потенциалом "Устройство выбрано" 78 подается на вход элемента И 63 для разрешения прохождения высоким потенциалом сигнала "Запись данных" 20.2. Сигнал "Запись данных" 20.2 одновременно поступает на вход программируемой матрицы 174 (фиг. 16) и при записи по адресу 177560 на ее выходе формируются высоким потенциалом сигналы "Управление первого типа" по "Управление пятого типа" 20. (59-55). Эти сигналы открывают приемопередатчики 46 - 48 в узле селектора адреса 25 (фиг. 2-6) для записи информации из ЦП 2 в регистр состояния 177560 младшим байтом через приемопередатчики 46, 47 и через приемопередатчик 48 для записи информации в (15-12) разрядах.

При этом 12 разряд установлен при наличии ошибки четности, 13 разряд установлен при наличии ошибки в стоповом бите, 14 разряд установлен при переполнении (07-00) разрядов регистров состояния 177560, 15 разряд установлен при наличии любой из названных ошибок. Передний фронт сигнала "Запись данных" 20.2 в узле логики управления 26 (фиг. 7) формирует передний фронт сигнала "Ответ устройства" 20.6 по цепи: элемент И 63, элементы ИЛИ 57.70, элемент ИЛИ-НЕ 67, элемент НЕ 61 и с выхода передатчика 72 снимается магистральный сигнал "Ответ устройства" 7.6 и передается через магистраль 1 в центральный процессор 2, свидетельствуя о том, что операция "Запись данных" окончена.

При чтении регистра данных 177562 на выходе программируемой матрицы 174 (фиг. 16), в соответствии с таблицей состояния ее термов (фиг. 18), активный уровень высокого потенциала принимают сигналы "Управление второго, четвертого и шестого типов" 20.56, 58, 60, которые поступают на вторые входы управления приемопередатчиков 46 - 48, тем самым обеспечивают передачу информации из устройства ввода-вывода 3 через магистраль 1 в ЦП 2.

При этом читается младший байт и разряды <15-12>, несущие информацию о типе ошибки.

При чтении регистра состояния 177564 на выходах программируемой матрицы 174 (фиг. 16), в соответствии с таблицей состояния ее термов (фиг. 18), активный уровень высокого потенциала принимают сигналы "Управление второго и четвертого типов" 20.56, 58, которые поступают на вторые входы управления приемопередатчиков 46, 47, тем самым обеспечивают передачу информации младшим байтом из устройства ввода-вывода 3 в центральный процессор 2.

При записи информации в регистр данных 177566 из ЦП 2 в устройство ввода-вывода 3 на выходе программируемой матрицы 174 формируются высокие потенциалы "Управление первого типа" 20.55 и с "Управления третьего типа" по "Управление шестого типа" 20.60-57. Наличие высоких потенциалов на первом управляющем входе приемопередатчика 46 и на двух управляющих входах приемопередатчиков 47, 48 обеспечивает передачу информации в регистр данных 177566 младшим байтом и при наличии ошибок запись информации в разряды (15-12) адресно-информационных шин 19. (15-12).

В устройстве ввода 171 (фиг. 17) во время включения питания в исходное состояние устанавливаются регистр страницы 177520, выполненный на регистрах 181, 182, системный регистр 177522, выполненный на регистрах 183, 184, сигналом "Сброс" 20.65, с выхода формирователя 188, при этом сигнал "Авария источника питания" 20.54 принимает значение высокого потенциала с включением питания "МикроЭВМ".

Чтение регистра 177520 осуществляется следующим образом.

В адресной части ЦП 2 выставляет магистральные сигналы "Синхронизация обмена", "Чтение данных" и "Выборка устройства" 7.(1-3), которые передаются через приемопередатчик 50 узла селектора адреса 25 (фиг. 6) как сигналы "Синхронизация обмена" 20.3, "Чтение данных первого типа" 20.1 и "Выбор устройства" 54. Последний сигнал поступает на вход программируемой матрицы и на вход набора D-триггеров 74 в логике управления 26 (фиг. 7), где по сигналу "Синхронизация обмена" 20.3 на выходе набора D-триггера 74 формируется сигнал "Устройство выбрано" 78. Сигнал 78 поступает на вход элемента ИЛИ 199 узла дешифраторов 172 (фиг. 15). На другой вход элемента ИЛИ 199 подается сигнал "Разрешение устройства ввода" 20.50 с выхода набора D-триггеров 196, где он был сформирован с приходом сигналов "Выбор устройства ввода" 20.44 и "Синхронизация обмена" 20.3. Сигнал 20.44 снимается с выхода программируемой матрицы 53 при появлении на входе матрицы адреса 177520, при этом выход ВЧ матрицы 53 становится активным высоким потенциалом.

Сигнал 20.50 поступает совместно с сигналом 20.1 на вход элемента И 178 и формируется сигнал "Чтение устройства ввода" 20.47, который подается через элемент ИЛИ 198 как сигнал "Управление устройством ввода" 20.53. Этот сигнал поступает на формирователь 188. С выхода формирователя 188 снимается сигнал "Разрешение устройства ввода с инверсией" 20.51, который поступает на первый вход выбора 20.51 дешифратора 195, на информационный вход дешифратора 195 подается сигнал "Чтение устройства ввода" 20.47, на адресные входы 18.(2, 1), подается содержимое первого и второго адресных шин с выхода набора D-триггера 74. На выходе дешифратора 195 формируется сигнал "Чтение регистра страницы" 20.39, который разрешает чтение информации с выхода формирователей 185, 186, на вход которых поступает информация с регистра страницы 177520, выполненного на регистрах 181, 182. Сигнал "Чтение данных первого типа" 20.1 в узле логики управления 26 (фиг. 7) поступает через элемент НЕ 58, элемент ИЛИ-НЕ 66 на вход элемента ИЛИ 57 для формирования через элемент ИЛИ 70, ИЛИ-НЕ 67, элемент НЕ 61 и приемопередатчик 72 магистрального сигнала "Ответ устройства" 7.6. Сигнал 7.6 поступает через магистраль 1 в ЦП 2 и сигнализирует об окончании режима "Чтение данных".

На этом заканчивается операция чтение регистра страницы 177520.

Запись в регистр страницы осуществляется с формированием центральным процессором ЦП 2 сигналов "Синхронизация обмена" 20.3 и "Запись данных" 20.2 на выходе приемопередатчика 50. Сигнал "Запись данных" 20.2 совместно с сигналом "Разрешение устройства ввода" 20.50 поступают на вход элемента И 179 узла программируемой матрицы 173 (фиг. 16), на выходе элемента И 179 формируется сигнал "Запись устройства ввода" 20.34 и поступает на вход элемента ИЛИ 198, с его выхода сигнал 20.53, поступает на выход формирователя 188. Сигнал "Разрешение устройства ввода с инверсией" 20.51 формируется на выходе с формирователя 188 и разрешает формирование сигналов на выходах дешифратора 194, сигнал 20.34 через элемент НЕ 197 поступает на входы выбора дешифратора 194. При обращении к регистру страницы на адресные входы подается информация первого и второго битами. На выходе дешифратора 194 формируются сигналы загрузки регистра.

Передний фронт сигнала "Запись данных" 20.2 формирует магистральный сигнал "Ответ устройства" 7.6, в узле логики управления 26 (фиг. 7) сигнал "Запись данных" 20.2 совместно с сигналом "Устройство выбрано" на входах элемента И 63 формируют на его выходе сигнал, проходящий через элементы ИЛИ 57, 70, элемент ИЛИ-НЕ 67, элемент НЕ 61 и приемопередатчик 72, на выходе которого формируется магистральный сигнал "Ответ устройства" 7.6, поступающий через магистраль 1 в центральный процессор 2 и сигнализирующий об окончании цикла записи данных.

Чтение системного регистра осуществляется формированием в адресной части 177522 сигналов "Синхронизация обмена" 20.3 и "Чтение данных первого типа" 20.1 Аналогичным образом формируется сигнал "Чтение системного регистра" 20.40, который подается на выходы регистров 183, 184. Запись системного регистра 177522 осуществляется в эти же регистры 183, 184, только формируются сигналы "Запись младшего байта" и "Запись старшего байта" на выходе дешифратора 195 по соответствующим сигналам на его входе. Чтение регистра конфигурации 177522 осуществляется формированием центральным процессором 2 сигналов "Синхронизация обмена" 20.3 и "Чтение данных первого типа" 20.1.

При этом на выходе дешифратора 195 формируется сигнал "Чтение регистра конфигурации" 20.41. С выходов формирователя 187 считывается информация о состоянии регистра конфигурации. Ввод информации с программируемых запоминающих устройств 190, 191 осуществляется с установкой ЦП 2 адреса 173000.

При этом на выходе матрицы 53 высоким потенциалом формируется сигнал "Выбор адреса устройства ввода" 20.43, который защелкивается по сигналу "Синхронизация обмена" 20.3 в наборе D-триггеров 196 узла дешифраторов 172 (фиг. 15) как сигнал "Разрешение адреса устройства ввода" 20.49, который поступает на вход элемента ИЛИ 176, а с выхода этого элемента сигнал "Управление ответом ошибки" 20.45 поступает на вход одновибратора 75 узла логики управления 26 (фиг. 7), который формирует через 1 мкс от переднего фронта "Чтение данных первого типа" 20.1 сигнал "Ответ устройства" 7.6. За это время считывается из первой ячейки ПЗУ 190, 191 в запоминающее устройство 4 и считывается константа из этих ПЗУ для формирования последующего адреса при "оконной" адресации на выходах мультиплексора 189, необходимых дополнительных адресов старших разрядов для ПЗУ 190, 191.

При этом по адресной шине 18.8 передается информация выбора младшего байта низким потенциалом на шине 18.8 и высоким потенциалом - для выбора старшего байта константы.

Центральный процессор инкрементно выставляет последующие адреса по достижении адреса 173776.

На этом заканчивается цикл ввода информации из ПЗУ 190, 191 в постоянное запоминающее устройство 4.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРО-ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2000 |

|

RU2209462C2 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1566359A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1991 |

|

SU1784989A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| Программируемый контроллер | 1991 |

|

SU1833870A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для формирования изображений | 1987 |

|

SU1413647A1 |

Изобретение относится к области микропроцессорной техники, в частности, может применяться для реализации обмена информацией. Цель изобретения - повышение надежности за счет реализации устройства ввода-вывода. Поставленная цель достигается тем, что в микроЭВМ, содержащую центральный процессор, устройство ввода-вывода и оперативное запоминающее устройство, введены новые связи в устройстве ввода-вывода между узлами: адаптера связи, регистра состояния, селектора адреса, логики управления, управления приемопередачи, приемопередачи, программируемой матрицы, устройства ввода и дешифратора, в который включены два дешифратора, элемент НЕ, два элемента ИЛИ и набор D-триггеров, а также введены новые связи между программируемыми матрицами и приемопередатчиками для осуществления загрузки из программируемой памяти при выборе стартового адреса 173000. 19 ил.

МикроЭВМ, содержащая центральный процессор, устройство ввода-вывода, оперативное запоминающее устройство, при этом входы-выходы соединены через магистрали общей шины с входами-выходами оперативного запоминающего устройства и устройства ввода-вывода, отличающаяся тем, что устройство ввода-вывода содержит узел адаптера связи, узел регистра состояния, узел селектора адреса, узел логики управления, узел управления приемопередачи, узел приемопередачи, узел программируемой матрицы, узел устройства ввода, узел дешифраторов, в который включены два дешифратора, набор D-триггеров, элемент НЕ, два элемента ИЛИ, при этом узел адаптера связи подключен соответственно адресно-информационными входами третьего типа и первого типа второго бита к одноименным выходам узла селектора адреса, узла управления приемопередачи и узла устройства ввода, входами "Установка" и "Управление выходными данными" - к одноименным выходам узла приемопередачи, входом "Регистр состояния выхода" - к одноименному выходу узла управления приемопередачи, информационный вход "Прием данных" и выход "Передача данных" узла адаптера связи образуют токовую петлю, узел регистра состояния подключен соответственно адресными входами с второго по четвертый бит к одноименным выходам узла логики управления и одноименным входам узла управления приемопередачи и узла программируемой матрицы, входом "Останов" - к одноименному выходу узла адаптера связи, входами "Разрешение ввода", "Разрешение вывода", "Готов ввод", "Готов вывод", "Ошибка четности", "Ошибка стопового бита", "Ошибка переполнения" - к одноименным выходам узла приемопередачи, входом "Управление входом" - к одноименному выходу узла управления приемопередачи, адресноинформационными входами-выходами второго типа - к одноименным входам-выходам узла селектора адреса, входом "Чтение регистра состояния" - к одноименному выходу узла логики управления, узел логики управления подключен соответственно адресно-информационными входами-выходами третьего типа и первого типа с первого по тринадцатый бит к одноименным входам-выходам узла селектора адреса, входом "Выбор пульта" - к одноименному выходу узла селектора адреса, входами "Чтение данных первого типа", "Запись данных", "Синхронизация обмена", "Выборка устройства" - к одноименным выходам узла селектора адреса, входом "Ошибка стопового бита" - к одноименному выходу узла приемопередачи, магистральными входами-выходами "Авария источника питания", "Ответ устройства", "Останов" - к одноименным входам-выходам магистрали, узел селектора адреса соответственно подключен входами с первого по шестой вектора - к одноименным выходам узла приемопередачи, адресно-информационными входами-выходами первого и третьего типов - к одноименным входам-выходам узла устройства ввода, выходной шиной "Сигнал выбора устройства" - к одноименной входной шине узла логики управления, магистральными входами-выходами "Выборка устройства", "Запись данных", "Синхронизация обмена", "Чтение данных", "Авария источника питания", "Признак записи байта" - к одноименным входам-выходам магистрали, узел управления приемопередачи подключен соответственно адресным входом первого бита и адресным входом первого типа с инверсией к одноименным выходам узла логики управления, адресно-информационными входами - к одноименным выходам узла приема передачи, входами "Запись младшего байта" и "Чтение входного буфера" - к одноименным выходам узла логики управления, узел приемопередачи подключен соответственно к адресным входам второго типа, входами "Чтение данных второго типа" и "Чтение данных пятого типа" к одноименным выходам узла логики управления, адресно-информационными входами-выходами третьего типа и второго типа с первого по седьмой бит - к одноименным выходам узла управления приема передачи, входами "Управление входными данными", "Синхронизация" - к одноименным выходам адаптера связи, входами "Регистр состояния выхода", "Разрешение буфера", "Регистр состояния входа", "Управление входом" - к одноименным выходам узла управления приема передачи, магистральными входами-выходами, "Запрос прерывания", "Выходной сигнал предоставления прерывания", "Входной сигнал предоставления прерывания" и "Установка" подключены к одноименным входам-выходам магистрали, узел устройства ввода подключен соответственно адресно-информационными входами-выходами третьего и первого типов к одноименным входам-выходам селектора адреса, входами "Загрузка регистра страницы младшего байта", "Загрузка регистра страницы старшего байта", "Загрузка системного регистра младшего байта", "Загрузка системного регистра старшего байта", "Чтение регистра страницы", "Чтение системного регистра", "Чтение регистра конфигурации" - к одноименным выходам узла дешифраторов, адресными входами с первого по четвертый бит - к одноименным выходам узла логики управления и адресными входами с пятого по восьмой бит - к одноименным выходам узла дешифраторов, узел дешифраторов подключен соответственно адресными входами первого и второго бит к одноименным выходам узла логики управления, адресно-информационными входами-выходами первого типа с пятого по восьмой бит - к одноименным входам-выходам узла селектора адреса, узел программируемой матрицы подключен соответственно адресными входами первого и второго бит к одноименным выходам узла логики управления, адресно-информационными входами-выходами первого типа с восьмого по одиннадцатый бит - к одноименным входам-выходам узла селектора адреса, магистральными адресными входами-выходами с восьмого по одиннадцатый бит подключены к одноименным входам-выходам магистрали, в узле дешифраторов к его первым и вторым информационным входам подключены соответственно адресные входы первого и второго битов, выходы первого дешифратора "Загрузка регистра страницы старшего байта", "Загрузка системного регистра старшего байта", "Загрузка регистра страницы младшего байта", "Загрузка системного регистра младшего байта" и выходы второго дешифратора "Чтение регистра страницы", "Чтение системного регистра", "Чтение регистра конфигурации" подключены к одноименным выходам узла, при этом узел селектора адреса выходом "Авария источника питания" подключен к одноименному входу узла устройства ввода, выходами "Синхронизация обмена", "Выбор адреса устройства ввода", "Выбор устройства ввода" подключен соответственно к одноименным входам узла дешифраторов, узел логики управления входом "Сброс регистра" подключен к одноименному входу узла дешифраторов, входом "Управление ответом ошибки" подключен к одноименному выходу программируемой матрицы, выходной шиной "Устройство выбрано" подключен к одноименным входам узла дешифраторов и программируемой матрицы, адресным выходом второго типа подключен к одноименному входу узла программируемой матрицы, узел устройства ввода выходом "Разрешение устройства ввода с инверсией" подключен к одноименному входу узла дешифраторов, выходом "Управление ответом ошибки с инверсией" подключен к одноименному входу узла логики управления, узел дешифраторов выходами "Разрешение устройства ввода", "Выбор внешнего устройства" и "Разрешение адреса устройства ввода" подключен соответственно к одноименным входам узла программируемой матрицы, выходом "Управление устройством ввода" подключен к одноименным входам узла логики управления и узла устройства ввода, узел программируемой матрицы выходами "Управление ответом ошибки", "Чтение устройства ввода" подключен соответственно к одноименным входам узла устройства ввода, выходами "Чтение входного буфера с инверсией", выходами с "Управление первого типа" по "Управление шестого типа" подключен к одноименным входам узла селектора адреса, выходом "Векторная шина седьмого типа" подключен к одноименному входу узла логики управления, выходом "Запись устройства ввода" подключен к одноименному входу узла дешифраторов, входами "Чтение данных первого типа", "Запись данных", "Синхронизация обмена" подключен соответственно к одноименным выходам узла селектора адреса, входами "Чтение входного буфера", "Чтение регистра состояния", "Чтение пятого типа" подключен к одноименным выходам узла логики управления, входами "Векторная шина четвертого типа" и "Чтение четвертого типа" подключен к одноименным выходам узла приемопередачи, при этом в узле дешифраторов вход "Запись устройства ввода" подключен к входу элемента НЕ и к первому входу первого элемента ИЛИ, выход которого подключен к выходу "Управление устройством ввода" узла, выход элемента НЕ подключен к первому и второму входам выбора первого дешифратора, вход "Чтение устройства ввода" подключен к информационному входу второго дешифратора и второму входу первого элемента ИЛИ, входная шина "Устройство выбрано" подключена к первому входу второго элемента ИЛИ, выход которого подключен к выходу "Выбор внешнего устройства" узла, вход "Разрешение устройства ввода с инверсией" подключен к входу разрешения первого дешифратора и к первому входу выбора второго дешифратора, входы "Выбор адреса устройства ввода", "Выбор устройства ввода", адресно-информационные входы-выходы первого типа с пятого по восьмой бит соединены соответственно с первого по шестой входами набора D-триггеров, входы "Синхронизация обмена" и "Сброс регистра" подключены соответственно к входам тактирования и сброса набора D-триггеров, первый выход которого подключен к выходу "Разрешение адреса устройства ввода" узла, второй выход набора D-триггеров подключен к первому информационному входу первого дешифратора, к второму входу второго элемента ИЛИ и к выходу узла "Разрешение устройства ввода", с третьего по шестой выходы набора D-триггеров подключены соответственно к адресным выходам с пятого по восьмой бит узла.

| SU, авторское свидетельство N 1716528, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство N 1751776, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| GB, заявка N 2127190, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| РСТ, заявка N 81/02071, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мик Дж | |||

| и др | |||

| Проектирование микропроцессорных устройств с разрядно-модульной организацией | |||

| - М.: "Мир", 1984, т.1, с.7, рис.1.2. | |||

Авторы

Даты

1998-04-10—Публикация

1994-12-19—Подача