Изобретение относится к области микропроцессорной техники, в частности, может применяться для реализации обмена информации.

Известна микроЭВМ [1], содержащая центральный процессор, устройство ввода-вывода, оперативное запоминающее устройство.

Недостатком данной микроЭВМ является сложность устройства ввода-вывода, также отсутствие устройства ввода, что не позволяет выполнить загрузку и запуск начальных программ и диагности микроЭВМ.

Известна микроЭВМ по патенту Российской Федерации 2108619 [2].

Недостатком данной микроЭВМ является снижение ее быстродействия из-за наличия в устройстве ввода-вывода программируемой матрицы с задержкой в 130 нс на пути управления приемопередачей данных между центральным процессором и устройством ввода-вывода, а также сложность устройства ввода-вывода.

Целью данного изобретения является повышение быстродействия обмена информацией и сокращение числа оборудования в устройстве ввода-вывода.

Поставленная цель достигается тем, что микроэлектронная вычислительная машина содержит центральный процессор, устройство ввода-вывода, статическое запоминающее устройство, устройство ввода, при этом устройство ввода-вывода содержит узел адаптера связи, узел регистра состояния, узел селектора адреса, узел логики управления, узел управления приемопередачей, узел приемопередачи, причем узел селектора адреса содержит пять приемопередатчиков, программируемую логическую матрицу, элемент развязки, узел логики управления содержит четыре элемента ИЛИ-НЕ, элемент И, два элемента И-НЕ, три элемента ИЛИ, пять элементов НЕ, три передатчика, набор D-триггеров, одновибратор, ограничительный элемент, накопительный элемент, при этом узел адаптера связи подключен соответственно адресно-информационными входами-выходами второго бита и первого типа нулевого бита к одноименным выходам узла селектора адреса и узла управления приемопередачей, входами "Установка", "Управление выходами данными" - к одноименным выходам узла приемопередачи, входом "Регистр состояния выхода" - к одноименному выходу узла управления приемопередачей, информационные вход "Прием данных" и выход "Передача данных" образуют токовую петлю, узел регистра состояния подключен соответственно адресными входами с второго по четвертый бит к одноименным выходам узла логики управления и одноименным входам узла управления приемопередачей, входом "Останов" - к одноименному выходу узла адаптера связи, входами "Разрешение ввода", "Разрешение вывода", "Готов ввод", "Готов вывод", "Ошибка честности", "Ошибка стопового бита", "Ошибка переполнения" подключен к одноименным выходам узла приемопередачи, входом "Управление входом" - к одноименному выходу узла управления приемопередачей, адресно-информационным входам-выходам первого типа - к одноименным входам-выходам узла селектора адреса, входом "Чтение регистра состояния" - к одноименному выходу узла логики управления, который подключен соответственно адресно-информационными входами - выходами с первого по тринадцатый бит и первого типа нулевого бита к одноименным входам - выходам узла селектора адреса, входами "Выбор пульта", "Чтение данных первого типа", "Запись данных", "Синхронизация обмена", "Выборка устройства" - к одноименным выходам узла селектора адреса, входом "Ошибка стопового бита" - к одноименному выходу узла приемопередачи, магистральными входами-выходами "Авария источника питания", "Ответ устройства", "Останов" - к одноименным входам-выходам магистрали, узел селектора адреса подключен соответственно входом с первого по шестой вектор к одноименным выходам узла приемопередачи, выходами "Выборка устройства", "Управление входом" - к одноименным входам узла логики управления, магистральными адресно-информационными входами-выходами, магистральными входами-выходами "Выборка устройства", "Запись данных", "Синхронизация обмена", "Чтение данных", "Авария источника питания", "Признак записи байта" - к одноименным входам-выходам магистрали, узел управления приемопередачей подключен соответственно адресными входами с первого по четвертый битами, адресными входами первого типа к одноименным выходам узла логики управления, адресно-информационными шинами - к одноименным шинам узла приемопередачи, входами "Запись младшего байта", "Чтение входного буфера" - к одноименным выходам узла логики управления, узел приемопередачи подключен соответственно адресным входом второго типа, входами "Чтение данных второго типа", "Чтение данных пятого типа" - к одноименным выходам узла логики управления, адресно-информационными входами-выходами с первого по седьмой бит и первого типа нулевого бита - к одноименным входам-выходам узла управления приемопередачей, входами "Управления входными данными", "Синхронизация" - к одноименным выходам узла адаптера связи, входами "Регистр состояния выхода", "Разрешение буфера", "Регистр состояния входа", "Управление входом" - к одноименным выходам узла управления приемопередачей, магистральными входами-выходами "Запрос прерывания", "Выходной сигнал предоставления прерывания" и "Установка" - к одноименным входам-выходам магистрали, причем в узле селектора адреса первый приемопередатчик первой и шестой векторными входными шинами и магистральным входом-выходом "Запись данных" подключен соответственно к одноименным шинам и к входу-выходу узла селектора адреса, магистральные входы-выходы нулевого, второго, шестого и седьмого битов и соответствующими адресно-информационными входами-выходами подключены соответственно к одноименным входам-выходам узла селектора адреса, второй приемопередатчик второй, третий и шестой векторными входными шинами подключен соответственно к одноименным входам узла селектора адреса, магистральными адресно-информационными входами-выходами первого и с третьего по пятый битами и соответствующими адресно-информационными входами подключены соответственно к одноименным входам-выходам узла селектора адреса, третий приемопередатчик магистральными адресно-информационными входами-выходами с двенадцатого по пятнадцатый битами и соответствующими адресно-информационными входами-выходами подключены соответственно к одноименным входам-выходам узла селектора адреса, четвертый приемопередатчик магистральными адресно-информационными входами-выходами с восьмого по одиннадцатый битами и соответствующими адресно-информационными входами-выходами первого типа подключен соответственно к одноименным входам-выходам узла селектора адреса, пятый приемопередатчик магистральными входам-выходам "Выборка устройства", "Запись данных", "Синхронизация обмена", "Чтение данных" и выходами "Сигнал выборки устройства", "Запись данных", "Синхронизация обмена", "Чтение данных" подключены соответственно к одноименным входам-выходам узла селектора адреса, программируемая логическая матрица с первого по тринадцатый адресными входами подключена соответственно адресно-информационными входами первого типа нулевого бита и входами с первого по двенадцатый бит к одноименным входам узла селектора адреса, выходами "Выборка устройства" и "Выборка пульта" подключена соответственно к одноименным выходам узла селектора адреса, выход пятого приемопередатчика "Сигнал выборки устройства" подключен к пятнадцатому адресному входу программируемой логической матрицы, выход равенства адреса третьего приемопередатчика подключен к входу элемента развязки, при этом в узле логики управления с первого по третий информационные входы набора D-триггеров входами "Сигнал выборка устройства", адресно-информационными входами первого и второго битов подключены соответственно к одноименным входам узла логики управления, пятый и шестой информационные входы набора D-триггеров адресно-информационными входами четвертого бита и первого типа нулевого бита подключены соответственно к одноименным входам узла логики управления, вход адресно-информационный третьего бита и шина управления "Выбор пульта" подключены соответственно к одноименным входам узла логики управления и к первому и второму входами первого элемента ИЛИ, выход которого подключен к четвертому информационному входу набора D-триггеров, вход "Синхронизация обмена" подключен к первому входу второго элемента ИЛИ, к тактирующему входу набора D-триггеров и к входу узла логики управления, выход второго элемента ИЛИ подключен к сбросовому входу набора D-триггеров, выход первого элемента ИЛИ-НЕ через первый элемент НЕ подключен к первому входу первого передатчика, инверсный выход одновибратора подключен к второму входу первого передатчика, выход которого подключен к магистральному выходу "Ответ устройства" узла логики управления, шина "Устройство выбрано" с первого выхода набора D-триггеров подключена к первому входу элемента И и к входу второго передатчика, к второму входу элемента И подключен вход "Запись данных" узла логики управления, выход элемента И подключен к первому входу третьего элемента ИЛИ и через второй элемент НЕ к первому входу второго элемента ИЛИ-НЕ, второй выход набора D-триггеров адресной шиной первого бита подключен к выходу узла логики управления, к первым выходам первого и второго элементов И-НЕ и через третий элемент НЕ к выходу адресной шины первого типа узла логики управления, третий выход набора D-триггеров адресной шины второго бита подключен к выходу узла логики управления, к первому входу третьего элемента ИЛИ-НЕ и второму входу второго элемента И-НЕ, выходы которых соответственно подключены к выходам "Чтение входного буфера" и адресная шина второго типа узла логики управления, четвертый и пятый выходы набора D-триггеров подключены соответственно адресными шинами третьего и четвертого бита к выходам узла логики управления, шестой выход набора D-триггеров адресная шина нулевого бита подключен к второму входу второго элемента ИЛИ-НЕ, выход которого подключен к выходу "Запись младшего байта" узла логики управления, вход узла логики управления "Ошибка стопого бита" через третий передатчик подключен к магистральному выходу "Останов" узла логики управления, вход узла логики управления "Чтение данных первого типа" через четвертый элемент НЕ подключен к первому входу четвертого элемента ИЛИ-НЕ, выход которого подключен соответственно к вторым входам третьего элемента ИЛИ и первого элемента И-НЕ и через пятый элемент НЕ подключен к выходу "Чтение данных пятого типа" узла логики управления, одновибратор первым входом подключен через ограничительный элемент к положительной шине источника питания микроЭВМ и через накопительный элемент к второму входу одновибратора, третий вход одновибратора подключен к обшей шине, сбросовый вход одновибратора подключен к положительной шине источника питания микроЭВМ, выход "Чтение данных четвертого типа" узла приемопередачи подключен к одноименному входу узла селектора адреса, выходы узла логики управления "Чтение входного буфера", "Чтение регистра состояния" и "Чтение данных пятого типа" подключены соответственно к одноименным входам узла селектора адреса, выходы узла логики управления адресно-информационный выход второго бита и адресные шины второго типа и первого бита подключены соответственно к одноименным входам узла селектора адреса, вход четвертая векторная шина узла логики управления подключен к одноименному выходу узла приемопередачи, причем в узел селектора адреса включен элемент НЕ, через который вход "Управление входными данными" узла селектора адреса подключен к входу разрешения состояния высокого импеданса третьего приемопередатчика, выход элемента развязки подключен к адресно-информационному входу-выходу пятнадцатого бита третьего приемопередатчика, на вход разрешения открытого вывода которого подключена с входа узла селектора адреса адресная шина первого бита, входы узла селектора адреса "Чтение данных пятого типа" и адресная шина второго типа подключены соответственно к входам разрешение состояния высокого импеданса и разрешение открытого вывода первого приемопередатчика, входы узла селектора адреса "Чтение данных четвертого типа" и "Чтение регистра состояния" подключены соответственно к входам разрешение состояния высокого импеданса и разрешение открытого вывода второго приемопередатчика, адресно-информационный вход второго бита узла селектора адреса подключен к одноименному выходу первого приемопередатчика, адресно-информационный выход тринадцатого бита третьего приемопередатчика подключен к четырнадцатому адресному входу программируемой логической матрицы, при этом в узел логики управления включен четвертый передатчик, входы узла логики управления адресная шина первого типа и "Чтение данных третьего типа" подключены соответственно к первому и второму входам четвертого передатчика, с выхода которого адресно-информационный выход второго бита подключен к выходу узла логики управления, выход второго передатчика подключен к второму входу четвертого элемента ИЛИ-НЕ, на второй вход третьего элемента ИЛИ-НЕ подключен вход узла логики управления "Чтение данного пятого типа", выход третьего элемента ИЛИ подключен к первому входу первого элемента ИЛИ-НЕ, к второму входу которого подключена с входа узла логики управления четвертая векторная шина, с первого выхода набора D-триггеров шина "Устройство выбрано" подключена к четвертому входу одновибратора.

Существенными отличиями являются введение новых связей между узлом логики управления, включение в узел селектора адреса элемента НЕ и новых связей на управление входом разрешения состояния высокого импеданса и управление входом разрешения открытого вывода первого, второго, третьего приемопередатчиков, включение в узел логики управления четвертого передатчика и введение новых связей на управление элементов ИЛИ, ИЛИ-НЕ и одновибратора.

Данное техническое решение в научно-технической и патентной литературе не выявлено.

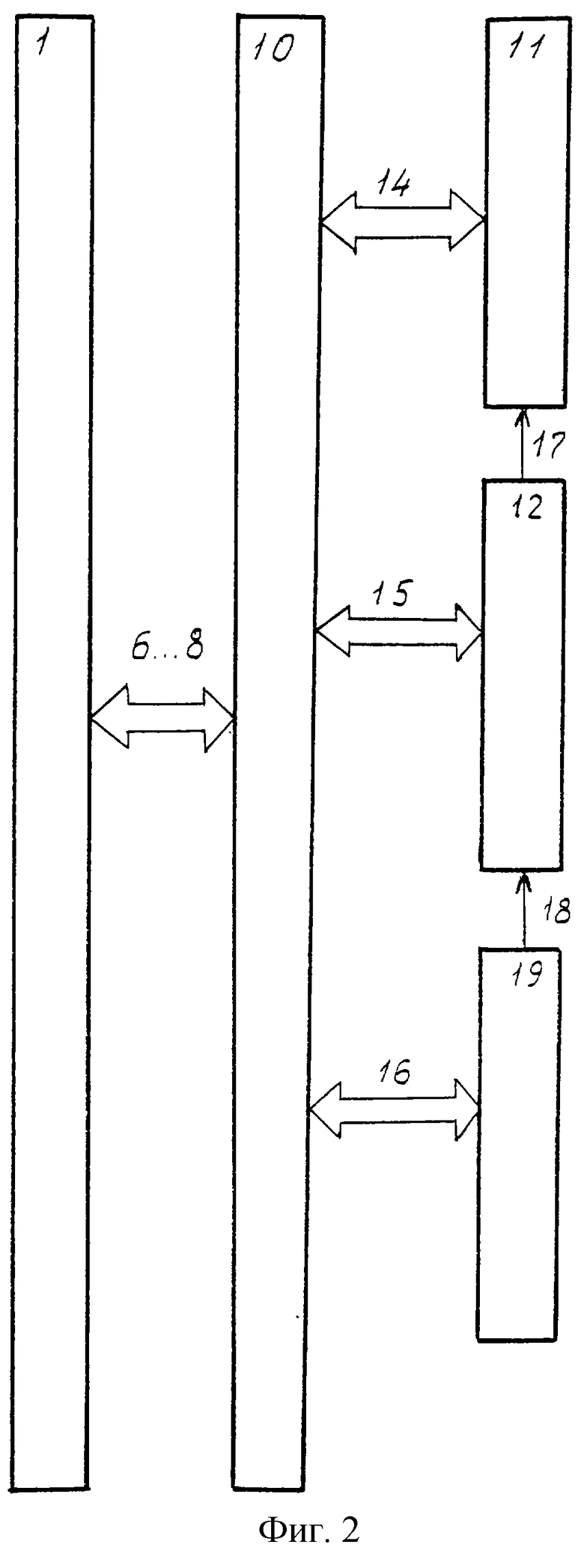

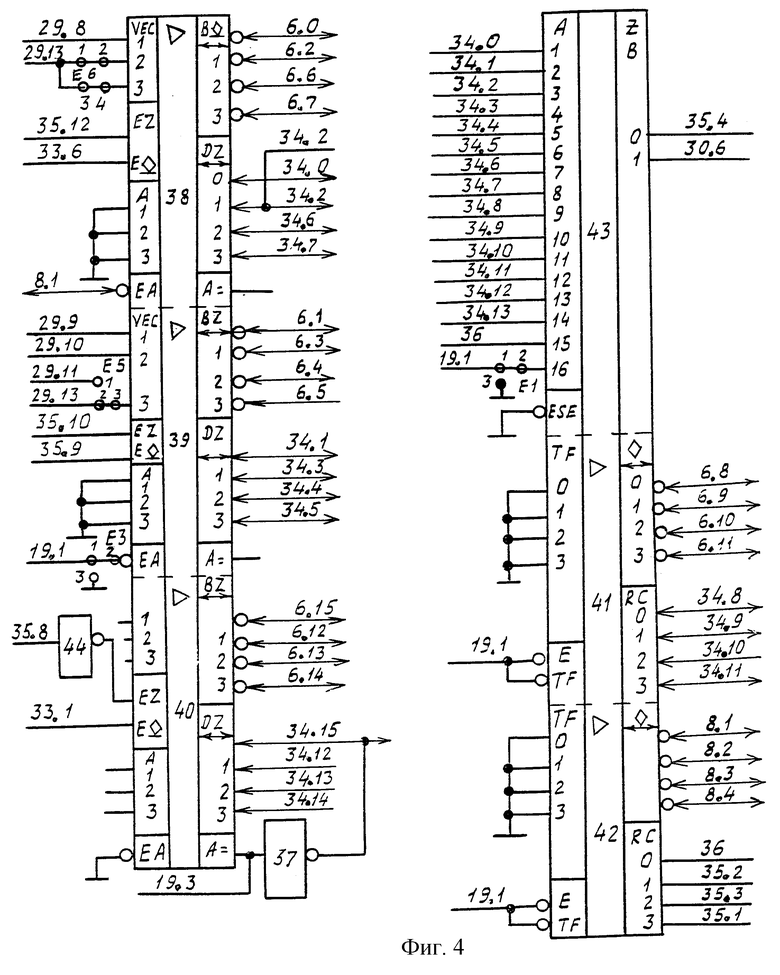

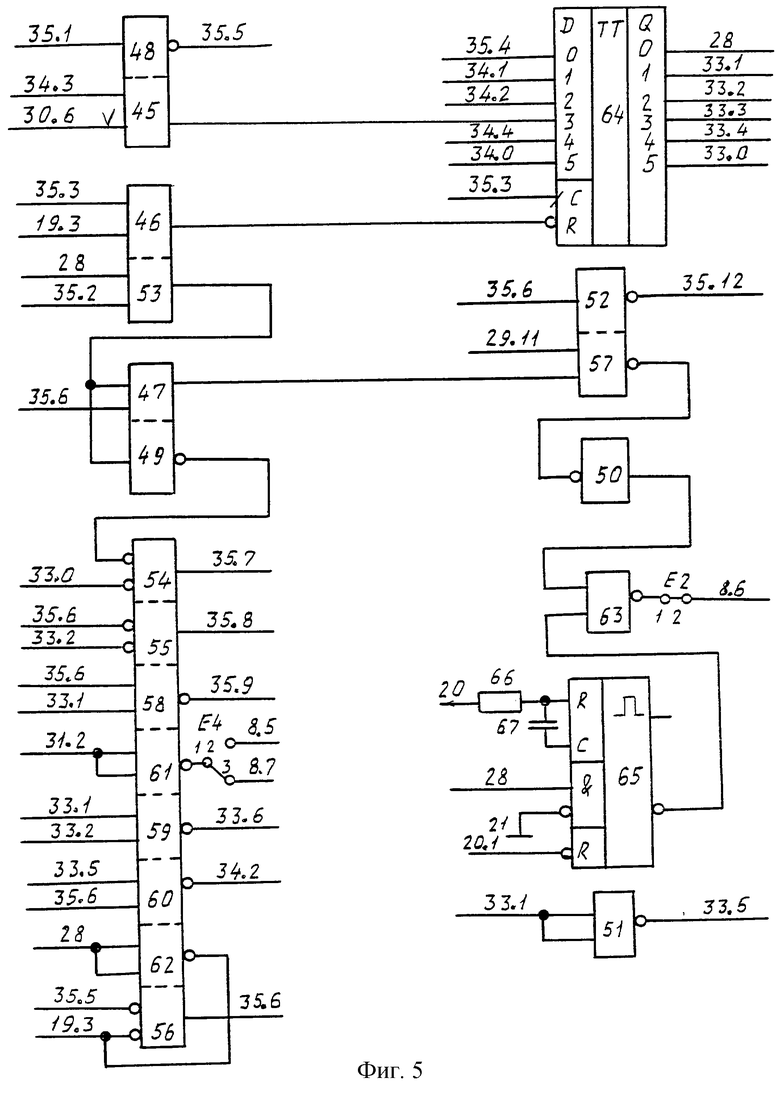

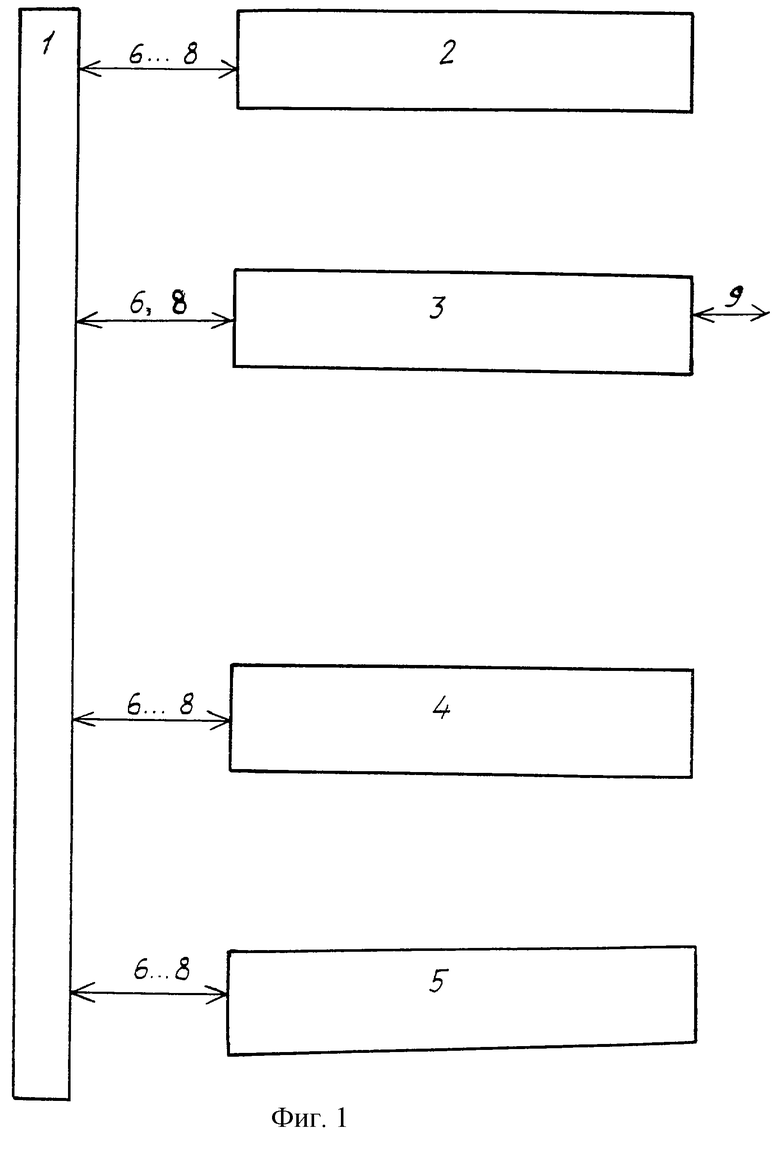

Сущность изобретения поясняется чертежами. На фиг.1 показана функциональная схема микроЭВМ, на фиг.2 - центрального процессора, на фиг.3 - устройства ввода-вывода, на фиг.4 показана принципиальная электрическая схема узла селектора адреса устройства ввода-вывода, на фиг.5 - узла логики управления устройства ввода-вывода.

МикроЭВМ содержит магистраль 1, центральный микропроцессор 2, устройство ввода-вывода 3, устройство ввода 4, статическое запоминающее устройство 5, магистральные вводы-выводы 6-8, шины токовой петли 9, причем центральный процессор 2 (фиг.2) содержит устройство сопряжения с магистралью 10, резидентное оперативное запоминающее устройство 11, устройство управления синхронизацией 12, микропроцессор 13, шины ввода-вывода 14-16, шины вывода 17, 18, шина логической единицы микроЭВМ 19, шина питания микроЭВМ 20, общая шина 21,

при этом устройство ввода-вывода 3 (фиг.3) содержит узел адаптера связи 22, узел регистра состояния 23, узел селектора адреса 24, узел логики управления 25, узел управления приемопередачи 26, узел приемопередачи 27,

причем устройство ввода-вывода (фиг.3) содержит шину "Устройство выбрано" 28, шины управления 29-31, адресно-информационные шины 32, адресные шины 33, адресно-информационные входы-выходы 34, шина управления 35, "Сигнал выборки устройства" 36,

при этом узел селектора адреса 24 устройства ввода-вывода 3 (фиг.4) содержит элемент развязки 37, приемопередатчики 38-42, программирующую логическую матрицу 43, элемент НЕ 44,

причем узел логики управления устройства ввода-вывода 3 (фиг.5) содержит элементы ИЛИ 45-47, элементы НЕ 48-52, элемент И 53, элементы ИЛИ-НЕ 54-57, элементы И-НЕ 58, 59, передатчики 60-63, набор D-триггеров 64, одновибратор 65, ограничительный элемент 66, накопительный элемент 67, кроме того, магистральные входы-выходы 6 содержат магистральные адресно-информационные входы-выходы 6.(15-0), магистральные входы-выходы 7 содержат магистральные адресные входы-выходы 7.(21-16), магистральные входы-выходы 8 содержат магистральные входы-выходы "Выборка устройства" 8.1, "Запись данных" 8.2, "Синхронизация обмена" 8.3, "Чтение данных" 8.4, "Авария источника питания" 8.5, "Ответ устройства" 8.6, "Останов" 8.7, "Запрос прерывания" 8.8, "Выходной сигнал предоставления прерывания" 8.9, "Входной сигнал предоставления прерывания" 8.10, "Установка" 8.11, "Входной сигнал разрешения захвата магистрали" 8.12, "Выходной сигнал разрешения захвата магистрали" 8.13, "Признак записи байта" 8.14. Шины токовой петли 9 содержат вход "Прием данных" 9.1, выход "Передача данных" 9.2. Шина управления 29 содержит шины "Регистр состояния выхода" 29.1, "Разрешение буфера" 29.2, "Регистр состояния входа" 29.3, "Разрешение ввода" 29.4, "Разрешение вывода" 29.5, "Управление входом" 29.6, "Синхронизация" 29.7, с первой по седьмую векторные шины 29. (14-8). Шины управления 30 содержат шины "Установка" 30.1, "Управление с инверсией" 30.2, "Входной буфер" 30.3, "Готов ввод" 30.4, "Готов вывод" 30.5, "Выбор пульта" 30.6, "Разрешение пульта" 30.7, "Управление выходными данными" 30.8, "Управление входными данными" 30.9. Шины управления 31 содержат шины "Ошибка четности" 31.1, "Ошибка стопового бита" 31.2, "Ошибка переполнения" 31.3. Адресно-информационные шины 32 содержат адресно-информационные шины с нулевого по седьмой бит 32.(7-0). Адресные шины 33 содержат адресные шины с нулевого по четвертый бит 33.(4-0) и адресные шины первого и второго типа 33.(6,5). Адресно-информационные входы-выходы содержат адресно-информационные входы-выходы с первого по пятнадцатый бит 34. (15-1), адресно-информационные входы-выходы первого типа нулевого, шестого, седьмого и с двенадцатого по четырнадцатый бит 34.(14-12, 7, 6, 0). Шина управления 35 содержит шины "Чтение данных первого типа" 35.1, "Запись данных" 35.2, "Синхронизация обмена" 35.3, "Выборка устройства" 35.4, "Чтение данных второго типа" 35.5, "Чтение данных третьего типа" 35.6, "Запись младшего байта" 35.7, "Чтение входного буфера" 35.8, "Чтение регистра состояния" 35.9, "Чтение данных четвертого типа" 35.10, "Останов" 35.11, "Чтение данных пятого типа" 35.12.

Работа микроЭВМ осуществляется следующим образом. В цикле "Чтение" данные передаются от устройства ввода-вывода 3 или от статического запоминающего устройства 5 (ведомое устройство) в центральный процессор 2 (ведущее устройство).

Всякий цикл обращения к магистрали 1 микроЭВМ начинается с адресации ведомого устройства, после завершения адресной части цикла (~250 нс) ведущее устройство осуществляет чтение, которое выполняется асинхронно и требует ответа от адресуемого устройства. Функции синхронизации при передаче адреса и приема передаче данных выполняют магистральные сигналы управления: "Синхронизация обмена" 8.3, "Признак записи байта" 8.14, "Запись данных" 8.2, "Чтение данных" 8.4, "Ответ устройства" 8.6.

1. Магистральный сигнал "Синхронизация обмена" 8.3 вырабатывается ведущим устройством, то есть центральным процессором 2, не ранее чем через 150 нс после установки адреса и предназначен для запоминания адреса во входной логики выбранного устройства.

2. Ведомое устройство дешифрирует адрес и запоминает его.

3. Ведущее устройство снимает магистральные адресно-информационные входы- выходы 6. (15-0), очищает магистральный сигнал "Выборка устройства" 8.1 и вырабатывает магистральный сигнал "Чтение данных" 8.4, сигнализируя о том, что оно готово принять данные от ведомого устройства и ожидает поступление магистрального сигнала "Ответ устройства" 8.6.

4. Ведомое устройство помещает данные на магистральных адресно-информационных входах-выходах 6.(15-0) и вырабатывает оповещающий об этом магистральный сигнал "Ответ устройства" 8.6. Если сигнал не вырабатывается в течение 10 мкс после выработки сигнала "Чтение данных" 8.4, вызывается внутреннее прерывание по ошибке обращения к магистрали 1 с адресом вектора 4.

5. Ведущее устройство принимает магистральный сигнал "Ответ устройства" 8.6, принимает данные и снимает магистральный сигнал "Чтение данных" 8.4.

6. Ведомое устройство по заднему фронту снимает магистральный сигнал "Ответ устройства" 8.4, завершая операцию передачи данных.

7. Ведущее устройство по заднему фронту магистрального сигнала "Ответ устройства" 8.4 снимает магистральный сигнал "Синхронизация обмена" 8.3, во время цикла "Чтение" магистральный сигнал "Признак записи байта" 8.14 не вырабатывается. Ведущее устройство, кроме того, по магистральным адресно-информационным входам-выходам 6. (15-0) передает магистральный сигнал "Выборка устройства" 8.1 в адресной части, если этот адрес находится в диапазоне 160000-177777. Магистральный сигнал "Чтение данных", поступивший в устройство ввода-вывода 3, проходит в узле селектора адреса 24 (фиг.3, 4) через пятый приемопередатчик 42 и передает в узел логики управления 25 (фиг. 3, 5), где вырабатываются сигналы "Чтение данных пятого типа" 35.12, "Чтение данных четвертого типа" 35.10 и "Чтение входного буфера" 35.9 уровнями логического нуля микроЭВМ, которые поступают соответственно на входы разрешения состояния высокого импеданса с первого по пятый приемопередатчики 38-40, на входы разрешения открытого вывода которых поступают соответственно из узла логики управления 25 (фиг. 3, 5) адресная шина второго типа 33.6, "Чтение регистра состояния" 35.9, и адресная шина первого бита 33. 1 уровнем логической единицы микроЭВМ. В цикле "Чтение" с адресно-информационных входов-выходов 34.(15-0) информация с первого по четвертый приемопередатчики 38-41 поступает через магистральные адресно-информационные входы-выходы 6. (15-0) в магистраль 1 и в центральный процессор 2.

При выполнении цикла "Запись" данные передаются от центрального процессора 2 (ведущего) в статическое запоминающее устройство 5 или в устройство ввода-вывода 3 (ведомое).

1. Ведущее устройство в адресной части цикла передает адрес по магистральным адресно-информационным входам-выходам 6. (15-0), а также, если это необходимо, вырабатывает магистральный сигнал "Признак записи байта" 8.14. Не ранее чем через 150 нс после установки адреса вырабатывается магистральный сигнал "Синхронизация обмена" 8.3.

2. Ведомое устройство дешифрирует адрес и запоминает его.

3. Ведущее устройство снимает адрес с магистральных адресно-информационных входов-выходов 6.(15-0), снимает магистральный сигнал "Выборка устройства" 8.1, помещает данные на магистральных адресно-информационных входах-выходах 6.(15-0) и через 100 нс (минимально) вырабатывает магистральный сигнал "Запись данных" 8.2.

4. Ведомое устройство принимает данные по магистральным адресно-информационным входам-выходам 6.(15-0) и вырабатывает магистральный сигнал "Ответ устройства" 8.6, означающий что данные им приняты. Если не вырабатывается магистральный сигнал "Ответ устройства" 8.6 после выработки "Запись данных" 8.2, вызывается внутреннее прерывание по ошибке обращения к магистрали с адресом вектора 4.

5. Ведущее устройство, получив магистральный сигнал "Ответ устройства" 8.6 через 150 нс (минимально), снимает магистральный сигнал "Запись данных" 8.2, а через 250 нс (минимально) с магистральных адресно-информационных входов-выходов 6.(15-0) снимаются данные.

6. Ведомое устройство снимает магистральный сигнал "Ответ устройства" 8.6, завершая операцию приема данных.

7. Ведущее устройство снимает магистральный сигнал "Синхронизация обмена" 8.3, завершая цикл "Запись".

8. Магистральный сигнал "Признак записи байта" 8.14 во время передачи данных может быть как пассивным, так и активным, определяя тем самым вывод 16-разрядного слова или байта.

При цикле "Запись" на входы разрешения состояния высокого импеданса с первого по третий приемопередатчик 38-40 в узле селектора 24 (фиг.3, 4) с устройства ввода-вывода 3 (фиг.3) подаются уровни логической единицы микроЭВМ сигналами "Чтение данных пятого типа" 35.12, "Чтение данных четвертого типа" 35.10, "Чтение входного буфера" 35.9 соответственно, а на входы разрешение открытого вывода данных приемопередатчиков 38-40 в узле селектора адреса 24 (фиг. 3, 4) устройства ввода-вывода 3 (фиг.3) соответственно подаются сигналы адресная шина второго типа 33.6, "Чтение регистра состояния" 35.9 и адресная шина первого бита уровнем логической единицы микроЭВМ. В цикле "Запись" с магистральных адресно-информационных входов-выходов 6.(15-0) информация с первого по четвертый приемопередатчики 38-41 поступает на адресно-информационные входы-выходы 34.(15-0) устройства ввода-вывода. При выполнении цикла "Чтение с модификацией" адресная часть при формировании магистрального сигнала "Чтение данных" 8.4 выполняется аналогично циклу "Чтение". Но при этом магистральный сигнал "Синхронизация обмена" 8.3 остается активным и после окончания сигнала "Чтение данных" 8.4, что позволяет записать результат выполнения команды без повторения адресной части цикла. При этом операция "Запись" может быть байтовой при активном магистральном сигнале "Признак записи байта" 8.14.

Работа приемопередатчиков 38-40 в устройстве ввода-вывода 3 селектора адреса 24 (фиг.4) аналогична циклам "Чтение" и "Запись".

Работа микроЭВМ в режиме прерывания программы.

1. Устройство, которому необходимо обслуживание в режиме прерывания, вырабатывает магистральный сигнал "Запрос на прерывание" 8.8.

2. Центральный процессор 2 (фиг.2) удовлетворяет требование, вырабатывает магистральные сигналы "Чтение данных" 8.4 и "Входной сигнал предоставления прерывания" 8.10.

3. Устройство получает магистральные сигналы "Чтение данных" 8.4 и "Входной сигнал предоставления прерывания" 8.10 и запрещает распространение этого сигнала другим устройствам. Устройство ввода-вывода 3 (фиг.3) помещает адрес вектора на векторные шины 29 (13-8) и через приемопередатчики первый и второй 38, 39 узла селектора адреса 24 (фиг.3, 4) в режиме "Чтение", когда на входе разрешения состояния высокого импеданса установлен уровень логического нуля микроЭВМ, а на входе разрешения открытого вывода установлен уровень логической единицы микроЭВМ с векторных входов названных приемопередатчиков 38, 39 на магистральные адресно-информационные входы-выходы 6.(7-2) помещает адрес вектора прерывания, вырабатывает сигнал "Ответ устройства" 8.6 и снимает магистральный сигнал "Запрос на прерывание" 8.8. Если магистральный сигнал "Ответ устройства" 8.6 не вырабатывается в течение 10 мнс, центральный процессор переходит в режим пульта с устройством ввода-вывода 3.

4. Центральный процессор 2 принимает адрес вектора прерывания и снимает магистральные сигналы "Чтение данных" 8.4 и "Входной сигнал предоставления прерывания" 8.10.

5. Устройство ввода-вывода снимает магистральный сигнал "Ответ устройства" 8.6 по завершении передачи вектора прерывания.

6. Центральный процессор 2 помещает в стек текущее содержимое счетчика команд и регистра состояния процессора и загружает в них новое содержимое из двух последовательных ячеек, адрес первой из которых является адресом вектора прерывания, после чего переходит к выполнению программы устройства, запросившего прерывание. Работа устройства ввода-вывода в режиме ввода с организацией векторного прерывания: информация может быть передана от внешнего устройства в магистраль 1 микроЭВМ, если флаг "Разрешение прерывания" установлен, т.е. установлен шестой разряд регистра состояния приемника в уровень логической единицы микроЭВМ. Регистр данных в узле приемопередачи 27 (фиг. 3) асинхронного приемопередатчика заполняется информацией от внешнего устройства. После заполнения устанавливается флаг "Готовность чтения", т.е. устанавливается седьмой разряд регистра состояния приемника в уровень логической единицы микроЭВМ, формирующий сигнал "Готов ввод" 30.4, который поступает в узел приемопередачи 27 (фиг.3). Если установлен шестой разряд в регистре состояния приемника асинхронного приемопередатчика в узле приемопередачи 27 (фиг. 3), по сигналу "Готов ввод" 30.4 формируется магистральный сигнал "Запрос на прерывание" 8.8, поступающий в магистраль 1 микроЭВМ с выхода узла приемопередачи 27. Центральный процессор 2 (фиг.2) вырабатывает магистральные сигналы "Чтение данных" 8.4 и "Входной сигнал предоставления прерывания" 8.10, которые поступают в узел приемопередачи 27 (фиг.3) и вырабатывают вектор прерывания, поступающий по векторным шинам 29.(13-8) на вход селектора адреса 24 (фиг.4), где через первый и второй приемопередатчики 38, 39 с векторных входов аналогично, как и в режиме "Чтение", передается в магистраль 1 микроЭВМ адрес вектора прерывания устройства ввода-вывода при условии, что адресные входы приемопередатчиков 38, 39 подключены к общей шине. МикроЭВМ переходит на подпрограмму обслуживания внешнего устройства, затребовавшего прерывание. В режиме вывода информации с организацией векторного прерывания из магистрали 1 микроЭВМ во внешнее устройство, если флаг "Разрешение прерывания", то есть шестой разряд регистра состояния передатчика установлен в уровень логической единицы микроЭВМ центральным процессором 2. Когда регистр данных асинхронного приемопередатчика в узле приемопередачи 27 (фиг.3) свободен, устанавливается флаг "Готовность записи", т.е. седьмой разряд регистра состояния передатчика устанавливается в логическую единицу микроЭВМ, Формируется на выходе узла приемопередачи 27 сигнал "Готов вывод" 30.5, который поступает в узел регистра состояния 23 и в узел приемопередачи 27 на вход схемы прерывания. Если установлен шестой разряд регистра состояния в уровень логической единицы микроЭВМ в узле приемопередачи 27 по сигналу "Готов вывод" 30.5, на выходе узла приемопередачи 27 (фиг.3) формируется магистральный сигнал "Запрос на прерывание" 8.8 и поступает через магистраль 1 микроЭВМ в центральный процессор 2, который вырабатывает магистральные сигналы "Чтение данных" 8.4 и "Входной сигнал предоставления прерывания" 8.10. Первый сигнал поступает через пятый приемопередатчик 42 узла селектора адреса 24 (фиг.4) в узел логики управления 25 (фиг.5), с выхода которого сигнал "Чтение данных второго типа" 35.5 поступает в узел приемопередачи 27 (фиг.3) на вход схемы прерывания, куда поступает также магистральный сигнал "Входной сигнал предоставления прерывания" 8.10. Эти сигналы инициируют передачу вектора прерывания с выхода узла приемопередачи 27 на векторные входы первого и второго приемопередатчиков 38, 39. Передача вектора прерывания в магистраль 1 происходит аналогично, как описано в цикле "Чтение". В режиме программного обмена информации центральный процессор 2 опрашивает регистр данных в асинхронном приемопередатчике узла приемопередачи 27 (фиг. 3), и, когда он свободен, устанавливается седьмой разряд регистра состояния в логический уровень единицы микроЭВМ передатчика узла приемопередачи 27 (фиг. 3) и устанавливается в единичный уровень микроЭВМ сигнал "Готов вывод" 30.5 на выходе узла приемопередачи 27. Центральный процессор 2 по этому сигналу формирует сигнал "Запись данных" 8.2, а если формируется на выходе узла приемопередачи 27 (фиг.3) сигнал "Готов ввод" 30.4, т.е. когда устанавливается седьмой разряд в логическую единицу микроЭВМ регистра состояния узла приемопередачи 27, центральный процессор 2 формирует сигнал "Чтение данных" 8.4. Векторная шина четвертого типа 29.11 поступает на первый элемент ИЛИ-НЕ 57 узла логики управления 25 (фиг.5) и по сигналу "Запись данных" 35.2 или "Чтение данных третьего типа" 35.6 через третий элемент ИЛИ 47 узла логики управления 25 (фиг.5) подается на вход первого элемента ИЛИ-НЕ 57, с выхода которого через элемент НЕ 50 - на вход первого передатчика 63 для формирования магистрального сигнала "Ответ устройства" 8.6. В случае непоступления сигнала "Ответ устройства" 8.6 через второй вход первого передатчика 50 с инверсного выхода одновибратора 65 через 10 мкс сформируется ошибка по четвертому вектору.

На четвертый вход одновибратора 65 подается сигнал "Устройство выбрано" 28 уровнем логической единицы микроЭВМ с первого выхода набора D-триггеров 64 и запускается одновибратор 65, постоянная времени RC цепи которого задана на 10 мкс.

На четвертый передатчик 56 узла логики управления 25 (фиг.5) подается адресная шина первого типа 33.5 и "Чтение данных второго типа" 35.6 для управления адресно-информационным входом-выходом 34.2.

В узле логики управления 25 (фиг.5) с выхода второго передатчика 62 по сигналу "Устройство выбрано" 28 формируется сигнал "Чтение данных третьего типа" 35.6 на выходе четвертого элемента ИЛИ-НЕ 56 в зависимости от состояния уровня сигнала "Чтение данных второго типа" 35.5 на входе четвертого элемента ИЛИ-НЕ 56. При сигнале 35.5 уровнем логического нуля микроЭВМ и при уровне логической единицы микроЭВМ сигнала 28 на выходе элемента ИЛИ-НЕ 56 формируется уровень логической единицы микроЭВМ и через элемент НЕ 52 низким логическим сигналом микроЭВМ поступает на управление состояния высокого импеданса первого приемодатчика 38 узла селектора адреса 24 (фиг.4).

В данной микроЭВМ центральный процессор 2 выполнен по технической документации [3] . Устройство ввода выполнено по заявке 3796864 (а.с. СССР 1243033) с использованием элементов перепрограммируемой памяти после стирания информации ультрафиолетовым светом. В устройстве ввода-вывода 3 узел адаптера связи 22, узел регистра состояния 23, узел управления приемопередачи 26, узел приемопередачи 27 выполнены, как в прототипе.

Сокращение числа оборудования достигается за счет исключения в устройстве ввода-вывода 3 узла дешифраторов и узла программируемой матрицы. Повышение производительности микроЭВМ достигается за счет исключения программируемой логической матрицы из цепи управления приемопередачей в устройстве ввода-вывода 3.

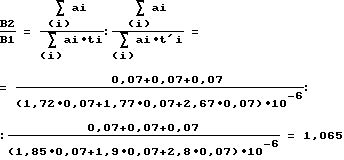

Тип программируемой логической матрицы КР556 РТ2. Время разрешения, выборка адреса и выборка хранимой информации соответственно составляют 30, 70 и 30 нс, т.е. цикл обращения к ПЛМ составляет 130 нс. Рост производительности рассчитывается по ГОСТ 16325-86 Приложение 2, раздел 2 с учетом времени выполнения операции обмена информации с устройством ввода-вывода 3 в циклах "Чтение" - 1,85 мкс, "Записи" - 1,9 мкс, "Чтение-модификация-запись" 2,8 мкс в прототипе с применением центрального процессора [3]. С уменьшением при обращении через устройство ввода-вывода 3 на 0,13 мкс каждой операции установки данных по сигналу "Чтение данных" 8.4 в цикле "Чтение" или по его отсутствию в цикле "Запись" коэффициент производительности микроЭВМ возрастет с учетом веса ai=0,07 названных операций по приведенному ГОСТУ и учетом сокращения времени на 0,13 мкс:

Таким образом, рост производительности предлагаемой микроЭВМ по сравнению с прототипом [2] составляет 6,5%.

Источники информации

1. Дж. Мик. и др. Проектирование микропроцессорных устройств с разрядно-модульной организацией. - М. : Мир, т. 1, 1984 г., с. 7, рис. 1, 2 (аналоги).

2. RU, патент 2108619, G 06 F 15/00, 1994 г. (прототип).

3. Микроэлектронная вычислительная машина "Электроника МС 1280", ПГЩМ 2.791.007 ТУ, з-д "Процессор", г. Воронеж, 1986 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1566359A1 |

| Станция локальной сети | 1990 |

|

SU1824640A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| Устройство для контроля дублированной системы | 1985 |

|

SU1293861A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

Изобретение относится к области микропроцессорной техники и может использоваться для реализации обмена информацией. Техническим результатом является увеличение быстродействия обмена информацией. Устройство содержит центральный процессор, устройство ввода-вывода, устройство ввода, статическое запоминающее устройство, при этом устройство ввода-вывода содержит узел адаптера связи, узел регистра состояния, узел селектора адреса, узел логики управления, узел управления передачей, узел приемопередачи. 5 ил.

Микроэлектронная вычислительная машина, содержащая центральный процессор, устройство ввода-вывода, статическое запоминающее устройство, устройство ввода, при этом устройство ввода-вывода содержит узел адаптера связи, узел регистра состояния, узел селектора адреса, узел логики управления, узел управления приемопередачей, узел приемопередачи, причем узел селектора адреса содержит пять приемопередатчиков, программируемую логическую матрицу, элемент развязки, узел логики управления содержит четыре элемента ИЛИ-НЕ, элемент И, два элемента И-НЕ, три элемента ИЛИ, пять элементов НЕ, три передатчика, набор D-триггеров, одновибратор, ограничительный элемент, накопительный элемент, при этом узел адаптера связи подключен соответственно адресно-информационными входами-выходами второго бита и первого типа нулевого бита к одноименным выходам узла селектора адреса и узла управления приемопередачей, входами "Установка", "Управление выходными данными" - к одноименным выходам узла приемопередачи, входом "Регистр состояния выхода" - к одноименному выходу узла управления приемопередачей, информационные вход "Прием данных" и выход "Передача данных" образуют токовую петлю, узел регистра состояния подключен соответственно адресными входами с второго по четвертый бит к одноименным выходам узла логики управления и одноименным входам узла управления приемопередачей, входом "Останов" - к одноименному выходу узла адаптера связи, входами "Разрешение ввода", "Разрешение вывода", "Готов ввод", "Готов вывод", "Ошибка четности", "Ошибка стопового бита", "Ошибка переполнения" подключен к одноименным выходам узла приемопередачи, входом "Управление входом" - к одноименному выходу узла управления приемопередачей, адресно-информационными входами-выходами первого типа - к одноименным входам-выходам узла селектора адреса, входом "Чтение регистра состояния" - к одноименному выходу узла логики управления, который подключен соответственно адресно-информационными входами-выходами с первого по тринадцатый бит и первого типа нулевого бита к одноименным входам-выходам узла селектора адреса, входами "Выбор пульта", "Чтение данных первого типа", "Запись данных", "Синхронизация обмена", "Выборка устройства" - к одноименным выходам узла селектора адреса, входом "Ошибка стопового бита" - к одноименному выходу узла приемопередачи, магистральными входами-выходами "Авария источника питания", "Ответ устройства", "Останов" - к одноименным входам-выходам магистрали, узел селектора адреса подключен соответственно входом с первого по шестой вектор к одноименным выходам узла приемопередачи, выходами "Выборка устройства", "Управление входом" - к одноименным входам узла логики управления, магистральными адресно-информационными входами-выходами, магистральными входами-выходами "Выборка устройства", "Запись данных", "Синхронизация обмена", "Чтение данных", "Авария источника питания", "Признак записи байта" - к одноименным входам-выходам магистрали, узел управления приемопередачей подключен соответственно адресными входами с первого по четвертый битами, адресными входами первого типа к одноименным выходам узла логики управления, адресно-информационными шинами - к одноименным шинам узла приемопередачи, входами "Запись младшего байта", "Чтение входного буфера" - к одноименным выходам узла логики управления, узел приемопередачи подключен соответственно адресным входом второго типа, входами "Чтение данных второго типа", "Чтение данных пятого типа" - к одноименным выходам узла логики управления, адресно-информационными входами-выходами с первого по седьмой бит и первого типа нулевого бита - к одноименным входам-выходам узла управления приемопередачей, входами "Управление входными данными", "Синхронизация" - к одноименным выходам узла адаптера связи, входами "Регистр состояния выхода", "Разрешение буфера", "Регистр состояния входа", "Управление входом" - к одноименным выходам узла управления приемопередачей, магистральными входами-выходами "Запрос прерывания", "Выходной сигнал предоставления прерывания" и "Установка" - к одноименным входам-выходам магистрали, причем в узле селектора адреса первый приемопередатчик первой и шестой векторными входными шинами и магистральным входом-выходом "Запись данных" подключен соответственно к одноименным шинам и к входу-выходу узла селектора адреса, магистральные входы-выходы нулевого, второго, шестого и седьмого битов и соответствующими адресно-информационными входами-выходами подключены соответственно к одноименным входам-выходам узла селектора адреса, второй приемопередатчик второй, третьей и шестой векторными входными шинами подключен соответственно к одноименным входам узла селектора адреса, магистральными адресно-информационными входами-выходами первого и с третьего по пятый битами и соответствующими адресно-информационными входами подключены соответственно к одноименным входам-выходам узла селектора адреса, третий приемопередатчик магистральными адресно-информационными входами-выходами с двенадцатого по пятнадцатый битами и соответствующими адресно-информационными входами-выходами подключены соответственно к одноименным входам-выходам узла селектора адреса, четвертый приемопередатчик магистральными адресно-информационными входами-выходами с восьмого по одиннадцатый битами и соответствующими адресно-информационными входами-выходами первого типа подключен соответственно к одноименным входам-выходам узла селектора адреса, пятый приемопередатчик магистральными входами-выходами "Выборка устройства", "Запись данных", "Синхронизация обмена", "Чтение данных" и выходами "Сигнал выборки устройства", "Запись данных", "Синхронизация обмена", "Чтение данных" подключен соответственно к одноименным входам-выходам узла селектора адреса, программируемая логическая матрица с первого по тринадцатый адресными входами подключена соответственно адресно-информационными входами первого типа нулевого бита и входами с первого по двенадцатый бит к одноименным входам узла селектора адреса, выходами "Выборка устройства" и "Выборка пульта" подключена соответственно к одноименным выходам узла селектора адреса, выход пятого приемопередатчика "Сигнал выборки устройства" подключен к пятнадцатому адресному входу программируемой логической матрицы, выход равенства адреса третьего приемопередатчика подключен к входу элемента развязки, при этом в узле логики управления с первого по третий информационные входы набора D-триггеров входами "Сигнал выборка устройства", адресно-информационными входами первого и второго битов подключены соответственно к одноименным входам узла логики управления, пятый и шестой информационные входы набора D-триггеров адресно-информационными входами четвертого бита и первого типа нулевого бита подключены соответственно к одноименным входам узла логики управления, вход адресно-информационный третьего бита и шина управления "Выбор пульта" подключены соответственно к одноименным входам узла логики управления и к первому и второму входам первого элемента ИЛИ, выход которого подключен к четвертому информационному входу набора D-триггеров, вход "Синхронизация обмена" подключен к первому входу второго элемента ИЛИ, к тактирующему входу набора D-триггеров и к входу узла логики управления, выход второго элемента "ИЛИ" подключен к сбросовому входу набора D-триггеров, выход первого элемента ИЛИ-НЕ через первый элемент НЕ подключен к первому входу первого передатчика, инверсный выход одновибратора подключен к второму входу первого передатчика, выход которого подключен к магистральному выходу "Ответ устройства" узла логики управления, шина "Устройство выбрано" с первого выхода набора D-триггеров подключена к первому входу элемента И и к входу второго передатчика, к второму входу элемента И подключен вход "Запись данных" узла логики управления, выход элемента И подключен к первому входу третьего элемента ИЛИ и через второй элемент НЕ к первому входу второго элемента ИЛИ-НЕ, второй выход набора D-триггеров адресной шиной первого бита подключен к выходу узла логики управления, к первым выходам первого и второго элементов И-НЕ и через третий элемент НЕ к выходу адресной шины первого типа узла логики управления, третий выход набора D-триггеров адресной шиной второго бита подключен к выходу узла логики управления, к первому входу третьего элемента ИЛИ-НЕ и второму входу второго элемента И-НЕ, выходы которых соответственно подключены к выходам "Чтение входного буфера" и "Адресная шина второго типа" узла логики управления, четвертый и пятый выходы набора D-триггеров подключены соответственно адресными шинами третьего и четвертого бита к выходам узла логики управления, шестой выход набора D-триггеров "Адресная шина нулевого бита" подключен к второму входу второго элемента ИЛИ-НЕ, выход которого подключен к выходу "Запись младшего байта" узла логики управления, вход узла логики управления "Ошибка стопового бита" через третий передатчик подключен к магистральному выходу "Останов" узла логики управления, вход узла логики управления "Чтение данных первого типа" через четвертый элемент НЕ подключен к первому входу четвертого элемента ИЛИ-НЕ, выход которого подключен соответственно к вторым входам третьего элемента ИЛИ и первого элемента И-НЕ и через пятый элемент НЕ подключен к выходу "Чтение данных пятого типа" узла логики управления, одновибратор первым входом подключен через ограничительный элемент к положительной шине источника питания микроЭВМ и через накопительный элемент к второму входу одновибратора, третий вход одновибратора подключен к обшей шине, сбросовый вход одновибратора подключен к положительной шине источника питания микроЭВМ, отличающаяся тем, что выход "Чтение данных четвертого типа" узла приемопередачи подключен к одноименному входу узла селектора адреса, выходы узла логики управления "Чтение входного буфера", "Чтение регистра состояния" и "Чтение данных пятого типа" подключены соответственно к одноименным входам узла селектора адреса, адресно-информационными входами/выходами второго бита узел логики управления через адресные шины второго типа и первого бита подключен соответственно к одноименным выходам узла селектора адреса, вход "Четвертая векторная шина" узла логики управления подключен к одноименному выходу узла приемопередачи, причем в узел селектора адреса включен элемент НЕ, через который вход "Управление входными данными" узла селектора адреса подключен к входу "Разрешение состояния высокого импеданса" третьего приемопередатчика, выход элемента развязки подключен к адресно-информационному входу-выходу пятнадцатого бита третьего приемопередатчика, на вход "Разрешение открытого вывода" которого подключена с входа узла селектора адреса адресная шина первого бита, входы узла селектора адреса "Чтение данных пятого типа" и адресная шина второго типа подключены соответственно к входам "Разрешение состояния высокого импеданса" и "Разрешение открытого вывода" первого приемопередатчика, входы узла селектора адреса "Чтение данных четвертого типа" и "Чтение регистра состояния" подключены соответственно к входам "Разрешение состояния высокого импеданса" и "Разрешение открытого вывода" второго приемопередатчика, адресно-информационный вход второго бита узла селектора адреса подключен к одноименному выходу первого приемопередатчика, адресно-информационный выход тринадцатого бита третьего приемопередатчика подключен к четырнадцатому адресному входу программируемой логической матрицы, при этом в узел логики управления включен четвертый передатчик, входы узла логики управления "Адресная шина первого типа" и "Чтение данных третьего типа" подключены соответственно к первому и второму входам четвертого передатчика, с выхода которого адресно-информационный выход второго бита подключен к выходу узла логики управления, выход второго передатчика подключен к второму входу четвертого элемента ИЛИ-НЕ, на второй вход третьего элемента ИЛИ-НЕ подключен вход узла логики управления "Чтение данного пятого типа", выход третьего элемента ИЛИ подключен к первому входу первого элемента ИЛИ-НЕ, к второму входу которого подключена с входа узла логики управления четвертая векторная шина, с первого выхода набора D-триггеров шина "Устройство выбрано" подключена к четвертому входу одновибратора.

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| МИК ДЖ | |||

| и др | |||

| Проектирование микропроцессорных устройств с разрядно-модульной организацией | |||

| - М.: Мир, т.1, с.7, рис.1, 2 | |||

| ЭВМ | 1990 |

|

RU2024928C1 |

| US 4996662 А, 26.02.1991. | |||

Авторы

Даты

2003-07-27—Публикация

2000-06-08—Подача