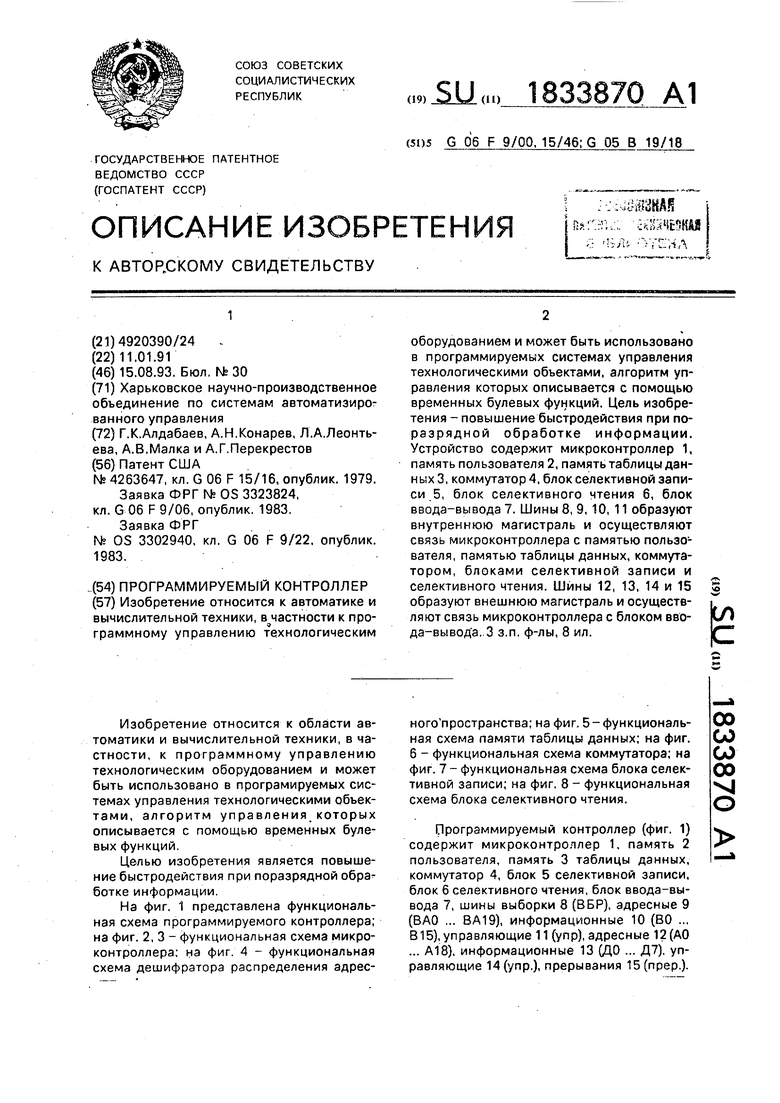

Изобретение относится к области автоматики и вычислительной техники, в частности, к программному управлению технологическим оборудованием и может быть использовано в програмируемых системах управления технологическими объектами, алгоритм управления которых описывается с помощью временных булевых функций.

Целью изобретения является повышение быстродействия при поразрядной обработке информации.

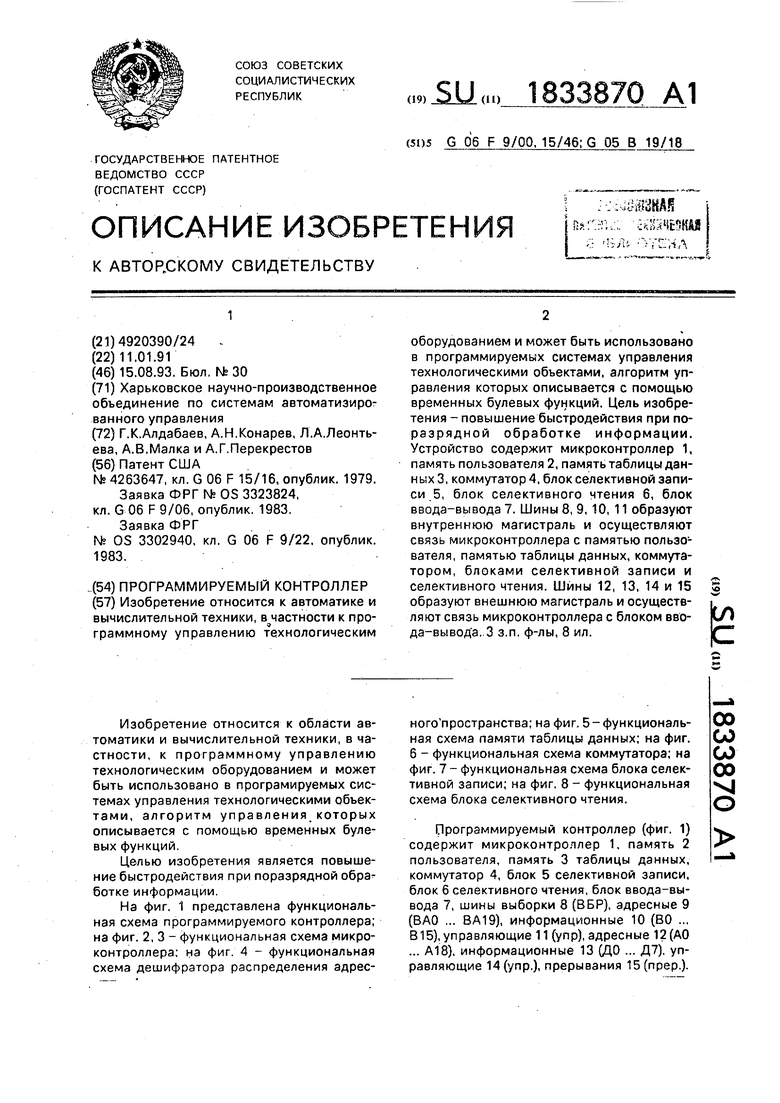

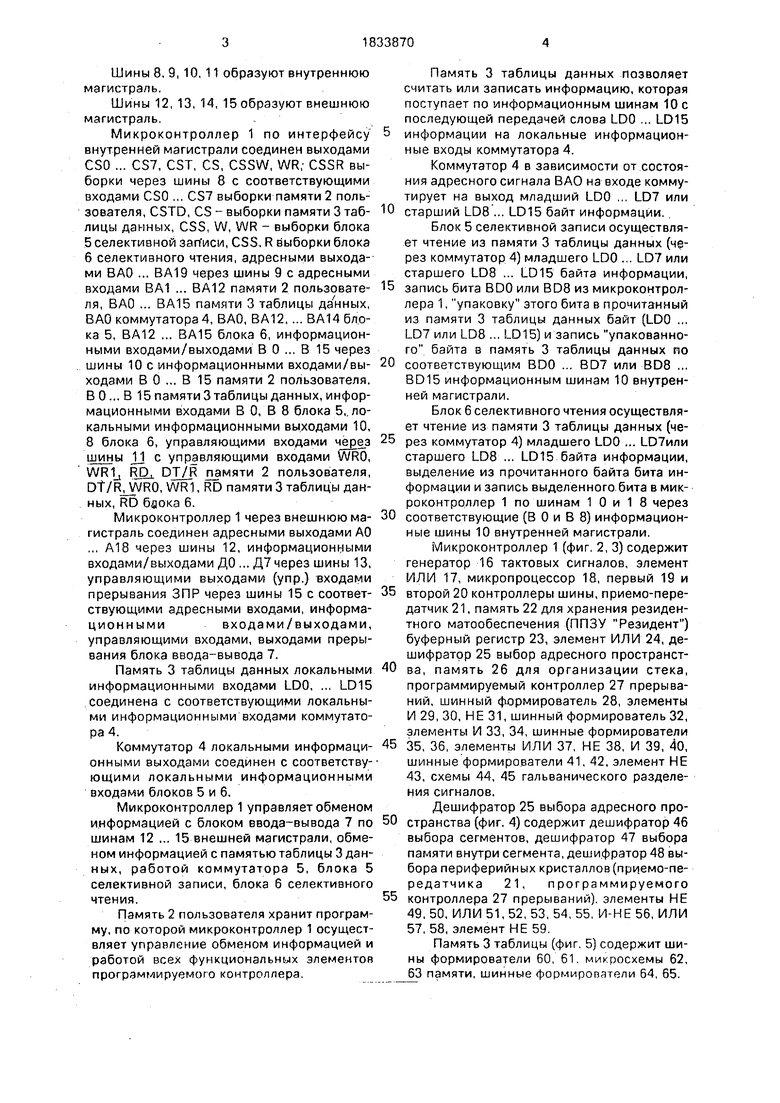

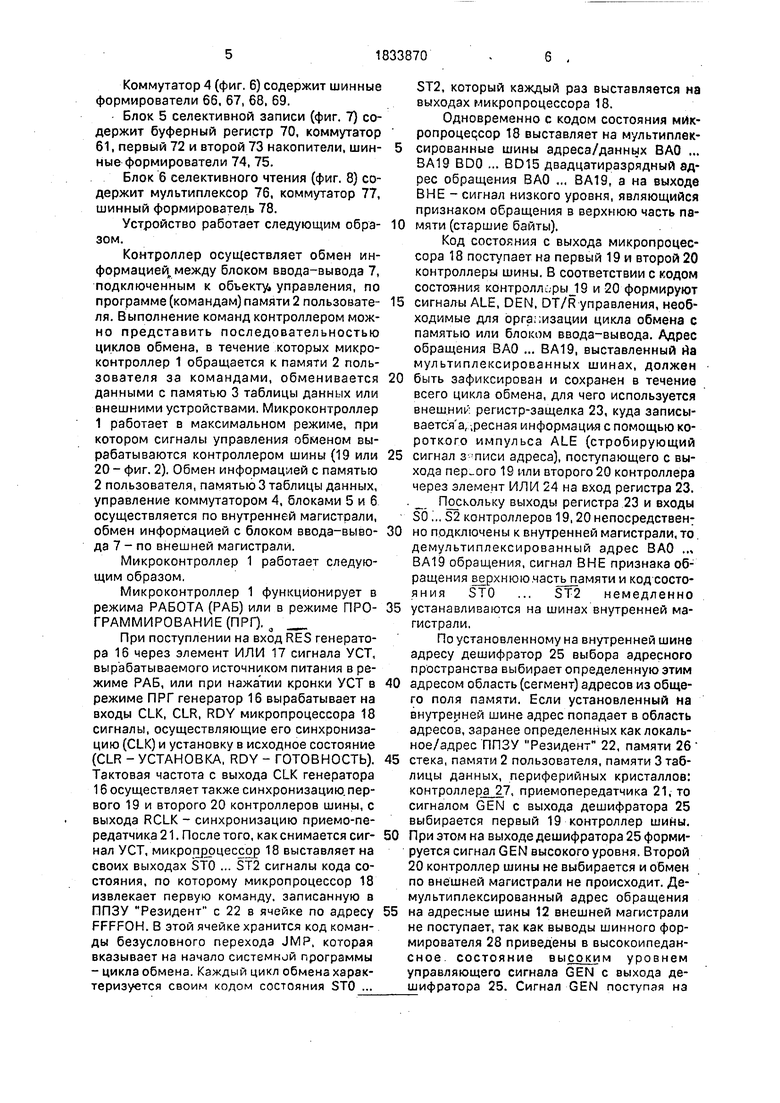

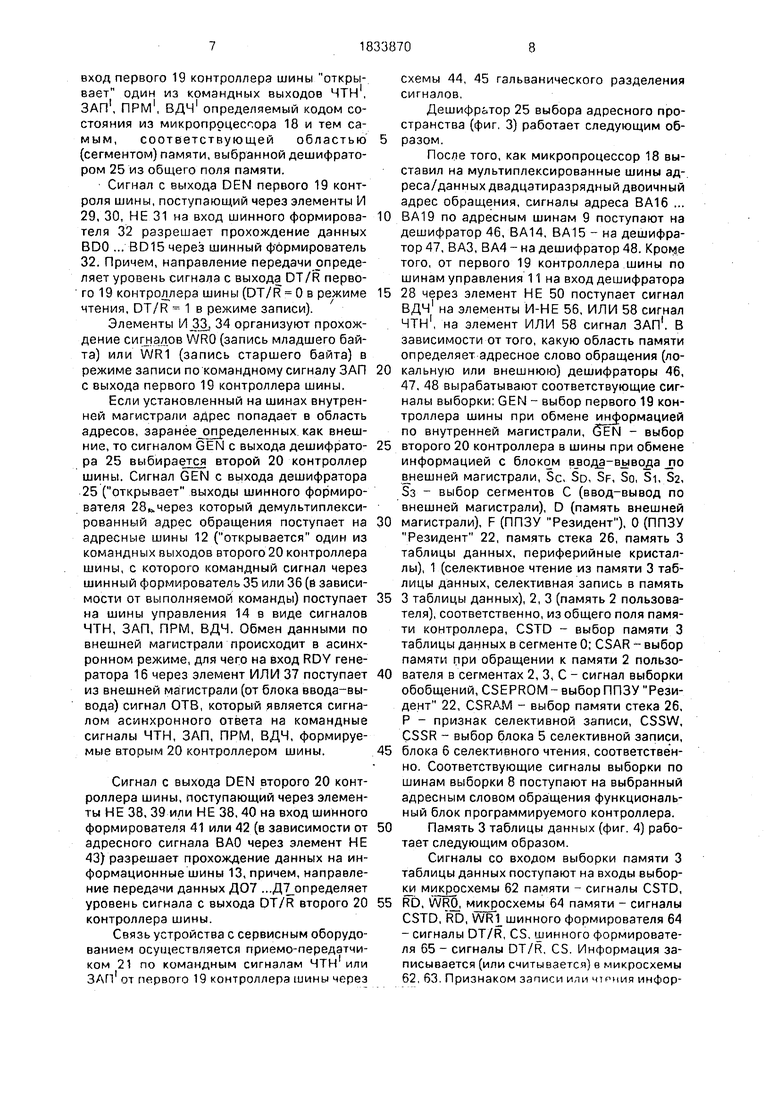

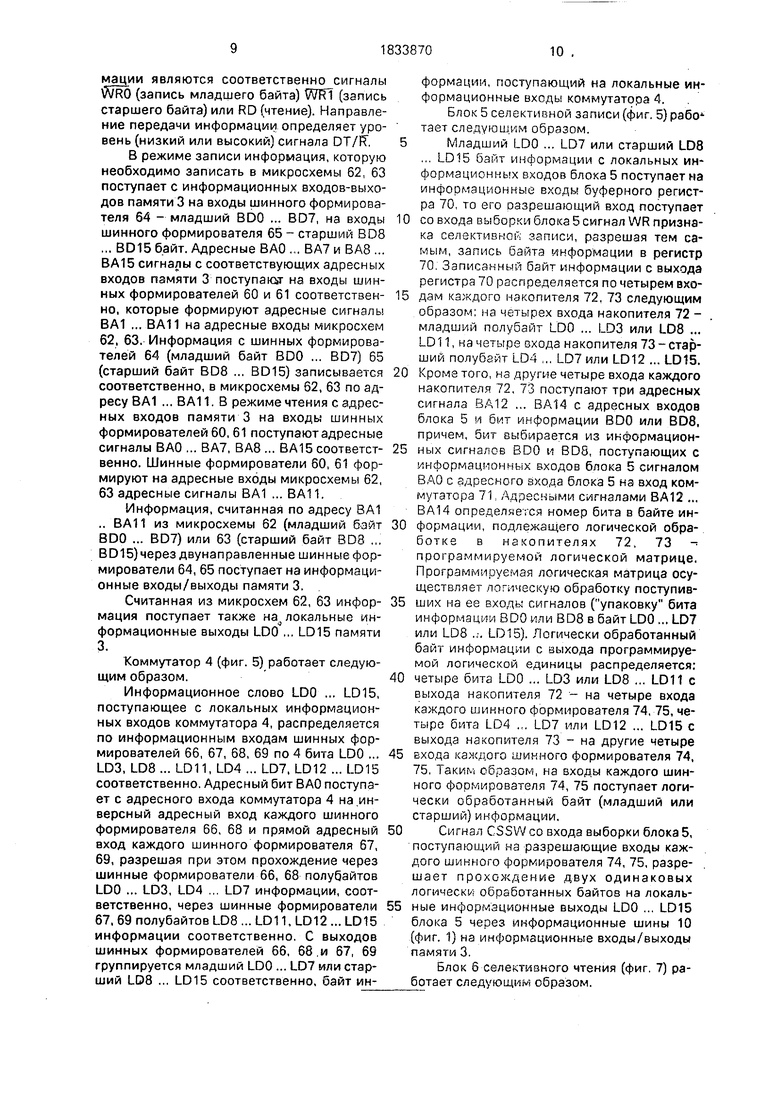

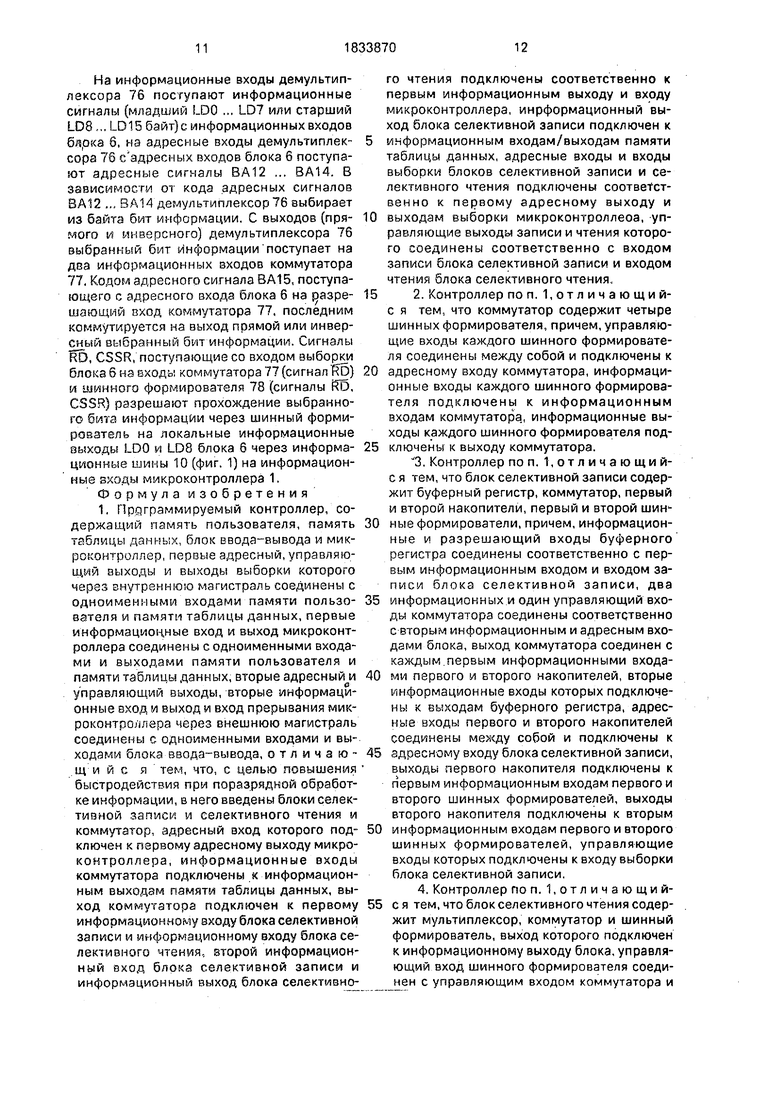

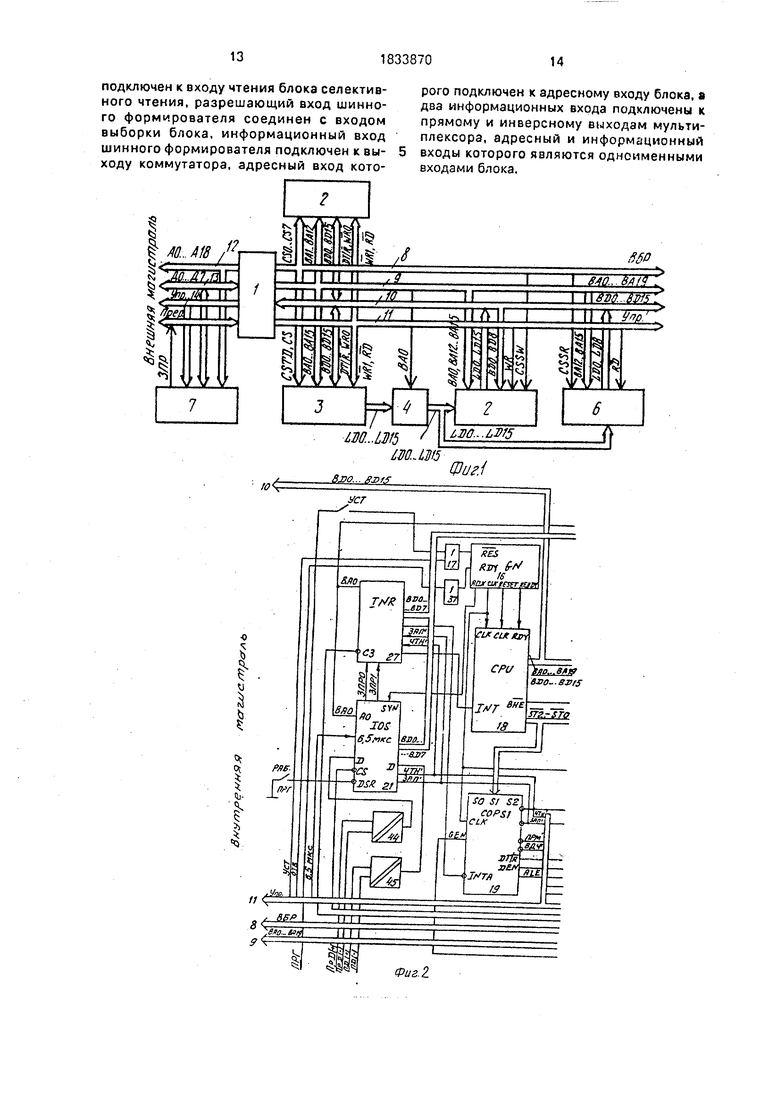

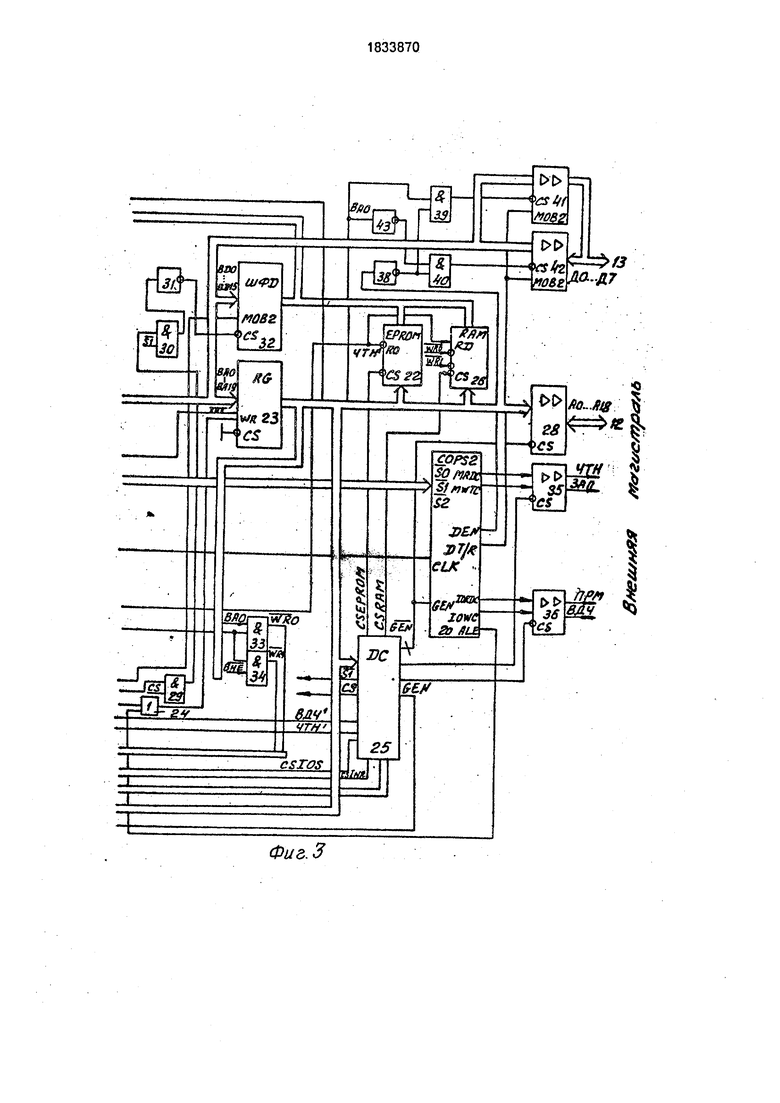

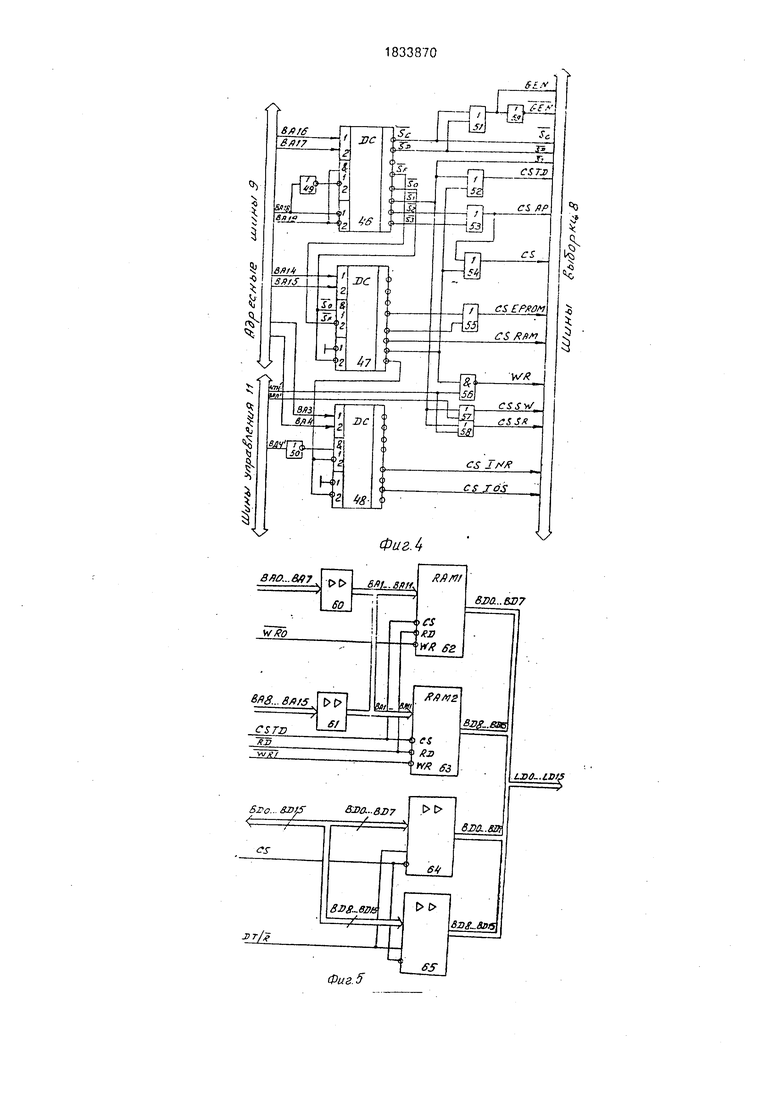

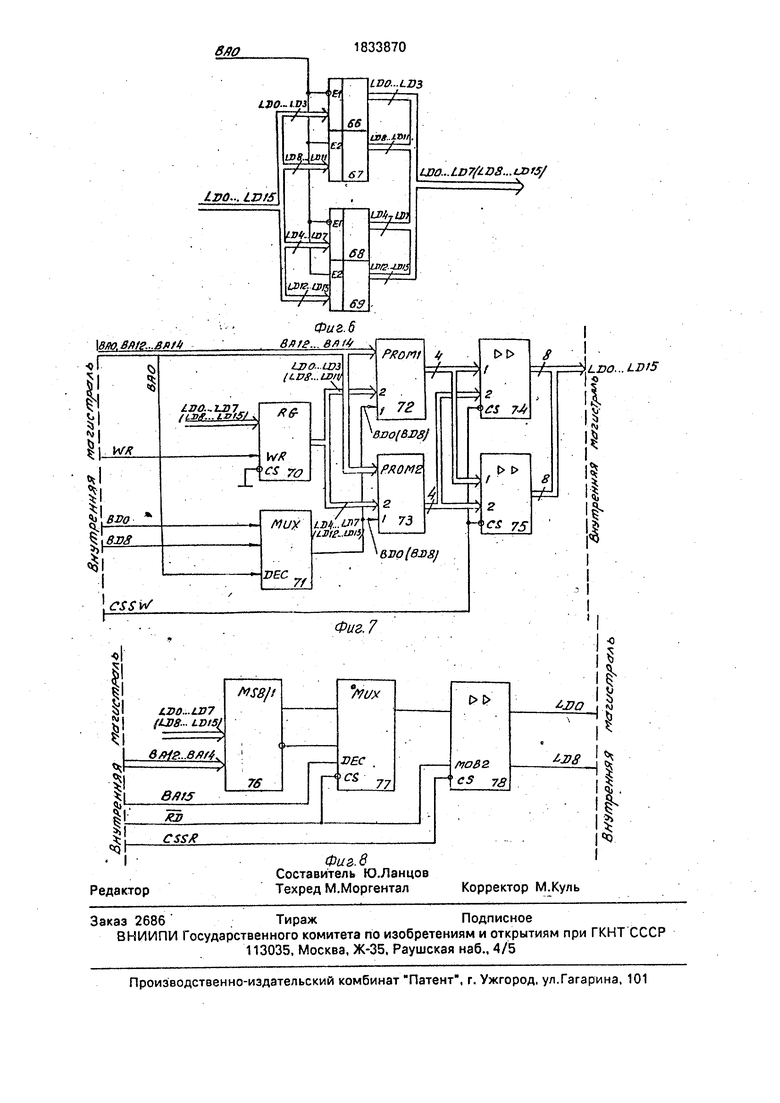

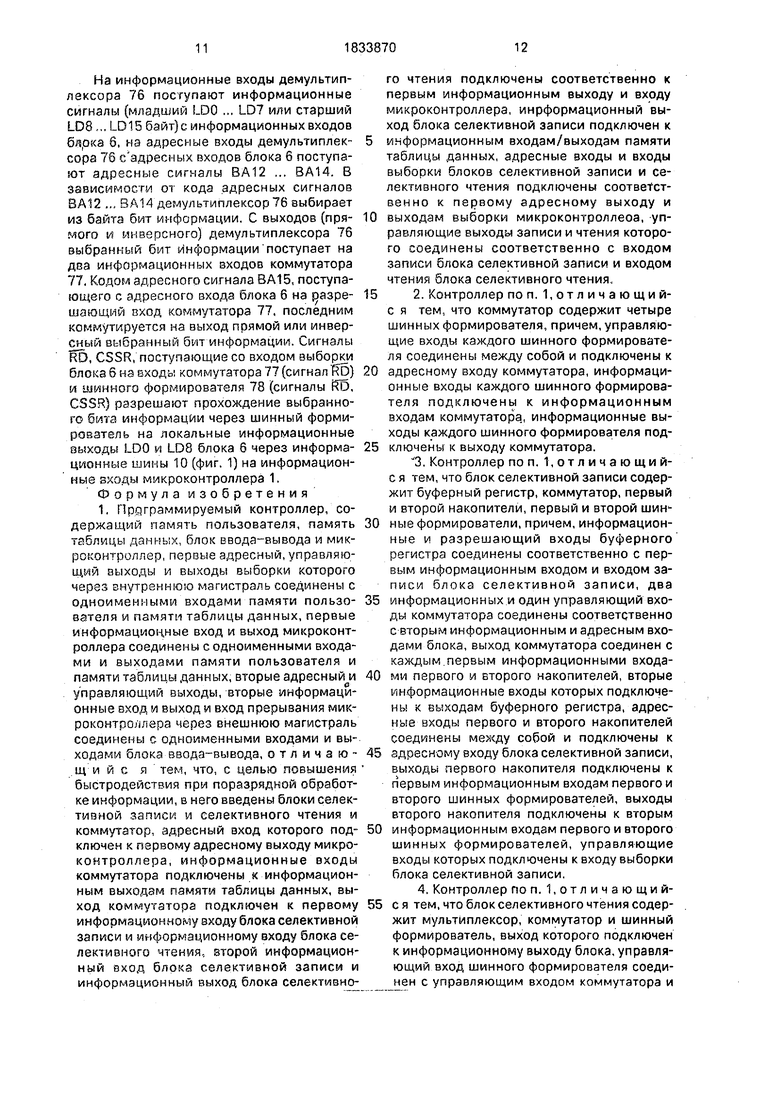

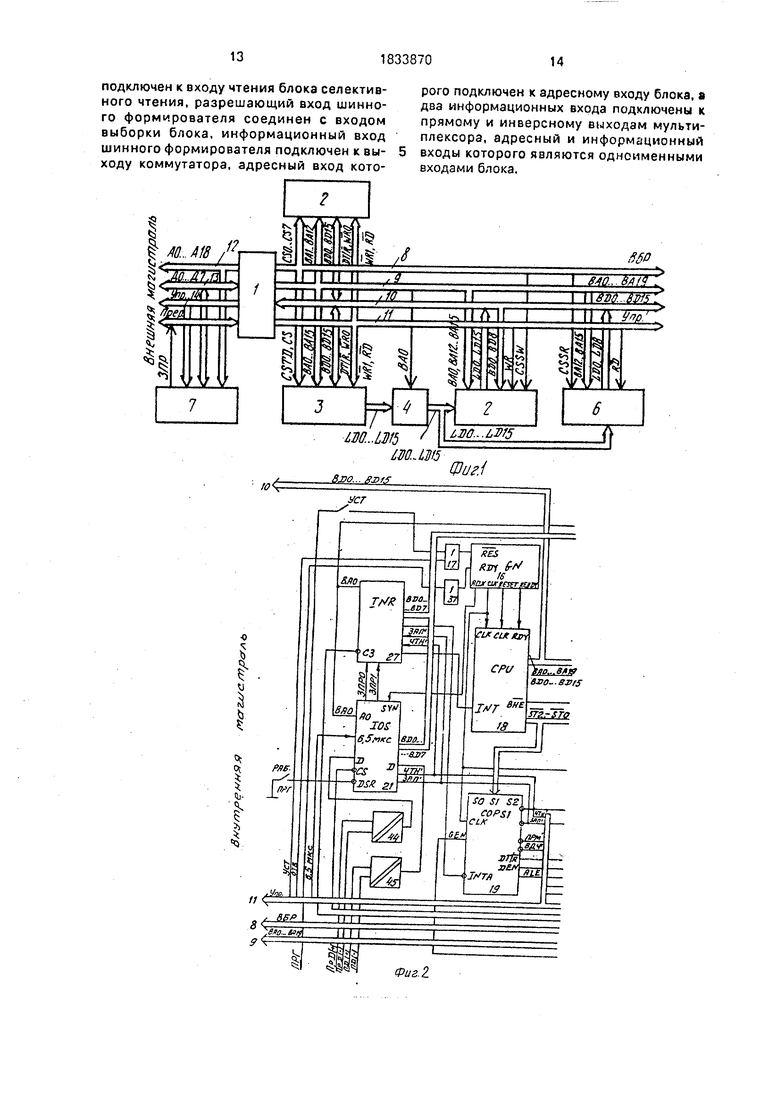

На фиг. 1 представлена функциональная схема программируемого контроллера; на фиг. 2,3- функциональная схема микроконтроллера: на фиг. 4 - функциональная схема дешифратора распределения адресного пространства; на фиг 5-функциональная схема памяти таблицы данных; на фиг. 6 - функциональная схема коммутатора; на фиг. 7 - функциональная схема блока селективной записи; на фиг. 8 - функциональная схема блока селективного чтения.

Программируемый контроллер (фиг. 1) содержит микроконтроллер 1, память 2 пользователя, память 3 таблицы данных, коммутатор 4, блок 5 селективной записи, блок 6 селективного чтения, блок ввода-вывода 7, шины выборки 8 (ВБР), адресные 9 (ВАО ... ВА19), информационные 10 (ВО ... В15), управляющие 11 (упр), адресные 12 (АО ... А18), информационные 13 (ДО ... Д7), управляющие 14 (упр.), прерывания 15(прер.).

00

со

CJ 00 XI

о

Шины 8, 9, 10, 11 образуют внутреннюю магистраль.

Шины 12, 13, 14, 15 образуют внешнюю магистраль.Микроконтроллер 1 по интерфейсу внутренней магистрали соединен выходами CSO ... CS7, CST, CS, CSSW, WR,- CSSR выборки через шины 8 с соответствующими входами CSO ... CS7 выборки памяти 2 пользователя, CSTD, CS - выборки памяти 3 таблицы данных, CSS, W, WR - выборки блока

5селективной загГисм, CSS. R ёыборки блока

6селективного чтения, адресными выходами ВАО ... ВА19 через шины 9 с адресными входами ВА1 .... ВА12 памяти 2 пользователя, ВАО ... ВА15 памяти 3 таблицы данных, ВАО коммутатора 4, ВАО, ВА12, ... ВА14 блока 5, ВА12 ... ВА15 блока б, информационными входами/выходами В 0 ... В 15 через шины 10 с информационными входами/выходами В 0 ... В 15 памяти 2 пользователя, В 0... В 15 памяти 3 таблицы данных, информационными входами В О, В 8 блока 5,, локальными информационными выходами 10, 8 блока 6, управляющими входами через шины JJ с управляющими входами WRO, RCL. DT/R гишяти 2 пользователя, Dt/R,WRO, WR1, RD памяти 3 таблицы данных, RD баока 6.

Микроконтроллер 1 через внешнюю магистраль соединен адресными выходами АО .,, А18 через шины 12, информационными входами/выходами ДО ... Д7 через шины 13, управляющими выходами (упр.) входами прерывания ЗПР через шины 15 с соответствующими адресными входами, информационнымивходами/выходами, управляющими входами, выходами прерывания блока ввода-вывода 7.

Память 3 таблицы данных локальными информационными входами LDO, .,, LD15 соединена с соответствующими локальными информационными входами коммутатора 4.

Коммутатор 4 локальными информационными выходами соединен с соответствующими локальными информационными входами блоков 5 и 6.

Микроконтроллер 1 управляет обменом информацией с блоком ввода-вывода 7 по шинам 12 ... 15 внешней магистрали, обменом информацией с памятью таблицы 3 дан- ных, работой коммутатора 5, блока 5 селективной записи, блока 6 селективного чтения.

Память 2 пользователя хранит программу, по которой микроконтроллер 1 осуществляет управление обменом информацией и работой всех функциональных элементов программируемого контроллера.

Память 3 таблицы данных позволяет считать или записать информацию, которая поступает по информационным шинам 10 с последующей передачей слова LDO ... LD15

информации на локальные информационные входы коммутатора 4.

Коммутатор 4 в зависимости от состояния адресного сигнала ВАО на входе коммутирует на выход младший LDO ... LD7 или

0 старший LD8 ... LD15 байт информации.

Блок 5 селективной записи осуществляет чтение из памяти 3 таблицы данных (через коммутатор 4) младшего LDO ... LD7 или старшего LD8 ... LD15 байта информации,

5 запись бита BDO или BD8 из микроконтроллера 1, упаковку этого бита в прочитанный из памяти 3 таблицы данных байт (LDO .., LD7 или LD8 ... LD15) и запись упакованного байта в память 3 таблицы данных по

0 соответствующим BDO ... BD7 или BD8 ... BD15 информационным шинам 10 внутренней магистрали.

Блок 6 селективного чтения осуществляет чтение из памяти 3 таблицы данных (че5 рез коммутатор 4) младшего LDO ... 1 О7или старшего LD8 ... LD15 байта информации, выделение из прочитанного байта бита информации и запись выделенного.бита в микроконтроллер 1 по шинам 1 0 и 1 8 через

0 соответствующие (В 0 и В 8) информационные шины 10 внутренней магистрали.

Микроконтроллер 1 (фиг, 2, 3) содержит генератор 16 тактовых сигналов, элемент ИЛИ 17, микропроцессор 18, первый 19 и

5 второй 20 контроллеры шины, приемо-пере- датчик 21, память 22 для хранения резидентного матообеспечения (ППЗУ Резидент) буферный регистр 23, элемент ИЛИ 24, дешифратор 25 выбор адресного пространст0 ва, память 26 для организации стека, программируемый контроллер 27 прерываний, шинный формирователь 28, элементы И 29, 30, НЕ 31, шинный формирователь 32, элементы И 33, 34, шинные формирователи

5 35, 36, элементы ИЛИ 37, НЕ 38, И 39, 40, шинные формирователи 41, 42, элемент НЕ 43, схемы 44, 45 гальванического разделения сигналов.

Дешифратор 25 выбора адресного про0 странства (фиг. 4) содержит дешифратор 46 выбора сегментов, дешифратор 47 выбора памяти внутри сегмента, дешифратор 48 выбора периферийных кристаллов (приемо-пе- редатчика 21, программируемого

5 контроллера 27 прерываний), элементы НЕ 49, 50, ИЛИ 51, 52, 53, 54, 55, И-НЕ 56, ИЛИ 57, 58, элемент НЕ 59.

Память 3 таблицы (фиг. 5) содержит шины формирователи 60, 61, микросхемы 62, 63 памяти, шинные формирователи 64, 65.

Коммутатор 4 (фиг. 6) содержит шинные формирователи 66, 67, 68, 69.

Блок 5 селективной записи (фиг. 7) содержит буферный регистр 70, коммутатор 61, первый 72 и второй 73 накопители, шин- ные формирователи 74, 75.

Блок 6 селективного чтения (фиг. 8) содержит мультиплексор 76, коммутатор 77, шинный формирователь 78.

Устройство работает следующим обра- зом.

Контроллер осуществляет обмен ин- формацией между блоком ввода-вывода 7, подключенным к объекту управления, по программе (командам) памяти 2 пользовате- ля. Выполнение команд контроллером можно представить последовательностью циклов обмена, в течение которых микроконтроллер 1 обращается к памяти 2 пользователя за командами, обменивается данными с памятью 3 таблицы данных или внешними устройствами. Микроконтроллер

1работает в максимальном режиме, при котором сигналы управления обменом вырабатываются контроллером шины (19 или 20 - фиг. 2). Обмен информацией с памятью

2пользователя, памятью 3 таблицы данных, управление коммутатором 4, блоками 5 и 6 осуществляется по внутренней магистрали, обмен информацией с блоком ввода-выво- да 7 - по внешней магистрали.

Микроконтроллер 1 работает следующим образом.

Микроконтроллер 1 функционирует в режима РАБОТА (РАБ) или в режиме ПРО- ГРАММИРОВАНИЕ(ПРГ). о

При поступлении на вход RES генератора 16 через элемент ИЛИ 17 сигнала УСТ, вырабатываемого источником питания в режиме РАБ, или при нажатии кронки УСТ в режиме ПРГ генератор 16 вырабатывает на входы CLK, CLR, RDY микропроцессора 18 сигналы, осуществляющие его синхронизацию (CLK) и установку в исходное состояние (CLR - УСТАНОВКА, RDY - ГОТОВНОСТЬ). Тактовая частота с выхода CLK генератора 16 осуществляет также синхронизацию, первого 19 и второго 20 контроллеров шины, с выхода RCLK - синхронизацию приемо-пе- редатчика 21. После того, как снимается сиг- нал УСТ, микропроцессор 18 выставляет на своих выходах STO ... ST2 сигналы кода состояния, по которому микропроцессор 18 извлекает первую команду, записанную в ППЗУ Резидент с 22 в ячейке по адресу FFFFOH. В этой ячейке хранится код команды безусловного перехода JMP. которая вказывает на начало системной программы - цикла обмена. Каждый цикл обмена характеризуется своим кодом состояния STO ...

ST2, который каждый раз выставляется на выходах микропроцессора 18.

Одновременно с кодом состояния мйк- ропроцерсор 18 выставляет на мультиплексированные шины адреса/данных ВАО ... ВА19 BDO ... BD15 двадцатиразрядный адрес обращения ВАО ... ВА19, а на выходе ВНЕ - сигнал низкого уровня, являющийся признаком обращения в верхнюю часть памяти (старшие байты).

Код состояния с выходз микропроцессора 18 поступает на первый 19 и второй 20 контроллеры шины. В соответствии с кодом состояния контроллйры 19 и 20 формируют сигналы ALE, DEN, DT/R управления, необходимые для организации цикла обмена с памятью или блоком ввода-вывода. Адрес обращения ВАО ... ВА19, выставленный йа мультиплексированных шинах, должен быть зафиксирован и сохранен в течение всего цикла обмена, для чего используется внешний регистр-защелка 23, куда записывается а, .ресная информация с помощью короткого импульса ALE (стробирующий сигнал записи адреса), поступающего с выхода первого 19 или второго 20 контроллера через элемент ИЛИ 24 на вход регистра 23. . Поскольку выходы регистра 23 и входы SO... S2 контроллеров 19,20 непосредствен: но подключены к внутренней магистрали, то. демультиплексированный адрес ВАО .., ВА19 обращения, сигнал ВНЕ признака обращения верхнюю настъдамяти и код состояния STO ... ST2 немедленно устанавливаются на шинах внутренней магистрали,

По установленному на внутренней шине адресу дешифратор 25 выбора адресного пространства выбирает определенную этим адресом область (сегмент) адресов из общего поля памяти. Если установленный на внутренней шине адрес попадает в область адресов, заранее определенных как локальное/адрес ППЗУ Резидент 22, памяти 26 стека, памяти 2 пользователя, памяти 3 таблицы данных, периферийных кристаллов: контроллера 27. приемопередатчика 21, то сигналом GEN с выхода дешифратора 25 выбирается первый 19 контроллер шины. При этом на выходе дешифратора 25 формируется сигнал GEN высокого уровня. Второй 20 контроллер шины не выбирается и обмен по внешней магистрали не происходит. Демультиплексированный адрес обращения на адресные шины 12 внешней магистрали не поступает, так как выводы шинного формирователя 28 приведены в высокоипедан- сное. состояние высоким уровнем управляющего сигнала GEN с выхода дешифратора 25. Сигнал GEN поступая на

вход первого 19 контроллера шины открывает один из командных выходов ЧТН1, ЗАП , ПРМ , ВДЧ определяемый кодом состояния из микропроцессора 18 и тем самым, соответствующей областью (сегментом) памяти, выбранной дешифратором 25 из общего поля памяти.

Сигнал с выхода DEN первого 19 контроля шины, поступающий через элементы И 29, 30, НЕ 31 на вход шинного формирователя 32 разрешает прохождение данных BDO ... BD15 через шинный формирователь 32. Причем, направление передачи определяет уровень сигнала с выхода DT/R первого 19 контроллера шины (DT/R 0 в режиме чтения, DT/R 1 в режиме записи).

Элементы , 34 организуют прохождение сигналов WRO (запись младшего байта) или WR1 (запись старшего байта) в режиме записи по командному сигналу ЗАП с выхода первого 19 контроллера шины.

Если установленный на шинах внутренней магистрали адрес попадает в область адресов, заранёе одределенных. как внешние, то сигналом GEN с выхода дешифратора 25 выбирается второй 20 контроллер шины. Сигнал GEN с выхода дешифратора 25 (открывает выходы шинного формирователя 28&через который демультиплексированный адрес обращения поступает на адресные шины 12 (открывается один из командных выходов второго 20 контроллера шины, с которого командный сигнал через шинный формирователь 35 или 36 (в зависимости от выполняемой команды) поступает на шины управления 14 в виде сигналов ЧТН, ЗАП, ПРМ, ВДЧ. Обмен данными по внешней магистрали происходит в асинхронном режиме, для чего на вход RDY генератора 16 через элемент ИЛИ 37 поступает из внешней магистрали (от блока ввода-вывода) сигнал ОТВ, который является сигналом асинхронного ответа на командные сигналы ЧТН, ЗАП, ПРМ, ВДЧ, формируемые вторым 20 контроллером шины.

Сигнал с выхода DEN второго 20 контроллера шины, поступающий через элементы НЕ 38, 39 или НЕ 38, 40 на вход шинного формирователя 41 или 42 (в зависимости от адресного сигнала ВАО через элемент НЕ 43) разрешает прохождение данных на информационные шины 13,причем,направление передачи данных Д07 ...Доопределяет уровень сигнала с выхода DT/R второго 20 контроллера шины.

Связь устройства с сервисным оборудованием осуществляется приемо-передатчи- ком 21 по командным сигналам ЧТН или ЗАП1 от первого 19 контроллера шины через

схемы 44, 45 гальванического разделения сигналов.

Дешифратор 25 выбора адресного пространства (фиг. 3) работает следующим образом.

После того, как микропроцессор 18 выставил на мультиплексированные шины ад-, реса/данных двадцэтиразрядный двоичный адрес обращения, сигналы адреса ВА16 ...

0 ВА19 по адресным шинам 9 поступают на дешифратор 46, ВА14. ВА15 - на дешифратор 47, ВАЗ, ВА4 - на дешифратор 48. Кроме того, от первого 19 контроллера шины по шинам управления 11 на вход дешифратора

5 28 через элемент НЕ 50 поступает сигнал ВДЧ1 на элементы И-НЕ 56, ИЛИ 58 сигнал ЧТН1, на элемент ИЛИ 58 сигнал ЗАП1. В зависимости от того, какую область памяти определяет адресное слово обращения (ло0 кальную или внешнюю) дешифраторы 46, 47, 48 вырабатывают соответствующие сигналы выборки: GEN - выбор первого 19 контроллера шины при обмене информацией по внутренней магистрали, (JEN - выбор

5 второго 20 контроллера в шины при обмене информацией с блоком в вода-вывода jno внешней магистрали, Sc, SD, SF, So, Si, 82, 83 - выбор сегментов С (ввод-вывод по внешней магистрали), D (память внешней

0 магистрали), F (ППЗУ Резидент), О (ППЗУ Резидент 22, память стека 26, память 3 таблицы данных, периферийные кристаллы), 1 (селективное чтение из памяти 3 таблицы данных, селективная запись в память

5 3 таблицы данных), 2, 3 (память 2 пользователя), соответственно, из общего поля памяти контроллера, CSTD - выбор памяти 3 таблицы данных в сегменте 0; CSAR - выбор памяти при обращении к памяти 2 пользо0 вателя в сегментах 2, 3, С - сигнал выборки обобщений, CSEPROM - выбор ППЗУ Резидент 22, CSRAM - выбор памяти стека 26, Р - признак селективной записи, CSSW, CSSR - выбор блока 5 селективной записи,

5 блока 6 селективного чтения, соответственно. Соответствующие сигналы выборки по шинам выборки 8 поступают на выбранный адресным словом обращения функциональный блок программируемого контроллера.

0 Память 3 таблицы данных (фиг. 4) работает следующим образом.

Сигналы со входом выборки памяти 3 таблицы данных поступают на входы выборки микросхемы 62 памяти - сигналы CSTD,

5 RD, WRO, микросхемы 64 памяти - сигналы CSTD, RD, WR1 шинного формирователя 64 - сигналы DT/R, CS, шинного формирователя 65 - сигналы DT/R, CS. Информация записывается (или считывается) е микросхемы 62, 63. Признаком записи или чтения информадии являются соответственно сигналы tfVRO (запись младшего байта) WR1 (запись старшего байта) или RD (чтение). Направление передачи информации определяет уровень (низкий или высокий) сигнала DT/R.

В режиме записи информация, которую необходимо записать в микросхемы 62, 63 поступает с информационных входов-выходов памяти 3 на входы шинного формирователя 64 - младший BDO ... BD7, на входы шинного формирователя 65 - старший BD8 ... BD15 байт. Адресные ВАО ... ВА7 и ВА8 ... ВА15 сигналы с соответствующих адресных входов памяти 3 поступают на входы шинных формирователей 60 и 61 соответственно, которые формируют адресные сигналы ВА1 ... ВА11 на адресные входы микросхем 62, 63. Информация с шинных формирователей 64 (младший байт BDO ... BD7) 65 (старший байт BD8 ... BD15) записывается соответственно, в микросхемы 62, 63 по адресу ВА1 ... ВА11. В режиме чтения с адресных входов памяти 3 на входы шинных формирователей 60, 61 поступают адресные сигналы ВАО ... ВА7, ВА8 ... ВА15 соответственно. Шинные формирователи 60, 61 формируют на адресные входы микросхемы 62, 63 адресные сигналы ВА1 ... ВА11.

Информация, считанная по адресу ВА1 .. ВА11 из микросхемы 62 (младший байт BDO ... BD7) или 63 (старший байт BD8 ,,, BD15) через двунаправленные шинные формирователи 64, 65 поступает на информационные входы/выходы памяти 3.

Считанная из микросхем 62, 63 информация поступает также на локальные информационные выходы LDO ... LD15 памяти 3.

Коммутатор 4 (фиг. 5) работает следующим образом.

Информационное слово LDO ... LD15, поступающее с локальных информационных входов коммутатора 4, распределяется по информационным входам шинных формирователей 66, 67, 68, 69 по 4 бита LDO ... LD3, LD8... LD11, LD4 ... LD7. LD12 ... LD15 соответственно. Адресный бит ВАО поступает с адресного входа коммутатора 4 на .инверсный адресный вход каждого шинного формирователя 66, 68 и прямой адресный вход каждого шинного формирователя 67, 69, разрешая при этом прохождение через шинные формирователи 66, 68 полубайтов LDO ... LD3, LD4 ... LD7 информации, соответственно, через шинные формирователи 67. 69 полубайтов LD8 ... LD11, LD12 ... LD15 информации соответственно. С выходов шинных формирователей 66, 68.и 67, 69 группируется младший LDO ... LD7 или старший LD8 ... LD15 соответственно, байт информации, поступающий на локальные информационные входы коммутатора 4.

Блок 5 селективной записи (фиг. 5)рабо тает следующим образом. 5Младший LDO ... LD7 или старший LD8

... LD15 байт информации с локальных информационных входов блока 5 поступает на информационные входы буферного регистра 70, то его разрешающий вход поступает

0 со входа выборки блока 5 сигнал WR признака селективной записи, разрешая тем самым, запись байта информации в регистр 70, Записанный байт информации с выхода регистра 70 распределяется по четырем вхо5 дам каждого накопителя 72, 73 следующим образом: на четырех входа накопителя 72 - младший полубайт LDO ... LD3 или LD8 ... LD11, на четыре входа накопителя 73 - старший полубайт LD4 ,,, LD7 или LD12 ... LD15.

0 Кроме того, на другие четыре входа каждого накопителя 72, 73 поступают три адресных сигнала ВА12 ... ВА14 с адресных входов блока 5 и бит информации BDO или BD8, причем, бит выбирается из информацион5 ных сигналов BDO и BD8, поступающих с информационных входов блока 5 сигналом ВАО с адресного входа блока 5 на вход коммутатора 71 Адресными сигналами ВА12 ... ВА14 определяется номер бита в байте ин0 формации, подлежащего логической обработке в накопителях 72, 73 - программируемой логической матрице. Программируемая логическая матрица осуществляет логическую обработку поступив5 ших на ее входы сигналов (упаковку бита информации BDO или BD8 в байт LDO ... LD7 или LD8 .;. LD15). Логически обработанный байт информации с выхода программируемой логической единицы распределяется:

0 четыре бита LDO ... LD3 или LD8 ... LD11 с выхода накопителя 72 - на четыре входа каждого шинного формирователя 74, 75, четыре бета LD4 ... LD7 или LD12 ... LD15 с выхода накопителя 73 - на другие четыре

5 входа каждого шинного формирователя 74, 75, Таким образом, на входы каждого шинного формирователя 74, 75 поступает логически обработанный байт (младший или старший) информации.

0 Сигнал CSSW со входа выборки блока 5, поступающий на разрешающие входы каждого шинного формирователя 74, 75, разрешает прохождение двух одинаковых логически обработанных байтов на локаль5 ные информационные выходы LDO ... LD15 блока 5 через информационные шины 10 (фиг. 1) на информационные входы/выходы памяти 3.

Блок 6 селективного чтения (фиг. 7) работает следующим образом.

На информационные входы демультип- лексора 76 поступают информационные сигналы (младший LDO ,., LD7 или старший LD8,,, LD15 байт) с информационных входов бярка 6, на адресные входы демультиплек- сора 76 с адресных входов блока б поступают адресные сигналы ВА12 ... ВА14. В зависимости от кода адресных сигналов ВА12 .,, ВА14 демультиплексор 76 выбирает из байта бит информации. С выходов (прямого и инверсного) демультиплексора 76 выбранный бит информации поступает на два информационных входов коммутатора 77. Кодом адресного сигнала ВА15, поступающего с адресного входа блока 6 на разрешающий вход коммутатора 77, последним коммутируется на выход прямой или инверсный выбранный бит информации. Сигналы RD, CSSR, поступающие со входом выборки блока 6 на входы коммутатора 77 (сигнал Ш5) и шинного формирователя 78 (сигналы RD, CSSR) разрешают прохождение выбранного бита информации через шинный формирователь на локальные информационные выходы LDO и LD8 блока 6 через информационные шины 10 (фиг. 1) на информационные входы микроконтроллера 1. Формула изобретения 1. Программируемый контроллер, содержащий память пользователя, память таблицы данных, блок ввода-вывода и микроконтроллер, первые адресный, управляющий выходы и выходы выборки которого через внутреннюю магистраль соединены с одноименными входами памяти пользователя и памяти таблицы данных, первые информационные вход и выход микроконтроллера соединены с одноименными входами и выходами памяти пользователя и памяти таблицы данных, вторые адресный и управляющий выходы, вторые информационные вход и выход и вход прерывания микроконтроллера через внешнюю магистраль соединены с одноименными входами и выходами блока ввода-вывода, отличаю- щ и и с я тем, что, с целью повышения быстродействия при поразрядной обработке информации, в него введены блоки селективной записи и селективного чтения и коммутатор, адресный вход которого подключен к первому адресному выходу микро- контроллера, информационные входы коммутатора подключены к информационным выходам памяти таблицы данных, выход коммутатора подключен к первому информационному входу блока селективной записи и информационному входу блока селективного чтения, второй информационный вход блока селективной записи и информационный выход блока селективного чтения подключены соответственно к первым информационным выходу и входу микроконтроллера, инрформационный выход блока селективной записи подключен к

информационным входам/выходам памяти таблицы данных, адресные входы и входы выборки блоков селективной записи и селективного чтения подключены соответственно к первому адресному выходу и

0 выходам выборки микроконтроллеоа, управляющие выходы записи и чтения которого соединены соответственно с входом записи блока селективной записи и входом чтения блока селективного чтения,

5 2. Контроллер по п. 1,отличающий- с я тем, что коммутатор содержит четыре шинных формирователя, причем, управляющие входы каждого шинного формирователя соединены между собой и подключены к

0 адресному входу коммутатора, информационные входы каждого шинного формирователя подключены к информационным входам коммутатора, информационные выходы каждого шинного формирователя под5 ключены к выходу коммутатора.

J3, Контроллер по п. 1, о т л и ч а ю щ и й- с я тем, что блок селективной записи содержит буферный регистр, коммутатор, первый и второй накопители, первый и второй шин

0 ные формирователи, причем, информационные и разрешающий входы буферного регистра соединены соответственно с первым информационным входом и входом записи блока селективной записи, два

5 информационных и один управляющий входы коммутатора соединены соответственно с вторым информационным и адресным входами блока, выход коммутатора соединен с каждым.первым информационными входа0 ми первого и второго накопителей, вторые информационные входы которых подключены к выходам буферного регистра, адресные входы первого и второго накопителей соединены между собой и подключены к

5 адресному входу блока селективной записи, выходы первого накопителя подключены к первым информационным входам первого и второго шинных формирователей, выходы второго накопителя подключены к вторым

0 информационным входам первого и второго шинных формирователей, управляющие входы которых подключены к входу выборки блока селективной записи.

4, Контроллер по п. 1,отличающий5 с я тем, что блок селективного чтения содержит мультиплексор, коммутатор и шинный формирователь, выход которого подключен к информационному выходу блока, управляющий вход шинного формирователя соединен с управляющим входом коммутатора и

подключен к входу чтения блока селективного чтения, разрешающий вход шинного формирователя соединен с входом выборки блока, информационный вход шинного формирователя подключен к выходу коммутатора, адресный вход которого подключен к адресному входу блока, а два информационных входа подключены к прямому и инверсному выходам мультиплексора, адресный и информационный входы которого являются одноименными входами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Устройство для адресации памяти | 1990 |

|

SU1741142A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Программируемый контроллер | 1989 |

|

SU1647594A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Запоминающее устройство | 1990 |

|

SU1805496A1 |

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

Изобретение относится к автоматике и вычислительной техники, властности к программному управлению технологическим оборудованием и может быть использовано в программируемых системах управления технологическими объектами, алгоритм управления которых описывается с помощью временных булевых функций. Цель изобретения - повышение быстродействия при поразрядной обработке информации. Устройство содержит микроконтроллер 1, память пользователя 2, память таблицы данных 3, коммутатор 4, блок селективной записи 5, блок селективного чтения 6, блок ввода-вывода 7. Шины 8, 9, 10, 11 образуют внутреннюю магистраль и осуществляют связь микроконтроллера с памятью пользователя, памятью таблицы данных, коммутатором, блоками селективной записи и селективного чтения. Шины 12, 13, 14 и 15 образуют внешнюю магистраль и осуществляют связь микроконтроллера с блоком ввода-вывода..3 з.п. ф-лы, 8 ил. Ј

I §М-..АЮ/

о

I

у

Ч

Hi

Ш.ШЩиг.1

ft

ВнешмЯЯ Ma&vcsyo&Au

N6

s

CVi

tUSvw у р«Јлену ff0df ec,e

W инь/ 3

.BMe...efltit

Фиг. 6 вдгг... вям

Фиг. 7

LDO...LD15 о

| Патент США Ms 4263647, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Заявка ФРГ № OS 3323824, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Заявка ФРГ № OS 3302940, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| опублик | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1993-08-15—Публикация

1991-01-11—Подача