Изобретение относится к области микропроцессорной техники и может применяться для реализации устройств обмена информацией.

Цель изобретения расширение функциональных возможностей микроЭВМ за счет диагностики устройства ввода-вывода и расширения объема используемой памяти.

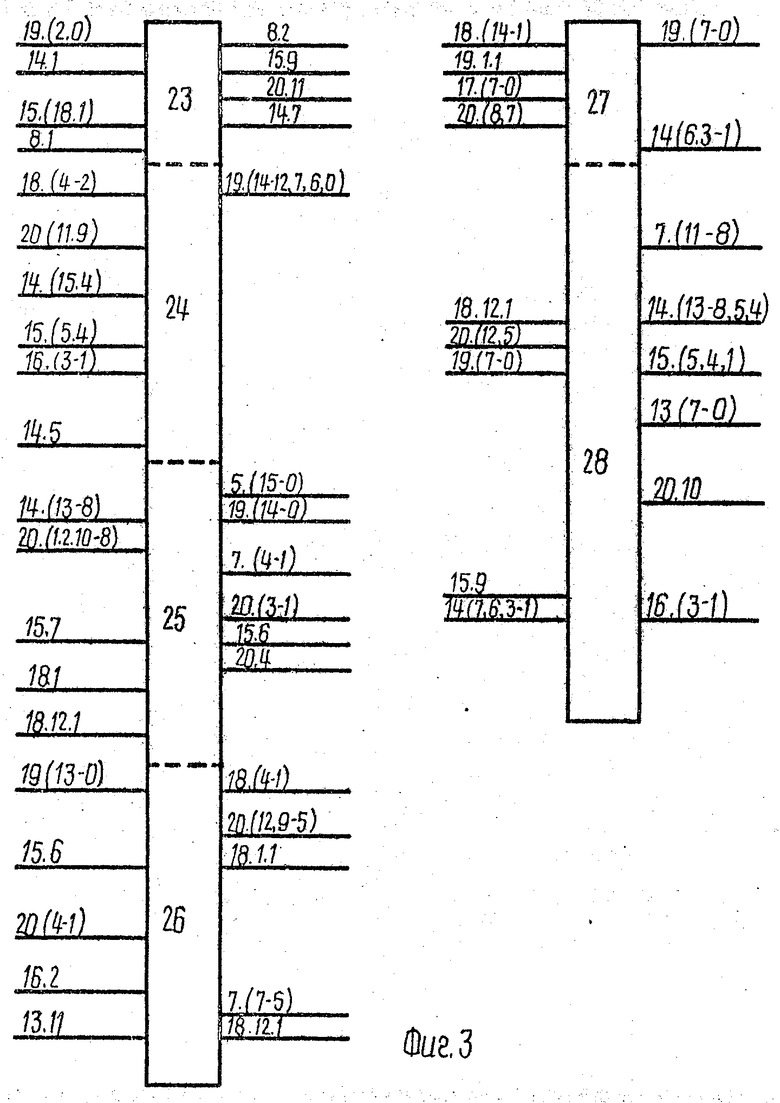

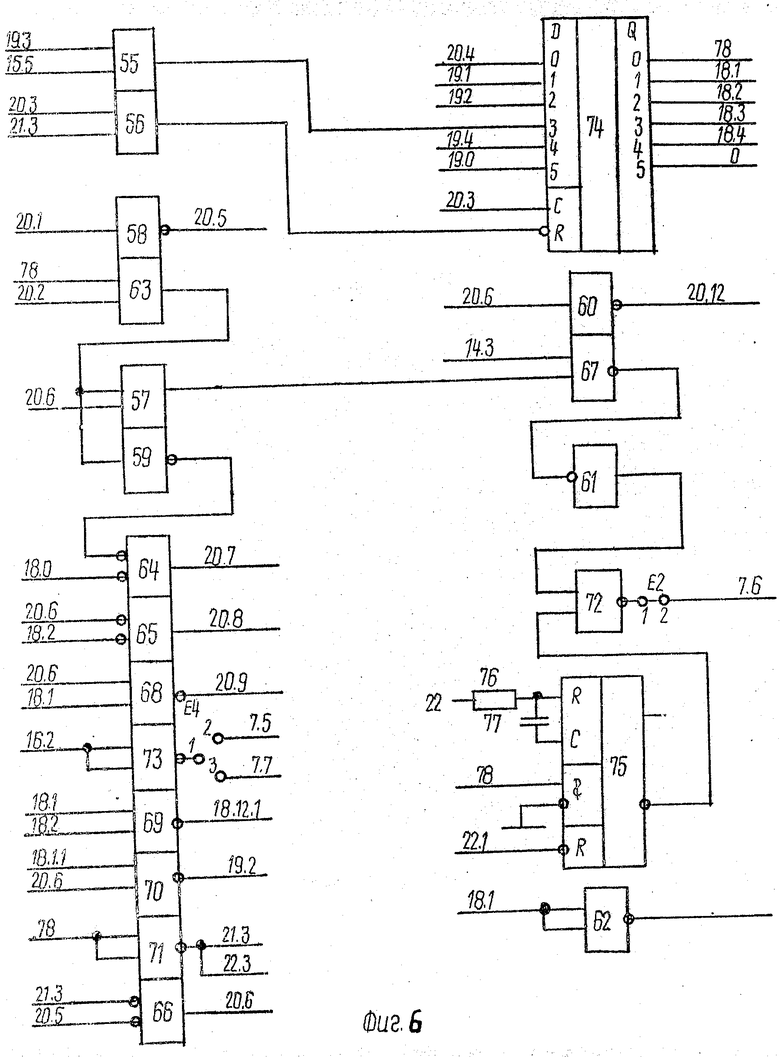

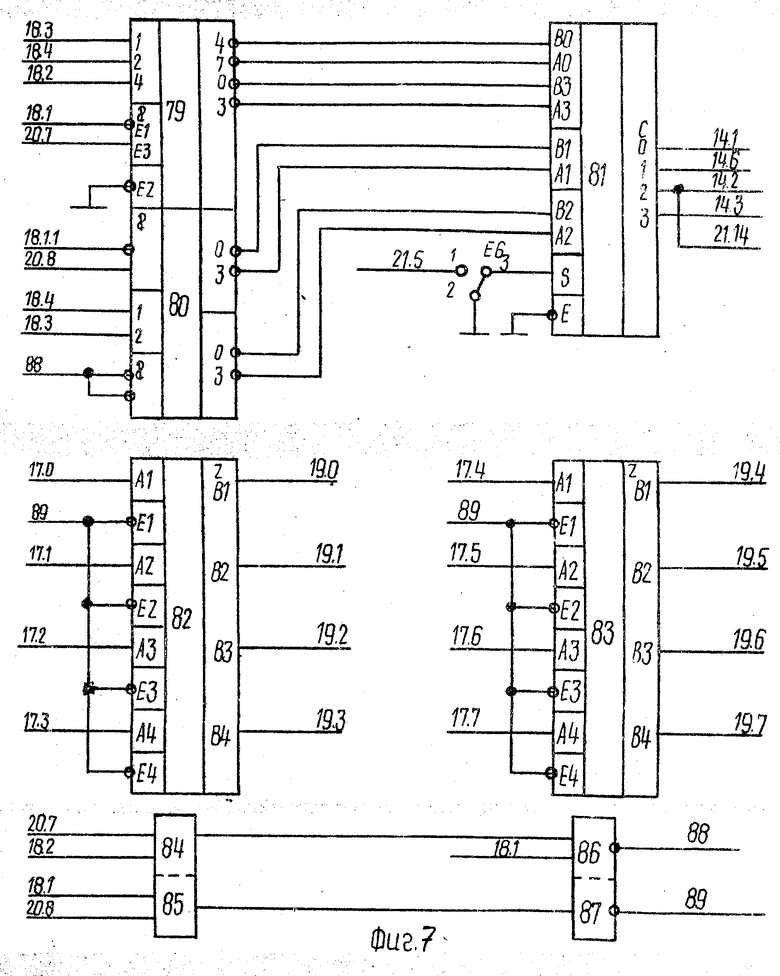

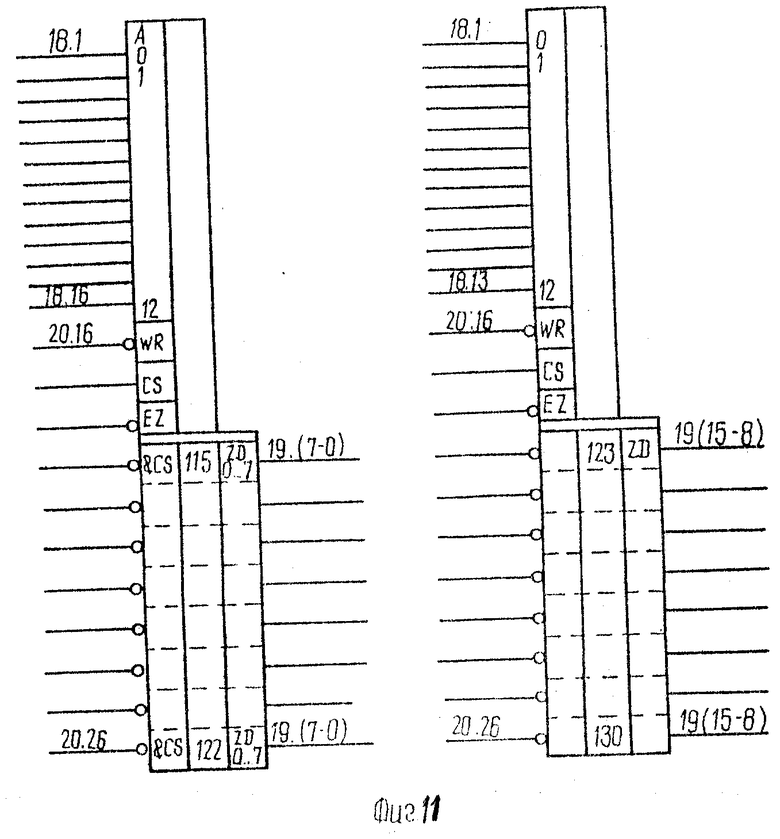

На фиг. 1 показана функциональная схема микроЭВМ; на фиг. 2 центрального процессора; на фиг. 3 устройства ввода-вывода; на фиг. 4 узел адаптера связи; на фиг. 5 узел селектора адреса; на фиг. 6 узел логики управления; на фиг. 7 узел управления приемом-передачей; на фиг. 8 узел приема-передачи; на фиг. 9 функциональная схема статического ОЗУ; принципиальные электрические схемы представлены на фиг. 10 узла магистральных приемопередатчиков; на фиг. 11 узла элементов памяти; на фиг. 12 узла адресации; на фиг. 13 узла управления памятью.

МикроЭВМ (фиг. 1) содержит магистраль 1, центральный процессор 2, устройство ввода-вывода 3, статическое ОЗУ 4, магистральные вводы-выводы 5-7, шины токовой петли 8, причем центральный процессор 2 (фиг. 2) содержит устройство сопряжения с магистралью 9, СОЗУ 10, устройство обработки данных 11, шины ввода-вывода 12, 13, при этом устройство ввода-вывода 3 (фиг. 3) содержит управляющие шины 14-16, адресно-информационные шины первого типа 17, адресные шины 18, адресно-информационные шины второго типа 19, шины управления 20, шина высокого логического уровня 21, шина питания плюс 5 в 22, узел адаптера связи 23, узел регистра состояния 24, узел селектора адреса 25, узел логики управления 26, узел управления приемом-передачей 27, узел приема-передачи 28, причем узел адаптера связи 23 (фиг. 3, 4) содержит генератор 29, триггеры 30, 31, мультиплексор 32, приемник 33, элемент "И" 34, передатчик 35, ограничительный элемент 36, узел регистра состояния 24 (фиг. 3, 5) содержит мультиплексоры 37-39, буферные элементы на три состояния 40-45. Узел селектора адреса 25 (фиг. 3, 5) содержит приемопередатчики 46-50, элементы И 51, 52, программируемую логическую матрицу 53, управляющую шину сигнала выбора устройства 54. Узел логики управления 26 (фиг. 3, 6) содержит элементы ИЛИ 55-57, инверторы 58-62, элемент И 63, элементы ИЛИ-НЕ 64-67, элементы И-НЕ 68-69, передатчики 70-73, триггер 74, одновибратор 75, ограничительный элемент 76, накопительный элемент 77, шину "устройство выбрано" 78. Узел управления приемопередачей 27 (фиг. 3, 7) содержит дешифраторы 79, 80, мультиплексор 81, буфер на три состояния 82, 83, элементы И 84, 85, элемент И-НЕ 86, инвертор 87, шину управления с инверсией 88, шину разрешения входного буфера 89. Узел приема-передачи 28 (фиг. 3, 8) содержит триггер 90, инвертор 91, элемент ИЛИ 92, программируемую логическую матрицу 93, асинхронный приемопередатчик данных 94, буферы на три состояния 95, 96, элемент прерывания 97, шины выбора первого и второго типа 98, 99. Статическое ОЗУ 4 содержит узел магистральных приемопередатчиков 100, узел элементов памяти 101, узел адресации 102 и узел управления памятью 103, узел магистральных приемопередатчиков 100 (фиг. 9, 10) содержит приемопередатчики 104-109, приемники 110-113, инвертор 114. Узел элементов памяти 101 (фиг. 9, 11) содержит элементы памяти 115-130. Узел адресации 102 (фиг. 9, 12) содержит регистры 131, 132, дешифраторы 133, 134, элементы набора резисторов 135-138, перемычки 139-142. Узел управления памятью 103 (фиг. 9, 13) содержит элементы И-НЕ 143-151, элементы ИЛИ 152, 153, элементы И 154-156, триггеры с защелкой 157, 158, перемычки 159-163, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 164-167, элемент набора резисторов 168, перемычка 169.

При этом магистральные адресно-информационные шины 5 содержат 5.(15-0), магистральные адресные шины 6 содержат 6.(21-16), магистральные управляющие шины 7 содержат шины: выборка устройства 7.1, запись данных 7.2, синхронизация обмена 7.3, чтение данных 7.4, авария источника питания 7.5, ответ устройства 7.6, останов 7.7, запрос прерывания 7.8, выходной сигнал предоставления прерывания 7.9, входной сигнал предоставления прерывания 7.10, установка 7.11, входной сигнал разрешения захвата магистрали 7.12, выходной сигнал разрешения захвата магистрали 7.13, признак записи байта 7.14, шины токовой петли 8 содержат шины: вход данных 8.1, выход данных 8.2, шины управления 14 содержит шины регистра состояния выходного буфера 14.1, разрешения выходного буфера 14.2, регистр состояния входного буфера 14.3, разрешения ввода 14.4, разрешение вывода 14.5, управление входным буфером 14.6, управляющие шины 14.(8-13) с первого по шестой векторами, шины управления 15 содержат шины установки 15.1, управления с инверсией 15.2, входного буфера 15.3, готов ввод 15.4, готов вывод 15.5, выбор пульта 15.6, разрешения пульта 15.7, выходные данные 15.8, входные данные 15.9, шина управления 16 содержит ошибку четности 16.1, ошибку стопового бита 16.2, ошибку переполнения 16.3, адресно-информационные шины первого типа 17 содержат 17.(7-0), адресные шины 18 содержат 18.(13-1) адресную шину первого типа с инверсией 18.1.1, адресную шину второго типа 18.12.1, адресную шину третьего типа 18.16.1, адресную шину четвертого типа 18.16.1, адресную шину пятого типа 18.17, адресно-информационные шины первого типа 19 содержат 19.(15-1), адресно-информационные шины второго типа 19.(14-12, 7, 6, 0), адресно-информационные шины третьего типа 19.0, шины управления 20 содержат чтение данных первого типа 20.1, запись данных 20.2, синхронизация обмена 20.3, синхронизация обмена с инверсией 20.3.1, выборка устройства 20.4, чтение данных второго типа 20.5, чтение данных третьего типа 20.6, запись младшего байта 20.7, чтение входного буфера 20.8, чтение регистра состояния 20.9, чтение четвертого типа 20.10, останов 20.11, чтение пятого типа 20. 12, ответ устройства 20.13, признак записи байта 20.14, запись младшего байта памяти 20.15, запись старшего байта памяти 20.16, выбор кристалла памяти 20.17, разрешение памяти 20.18, выбор элемента памяти 20.(26-19), выбор адреса 20. (30-27), выбор расширения адреса 20.(32, 31).

Работа микроЭВМ. Перед вводом-выводом информации программно осуществляется диагностика устройства ввода-вывода информации по данному алгоритму:

выход данных адаптера связи коммутируется на вход асинхронного приемопередатчика данных;

из центрального процессора на вход приемопередатчика данных устанавливается информация, которая на выходе преобразуется в асинхронную последовательность импульсов и поступает на вход асинхронного приемопередатчика данных;

считывается информация с выхода асинхронного приемопередатчика данных и проверяется на четность по отношению к информации, выставленной из ЦП.

Коммутация выхода данных с узла адаптера связи на вход асинхронного приемопередатчика данных осуществляется следующим образом.

В узел адаптера связи 23 по адресно-информационной шине 19.2 подается программно высокий логический уровень на информационный вход триггера 31.

Триггер стробируется сигналом по управляющей шине регистра состояния выходного буфера 14.1 и устанавливается в единичное состояние.

Высокий логический уровень с прямого выхода триггера 31 подается на вход селектора мультиплексора 32. Подаваемые на вход мультиплексора преобразованные асинхронные данные поступают на второй вход мультиплексора 32 и выходят с его нулевого выхода на информационный вход триггера 90 узла приема-передачи для задержки на один такт синхроимпульса с целью формирования предыдущей посылки в асинхронном приемопередатчике данных 94.

После задержки на один такт синхроимпульсы поступают на вход приемопередатчика 94. В приемопередатчике 94 последовательная серия импульсов преобразуется и поступает на выход в параллельном коде адресно-информационные сигналы 17. При заполнении входного буфера в приемопередатчике 94 на выходе буфера на три состояния 95 формируется сигнал готов ввод 15.4, который считывается центральным процессором 2 и центральный процессор 2 считывает с буферных устройств на три состояния 82, 83 адресно-информационные сигналы второго типа 19.(7-0).

Центральный процессор 2 сравнивает на четность информацию, которую выставил на вход асинхронного приемопередатчика 94, и информацию, которая считана с его выхода, и тем самым проверяет асинхронный приемопередатчик данных 94 на достоверность передаваемой информации.

На выходе 15.8 асинхронного приемопередатчика 94 формируется информация в последовательном коде, так что при четном числе импульсов добавляется импульс проверки на четность низким логическим уровнем, при нечетном числе импульсов добавляется импульс высоким логическим уровнем.

Эта информация поступает через триггер 90 на вход асинхронного приемопередатчика данных (АППД) 90, где контролируется на четность в случае искажения ошибки на выходе 16.1 АППД 90 вырабатывается сигнал "Ошибка четности", которая через буфер на три состояния 43 в узле регистра состояния 24 поступает по адресно-информационной шине второго типа 19.12 в центральный процессор 2 через магистраль 1.

После диагностики устройства ввода-вывода осуществляется передача информации в обычном порядке.

В аналоге авт. св. N 1604040 последний банк статического запоминающего устройства занимают адреса внешних устройств и этот банк памяти при обращении к ней не используется.

В данном статическом ОЗУ в узле управления памятью 103 включен второй триггер с защелкой 158, на первый информационный вход которого подается сигнал выборки устройства 20.4. При этом адреса внешних устройств смещаются в область несуществующей памяти и последний банк памяти используется для записи и считывания информации.

На второй информационный вход второго триггера с защелкой 152 подключен выход элемента ИЛИ 152, который совместно с элементами ИСКЛЮЧАЮЩЕЕ ИЛИ 164-167, элементами И-НЕ 143, 144 объединяет информацию адресных шин 18. (21-22).

На вход тактирования второго триггера с защелкой 158 подключена управляющая шина синхронизации обмена с инверсией 20.3.1, первый прямой выход триггера с защелкой 158 подключен к входу разрешения первого дешифратора 133, выходы которого служат для разрешения элементов памяти 115-130 и входу разрешения второго дешифратора 134, выходы которых объединяются на элементах И-НЕ 150, 151 и элементе И 155.

Выход сигнала с элемента И 155 поступает на вход элемента И 156, с выхода которого разрешает прохождение сигналов с выхода элементов И-НЕ 145, 146 для формирования сигналов на выходе элементов И-НЕ 147, 148 и резисторной сборки 168 соответственно запись младшего байта памяти и запись старшего байта памяти.

Одновременно сигнал с выхода элемента И 155 формирует на выходе резисторной сборки 168 сигнал "Выбор кристалла памяти" 20.17.

Кроме того, сигнал с выхода элемента И 155 проходит через элементы И 154 для формирования сигнала "Ответ устройства" 20.13 и, проходя через элемент И-НЕ 149 и резисторную сборку 168, формируется сигнал "Разрешение памяти" 20.18. Управляющие сигналы 20.(18-15) поступают в узел элементов памяти 101 для управления элементами памяти 115-130.

Сигнал с второго инверсного выхода второго триггера с защелкой 158 подается на второй вход разрешения второго дешифратора 134 для формирования сигналов выбор адреса 20.(30-27).

Центральный процессор 2 управляет диагностикой устройства ввода-вывода, записью и считыванием статического ОЗУ 4.

При этом центральный процессор 2 содержит устройство сопряжения с магистралью 9, СОЗУ 10 и устройство обработки данных 11.

Центральный процессор 2 соответствует микроЭВМ МСО 102, взятый за прототип микроЭВМ по заявке N 4431032/24.

Введение триггера и мультиплексора в узел адаптера связи позволяет осуществлять диагностику устройства ввода-вывода и повышать надежность приема-передачи информации.

Введение второго триггера с защелкой, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, И-НЕ, ИЛИ и управляющих сигналов триггера с защелкой позволяет использовать последний банк памяти, составляющий 4К слов, т.е. при полном объеме памяти 64К увеличен объем используемой памяти на 6%

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| МИКРО-ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 2000 |

|

RU2209462C2 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения двух микроЭВМ с общей памятью | 1988 |

|

SU1674141A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для сопряжения двух микро эвм с общей памятью | 1985 |

|

SU1280643A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С ПАМЯТЬЮ | 1991 |

|

RU2018941C1 |

Изобретение относится к области микропроцессорной вычислительной техники, в частности, может применяться для реализации устройств обмена информации. Цель изобретения расширение функциональных возможностей за счет диагностики устройства ввода-вывода и расширения объема использования статического оперативного запоминающего устройства. МикроЭВМ содержит центральный процессор, устройство ввода-вывода, статическое оперативное запоминающее устройство, при этом магистраль подключена адресно-информационными, адресными и управляющими входами-выходами к центральному процессору, устройству ввода-вывода и статическому ОЗУ. Сущность изобретения заключается в том, что в узел адаптера связи устройства ввода-вывода включен триггер и мультиплексор, с помощью которых выход устройства ввода-вывода коммутируется на вход и программно осуществляется его диагностика. Кроме этого, в узел управления памятью в статическом ОЗУ включены четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента И-НЕ, ИЛИ, триггер, которые позволяют использовать последний банк памяти. 13 ил.

МИКРОЭВМ, содержащая центральный процессор, устройство ввода-вывода, статическое оперативно-запоминающее устройство, при этом центральный процессор включает устройство сопряжения с магистралью, сверхоперативное запоминающее устройство, устройство обработки данных, причем устройство ввода-вывода содержит узел адаптера связи, узел регистра состояния, узел селектора адреса, узел логики управления, узел управления приема-передачи, узел приема передачи, при этом адаптер связи устройства ввода-вывода содержит генератор импульсов, триггер, приемник, передатчик, ограничительные элементы, узел регистра состояния содержит три мультиплексора, шесть элементов развязки, узел селектора адреса содержит пять приемо-передатчиков, программируемую логическую матрицу, узел логики управления содержит три элемента ИЛИ-НЕ, два элемента И-НЕ, четыре передатчика, триггер, одновибратор, ограничительный элемент, накопительный элемент, узел управления приема-передачи содержит два дешифратора, мультиплексор, два элемента развязки с тремя состояниями, два элемента И, элемент И-НЕ, узел приема-передачи содержит триггер, элемент НЕ, элемент ИЛИ, программируемую логическую матрицу, асинхронный приемопередатчик, два элемента развязки на три состояния элемент прерывания, причем узел адаптера связи подключен соответственно адресно-информационными входами второго и нулевого бита к одноименным выходам узла селектора адреса и узла управления приема-передачи адресно-информационным входом нулевого бита к одноименному выходу узла регистра состояния, входом установки к одноименному выходу узла приема-передачи, входом управления выходными данными к одноименному выходу узла приема-передачи, информационный вход приема данных и одноименный выход передачи данных узла адаптера связи образуют токовую петлю, вход управления выходом которого подключен к одноименному выходу узла управления приема-передачи, узел регистра состояния подключен адресными входами с второго по четвертый бит соответственно к выходам узла логики управления, вход чтения узла регистра состояния подключен к одноименному выходу узла адаптера связи, входы разрешения ввода, разрешения вывода подключены к одноименным выходам узла управления приема-передачи, входы "Готов ввод", "Готов вывод", подключены к одноименным выходам узла приема-передачи, входы "Ошибка четности", "Ошибка стопового элемента", "Ошибка переполнения" подключены к одноименным выходам узла приема-передачи, вход управления выходом подключен к одноименному выходу узла управления приема-передачи, с первого по шестой входы вектора подключены к одноименным выходам узла приема-передачи, входы "Чтение третьего типа", Запись младшего байта", "Чтение входного буфера", "Чтение регистра состояния" подключены к одноименным выходам узла логики управления, вход "Чтение четвертого типа" подключен к одноименному выходу узла приема-передачи, вход "Разрешение пульта" подключен к одноименному выходу узла приема-передачи, адресный вход первого бита подключен к одноименному выходу узла логики управления, адресно-информационные выходы второго типа подключены к одноименным входам-выходам узла селектора адреса, узел логики управления подключен соответственно адресно-информационными входами с нулевого по тринадцатый бит к одноименным входам-выходам узла селектора адреса, входом "Выбор пульта" к одноименному выходу узла селектора адреса, входами "Чтение данных первого типа", "Запись данных", "Синхронизация обмена", "Выборка устройства" к одноименным входам-выходам узла селектора адреса, входом "Ошибка стопового бита", входом шестого вектора к одноименным выходам узла приема-передачи, магистральные входы-выходы "Авария источника питания", "Ответ устройства", "Останов" подключены соответственно к одноименным входам-выходам магистрали, узел селектора адреса подключен входами с первого по шестой векторов соответственно к одноименным выходам узла приема-передачи, входами "Чтение данных пятого типа", "Запись младшего байта", "Чтение входного буфера", "Чтение регистра состояния" к одноименным выходам узла логики управления, входом "Чтение четвертого типа" к одноименному выходу узла приема-передачи, входом "Разрешение пульта" к одноименному выходу узла приема-передачи адресным входом первого бита и адресным входом первого и второго бита к одноименным выходам узла логики управления, узел управления приема-передачи подключен соответственно адресными входами с нулевого по четвертый бит к одноименным выходам узла логики управления, адресным входом первого бита с инверсией к одноименному выходу узла логики управления, адресно-информационными входами первого типа к одноименным выходам узла приема-передачи, входами "Запись младшего байта" и "Чтение входного буфера" к одноименным выходам узла логики управления, магистральные адресно-информационные входы-выходы, магистральные управляющие входы-выходы подключены к одноименным входам-выходам магистрали, узел приема-передачи подключен соответственно адресным входом первого и второго бита к одноименному выходу узла логики управления, входами "Чтение данных второго типа", и "Чтение данных пятого типа" к одноименным выходам узла логики управления, адресно-информационными входами с нулевого по седьмой бит подключены к одноименным выходам узла управления приема-передачи, входом управления входными данными к одноименному выходу адаптера связи, входы "Регистр состояния выходного буфера", "Разрешение выходного буфера", "Регистр состояния входного буфера" подключены к одноименным выходам узла управления передачей, вход синхронизации подключен к одноименному выходу узла адаптера связи, магистральные входы-выходы "Запрос прерывания", "Выходной сигнал предоставления прерывания", "Входной сигнал предоставления прерывания" и "Установка" подключены к одноименным входам-выходам магистрали, при этом в узле адаптера связи выход генератора импульсов подключен к выходу узла, вход приемника подключен к входу-выходу токовой петли, выход передатчика через ограничительный элемент подключен к входу-выходу токовой петли, к информационному входу первого триггера подключен адресно-информационный вход-выход нулевого бита, к тактирующему входу вход управления выходом, к сбросному входу вход установки, прямой выход первого триггера подключен к выходу "Останов" узла адаптера связи, инверсный выход подключен к первому входу элемента И, к второму входу которого подключен вход "Выходные данные", к первому входу передатчика подключена шина логической единицы микроЭВМ, при этом статическое ОЗУ включает узел магистральных приемопередатчиков, узел элементов памяти, узел адресации, узел управления памятью, причем узел магистральных приемопередатчиков подключен соответственно магистральными адресно-информационными, адресными и управляющими входами-выходами к магистрали, входами "Ответ устройства", "Разрешение памяти" к одноименным выходам узла управления памятью, адресно-информационными входами к одноименным выходам узла элементов памяти, узел элементов памяти подключен соответственно адресными входами к одноименным выходам узла адресации, входами "Запись младшего байта", "Запись старшего байта", "Выбор кристалла памяти", "Разрешение памяти", подключен к одноименным выходам узла управления памятью, входами "Выбор элементов памяти", "Выбор разрешения адреса" подключен к одноименным выходам узла адресации, узел адресации подключен соответственно адресно-информационными входами к одноименным выходам узла элементов памяти, входом "Синхронизация обмена" к одноименному выходу узла магистральных приемопередатчиков, адресным входом третьего типа к одноименному выходу узла магистральных приемопередатчиков, узел управления памятью подключен соответственно адресными входами четвертого типа к одноименным выходам узла магистральных приемопередатчиков, входами "Чтение данных первого типа", "Запись данных", "Синхронизация обмена", "Признак записи байта" к одноименным выходам узла магистральных приемопередатчиков, входами "Выбор адреса" к одноименным выходам узла магистральных приемопередатчиков и к одноименным выходам узла адресации, адресно-информационным входом третьего типа к одноименному выходу узла элементов памяти, при этом узел адресации содержит первый и второй регистры, элемент НЕ, первый и второй дешифраторы, причем адресно-информационные входы первого типа узла адресации подключены соответственно к информационным входам первого и второго регистров, к информационному входу второго регистра, кроме того, подключена адресная шина третьего типа, выходы первого регистра, с первого по пятый выходы второго регистра подключены через резисторную сборку к адресным выходам узла адресации, с шестого по восьмой выходы второго регистра через резисторные сборки подключены соответственно с первого по третий информационными входами первого дешифратора, седьмой и восьмой выходы второго регистра подключены соответственно к первому и второму информационным выходам второго дешифратора, третий информационный вход которого подключен к шине логического нуля микроЭВМ, первый и второй входы разрешения первого дешифратора подключены к шине логического нуля микроЭВМ, управляющий вход "Синхронизация обмена" узла адресации подключен через элемент НЕ к входам записи регистров, входы размещения третьего состояния которых подключены к шине логического нуля микроЭВМ, при этом узел управления памятью содержит семь элементов И-НЕ, элемент ИЛИ, триггер, резисторную сборку, причем в узле управления памятью подключены соответственно адресно-информационные входы третьего типа, адресные входы пятого типа к первому и второму информационным входам триггера, вход синхронизации обмена с инверсией подключен к входу защелка триггера, вход "Выбор адреса" подключен к входам первого и второго элементов И-НЕ, вход "Чтение данных первого типа" подключен к первым входам первого элемента ИЛИ и третьего элемента И-НЕ, вход "Запись данных" подключен к второму входу первого элемента ИЛИ и первому входу второго элемента И, вход "Синхронизация обмена" подключен к третьему входу первого элемента ИЛИ и второму входу элемента И-НЕ, вход признак записи байта подключен к первым входам четвертого и пятого элемента И-НЕ, выходы "Запись младшего байта памяти", "Запись старшего байта памяти", "Выбор кристалла памяти", "Разрешение памяти" подключены к одноименным выходам набора резисторов, при этом в узле управления памятью первые прямой и инверсный выходы триггера подключены соответственно к третьему входу третьего и второму входу четвертого элементов И-НЕ, вторые прямой и инверсный выходы триггера подключены к второму входу второго элемента И, к третьему и четвертому входам которого подключены соответственно выходы первого и второго элементов И-НЕ, выход второго элемента И подключен к первым входам шестого и седьмого элементов И-НЕ, выходы четвертого и пятого элементов И-НЕ подключены к вторым входам шестого и седьмого элементов И-НЕ, выходы которых подключены к первому и второму входам набора резисторов, вход стробирования триггера подключен к входу узла адресации "Синхронизация обмена с инверсией", выход второго элемента И подключен через резисторную сборку к выходу "Выбор кристалла памяти", к пятому входу второго элемента И, к третьему входу первого элемента И, к третьему входу которого подключен выход первого элемента ИЛИ, выход третьего элемента И-НЕ подключен через резисторную сборку к выходу разрешения памяти, отличающаяся тем, что с целью расширения области применения за счет диагностики устройства ввода-вывода и расширения объема используемой памяти, в узел адаптера связи включены второй триггер и мультиплексор, причем выход приемника подключен к первому информационному входу мультиплексора, выход элемента И подключен к второму и третьему информационным входам мультиплексора, к информационному входу второго триггера подключена адресно-информационная шина второго бита, к тактирующему входу которого подключен вход управления выходом, сбросовый вход второго триггера подключен к входу установки, прямой выход второго триггера подключен к управляющему входу мультиплексора, выход которого подключен к второму входу передатчика, при этом в узел управления памятью включены четыре элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента И-НЕ, элемент ИЛИ и триггер, причем на первые входы с первого по четвертый элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены соответственно адресные шины шестого типа, вторые входы которых соединены с шиной логического нуля микроЭВМ, выходы элементов с первого по четвертый ИСКЛЮЧАЮЩЕЕ ИЛИ подключены соответственно к первым и вторым входам восьмого и девятого элементов И-НЕ, выходы которых подключены соответственно к первому и второму входам третьего элемента ИЛИ, выход которого подключен к первому информационному входу второго триггера, второй информационный вход которого соединен с входом "Выборка устройства", вход стробирования второго триггера соединен с входом "Синхронизации обмена с инверсией", первый инверсный выход и второй прямой выход второго триггера подключены к выходам выборки расширения адреса узла адресации и к одноименным входам узла адресации.

| Авторское свидетельство СССР N 1626935, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-09-20—Публикация

1991-02-07—Подача