Изобретение относится к импульсной технике и может быть использовано при построении синтезаторов частоты.

Известно устройство - делитель частоты с дробным переменным коэффициентом деления (ДДПКД), взятое в качестве прототипа.

ДДПКД состоит из делителя частоты с переменным коэффициентом деления (ДПКД), сумматора, первого и второго накопителей кода, блока изменения кода на ±1, блока анализа, входной и выходной шин, шин управления целыми n1 и дробными n2 коэффициентами деления и шины тактовой частоты [1].

ДДПКД работает следующим образом. ДПКД реализует целые коэффициенты деления в соответствии с кодом, поступающим через сумматор по шине управления n1. Первый накопитель кода преобразует параллельный код, поступающий по шине n2, в последовательность импульсов, которые являются импульсами переноса, и через сумматор увеличивает в отдельных циклах деления ДПКД коэффициент деления на единицу или оставляет без изменения, если сигнал переноса отсутствует. Так реализуется дробное деление.

Введение дробных коэффициентов деления приводит к появлению в спектре выходного сигнала нежелательных дискретных составляющих кратных минимальной дискретности дробного коэффициента деления. Их амплитуда ослаблена в N (N - коэффициент деления делителя частоты) раз по отношению к уровню основного сигнала. Для уменьшения амплитуды нежелательных дискретных составляющих в спектре выходного сигнала применен второй накопитель кода и блок изменения кода на ±1. При коде, соответствующем числу ноль на шине n2, импульсов переноса с первого накопителя кода не будет, а на выходах суммы код с равной вероятностью в пределах емкости накопителя кода может соответствовать любому числу. Если код суммы не соответствует числу ноль, то второй накопитель кода будет формировать импульсы переноса, и блок изменения кода на ±1 через сумматор будет изменять код на ±1. В результате будет формироваться последовательность коэффициентов деления N-1, N, N+1, причем количество циклов деления с коэффициентами N-1 и N+1 равно между собой и циклы деления следуют друг за другом, а с коэффициентом деления N может быть любое количество циклов деления. В этом случае средний коэффициент деления делителя частоты будет равен N. При включении дробных коэффициентов деления по шине n2 код суммы первого накопителя кода будет меняться с каждым тактовым импульсом, а это значит, что частота сигнала переноса второго накопителя кода будет иметь переменный, "набегающий", характер. Импульсы переноса первого накопителя кода будут суммироваться с кодом, соответствующим любому коэффициенту деления. Тогда ДПКД будет делить на коэффициенты N-1, N, N+1, N+2. Происходит "маскировка" импульса переноса с первого накопителя кода. В результате в спектре выходного сигнала уровень дискретных составляющих, образующихся за счет дробного деления, будет уменьшен в N2 раз. Хотя и появляются другие дискретные составляющие в спектре выходного сигнала, их частота будет выше и амплитуда значительно меньше.

Так как накопитель кода по выходам суммы содержит регистр, то после включения источника питания при выключенных дробных коэффициентах деления код суммы первого накопителя кода может с равной вероятностью соответствовать любому коэффициенту деления, в том числе и единице младшего дробного разряда. Этот же код может оставаться и при выключении дробных разрядов в коэффициенте деления. В этом случае при реализации целых коэффициентов деления в спектре выходного сигнала будет нежелательная дискретная составляющая, стабильная по частоте, и уровнем, равным уровню, как если бы работал первый накопитель кода.

Для управления работой второго накопителя кода введен блок анализа, вход которого подключен к выходу переноса первого накопителя кода, а выход соединен с запрещающим входом второго накопителя кода.

В описании прототипа приведены три варианта выполнения блока анализа: первый - RС-цепь, постоянная времени которой на 20-30% больше периода частоты следования импульсов переноса при единице младшего дробного разряда; второй - счетчик, емкость которого должна быть хотя бы на единицу больше емкости первого накопителя кода; третий - n-входовая схема совпадения, входы которой подключены к шине управления n2, a выход к запрещающему входу второго накопителя кода.

Выше отмечалось, что ДДПКД может быть использован при построении синтезаторов частоты, которые являются одним из основных узлов радиоприемных или передающих устройств (РПУ).

В процессе эксплуатации РПУ, в которых было внедрено устройство, описанное в прототипе, были обнаружены недостатки. В устройствах, в которых в блоке анализа применены RC-цепь или счетчик частоты, при переключении с частоты настройки РПУ, в формировании которой коэффициент деления ДДПКД имеет дробную часть, на частоту которой коэффициент деления ДДПКД не имеет дробной части, происходит кратковременное увеличение нежелательных дискретных составляющих до 40 дБ.

Это объясняется тем, что при выключении дробных коэффициентов деления формирование импульсов переноса первым накопителем кода прекращается, а так как RC-цепь имеет постоянную времени на 20-30% больше периода следования импульсов переноса при единице младшего дробного разряда или емкость счетчика на единицу больше емкости первого накопителя кода, то второй накопитель кода будет продолжать работать до тех пор, пока RC-цепь не разрядится или емкость счетчика не заполнится и не поступит сигнал запрета на второй накопитель кода. Замечено, что максимальное увеличение дискретных составляющих происходит тогда, когда при выключении дробных разрядов остаточный код суммы первого накопителя соответствует единице младшего дробного разряда.

В устройствах, в которых блок анализа реализован на схеме совпадения, после переключения с частоты настройки, в формировании которой коэффициент деления имеет только целочисленное значение, на частоту, в формировании которой коэффициент деления включает и дробную часть, второй накопитель кода будет включен сразу, а сигналы переноса с первого накопителя кода могут поступать с отставанием. Отставание будет тем больше, чем меньше значение дробной части, и максимальное будет при единице младшего дробного разряда. В результате на время отставания импульсов переноса в спектре выходного сигнала делителя частоты появляются нежелательные дискретные составляющие.

Появление дискретных составляющих в спектре выходного сигнала делителя частоты, который применен в синтезаторе, приводит к ухудшению реальной избирательности РПУ, а это значит, что часть принимаемой информации может быть искажена или не принята.

На практике при тактовой частоте накопителей 100 кГц, четырех дробных разрядах и времени перестройки синтезатора с одной частоты на другую, равному 10 мс, вышеописанные недостатки блока анализа приводят следующие увеличения нежелательных дискретных составляющих в спектре выходного сигнала синтезатора:

70 мс, если блок анализа реализован на RC-цепи;

35-40 мс, если блок анализа реализован на счетчике частоты;

20-25 мс, если в блоке анализа применена схема совпадения.

Увеличения нежелательных дискретных составляющих в спектре выходного сигнала не будет, если блок анализа будет включать второй накопитель кода с появлением первого импульса переноса и выключать, как только на шине управления дробными коэффициентами деления появится код, соответствующий нулю в дробной части коэффициента деления.

Задача изобретения - повышение чистоты спектра выходного сигнала делителя частоты с дробным переменным коэффициентом деления.

Решение задачи достигается тем, что в делитель частоты с дробным переменным коэффициентом деления, который состоит из делителя частоты с переменным коэффициентом деления, сумматора, двух накопителей кода, блока изменения кода, блока анализа, шин управления целыми n1 и дробными n2 коэффициентами деления, входной и выходной шин, шины тактовых сигналов, введены: в блоке анализа второй вход, а в управлении для выключения блока анализа шина n3, которая подключена к его второму входу.

В качестве блока анализа предлагается применить RS-триггер.

Один из входов, например вход R, соединен с выходом переноса первого накопителя кода, а второй, например вход S, подключен к шине n3.

При появлении первого импульса переноса на первый вход блока анализа на выходе его сформируется сигнал, инверсный тому, который имелся до включения дробных разрядов. Выходной сигнал блока анализа снимет запрет на работу второму накопителю кода. При выключении дробных разрядов сигнал, одновременно поступающий от внешнего устройства по шине n3, выключит блок анализа, то есть его выходной сигнал сменится на инверсный, и второй накопитель кода прекратит свою работу. В результате в спектре выходного сигнала ДДПКД после включения или выключения дробных разрядов в коэффициенте деления не будут появляться кратковременные увеличения нежелательных дискретных составляющих.

Сопоставительный анализ показывает, что предложенное техническое решение отличается от прототипа тем, что введенные второй вход в блок анализа, а в управлении шина для выключения его, позволяют второй накопитель кода включать с появлением первого импульса переноса с первого накопителя кода и выключать при выключении дробных разрядов, что позволяет исключить возникновение нежелательных дискретных составляющих в спектре выходного сигнала ДДПКД.

Поэтому данное техническое решение отвечает критерию "новизна".

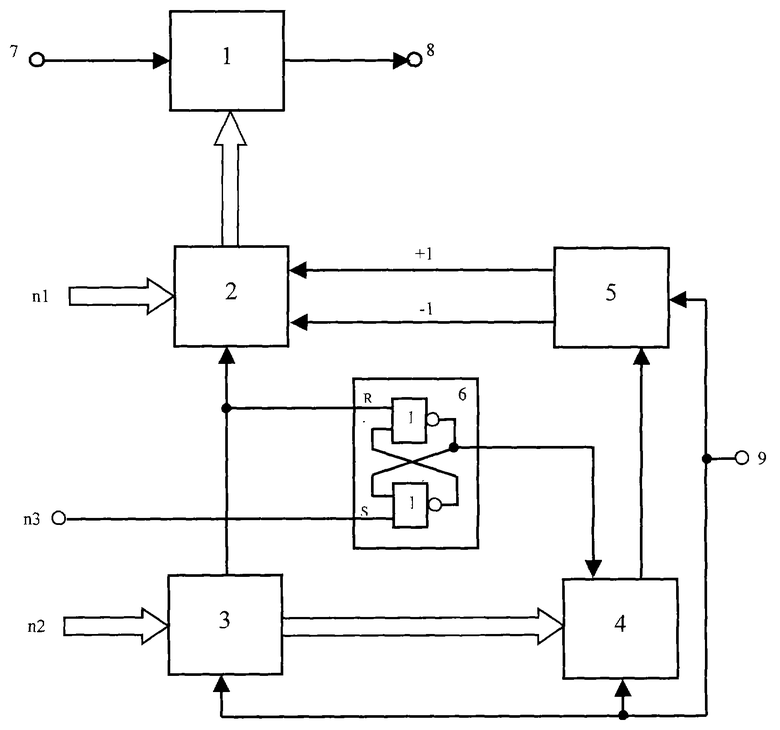

На чертеже представлена структурная схема ДДПКД, содержащая ДПКД 1, сумматор 2, имеющий информационные входы, первый вход переноса, второй и третий входы изменения кода на ±1 и выходы суммы, первый 3 и второй 4 накопители кода, блок 5 изменения кода, блок 6 анализа, состоящий, например, из RS-триггера, шины входную 7 и выходную 8, шину 9 тактовой частоты, первую n1, вторую n2 и третью n3 кодовые шины.

Вход ДПКД 1 подключен к входной шине 7, выход к выходной шине 8, а группа информационных входов соединена поразрядно с выходами суммы сумматора 2, группа информационных входов которого поразрядно подключена к первой кодовой шине, n1-шине, управления целыми коэффициентами деления. Вход переноса сумматора 2 подключен к первому входу, например входу R блока анализа 6 и выходу переноса накопителя 3 кода, группа информационных входов которого поразрядно подключена к второй кодовой шине, n2-шине, управления дробными коэффициентами деления, а группа выходов суммы поразрядно соединена с группой информационных входов второго накопителя 4 кода. Выход переноса второго накопителя 4 кода соединен с первым входом блока 5 изменения кода, два выхода которого подключены к двум входам сумматора 2, кроме этого, к шине 9 тактовой частоты подключены тактовые входы накопителей кода 3 и 4 и второй вход блока 5 изменения кода. Второй вход, например вход S, блока 6 анализа подключен к шине, n3-шине, выключения, а выход соединен с запрещающим входом второго накопителя 4 кода.

Рассмотрим работу схемы при условии, что блок 6 анализа реализован на RS-триггере. На входную шину 7 подадим сигнал частотой F, а на шину 9 тактовой частоты подадим сигнал частотой F/N (при описании работы устройства в качестве тактовой частоты можно использовать выходной сигнал ДПКД 1). На шину n1 подадим код, соответствующий коэффициенту деления N, на шину n2 - нулевой код. На шину n3 подадим короткий импульс, достаточный по длительности, чтобы RS-триггер в блоке 6 анализа установился в исходное состояние, при котором на входе накопителя 4 кода будет запрещающий сигнал. В этом случае на выходах переноса накопителей 3 и 4 кода импульсов не будет, и делитель начнет делить входную частоту на целочисленный коэффициент.

При включении дробных разрядов первый импульс переноса с первого накопителя 3 кода сменит состояние RS-триггера блока 6 анализа на противоположное и снимет сигнал запрета со второго накопителя 4 кода, и делитель будет работать, как написано выше.

Все последующие импульсы переноса будут подтверждать это состояние триггера. При отключении дробных разрядов необходимо одновременно от внешнего устройства по шине n3 подать короткий импульс для установки RS-триггера в блоке 6 анализа в исходное состояние. Задержками распространения сигнала в RS-триггере можно пренебречь. Второй накопитель 4 кода прекратит работу одновременно с отключением дробных разрядов.

При первоначальном включении питания необходимо подать короткий импульс по шине n3 для установки RS-триггера в исходное состояние.

Источник информации

1. Патент РФ 2041563, МКИ6 Н 03 К 23/66. Делитель частоты с дробным переменным коэффициентом деления, 09.08.95. Бюл. 22.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Цифровой синтезатор изменяющейся частоты | 1982 |

|

SU1107262A1 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1483632A1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525861A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

| Цифровой синтезатор изменяющейся частоты | 1988 |

|

SU1525860A2 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2440668C1 |

Изобретение относится к импульсной технике и может быть использовано при построении синтезаторов частоты. Техническим результатом является повышение чистоты спектра выходного сигнала. Устройство содержит делитель частоты с переменным коэффициентом деления, сумматор, два накопителя кода, блок изменения кода на ±1, блок анализа, выполненный на RS-триггере. 1 ил.

Делитель частоты с дробным переменным коэффициентом деления, содержащий делитель частоты с переменным коэффициентом деления (ДПКД), сумматор, имеющий информационные входы, первый вход переноса, второй и третий входы изменения кода на ±1 и выходы суммы, первый и второй накопители кода, блок изменения кода, блок анализа, первую для управления целыми и вторую для управления дробными коэффициентами деления кодовые шины, шину тактовой частоты, входную и выходную шины, к которым подключены соответственно вход и выход ДПКД, группа информационных входов которого поразрядно соединена с группой выходов суммы сумматора, группа информационных входов которого поразрядно подключена к первой кодовой шине, первый вход его соединен с выходом переноса первого накопителя кода, группа информационных входов которого поразрядно подключена ко второй кодовой шине, а группа выходов суммы поразрядно соединена с группой информационных входов второго накопителя кода, выход переноса которого соединен с первым входом блока изменения кода, первый и второй выходы которого подключены ко второму и третьему входам сумматора соответственно, кроме этого, к шине тактовой частоты подключены тактовые входы блока изменения кода, первого и второго накопителей кода, отличающийся тем, что блок анализа реализован на RS-триггере, первый вход, например R, которого соединен с выходом переноса первого накопителя кода, второй вход, например S, подключен к вновь введенной шине установки в исходное состояние RS-триггера, выход которого соединен с запрещающим входом второго накопителя кода.

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ИЗМЕНЯЕМЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1996 |

|

RU2134485C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2037958C1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1985 |

|

SU1372615A1 |

| Управляемый делитель частоты с дробным переменным коэффициентом деления | 1988 |

|

SU1718379A1 |

| SU 1769360 A1, 15.10.1992 | |||

| УНИВЕРСАЛЬНЫЙ ШАРНИР | 0 |

|

SU280126A1 |

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

Авторы

Даты

2004-01-20—Публикация

2002-01-08—Подача