Изобретение относится к вычислительной технике и может использоваться в узлах коммутации сообщений (пакетов) сети передачи данных (сети ПД) автоматизированной системы управления (АСУ) при управлении передачей данных по широковещательному многоточечному радиоканалу, имеющему динамическую неполносвязнную структуру.

Известно устройство для управления передачей данных по радиоканалу (А.С. СССР N 1162058, кл. H 04 L 7/00, 1985), содержащее последовательно соединенные синхронизатор и первый элемент И, а также элемент задержки, элемент ИЛИ и последовательно соединенные счетчик и триггер цикла передачи, последовательно соединенные генератор случайных чисел, блок сравнения и триггер разрешения передачи, а также последовательно соединенные второй элемент И и формирователь импульсов, что позволяет увеличить степень использования пропускной способности канала. Однако данное устройство обладает недостаточной скоростью передачи по радиоканалу.

Наиболее близким по технической сущности и выполняемым функциям к заявленному является устройство для управления передачей данных по радиоканалу (А.С. СССР N 1319298, кл. H 04 L 7/00, 1990), содержащее генератор случайных чисел и синхронизатор, первый, второй, третий и четвертый элементы И, счетчик, блок сравнения, триггер цикла передачи, триггер разрешения передачи, два формирователя импульсов, элемент ИЛИ, два элемента задержки, причем выход синхронизатора связан с первым входом первого элемента И и вторым входом второго элемента И, вход запроса передачи является третьим входом второго элемента И и связан с первым входом триггера разрешения передачи, выход которого связан со вторым входом элемента ИЛИ, входом элемента задержки и является выходом разрешения передачи, выход элемента задержки подключен к четвертому входу первого элемента И, третий вход которого связан с выходом триггера цикла передачи и первым входом второго элемента И, выход второго элемента И связан со входом формирователя импульсов и входом генератора случайных чисел, выход которого соединен с первым входом блока сравнения, второй вход которого подключен к первому выходу счетчика, выход формирователя импульсов связан с первым входом элемента ИЛИ, второй выход счетчика соединен со вторым входом триггера цикла передач, а вход счетчика подключен к выходу первого элемента И, выход блока сравнения подключен ко входу дополнительного формирователя импульсов, выход которого соединен со входом дополнительного элемента задержки и третьим входом элемента ИЛИ, а выход элемента ИЛИ является выходом "Включение передатчика", выход дополнительного элемента задержки связан с первыми входами третьего и четвертого элементов И, второй вход третьего элемента И соединен с выходом четвертого элемента И и является выходом сигнала "Столкновение", причем выход третьего элемента И связан со вторым входом триггера разрешения передачи, а второй вход четвертого элемента И подключен ко второму входу первого элемента И и первому входу триггера цикла передачи и является входом "Сигнал несущей".

При такой совокупности описанных элементов и связей достигается увеличение пропускной способности по радиоканалу.

Однако устройство-прототип имеет недостаток не обеспечивает функционирования устройства в канале множественного доступа, имеющем динамическую неполносвязную структуру.

Целью изобретения является разработка устройства управления передачей данных по радиоканалу для обеспечения возможности его работы в неполносвязном канале множественного доступа, имеющем быстроменяющуюся динамическую структуру.

Поставленная цель достигается тем, что в известное устройство управления передачей данных по радиоканалу, содержащее триггер цикла передачи и триггер разрешения передачи, первый, второй, третий и четвертый элементы И, элемент ИЛИ, синхронизатор, блок сравнения, формирователь импульсов, элемент задержки, причем синхронизатор связан с первым входом первого элемента И, а его выход подключен к первому входу второго элемента И, вход "Запрос передачи" подключен к третьему входу второго элемента И и первому входу триггера разрешения передачи, второй вход которого связан с выходом третьего элемента И, а выход триггера разрешения передачи соединен со вторым входом элемента ИЛИ, выход которого является выходом "Включение передатчика", выход элемента задержки связан с первыми входами третьего и четвертого элементов И, а выход четвертого элемента И подключен ко второму входу третьего элемента И и является выходом "Столкновение", дополнительно введены блоки определения интенсивности входного потока, выделения адреса, коммутации, опознавания адреса, два элемента ИЛИ, генератор интервала анализа, дешифратор. Причем вход "Сигнал несущей" подключен одновременно к первому и второму входу триггера цикла передачи, а выход триггера цикла передачи связан со вторым входом первого элемента И, входом формирователя импульсов и вторым входом блока выделения адреса. Выход формирователя импульсов связан с первым входом блока определения интенсивности входного потока, а второй вход блока определения интенсивности входного потока подключен к выходу генератора интервалов анализа и первым входам блоков опознавания адреса. Выходы блока определения интенсивности входного потока связаны со входами блока сравнения. При этом первый и второй выходы блока сравнения подключены к первому и второму входам первого введенного элемента ИЛИ, а третий выход блока сравнения соединен с первым входом блока коммутации. Выход первого введенного элемента ИЛИ связан со вторым входом блока коммутации, а третий вход блока коммутации подключен к выходу введенного элемента ИЛИ. Четвертый вход блока коммутации соединен со входом "Запрос передачи", третьим входом второго элемента И и первым входом триггера разрешения передачи. Первый выход блока коммутации является выходом "Разрешение передачи на частоте доступа к ретранслятору", а второй выход подключен ко второму входу второго элемента И. Выход второго элемента И связан с первым входом элемента ИЛИ с входом элемента задержки, а выход триггера разрешения передачи соединен со вторым входом элемента ИЛИ, и является выходом "Разрешение передачи на частоте основного канала". Выход канала множественного доступа подключен к первому входу блока выделения адреса и второму входу четвертого элемента И, а выходы блока выделения адреса связаны с группой входов блоков опознавания адреса. Входы дешифратора являются группой входов "Код адреса устройства", а соответствующие 1-N выходов дешифратора подключены к третьим входам 1-N блоков опознавания адреса, при этом выходы 1-N блоков опознавания адреса связаны с соответствующими 1-N входами второго введенного элемента ИЛИ.

При такой совокупности существенных признаков достигается то, что на основании анализа интенсивности входного потока сообщений, адресов абонентов-отправителей, выделенных из заголовков сообщений в предыдущем и текущем интервалах анализа, принимается решение о доступности (или недоступности) адресата. А на основании этого решения абонент осуществляют передачу сообщения либо в основной полосе частот канала, либо осуществит обмен данными на частоте доступа к ретранслятору соответственно, тем самым повышая интенсивность использования пропускной способности канала множественного доступа, и обеспечивая эффективную работу в канале, имеющем динамическую неполносвязную структуру.

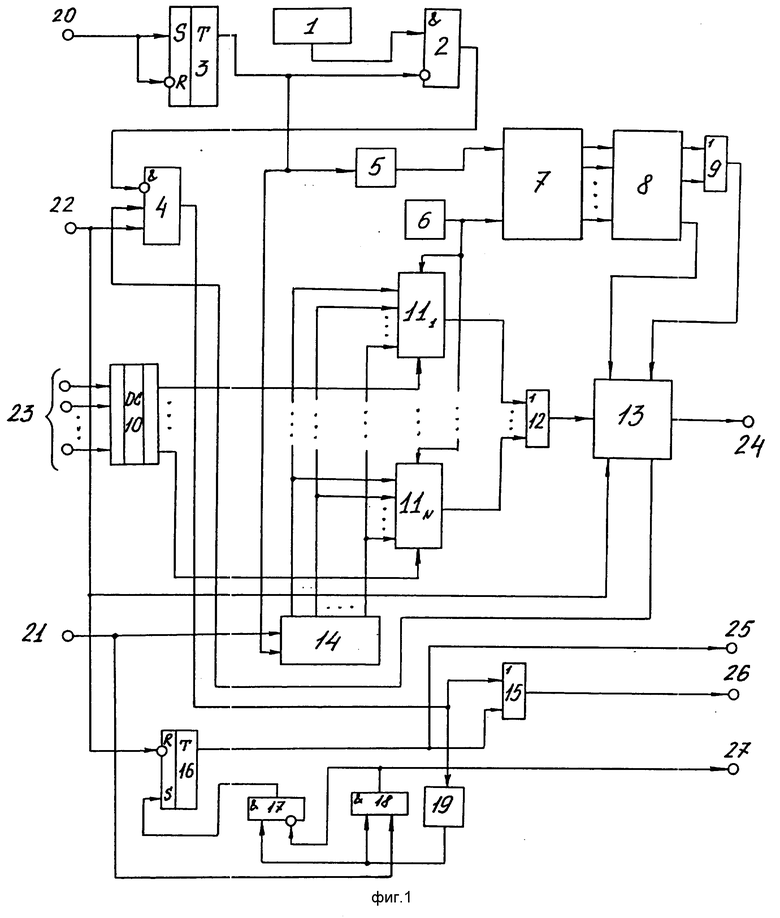

На фиг. 1 показана функциональная схема устройства управления передачей данных по радиоканалу; на фиг. 2 схема блока определения интенсивного входного потока; на фиг. 3 схема блока опознавания адреса; на фиг. 4 - функциональная схема блока выделения адреса; на фиг. 5 схема блока коммутации.

Заявленное устройство управления передачей данных по радиоканалу, показанное на фиг. 1, состоит из: синхронизатора 1, первого элемента И 2, триггера цикла передачи 3, второго элемента И 4, формирователя импульсов 5, генератора интервалов анализа 6, блока определения интенсивности входного потока 7, блока сравнения 8, первого элемента ИЛИ 9, дешифратора 10, N блоков опознавания адреса 111-11N, второго элемента ИЛИ 12, блока коммутации 13, блока выделения адреса 14, третьего элемента ИЛИ 15, триггера разрешения передачи 16, третьего элемента И 17, четвертого элемента И 18, элемента задержки 19. Причем, вход "Сигнал несущей" 20 является первым и вторым входом триггера цикла передачи 3. Выход триггера цикла передачи 3 связан со вторым входом первого элемента И 2, формирователем импульсов 5 и вторым входом 142 блока выделения адреса 14. При этом первый вход первого элемента И 2 соединен с выходом синхронизатора 1, а выход первого элемента И 2 подключен к первому входу второго элемента И 4. Второй вход второго элемента И 4 связан со вторым 136 выходом блока коммутации 13, а его третий вход соединен с первым входом триггера разрешения передачи 16, четвертым входом 134 блока коммутации 13 и является входом "Запрос передачи" 22. Выход второго элемента И 4 связан с первым входом третьего элемента ИЛИ 15 и входом элемента задержки 19. Выход элемента задержки 19 соединен с первым входом третьего 17 и первым входом четвертого 18 элементов И, причем выход четвертого элемента И 18 подключен ко второму входу третьего элемента И 17, и является выходом "Столкновение". Выход третьего элемента И 17 связан со вторым входом триггера разрешения передачи 16. Выход триггера разрешения передачи 16 подключен ко второму входу третьего элемента ИЛИ 15 и является выходом "Разрешение передачи в полосе основного канала" 25. Выход третьего элемента ИЛИ 15 является выходом "Включение передатчика" 26. Первый вход 141 блока выделения адреса 14 соединен со вторым входом четвертого элемента И 18 и является выходом канала множественного доступа 21. Выход формирователя импульсов 5 связан с первым 71 входом блока определения интенсивности входного потока 7, а второй вход 72 блока определения интенсивности входного потока 7 подключен к E1-EN первым входам блоков опознавания адреса 111-11N и выходу генератора интервалов анализа 6. Выходы С1-СN блока определения интенсивности входного потока 7 подключены к соответствующим входам блока сравнения 8. Причем первый 81 и второй 82 выходы блока сравнения 8 связаны с первым и вторым входом первого элемента ИЛИ 9, а выход первого элемента ИЛИ 9 соединен со вторым 132 входом блока коммутации 13. Третий выход 83 блока сравнения 8 подключен к первому входу 131 блока коммутации 13. Третий 133 вход блока коммутации 13 соединен с выходом второго элемента ИЛИ 12, а первый выход 135 блока коммутации 13 является выходом "Разрешение передачи на частоте доступа к ретранслятору" 24. Группа входов S1-SN "Код адреса" 23 является входами дешифратора 10, причем выходы L1-LN дешифратора 10 подключены к соответствующим R1-RN третьим входам N блоков опознавания адреса 111-11N. Группа F1-FN вторых входов N блоков опознавания адреса 111-11N соединена с K1-KN группой выходов блока выделения адреса 14, а выходы D1-DN блоков опознавания адреса 111-11N соединены с соответствующими входами второго элемента ИЛИ 12.

Заявляемое устройство реализуется следующим образом. Синхронизатор 1 представляет собой генератор тактовых импульсов и может быть реализован на интегральных микросхемах (ИМС) серий 511, 176 и описан Микросхемы и их применение: Справ.пособие. /В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалев и др. - М. Радио и связь, 1984, с.213, рис.7.6.

Триггер цикла передачи 3 и триггер разрешения передачи 16 могут быть реализованы на ИМС серий 133 и 564, описаны Микросхемы и их применение: Справ. пособие. /В. А.Батушев, В.Н.Вениаминов, В.Г.Ковалев и др. М. Радио и связь, 1984, с.118, рис.4.12.

Логические элементы И 2, 4, 17, 18 и логические элементы ИЛИ 9, 12, 15 могут быть реализованы на ИМС 133 и 564 и описаны Основы цифровой техники. /Л.А.Мальцева, Э.М.Фромберг. М. Радио и связь, 1986, с.20-24, рис.9, 11.

Формирователь импульсов 5 может быть реализован на ИМС серий 155, 176 и описан Основы цифровой техники. /Л.А.Мальцева, Э.М.Фромберг, В.С.Ямпольский. М. Радио и связь, 1986, с.30-31, рис.22.

Генератор интервалов анализа 6 представляет собой генератор импульсов с достаточно широким диапазоном изменения частоты генерируемых импульсов. Генератор интервалов анализа 6 может быть реализован на ИМС серий 155, 176 и описан Основы цифровой техники. /Л.А.Мальцева. М. Радио и связь, 1986, с. 28-29, рис.18, 19.

Блок сравнения 8 может быть реализован на ИМС серий 133, 564 и описан - Импульсные цифровые устройства. /И.О.Лебедев, А.М. Сидоров. Л. BAC, 1980, с. 51-53, рис.2.33, 2.34.

Дешифратор 10 может быть реализован на ИМС серий 176, 155 и описан - Микросхемы и их применение. Справочное пособие. /В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалев и др. М. Радио и связь, 1984, с.130, рис.4.29.

Линия задержки 19 может быть реализована в виде формирователя импульсов на ИМС серий 155 и 176 схема которого приведена и описана Основы цифровой техники. /Л.А.Мальцева. М. Радио и связь, 1986, с.30-31, рис.22.

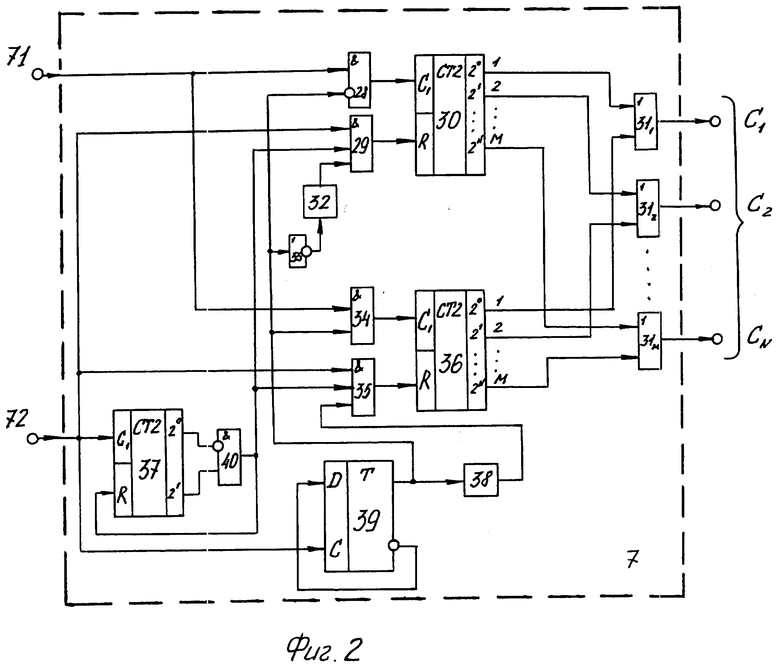

Одним из вариантов реализации блока определения интенсивности входного потока 7 может быть схема, показанная на фиг. 2 которая включает в себя элементы И 28, 29, 34, 35, 40, счетчики 30, 36 и 37, М элементов ИЛИ 311-31М, формирователи импульсов 32 и 38, инвертор 33, триггер 39. Причем первый 71 вход блока определения интенсивности входного потока 7 связан с первыми входами элементов И 28 и 34. Второй вход элемента И 34 связан со вторым входом элемента И 28, первым выходом триггера 39, входом формирователя импульсов 38 и входом инвертора 33. Второй вход 72 блока определения интенсивности входного потока 7 подключен к первым входам элементов И 29 и 35, входу счетчика 37 и второму триггера 39. Первый вход триггера 39 связан со своим вторым выходом. Выходы счетчика 37 связаны соответственно с первым и вторым входом элемента И 40. Выход элемента И 40 подключен ко вторым входам элементов И 29 и 35, а также ко второму входу счетчика 37. Выход формирователя импульсов 38 соединен с третьим входом элемента И 35. Выход элемента И 29 связан со вторым входом счетчика 30, а выход элемента И 28 с первым входом счетчика 30. Выход инвертора 33 последовательно через формирователь импульсов 32 подключен к третьему входу элемента И 29. Выход элемента И 34 соединен с первым входом счетчика 36, а выход элемента И 35 со вторым входом счетчика 36. Соответствующие выходы 1-М счетчика 30 подключены к первым входам соответствующих элементов ИЛИ 3121-31М, а соответствующие выходы 1-М счетчика 36 ко вторым входам соответствующих элементов ИЛИ 311-31М. При этом выход соответствующего элемента ИЛИ 311-31М является соответствующим С1-СN выходом блока определения интенсивности входного потока 7.

Логические элементы И 28, 29, 34, 35, 40, инвертор 33 и элементы ИЛИ 311-31М могут быть реализованы на ИМС серий 133, 564 и описаны - Основы цифровой техники. /Л.А.Мальцева, Э.М.Фромберг, В.С.Ямпольский. М. Радио и связь, 1986, с.20-24, рис.9,11.

Формирователи импульсов 32 и 38 могут быть реализованы на ИМС серий 155, 176 и описаны Основы цифровой техники. /Л.А.Мальцева, Э.М.Фромберг, В.С.Ямпольский. М. Радио и связь, 1986, с.30-31, рис.22.

Счетчики 30, 36, 37 могут быть реализованы на ИМС серий 133, 564 и описаны Микросхемы и их применение: Справ.пособие. /В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалев и др. М. Радио и связь, 1984, с.139, рис.4.38.

Триггер 39 может быть реализован на ИМС серий 133, 564 и описан - Микросхемы и их применение: Справ.пособие. /В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалев и др. М. Радио и связь, 1984, с.122, рис.4.16.

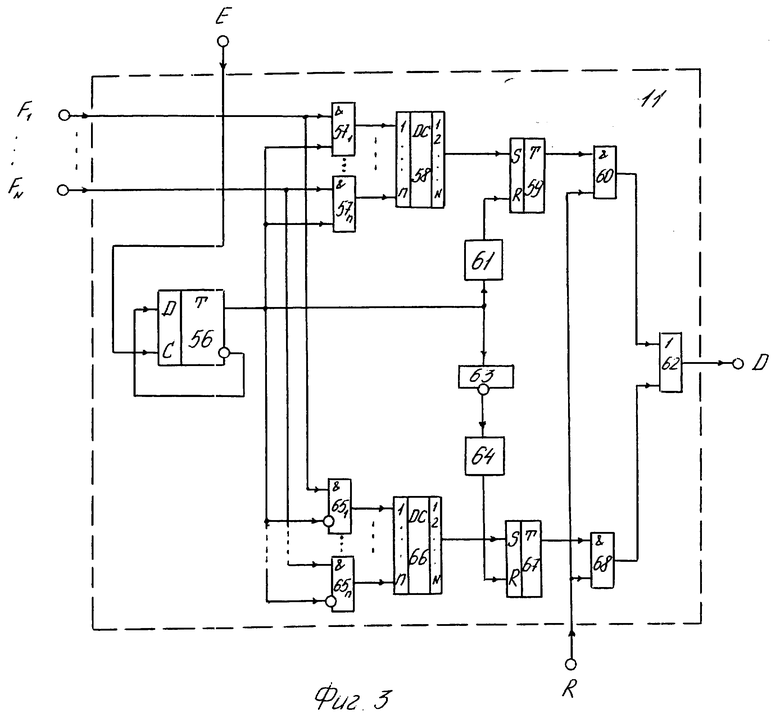

Одним из вариантов реализации блока опознавания адреса 11 может быть схема представлена на фиг. 3, которая состоит из: триггеров 56, 59 и 67, n элементов И 571-57n, n элементов И 651-65n, дешифраторов 58 и 66, элементов И 60 и 68, формирователей импульсов 61 и 64, элемента ИЛИ 62, инвертора 63. Причем группа входов комбинации адреса F1-FN связана с соответствующими первыми входами n элементов И 571-57n и соответствующими первыми входами n элементов И 651-65n. Вход E (от генератора интервалов анализа 6) соединен со вторым входом триггера 56. Первый вход триггера 56 подключен к своему второму выходу. Первый выход триггера 56 связан со вторыми входами элементов И 571-57n, вторыми входами элементов И 651-65n, а также входом формирователя импульсов 61 и входом инвертора 63. Выходы n элементов 571-57n соединены с соответствующими 1-n входами дешифратора 58. Выход дешифратора 58 подключен к первому входу триггера 59. Второй вход триггера 59 связан с выходом формирователя импульсов 61. Выходы n элементов И 651-65n соединены с соответствующими 1-n входами дешифратора 66. Выход дешифратора 66 подключен к первому входу триггера 67. Выход инвертора 63 связан со входом формирователя импульсов 64, а выход формирователя импульсов 64 со вторым входом триггера 67. Вход R сигнала разрешения соединен со вторыми входами элементов И 60 и 68. Первый вход элемента И 60 подключен к выходу триггера 59, а первый вход элемента И 68 к выходу триггера 67. Выходы элементов И 60 и 68 связаны соответственно с первым и вторым входами элемента ИЛИ 62. Выход элемента ИЛИ 62 является выходом D блока опознавания адреса 11.

Логические элементы И 571-57n, 60 и 68, И 651-65n, инвертор 63, элемент ИЛИ 62 могут быть реализованы на ИМС серий 133, 564 и описаны Основы цифровой техники. /Л.А.Мальцева, Э.М.Фромберг, В.С.Ямпольский. -М. Радио и связь, 1986, с.20-24, рис.9,11.

Формирователи импульсов 61 и 64 могут быть реализованы на ИМС серий 155 и описаны Основы цифровой техники. /Л.А.Мальцева, Э.М.Фромберг, В.С.Ямпольский. М. Радио и связь, 1986, с.30-31, рис.22.

Триггеры 59 и 67 могут быть реализованы на ИМС серий 133, 564 и описаны

Микросхемы и их применение Справ.пособие. /В.А.Батушев, В.В.Вениаминов, В. Г.Ковалев и др. М. Радио и связь, 1984, с.118, рис.4.12.

Триггер 56 может быть реализован на ИМС серий 133, 564 и описан - Микросхемы и их применение Справ.пособие. /В.А.Батушев, В.В.Вениаминов, В.Г. Ковалев и др. М. Радио и связь, 1984, с.122, рис. 4.16.

Дешифраторы 58 и 66 могут быть реализованы на ИМС серий 176, 155 и описаны Микросхемы и их применение: Справ.пособие. /В.А.Батушев, В.В.Вениаминов, В.Г.Ковалев и др. М. Радио и связь, 1984, с.130, рис.4.29, причем у дешифраторов используется только один выход, который настроен на необходимую кодовую комбинацию адреса.

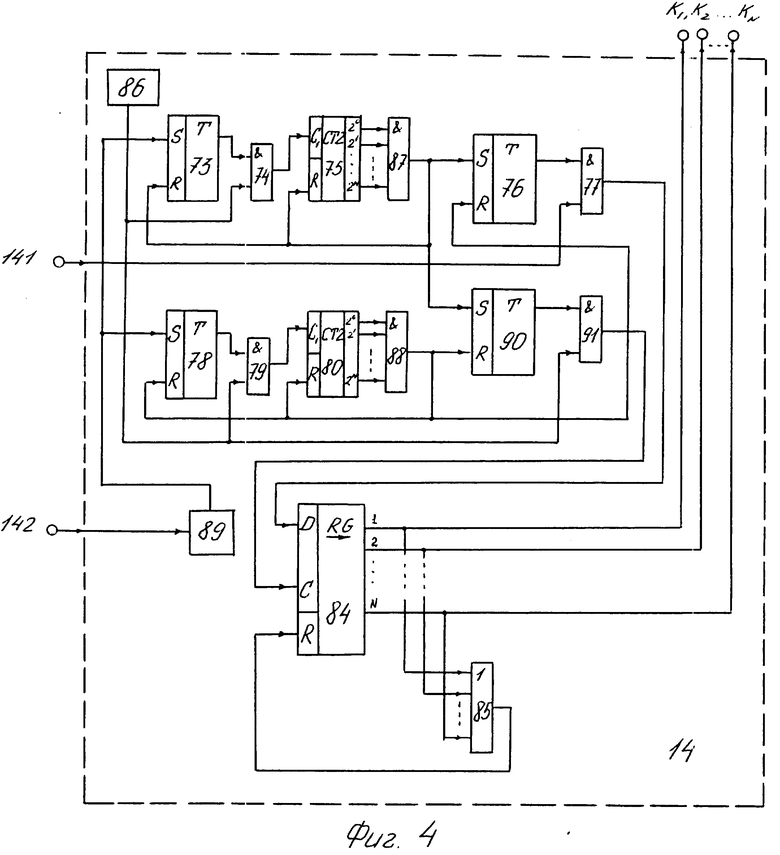

Одним из вариантов реализации блока выделения адреса 14 может быть схема, показанная на фиг. 4 которая состоит из: триггеров 73, 76, 78 и 90, элементов И 74, 77, 79, 87, 88 и 91, счетчиков 75 и 80, регистра сдвига 84, элемента ИЛИ 85, генератора тактовых импульсов 86 и формирователя импульсов 89. Причем первый вход 141 блока выделения адреса 14 подключен ко второму входу элемента И 77, а второй вход 142 блока выделения адреса 14 связан со входом формирователя импульсов 89. Выход формирователя импульсов 89 соединен с первыми входами триггеров 73 и 78. Выход генератора тактовых импульсов 86 подключен ко вторым входам элементов И 74, 79 и 91. Выход триггера 73 связан с первым входом элемента И 74, а выход элемента И 74 соединен с первым входом счетчика 75. Выходы счетчика 75 подключены к соответствующим входам элемента И 87. Выход элемента И 87 связан с первыми входами триггеров 76 и 90 и вторыми входами триггера 73 и счетчика 75. Выход триггера 76 подключен к первому входу элемента И 77. Выход элемента И 77 соединен с первым входом регистра сдвига 84. Выход триггера 78 связан с первым входом элемента И 79. Выход элемента И 79 подключен к первому входу счетчика 80. Выходы счетчика 80 связаны с соответствующими входами элемента И 88. Выход элемента И 88 соединен со вторыми входами триггеров 76, 78, 90 и счетчика 80. Выход триггера 90 подключен к первому входу элемента И 91, а выход элемента И 91 ко второму входу регистра сдвига 84. Выходы 1-N регистра сдвига 84 связаны с соответствующими входами элемента ИЛИ 85 и являются соответственно К1-КN выходами блока выделения адреса 14. Выход элемента ИЛИ 85 соединен с третьим входом регистра сдвига 84.

Логические элементы И 74, 77, 79, 87, 88, 91 и ИЛИ 85 могут быть реализованы на ИМС серий 133, 564 и описаны Основы цифровой техники. /Л.А.Мальцева, Э.М.Фромберг, В.С.Ямпольский. М. Радио и связь, 1986, с.20-24, рис.9,11.

Триггеры 73, 76, 78 и 90 могут быть реализованы на ИМС серий 133, 564 и описаны Микросхемы и их применение: Справ.пособие. /В.А.Батушев, В.В.Вениаминов, В.Г.Ковалев и др. М. Радио и связь, 1984, с.118, рис.4.12.

Счетчики 75 и 80 могут быть реализованы на ИМС серий 133, 564 и описаны

Микросхемы и их применение: Справ.пособие. /В.А.Батушев, В.В.Вениаминов, В. Г.Ковалев и др. М. Радио и связь, 1984, с.139, рис.4.37.

Регистр сдвига 84 и может быть реализован на ИМС серий 134 и 531 и описан Микросхемы и их применение Справ.пособие. /В.А.Батушев, В.В.Вениаминов, В.Г.Ковалев и др. М. Радио и связь, 1984, с.135, рис.4.35.

Генератор тактовых импульсов 86 может быть реализован на ИМС серий 176 и 511 и описан Микросхемы и их применение: Справ.пособие. /В.А.Батушев, В.В. Вениаминов, В.Г.Ковалев и др. М. Радио и связь, 1984, с.213, рис.7.6.

Формирователь импульсов 89 может быть реализован на ИМС серий 155, 176 и описан Основы цифровой техники. /Л.А.Мальцева, Э.М.Фромберг, В.С.Ямпольский. М. Радио и связь, 1986, с.30-31, рис.22.

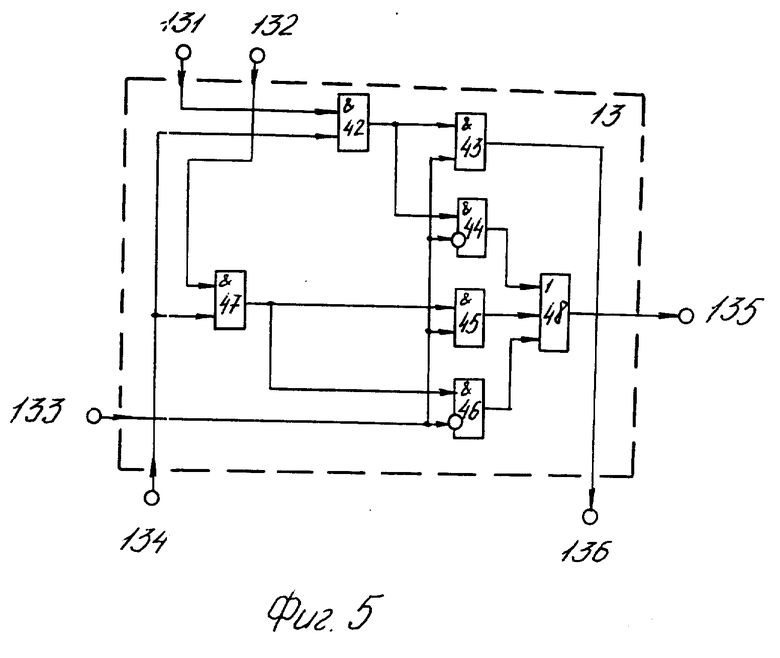

Одним из вариантов реализации блока коммутации 13 может быть схема, показанная на фиг. 5 и состоящая из элементов И 42, 43, 44, 45, 46 и 47, а также элемента ИЛИ 48. Причем первый вход 131 блока коммутации 13 подключен к первому входу элемента И 42. Второй вход 132 блока коммутации 13 связан с первым входом элемента И 47. Третий вход 133 блока коммутации 13 соединен со вторыми входами элементов И 43, 44, 45 и 46. Четвертый вход 134 блока коммутации 13 подключен ко вторым входам элементов И 42 и 47. Выход элемента И 42 соединен с первыми входами элементов И 43 и 44. Выход элемента И 47 связан с первыми входами элементов И 45 и 46. Выходы элементов И 44, 45 и 46 подключены соответственно к первому, второму и третьему входам элемента ИЛИ 48, а выход элемента ИЛИ 48 является первым выходом 135 блока коммутации 13. Выход элемента И 43 является вторым выходом 136 блока коммутации 13.

Логические элементы И 42, 43, 44, 45, 46 и 47, а также элемент ИЛИ 48 могут быть реализованы на ИМС серий 133, 564 и описаны Основы цифровой техники. /Л.А.Мальцева, Э.М.Фромберг, В.С.Ямпольский. М. Радио и связь, 1986, с. 20-24, рис.9, 11.

Заявляемое устройство работает следующим образом. Очевидно, что при организации каналов множественного доступа может иметь место ситуация, когда удаление отдельных абонентов или рельеф местности будут приводить к нарушению полносвязной конфигурации канала множественного доступа. Наиболее динамичной будет структура, в которой абоненты являются мобильными. Восстановление связности в таких условиях будет осуществляться с применением ретранслятора на летно-подъемных средствах. Абоненты, имеющие непосредственную связь в течение определенного интервала времени, осуществляют обмен данными в основной полосе частот канала (на частоте fн). Если абонент имеет сообщение, которое должен довести до другого абонента, не имеющего прямой связи с ним, то он осуществляет передачу данного сообщения на частоте доступа к ретранслятору (fд), который в широковещательном режиме передает данное сообщение с признаком передачи с борта ретранслятора ко всем включенным в канал абонентам на частоте fн (поскольку высота подъема ретранслятора обеспечивает его доступность всем абонентам канала множественного доступа).

Решение о доступности (или недоступности) адресата каждый абонент принимает на основе информации, получаемой им в течение предыдущего и текущего интервалов анализа (путем прослушивания канала множественного доступа на частоте fн), выделения из заголовков сообщений, проходящих по каналу (без учета сообщений, имеющих признак передачи с борта ретранслятора), адресов абонентов-отправителей и запоминания их на время, равное длительности интервала анализа, необходимое для повторного набора статистики). Кроме того, в каждом интервале анализа определяется также и максимальная достигнутая интенсивность входного потока сообщений Λ которая сравнивается с допустимой Lд, в результате чего принимается решение следующим образом:

1. если абонент доступен, Λ < Λд, то передача на частоте fн;

2. если абонент доступен, Λ > Λд, то передача на частоте fд;

3. если абонент не доступен, Λ < Λд, то передача на частоте fд;

4. если абонент не доступен, Λ > Λд, то передача на частоте fд.

Функциональная схема устройства, реализующего выполнение описанных функций управления передачей данных в неполносвязном радиоканале множественного доступа приведена на фиг. 1.

Принцип работы предлагаемого устройства заключается в следующем:

синхронизатор 1 формирует импульсы с периодом следования, равным τ, причем во всех устройствах, включенных в радиоканал, эти импульсы формируются синхронно. При появлении сигнала, информирующего о наличии в канале несущей (на входе сигнала наличия несущей 20 устройства), что свидетельствует о начале передачи другим (в общем случае другими) абонентом, триггер цикла передачи 3 переходит в состояние хранения логической единицы. При этом сигнал с уровнем логической единицы с его выхода поступает на второй вход первого элемента И 2 (тем самым запрещается прохождение очередного импульса с выхода синхронизатора 1 через первый элемент И 2), а также на вход формирователя импульсов 5 и на второй вход 142 блока выделения адреса 14, на первый вход 141 которого поступает последовательность символов заголовка передаваемого в канале сообщения (с выхода канала множественного доступа 21 устройства). В результате на группе выходов К1-КN блока выделения адреса 14 в параллельном коде появляется кодовая комбинация адреса абонента-отправителя, которая поступает на соответствующие группы вторых входов F1-FN всех N блоков опознавателя адреса 111-11N. При этом соответствующий данному адресу блок опознавателя адреса 11 запоминает его (тем самым фиксируется факт доступности этого абонента данному устройству, прослушивающему канал). С выхода формирователя импульсов 5 импульс поступает на первый вход 71 блока определения интенсивности входного потока 7, при этом последний осуществляет формирование и выдачу на группу своих выходов С1-СN кодовой комбинации, соответствующей интенсивности входного потока в канале в предыдущем и текущем интервалах анализа. По окончании очередного интервала анализа кодовая комбинация, соответствующая максимальной достигнутой в этом интервале анализа интенсивности входного потока, поступает на группу входов блока сравнения 8 и сравнивается с заданным пороговым значением интенсивности. В результате сравнения на одном из трех 81-83 выходов блока сравнения 8 появляется уровень логической единицы, который в случае L ≥ Λд поступает на выход 81 или выход 82 блока сравнения 8 и через элемент ИЛИ 9 на второй 132 вход блока коммутации 13, а при Λ < Λд на выход 83 блока сравнения 8 и соответственно на первый 131 вход блока коммутации 13.

При необходимости начать передачу на вход запроса передачи 22 устройства и на третий вход второго элемента И 4 поступает сигнал запроса передачи, соответственно он поступает на четвертый 134 вход блока коммутации 13, а также на первый вход триггера разрешения передачи 16. Одновременно на группу входов кода адреса 23 устройства и соответственно на группу входов S1-SN дешифратора 10 в параллельном коде поступает сигнал кода адреса абонента, которому предназначено сообщение. При этом в зависимости от кода адреса на одном из N выходов L1-LN дешифратора 10 появляется сигнал с уровнем логической единицы, который поступает на соответствующий третий вход R1-RN соответствующего блока опознавания адреса 111-11N. Если в предыдущем или текущем интервалах анализа данный абонент был признан доступным, то сигнал с уровнем логической единицы с выхода D1-DN данного блока опознавания адреса 111-11N через второй элемент ИЛИ 12 поступает на третий 133 вход блока коммутации 13. При этом, если в предыдущем или текущем интервалах анализа выполнено условие Λ < Λд и абонент доступен, то есть на входе 133 блока коммутации 13 логическая 1, а также, если абонент недоступен на частоте fн, что соответствует наличию на третьем 133 входе блока коммутации 13 уровня логического нуля, то с первого выхода 135 этого блока на выход разрешения передачи на fд 24 устройства поступает сигнал разрешения передачи на частоте доступа к ретранслятору fд (в соответствии с протоколом неконтролируемого случайного множественного доступа). В случае, если Λ ≥ Λд, то сигнал с уровнем логической единицы со второго 136 выхода блока коммутации 13 поступает на третий вход второго элемента И 4. Если в данный момент времени канал (fн) свободен, то первый элемент И 2 открыт сигналом с уровнем логического нуля, поступающего с выхода триггера цикла передачи 3 на второй вход первого элемента И 2. При этом ближайший по времени импульс с выхода синхронизатора 1 через открытый первый элемент И 2 поступает на первый вход второго элемента И 4. Поскольку на втором и третьем его входах присутствуют сигналы с уровнем логической единицы, то импульс с его выхода поступает через третий элемент ИЛИ 15 на выход включения передатчика 26 устройства. При этом включается передатчик на интервал времени, определяемый длительностью импульса, формируемого синхронизатором 1. Появляющийся после включения передатчика на частоте fн сигнал несущей в радиоканале приводит к появлению во всех устройствах, включенных в радиоканал, сигнала с уровнем логической единицы на выходе первого триггера 3. Одновременно сигнал поступает на вход элемента задержки 19, с выхода которого далее поступает на первые входы третьего 17 и четвертого 18 элементов И. Время задержки элемента задержки 19 равно длительности импульса, сформированного синхронизатором 1. Это время должно быть не меньше максимального времени распространения сигнала между абонентами τp. Если на передачу вышло одновременно два или несколько устройств, то на втором входе четвертого элемента И 18 появляется сигнал о наличии несущей в канале, а на выходе четвертого элемента И 18 и на выходе сигнала конфликта 27 устройства появляется сигнал, оповещающий о столкновении при попытке передачи. По сигналу столкновения абоненты радиоканала снимают со входов 22, 23 устройства сигналы запроса передачи и кода адреса и откладывают попытку передачи.

При отсутствии сигнала несущей, в момент появления импульса на выходе задержки 19, на выходе четвертого элемента И 18 отсутствует сигнал, а на выходе третьего элемента И 17 появляется сигнал, устанавливающий триггер разрешения передачи 16 в режим хранения логической единицы. При этом на выходах разрешения передачи на fн 25 и включения передатчика 26 устройства появляются сигналы, разрешающие включение передатчика и передачу данных в радиоканал на частоте fн.

После окончания передачи абонент снимает со входов 22, 23 устройства сигналы запроса передачи и кода адреса, что приводит к установке в исходное (нулевое) состояние триггера разрешения передачи 16 блока коммутации 13. Устройство продолжает набор статистики о доступности абонентов и интенсификации входного потока в очередном интервале анализа.

Блок определения интенсивности входного потока 7, показанный на фиг. 2, работает следующим образом. После включения питания первый импульс, поступающий с выхода генератора интервалов анализа 6 на второй вход 72 блока определения интенсивности входного потока 7, переводит триггер 39 в режим хранения логической единицы. При этом элемент И 34 открывается импульсами от формирователя импульсов 5, а счетчик 36 подсчитывает число передач в канале и определяет интенсивность входного потока сообщений. На выходах группы элементов ИЛИ 311-31М и соответственно на группе выходов С1-СN блока определения интенсивности входного потока 7 имеет место кодовая комбинация, соответствующая максимальной достигнутой на данный момент времени интенсивности входного потока сообщений. При поступлении очередного (второго) импульса от генератора интервалов анализа 6 триггер 39 переходит в режим хранения логического нуля, открывается элемент И 28, счетчик 30 работает аналогично счетчику 36. При поступлении третьего импульса от генератора интервалов анализа 6 счетчик 37 открывает элемент И 40. Сигнал с уровнем логической 1 поступает на вторые входы элементов И 29, 35. При этом на первые входы этих элементов поступает импульс от генератора интервалов анализа 6. Тем самым создаются условия для отпирания логических элементов И 29, 35 импульсом по третьему входу. Поэтому, в зависимости от состояния триггера 39, соответствующий счетчик обнуляется, за счет поступления через открытый элемент И 29 или И 35 импульса от соответствующего формирователя импульсов 32 или 38. Так, при нулевом состоянии триггера 39, за счет поступления через открытый элемент И 29 на второй вход счетчика 30 импульса с выхода формирователя импульсов 32, счетчик 30 обнуляется, а при единичном состоянии триггера 39, за счет поступления через открытый элемент И 35 на второй вход счетчика 36 импульса с выхода формирователя импульсов 38, обнуляется счетчик 36. В то же время импульс с выхода элемента И 40 поступает на второй вход счетчика 37 и обнуляет его. Благодаря такому наличию элементов и связей блок определения интенсивности входного потока 7 определяет интенсивность входного потока в предыдущем и текущем интервале анализа.

Блок опознавания адреса 11, функциональная схема которого приведена на фиг. 3, работает следующим образом. После включения питания первый импульс, пришедший с выхода генератора интервалов анализа 6 на вход E блока, переводит триггер 56 в режим хранения логической единицы. Уровень логической единицы с выхода последнего создает благоприятные условия для работы группе элементов И 571-57N. Благодаря этому все кодовые комбинации адресов, выделяемые блоком выделения адреса 14 в течение данного интервала анализа и поступающие на группу входов комбинации адреса F1-FN блока опознавания адреса 11 анализируются дешифратором 58. Причем у дешифратора 58 используется выход, настроенный на заданную кодовую комбинацию адреса. Если на его вход поступает соответствующая ему кодовая комбинация адреса, то сигнал с уровнем логической единицы с его выхода поступают на первый вход триггера 59, который переходит в режим хранения логической единицы, создавая условия для открывания элемента И 60. При поступлении очередного импульса с выхода генератора интервалов анализа 6 на вход E триггер 56 переходит в режим хранения логического нуля. При этом открывается группа элементов И 651-65N, кодовые комбинации адресов аналогичным образом анализирует дешифратор 66. Причем у дешифратора 66, также как и у дешифратора 56, используется только один выход, настроенный на заданную кодовую комбинацию адреса. При поступлении сигнала в виде уровня логической единицы с определенного выхода L1-LN дешифратора 10 на вход сигнала разрешения R, соответствующего блока опознавания адреса 11, в случае, если на первые входы элементов И 60, 68 подается логическая единица, то эти элементы открыты, и данный сигнал через элемент ИЛИ 62 поступает на выход D блока опознавания адреса 11. Этим самым подтверждается, что в течение предыдущего или текущего интервалов анализа абонент с данным адресом был доступен на частоте fн. В случае, если на вход сигнала разрешения R блока опознавания адреса 11 не поступает логическая единица, элементы И 60, 68 закрыты и на выходе D блока опознавания адреса 11 логический ноль, абонент полагается недоступным на частоте fн. Элементы 61, 63, 64 необходимы для приведения блока опознавания адреса 11 в исходное состояние в начале очередного интервала анализа.

Блок выделения адреса 14, показанный на фиг. 4, работает следующим образом. При передаче в канале множественного доступа каким-либо корреспондентом сообщения сигнал с уровнем логической единицы с выхода триггера цикла передачи 3 поступает на второй вход 142 блока выделения адреса 14 и далее на вход формирователя импульсов 89, импульс с выхода которого переводит триггеры 73 и 78 в единичное состояние. В результате этого последовательность таких импульсов, с выхода генератора тактовых импульсов 86, через открытые элементы И 74 и 79 поступает на входы счетчиков 75 и 80. Счетчик 75 отсчитывает количество символов заголовка, предшествующих символам адреса, после чего открывается элемент И 87 и с выхода логического элемента И 87 сигнал с уровнем логической единицы поступает на первые входы триггеров 76 и 90 и на вторые входы триггера 73 и счетчика 75. При этом триггер 73 переходит в нулевое состояние, тем самым прекращается поступление последовательности тактовых импульсов на вход счетчика 75, а триггеры 76 и 90 переходят в единичное состояние, тем самым открывая в соответствии с тактовыми импульсами от генератора тактовых импульсов 86 элемент И 91, а также создавая условия для открывания элемента И 77. При этом на вход синхронизации С регистра сдвига 84 с выхода элемента И 91 начинает поступать последовательность тактовых импульсов, а на его информационный вход D, через открывающийся элемент И 77, последовательность символов заголовка сообщения, поступающего из канала множественного доступа на первый вход 141 блока выделения адреса 14, причем, начиная с первого символа адреса. Счетчик 80, закончив отсчет количества символов, предшествующих символам адреса и количества символов самого адреса, открывает элемент И 88, и с выхода элемента И 88 сигнал с уровнем логической единицы поступает на вторые входы триггеров 76, 78 и 90 и счетчика 80. При этом прекращается поступление последовательности тактовых импульсов на вход счетчика 80 на вход C синхронизации регистра сдвига 84, а также поступление последовательности символов заголовка сообщения на информационный вход D регистра сдвига 84. Кодовая комбинация адреса, выделенная из состава заготовки сообщения, в параллельном коде поступает с выходов регистра сдвига 84 на входы элемента ИЛИ 85 и выходы К1-КN блока выделения адреса 14. Так как все кодовые комбинации, используемые для адресования, являются ненулевыми, то сигнал с уровнем логической единицы с выхода элемента ИЛИ 85 поступает на вход R, установки в нулевое состояние регистра сдвига 84 и переводит его в исходное состояние.

Блок коммутации 13 реализован в виде, показанном на фиг. 5. При таком наличии описанных элементов и связей между элементами обеспечивается требуемая коммутация блоков заявляемого устройства в соответствии с описанным алгоритмом работы.

Таким образом, при такой совокупности существенных признаков на основании анализа интенсивности входного потока сообщений в текущем и предыдущем интервалах анализа принимается решение о доступности или недоступности адресата. А на основании этого решения устройство управления передачей данных по радиоканалу обеспечивает возможность работы устройства в неполносвязном канале множественного доступа, имеющем быстроменяющуюся динамическую структуру.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| УСТРОЙСТВО ПОДКЛЮЧЕНИЯ ИСТОЧНИКОВ ИНФОРМАЦИИ К ОБЩЕЙ МАГИСТРАЛИ | 2001 |

|

RU2194301C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2233038C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2148294C1 |

| СПОСОБ СКРЕМБЛИРОВАНИЯ АНАЛОГОВОГО СИГНАЛА И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1997 |

|

RU2123764C1 |

| СПОСОБ И УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТОВ ДАННЫХ В КАНАЛЕ СВЯЗИ ОБЩЕГО ПОЛЬЗОВАНИЯ | 1997 |

|

RU2115246C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168870C1 |

Изобретение относится к вычислительной технике и может использоваться в узлах коммутации сообщений (пакетов) сети передачи данных автоматизированной системы управления. Целью изобретения является разработка устройства управления передачей данных по радиоканалу, для обеспечения возможности его работы в неполносвязном канале множественного доступа, имеющем быстроменяющуюся динамическую структуру. Устройство управления передачей данных по радиоканалу включает синхронизатор 1, элементы И 2, 4, 17 и 18, триггеры 3 и 16, формирователь импульсов 5, генератор интервалов анализа 6, блок определения интенсивности входного потока 7, блок сравнения 8, элементы ИЛИ 9, 12 и 15 , дешифратор 10, блоки опознавания адреса 111-11N, блок коммутации 13, блок выделения адреса 14, элемент задержки 19. При такой схеме анализ интенсивности входного потока осуществляется в предыдущем и текущем интервалах анализа, на основании чего, а также на основании анализа адресов абонентов отправителей принимается решение о доступности или недоступности адресата. 5 ил.

Устройство управления передачей данных по радиоканалу, содержащее синхронизатор, выход которого соединен с прямым входом первого элемента И, инверсный вход которого соединен с прямым выходом триггера цикла передачи, первый вход второго элемента И и инверсный вход триггера разрешения передачи соединены между собой и являются входом сигнала "Запрос передачи" устройства, входом сигнала несущей которого является первый вход триггера цикла передачи, прямой выход триггера разрешения передачи соединен с первым входом первого элемента ИЛИ и является входом "Разрешение передачи", второй вход первого элемента ИЛИ через элемент задержки соединен с первым входом третьего элемента И и с первым входом четвертого элемента И, выход которого соединен с инверсным входом третьего элемента И, выход которого соединен с прямым входом триггера разрешения передачи, выход первого элемента ИЛИ и выход четвертого элемента И являются соответственно выходами "Включение передатчика" и "Столкновения" устройства, а также блок сравнения и формирователь импульсов, отличающееся тем, что дополнительно введены блок определения интенсивности входного потока сообщений, блок выделения адреса, блок коммутации, N блоков опознавания адреса, второй и третий элементы ИЛИ, генератор интервала анализа и дешифратор, при этом первый и второй входы триггера цикла передачи соединены между собой, а выход триггера цикла передачи соединен с первым входом блока выделения адреса и с входом формирователя импульсов, выход которого соединен с первым входом блока определения интенсивности входного потока сообщений, второй вход которого соединен с выходом генератора интервала анализа и с первыми входами N блоков опознавания адреса, выходы блока определения интенсивности входного потока сообщений соединены с соответствующими входами блока сравнения, первый и второй выходы которого через второй элемент ИЛИ соединены с первым управляющим входом блока коммутации, к второму управляющему входу которого подключен третий выход блока сравнения, выходы N блоков опознавания адреса через третий элемент ИЛИ соединены с адресным входом блока коммутации, вход исходного состояния которого соединен с инверсным входом триггера разрешения передачи, первый выход блока коммутации является выходом "Разрешения передачи на частоте доступа к ретранслятору" устройства, а второй выход блока коммутации соединен с вторым входом второго элемента И, третий вход которого соединен с выходом первого элемента И, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, второй вход четвертого элемента И и второй вход блока выделения адреса соединены между собой и являются входом канала множественного доступа, выходы блока выделения адреса соединены с соответствующими входами N блоков опознавания адреса, к управляющим входам которых подключены соответствующие выходы дешифратора, входы которого являются входами "Код адреса" устройства.

| SU, авторское свидетельство, 1319298, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1997-12-20—Публикация

1995-01-10—Подача