Изобретение касается коммуникаций системы обработки данных, в частности схемы для регулирования потока информации по информационной шине путем перехвата коммуникаций между двумя устройствами.

Системы обработки данных часто требуют, чтобы периферийные устройства, терминалы или множество компьютеров сообщались между собой. В системе обработки данных высокой эффективности взаимные соединения между компонентами системы являются критическим параметром при достижении требуемой высокой эффективности работы. Пример высокой эффективной системы, которая обычно используется, представляет система связи.

Патент США N 4256926 является примером микроуправляемой системы коммутации связи, которая содержит распределенное управление через распределенные микропроцессоры, где микропроцессоры содержат буферы, которые образуют связь, необходимую между микропроцессорами.

Патент США N 4119803 описывает систему коммутации АТС, которая управляется парой управляющих блоков через централизованный механизм и включает в себя множество регистров для управления потоком и диалогом, которая производит управление и информационную связь с АТС.

Патент США N 4412282 описывает управляемую микропроцессором телефонную коммутационную сеть, которая обеспечивает повышенную надежность через схемы четности адресов и данных.

Патент США N 4580011 представляет распределенную обрабатывающую телефонную коммутационную систему, которая содержит главный управляющий микропроцессор, который, в свою очередь, управляет несколькими микропроцессорами специальных функций.

Различие между схемой связи и обычной схемой связи обработки данных заключается в том, что в системе обработки данных число терминалов для коммуникации меньше и что пропускная способность данных, необходимая для связи системы обработки данных, вообще выше. Однако также требуется способность динамичного соединения компонентов системы, поэтому разработаны разные способы для связи между одним элементом системы обработки данных и другим.

Пример этого приведен в патенте США N 4264782, где главный процессор сообщается с несколькими терминалами через сеть связи данных. В этой системе связи могут шифроваться, но также управляются центральным процессором. Когда центральный процессор является главным, терминалы становятся управляемыми и все управление связью по сети коммуникации данных проводится главным центральным процессором. Это может быть узким местом, когда системы обработки данных содержат несколько автономных элементов, требующих связи.

Патент США N 4551831 является другим примером схемы связи обработки данных, которая иллюстрирует мультиплексор, используемый для управления несколькими каналами. Центральный процессор управляет мультиплексором. Дальнейшая иллюстрация связи элемента обработки данных приведена в патенте США N 4710868, показывающим соединение нескольких автономных рабочих мест с центральным запоминающим устройством (ЗУ). Автономные рабочие места получают доступ к центральному ЗУ через двухуровневый переключатель, который производит перевод возможного адреса в реальный, а также коммутирование.

При этом требуются много высокоэффективных систем связи обработки данных для того, чтобы некоторые элементы обработки данных сообщались одновременно друг с другом. Эта возможность обеспечивается путем использования матричного коммутатора. Пример реализации матричного коммутатора приведен в патенте США N 4539564, где он сравнивается с одинарной информационной шиной, которая образует только один канал связи каждый раз. В типичной конфигурации матричный коммутатор создает возможность для любого терминала говорить с любым другим незанятым терминалом в системе и также будет производить одновременные связи между несколькими парами терминалов. Традиционно это достигается тем, что терминал, запрашивающий доступ к матричному коммутатору, делает это через центральный контроллер коммутатора, чтобы определить, может ли принимающий терминал принимать передачу от исходного (запрашивающего) терминала. После приема сигнала состояния, указывающего, что такая связь может быть произведена, матричный коммутатор получает команду произвести соединение между передающим терминалом и принимающим терминалом, чтобы два терминала могли обмениваться информацией. Когда связь должна быть окончена, исходный терминал традиционно посылает сигнал центральному контроллеру матричного коммутатора об отсоединении принимающего терминала.

Цель изобретения - создание логического средства для регулирования соединений между элементами в системе обработки данных путем контроля их связей для определения, когда должно быть произведено изменение в системе связи. Цель достигается путем контроля передач между двумя элементами системы.

Патент США N 4539564 представляет вариант реализации коммутатора матричного типа и описывает контроль входов и выходов. Однако этот контроль проводится только для эксплуатации, чтобы определить, когда происходят условия ошибки, и источники этих условий ошибки. Аналогичным образом в "Бюллетене технических решений IBM", т. 31, N 1, июнь 1988 г., в работе "Следящее устройство матричного коммутатора" также содержится схема эксплуатации для контроля и связи по расписанию через коммутатор матричного типа.

Однако ни одна из этих публикаций и ни одна из вышеупомянутых публикаций не описывает механизм, в котором связь контролируется, чтобы регулировать связь по информационной шине.

В соответствии с предлагаемым изобретением предусматривается система связи, которая устанавливает канал связи между двумя из множества устройств, соединенных с системой связи. Система далее включает схему первого порта, который соединен по крайней мере с одним устройством, и схему второго порта, который соединен по крайней мере со вторым устройством. Коммутатор соединен между первым и вторым портами, который образует коммуникационные соединения между портами. Коммутатор далее содержит схему контроля для контроля связей между устройствами для определения, что изменение в канале связи должно произойти и соответственно изменить канал связи.

В предпочтительном варианте реализации предусмотрена система обработки данных, которая соединена с матричным коммутатором через множество портов. При функционировании устройство, соединенное с портом, будет посылать информацию на порт, чтобы установить связь через матричный коммутатор, и второго порта с другим устройством. Матричный коммутатор в предпочтительном варианте реализации включает в себя схему контроля для контроля связи между двумя портами для определения, когда должно произойти прекращение связи. Матричный коммутатор тогда соединяет или разъединяет порты между устройствами.

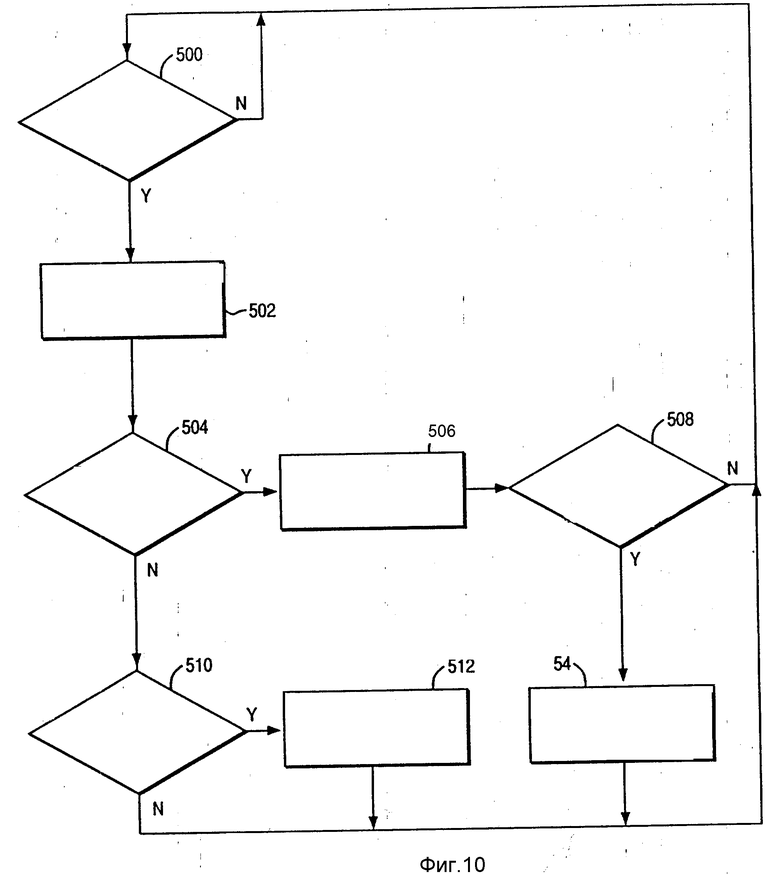

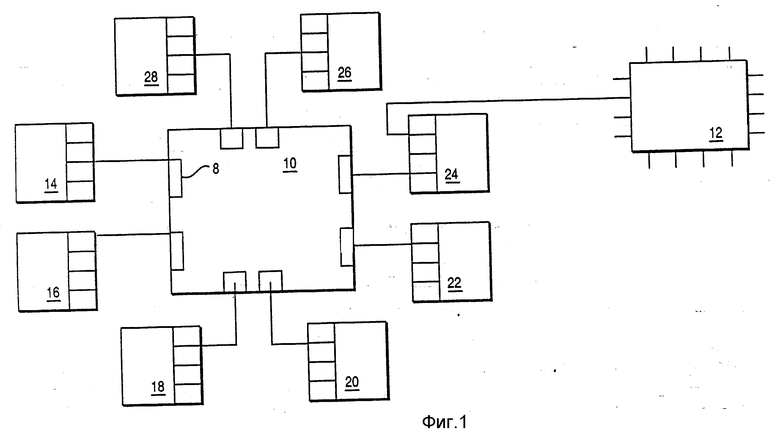

На фиг. 1 представлена блок-схема, показывающая восемь систем, соединенных с первым матричным коммутатором, и одну, соединенную со вторым матричным коммутатором; на фиг. 2 - блок-схема, показывающая содержание матричного коммутатора; на фиг. 3 - блок-схема, показывающая содержание схемы порта матричного коммутатора; на фиг. 4 - блок-схема, матричного коммутатора; на фиг. 5 - схема событий, показывающая события между портом A и портом B и матричным коммутатором при установлении канала связи между портом A и портом B; на фиг. 6 - схема событий, показывающая разъединение между портом A и портом B; на фиг. 7 -блок-схема порядка действия, показывающая управление портом, когда принят фрейм о связи от его канала; на фиг. 8 - блок-схема порядка действий, показывающая управление портом, когда принят запрос от шины связи; на фиг. 9 - блок-схема порядка действий, показывающая окончание связи портом; на фиг. 10 - блок-схема порядка действий, показывающая управление матричным коммутатором во время связи порта-с-портом.

На фиг. 1 представлена блок-схема системы связи, которая содержит несколько систем 14, 16, 18, 20, 22, 24, 26 и 28, каждая из которых соединена с матричным коммутатором 10. Каждая из систем, такая как система 14, соединена с матричным коммутатором 10 через порт 8. При этом следует отметить, что каждая система, такая как система 24, альтернативно может быть соединена с дополнительным матричным коммутатором (таким как коммутатор 12) для резервной возможности или соединения. В предпочтительном варианте реализации система 14 и система 24 являются Системой RI SC/6000 автономными рабочими местами, которые соединены последовательным световодным каналом с матричным коммутатором 10. В предпочтительном варианте реализации каждая Система RI SC/6000 может содержать четыре порта для реализации последовательных соединений канала связи. Пример протокола, используемого с последовательным соединением канала связи, представляет ES CON (Соединение предпринимательской системы для последовательного канала входа/выхода предпринимательской системы IBM 3090). Должно быть понятно в этом предпочтительном варианте реализации, что когда система должна быть соединена с другой системой для передачи информации на другую систему, вся информация передается по этому световодному каналу последовательной связи. Исходная система будет посылать фрейм информации до 32 байтов, чтобы первоначально установить связь с принимающей системой. После передачи и приема первого фрейма, устанавливающего соединение через матричный коммутатор 10, это соединение сохраняется, так что исходная система может непрерывно посылать дополнительные фреймы информации на принимающую систему, пока не будет послан фрейм об отсоединении, чтобы предупредить принимающую систему и коммутатор 10, что происходит отсоединение. В предпочитаемом варианте реализации матричный коммутатор является коммутатором N•N, поддерживающим N•N-портов для образования одновременной связи между соединенными портами и системами, соединенными с портами.

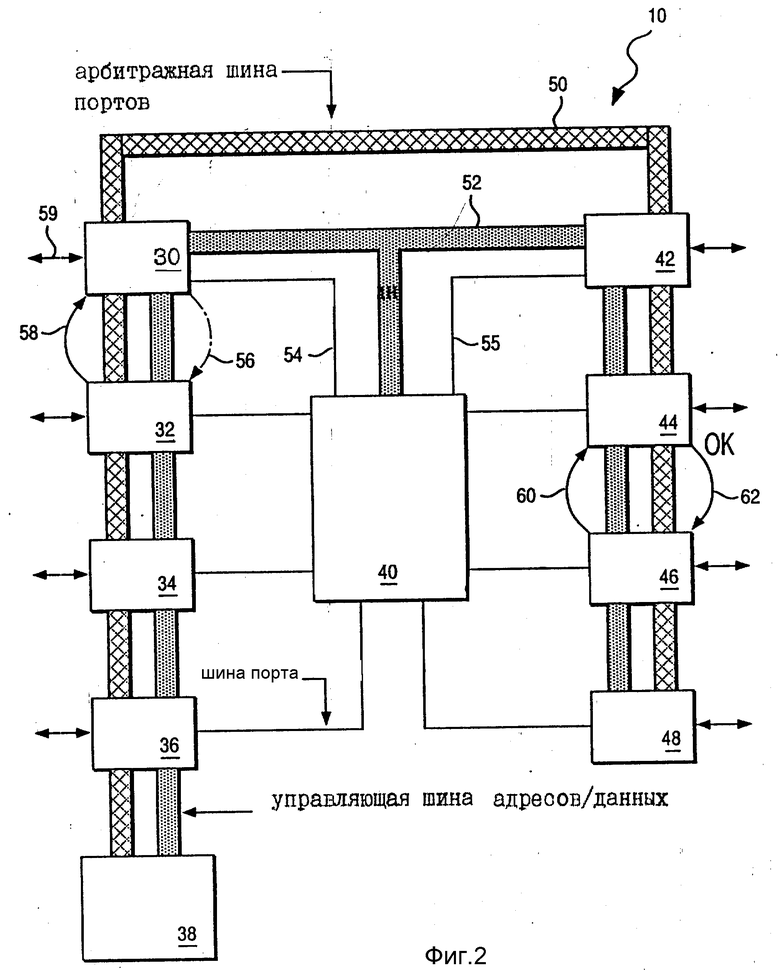

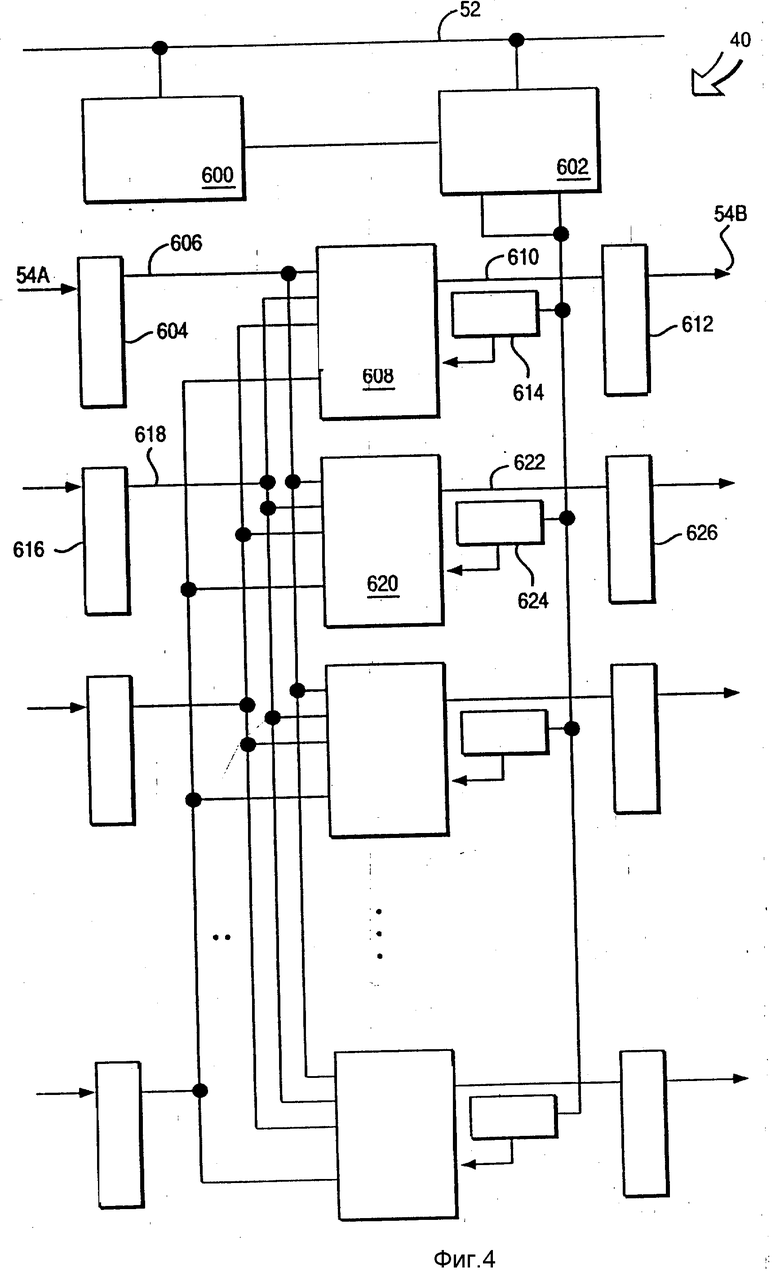

На фиг. 2 представлена блок-схема матричного коммутатора данных 10. В предпочтительном варианте реализации предусмотрен коммутатор 16 • 16. Только для этого описания показано восемь портов из 16. Каждый порт 30 соединен с арбитражной шиной 50 портов, управляющей шиной 52 портов и линиями передачи данных (такими как линии 54 и 55 для портов 30 и 42 соответственно). Каждый из портов соединен через эти линии данных с матричным коммутатором 40 16 • 16. Матричный коммутатор 40 может быть готовым промышленным изделием, таким как ГИГАБИТ Ложик 10C051, который образует соединение точек пересечения между портами (за исключением логики 600 и фиксаторов адресов 602, фиг. 4).

В предпочтительном варианте реализации каждый порт производит оптико-электрическое преобразование, чтобы информация передавалась электрически между портами через матрицу 40 16 • 16. Первоначально порт, такой как 30, может попытаться соединиться с другим портом, таким как порт 32. Сначала порт 30 запросит арбитраж, т.е. порт 30 запросит предоставления арбитражной шины через арбитр шины 38. После получения разрешения посылается запрос о соединении по управляющей шине 52 на порт 32. Затем происходит прием состояния. На фиг. 2 приведен пример, когда порт 32 пытается установить контакт с портом 30 путем передачи запроса, символически обозначенного стрелкой 58. Порт 30 посылает сигнал занято, обозначенный символически пунктирной стрелкой 56, обратно на порт 32, отклоняя переданный запрос. Следует отметить, что во время этой первоначальной попытки соединения порта-с-портом матрица 16 • 16 не была доступна. Это возможно благодаря наличию управления средством коммутатора, распределенного между портами. Иначе говоря, только после получения подтверждения, что передача данных может иметь место, коммутатор 40 привлекается к образованию соединения между портами.

Матричный коммутатор 40 соединен с управляющей шиной 52. Это может возбуждать матричный коммутатор 40 для ответа на команды, направленные ему. В предпочтительном варианте реализации только команды, которые направлены матричному коммутатору 40, являются командами диагностического характера. Во время нормального функционирования матричный коммутатор 40 просто контролирует управляющую шину 52 и управление связью между портами, чтобы определять когда соединения должны быть произведены или прекращены. Когда соединения произведены, линии, такие как 54, соединяются с линиями, такими как 55, для возможности передачи данных между портами, такими как порт 30 и порт 42, без запроса явных команд для коммутатора от портов или другого управляющего устройства.

Операция разъединения производится матричным коммутатором 40 без команды со стороны портов. Матричный коммутатор 40 производит перехват сообщений по командной (управляющей) шине 52, чтобы определить, когда разъединение должно быть произведено, путем анализа команд о разъединении на управляющей шине 52. Когда фрейм об окончании связи послан от одной системы другой, матричный коммутатор 40 путем контроля управляющей шины 52 автоматически определяет, какое соединение должно быть разъединено, тем самым экономя время в том, что не запрашивается отдельный протокол команды, чтобы сказать матричному коммутатору произвести разъединение. Это является важным, потому что операция разъединения происходит на базе высокого приоритета, и дальнейшее соединение с любым из портов может иметь место только в случае, когда происходит такое разъединение.

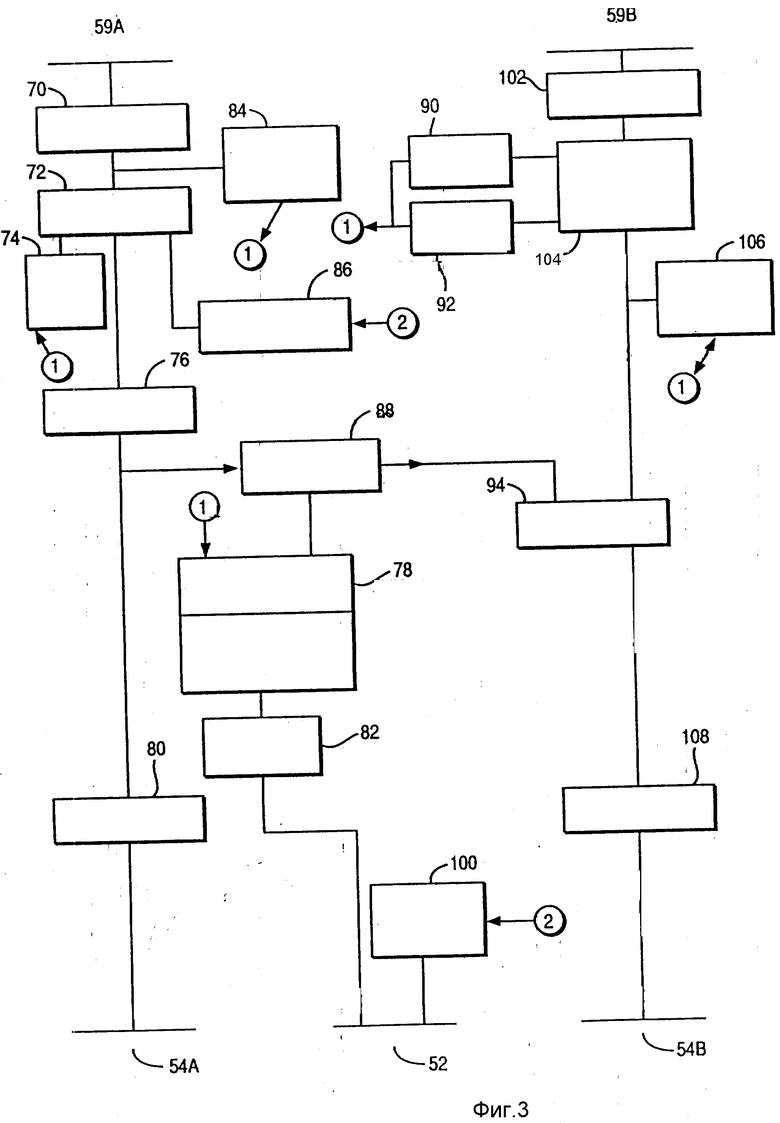

На фиг. 3 представлена блок-схема логики, содержащейся в каждом порте, таком как порт 30. Главная машина управления состоянием и машина состояния соединить/занято 78 управляют функционированием логики порта. Логика состояния 78 соединена с прерывающим управляющим устройством 82, которое производит прерывания в случае условий ошибки и от управляющей шины 52. Логика состояния 78 далее соединена с логикой 88 квитирования установления связи. Функционирование логики квитирования установления связи является типом, который описан в "Бюллетене технических решений IBM" (т. 32, N 6, ноябрь, 1989, с. 21 - 22) в работе "Способ оценки динамических трасс данных в коммутационном блоке данных", включенный здесь в качестве прототипа. Когда фрейм сначала принят от системы, он принимается по шине 598, где первоначально фиксируется символ в момент времени в принимающем регистре 102. Содержание этого регистра затем загружается в буфер 104 соединения/синхронизации, где логика управления записью или логика управления считыванием 90 и 92 соответственно вместе с логикой состояния 78 определяют будет ли буфер 104 функционировать как пропускающий буфер по типу первый входящий/первый выходящий элемент информации или как накапливающий буфер. Управление записью 92 определяет, где в буфере 104 данные должны быть записаны. Логика управления считыванием 90 определяет, с какого места в буфере 104 должен считываться следующий символ. Логика декодирования и детектирования ошибки 106 также соединена с логикой состояния 78, чтобы обозначать условия ошибки. Если фрейм должен быть передан на другой порт, запрос о соединении передается по управляющей шине. Как сказано ранее, арбитр посылает запрос арбитру шины 38 по шине 50 через интерфейс 100 арбитражной и управляющей шин. После получения разрешения машины состояния порта 78 посылает запрос о соединении и оценивает состояние, принятое по управляющей шине 52 от порта, подлежащего соединению. Если порт, который должен быть соединен, не занят, тогда соединение устанавливается автоматически матрицей 40, и данные из буфера 104 соединения/синхронизации пропускаются через регистр 108 по линии данных 54B на матричный коммутатор. Принимающий мультиплексор 94 определяет, должны ли быть загружены данные из канала связи 59B или логики квитирования установления связи 88 в регистр 108. Аналогичным образом данные, принимаемые от матричного коммутатора по линии 54A, проходят через регистр 80 через совмещенную логическую схему 76, который (регистр) предотвращает проход кодовых ошибок блока через передающий мультиплексор 72 на передающий регистр 70 по шине 59A. Следует отметить, что в передающей стороне логика 74 занятости и отклонения, а также логика 84 декодирования и детектирования ошибки предусмотрены для условий ошибки. Логика 74 занятости/отклонения определяет, когда принята индикация о занятости от управляющей шины 52, и образует фрейм занятости по линии 59A. Буфер 86 фрейма предназначен передавать ранее указанные фреймы, указывающие специфические условия ошибки.

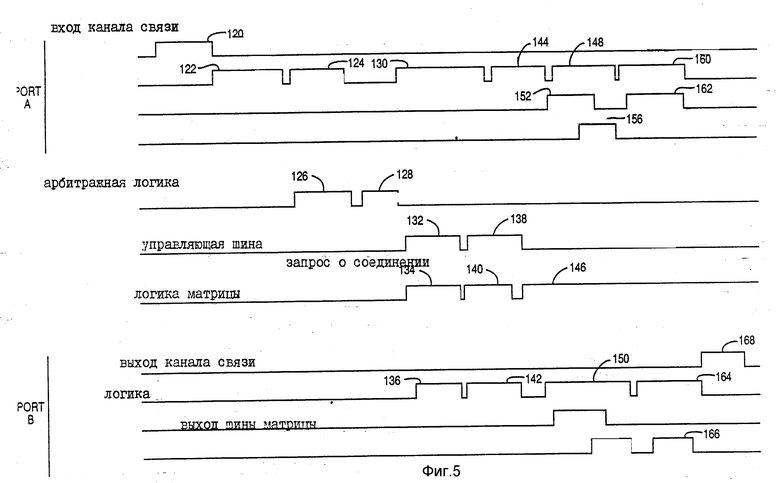

На фиг. 5 представлена схема событий, показывающая соединение между портом A и портом B. На фиг. 5 фрейм сначала принимается портом по шине (такой как 59B) в событии 120. В событии 122 логика порта изучает фрейм и определяет установленные соединения и в событии 124 решает конфликт в отношении управляющей шины. Арбитр 38 шины принимает запрос в событии 126 и разрешает (представляет) запрос в событии 128. В этом время логика порта A посылает запрос о соединении 130, который включает в себя соответствующие адреса портов, по управляющей шине 52, обозначенный под событием 132. Логика матрицы 600 (фиг. 4) следит за этим запросом в событии 134 и фиксирует адреса портов, которые фиксированы в фиксаторах 602, тогда как логика порта B анализирует этот запрос в событии 136. Логика порта B затем посылает ответ 142, который рассматривается логикой матрицы 600 в событии 140 по управляющей шине 52, как показано под событием 138. Этот ответ считывается логикой порта A в событии 133. В этом примере производится последовательное соединение. Поэтому логика матрицы 600 загружает адрес порта из фиксатора 602 в регистры, такие как 614 и 624, чтобы дать возможность схемам выборки данных 608 и 620 соединить внутреннюю шину 606 с внутренней шиной 622. Логика порта A тогда образует сигналы квитирования установления связи с портом B по шине матрицы, такой как 54A и 54B. Сначала происходят события 152 и 154 передачи квитирования установления связи из обоих портов и затем из обоих портов квитирование установления связи в событиях 156 и 158 передается обратно противолежащим портам. При этом следует отметить, что логика матрицы автоматически соединяет порты A и B через матричный коммутатор 40. В конечном счете фрейм посылается в событии 160 по шине матрицы в событии 162 к матрице в линии к порту B в событии 166, где логика порта анализирует фрейм в событии 164. Этот фрейм затем подается на выход линии связи с соединенным устройством в событии 168.

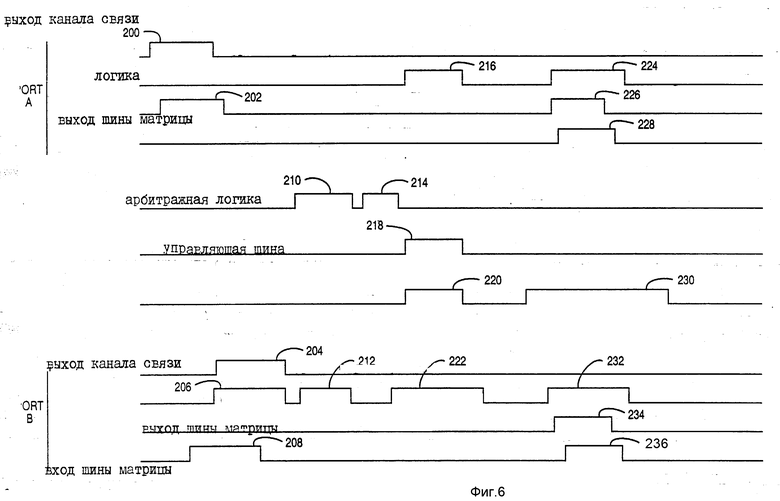

На фиг. 6 представлена схема событий, показывающая операцию разъединения. В этом примере порт A принимает фрейм о разъединении от своего соединенного устройства в событии 200. Это пропускается на выходную шину матрицы в событии 202. Это принимается портом B по входной шине матрицы в событии 208, где логика проверяет фрейм в событии 206, и фрейм распределяется по соединенным устройствам в событии 204. Логика в порте B затем определяет вопрос об арбитраже в отношении управляющей шины в событии 212 и принимается арбитром шины 38 в событии 210, что разрешает подать запрос в событии 214. Логика порта B затем посылает команду о разъединении в событии 222, которая рассматривается на управляющей шине в событии 218, посредством логики матрицы в событии 220 и логикой порта A в событии 216. Затем квитирование установления связи подается через управляющую шину в событиях 232 и 224 портами B и A соответственно через входную и выходную линии матрицы для соответствующих портов в событиях 226, 228, 234 и 236 соответственно. Важное событие состоит в том, что когда логика матрицы 40 автоматически отсоединяет порты A и B в событии 230 путем перехвата на управляющей шине и анализа команды о разъединении, затем посланную, специалистам в этой области техники должно быть понятно, что путем перехвата на шине с целью анализа команды о соединении и команды о разъединении дальнейших циклов шин не требуется для управления коммутатором, даже если коммутатор работает с тем, чтобы поддерживать автономные отношения между портами.

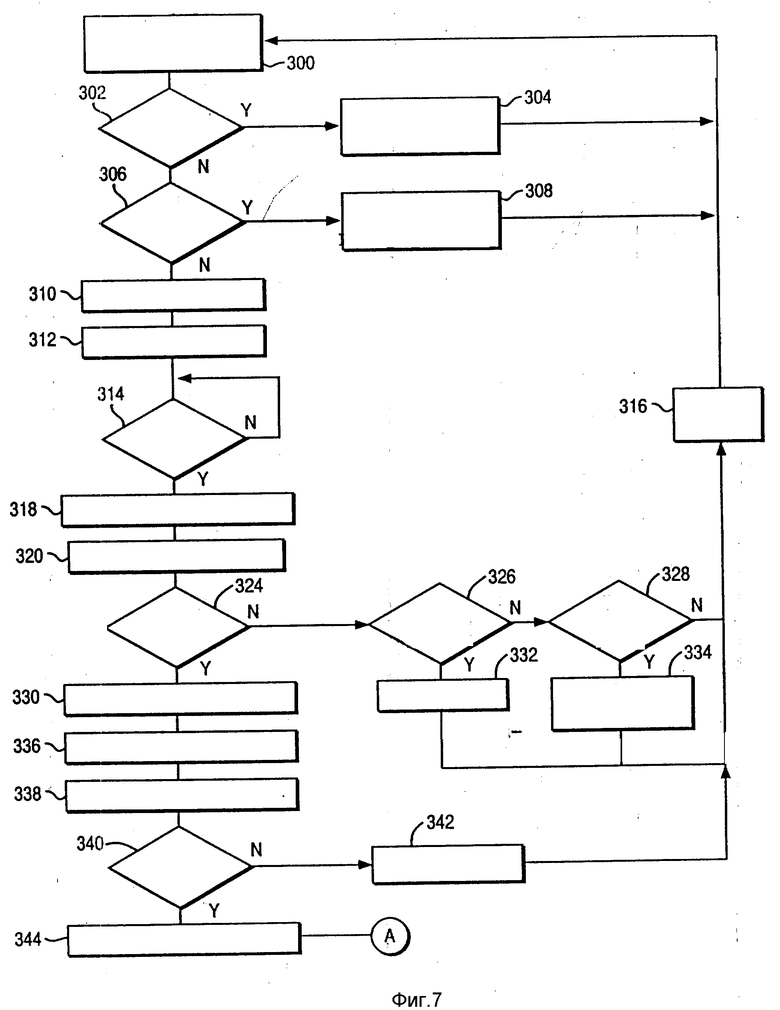

На фиг. 7 представлена блок-схема порядка действий, показывающая логику состояния порта 78, когда она принимает фрейм. В блоке 300 фрейм принимается от устройства, соединенного со стороной линии связи порта. Логика сначала определяет, относится ли фрейм к существующему соединению. Это относится к случаю, когда прежний фрейм установил соединение, и этот существующий фрейм просто является одним из фреймов в последовательности фреймов, который пропускается через существующее соединение. На стадии 304 фрейм пропускается через существующее соединение по шине матрицы на матричный коммутатор. Управляющая логика затем возвращается к стадии 300 для ожидания следующего фрейма. Однако на стадии 302 соединение не было ранее установлено, управляющая логика определяет, заполнен ли буфер 104. Если да, фрейм игнорируется на стадии 308, и управляющая логика возвращается на стадию ожидания следующего фрейма. Если буфер фреймов не был заполнен полностью, фрейм помещается в буфер на стадии 310, и управляющая логика решает конфликт в отношении управляющей шины на стадии 312. На стадии 314 логика ждет получения разрешения. В это время она приступает к выдаче запроса о соединении на стадии 318. На стадии 320 управляющая логика считывает записанный ответ порта. Ответ анализируется на стадии 324 для определения, занят ли он или нет (стадия 326), и в это время подается сообщение о занятости, или если порт сообщает, что у него сбой (стадия 328), посылается сообщение о сбое на стадии 334. Возвращение к стадии 324, если ответ успешный, порт маркируется как соединенный на стадии 330, и передача квитирования установления связи начинается на стадии 336 через матрицу. Когда принимаемое квитирование установления связи принято на стадии 338, оно анализируется на стадии 340. Если оно не в порядке, выдается сообщение об ошибке на стадии 342, и в это время буфер 104 очищается на стадии 316. Возвращение к стадии 340, если квитирование установления связи завершено успешно, фрейм посылается на матричный коммутатор 40 на стадии 324 и логика приступает к узлу A, показанному на фиг. 9 (о чем будет сказано ниже).

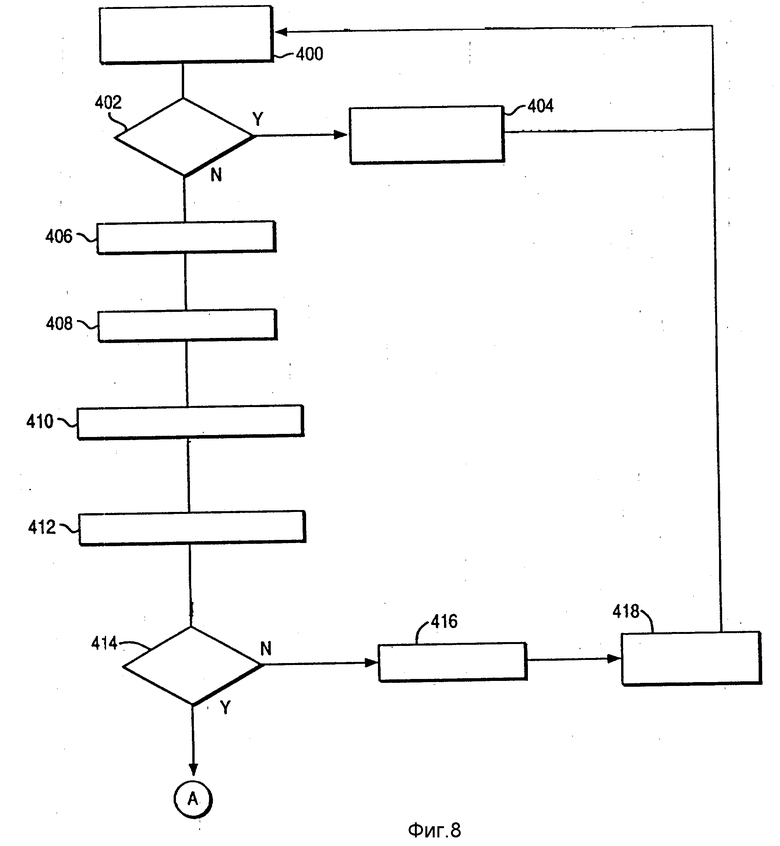

На фиг. 8 блок-схема порядка действий показывает функционирование управляющей логики порта, когда запрос принят от управляющей шины. Это происходит на стадии 400. В это время порт определяет, будет или нет он соединен на стадии 402. Если да, порт отвечает на стадии 404 сигналом "Занято", если нет, на стадии 406 порт отвечает, что он может произвести соединение. На стадии 408 порт запоминает индикацию, что он соединен, и на стадии 410 производит квитирование установления связи. Ответ о квитировании установления связи принимается на стадии 412 и анализируется на стадии 414, чтобы определить, в порядке ли оно. Если нет, тогда на стадии 416 посылается сообщение об ошибке и порт маркирует себя как отсоединенный на стадии 418, возвращаясь к стадии 400. Если, однако, на стадии 414 ответ о квитировании установления связи в порядке, тогда управляющая логика приступает к узлу A.

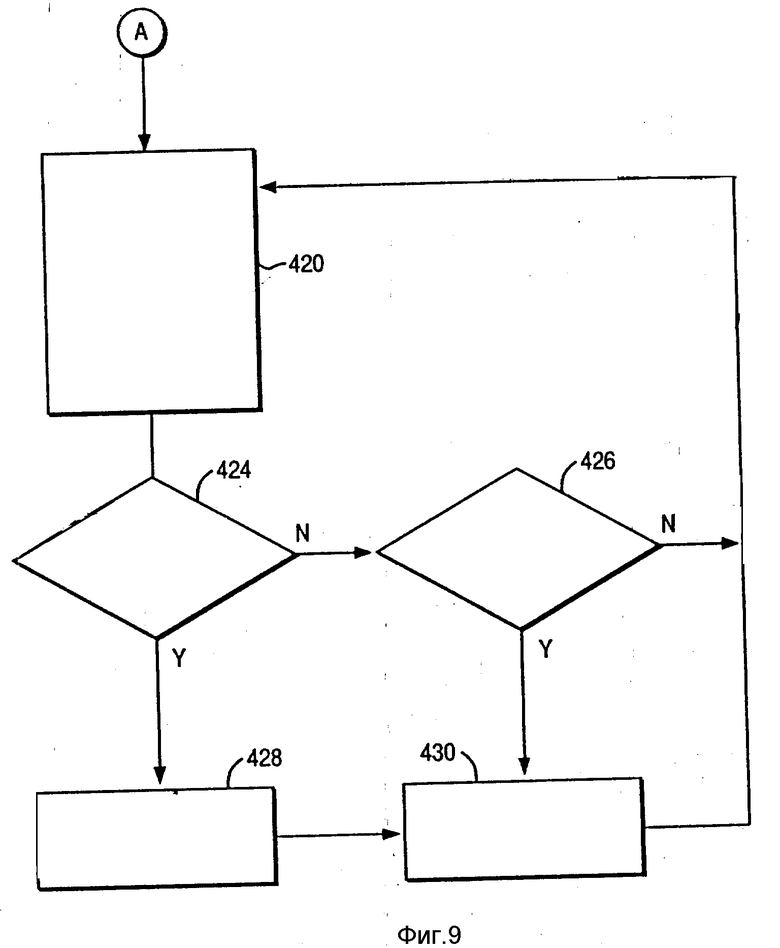

Узел A на фиг. 9 показан как соединяющий логику на фиг. 5 - 7 с каналом связи. Фреймы могут также посылаться от канала связи на матрицу, если это необходимо. На стадии 424 логика порта определяет, принят ли фрейм о разъединении от матричного коммутатора. Если нет, тогда логика порта определяет на стадии 426, принята ли команда о разъединении от управляющей шины. Если нет, тогда логика порта возвращается к стадии 420, чтобы продолжать посылать фреймы. Возвращение к стадии 424, если фрейм о разъединении был получен через матричный коммутатор, и затем на стадии 428 происходит выдача команды о разъединении по управляющей шине. Порт затем маркируется как отсоединенный на стадии 430. Аналогичным образом на стадии 426, если команда об отсоединении принята от управляющей шины, порт маркируется отсоединенным на стадии 430.

На фиг. 10 блок-схема порядка действий показывает управляющую логику матричного коммутатора 40. При этом следует отметить, что матричный коммутатор 40 является исполнительным устройством, которое перехватывает по управляющей шине и управляет соответственно соединениями коммутатора. На стадии 500 управляющая логика коммутатора определяет, послана ли команда по управляющей шине. Если нет, то она продолжает ждать. Если команда есть, тогда адреса портов фиксируются на стадии 502. На стадии 504 команда анализируется, чтобы определить, является ли это командой о соединении. Если да, на стадии 506 ответ порта контролируется и проверяется. Если ответ в порядке на стадии 508, тогда соединение шины между портами происходит на стадии 504. Аналогичным образом на стадии 510 команда анализируется, чтобы определить, является ли это командой о разъединении, и если да, тогда соединения порта разъединяются на стадии 512.

Специалисту в этой области техники должно быть понятно, что логика перехвата матричного коммутатора может также использоваться для управления иными функциями, чем просто соединение или разъединение устройств. Например, логика перехвата матричного коммутатора может использоваться для определения, когда произошло указанное событие, путем анализа информации, связанной с соединением двух портов, и для контроля операции автономных устройств, таких как предотвращение двух последовательных соединений с одним и тем же портом, или операции разъединения с несоединенным портом.

Хотя это изобретение описано со ссылкой на показанный вариант реализации, это описание не предназначено для толкования в ограниченном смысле. Разные модификации показанного варианта реализации, а также другие варианты реализации изобретения станут очевидны специалистам в этой области техники после ознакомления с предлагаемым.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2111532C1 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2117405C1 |

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| УСТРОЙСТВО ДЛЯ ОПТИМИЗАЦИИ ОРГАНИЗАЦИИ ДОСТУПА К ОБЩЕЙ ШИНЕ ВО ВРЕМЯ ПЕРЕДАЧИ ДАННЫХ С ПРЯМЫМ ДОСТУПОМ К ПАМЯТИ | 1991 |

|

RU2110838C1 |

| СИСТЕМА ОБРАБОТКИ И СПОСОБ ЕЕ ФУНКЦИОНИРОВАНИЯ | 1994 |

|

RU2150738C1 |

| СПОСОБ ПЕРЕДАЧИ ДАННЫХ ОТ ИСТОЧНИКА К ОДНОМУ ИЛИ НЕСКОЛЬКИМ ПРИЕМНИКАМ И СИСТЕМА ИЗОБРАЖЕНИЯ ДАННЫХ | 1992 |

|

RU2120138C1 |

| ПЛАТА РАСШИРЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1990 |

|

RU2009539C1 |

| СПОСОБ ФУНКЦИОНИРОВАНИЯ СИСТЕМЫ ОБРАБОТКИ | 1994 |

|

RU2142157C1 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ ЗАПРОСОВ НА ДОСТУП К ШИНЕ | 1990 |

|

RU2067314C1 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2068578C1 |

Изобретение относится к вычислительной технике и предназначено для образования коммуникационной линии связи между двумя устройствами. Система связи содержит первый порт, который соединен по крайней мере с одним устройством. Второй порт соединен со вторым устройством. Два порта соединяются через коммутатор, который содержит средство для контроля связи между устройствами и для определения, когда должно быть произведено изменение в линии связи. 4 з. п. ф-лы, 10 ил.

Авторы

Даты

1998-05-10—Публикация

1991-12-17—Подача