Изобретение относится к вычислительной технике и может быть использовано для динамического перераспределения и преобразования адресов памяти при организации вычислительного процесса, для управления блоком памяти при проведении диагностики и реконфигурации структуры в случае возникновения отказов отдельных сегментов.

Данное устройство может быть использовано при построении высоконадежных вычислительных машин, а также полупроводниковых систем памяти - аналогов дисковым накопителям.

Известно устройство памяти [1], в котором выделены отдельные сегменты. Каждый сегмент имеет программируемую схему управления, посредством которой осуществляется доступ в сегмент и работа сегментов в составе блока памяти.

Наиболее близким техническим решением является устройство перераспределения адресов памяти [2], в котором для выбора различных вариантов адресации используется ППЗУ и энергонезависимое ЗУПВ. Старшие разряды адреса интерпретируются ПЗУ и в зависимости от режима адресации выбирается конкретный вариант (определяется физическая область адресов).

К недостаткам данных устройств можно отнести большую сложность и слабую гибкость управления адресным пространством.

Сущность изобретения состоит в том, что память разделяется на сегменты и старшие разряды адреса дешифруются посредством блока дешифрации выборки сегментов памяти.

Блок дешифрации выборки сегментов памяти содержит N узлов выборки сегментов памяти, каждый узел имеет регистр сдвига, и сумматор по mod 2 и элемент И. Данное устройство формирует сигнал выборки для 2n сегментов памяти, таким образом число дешифруемых старших разрядов адреса равно n. Общее число сегментов может быть произвольным, но от числа сегментов зависят надежностные и функциональные возможности блока памяти в целом. Шина адресов данных и вход Запись/Чтение соединены параллельно со всеми сегментами блока памяти.

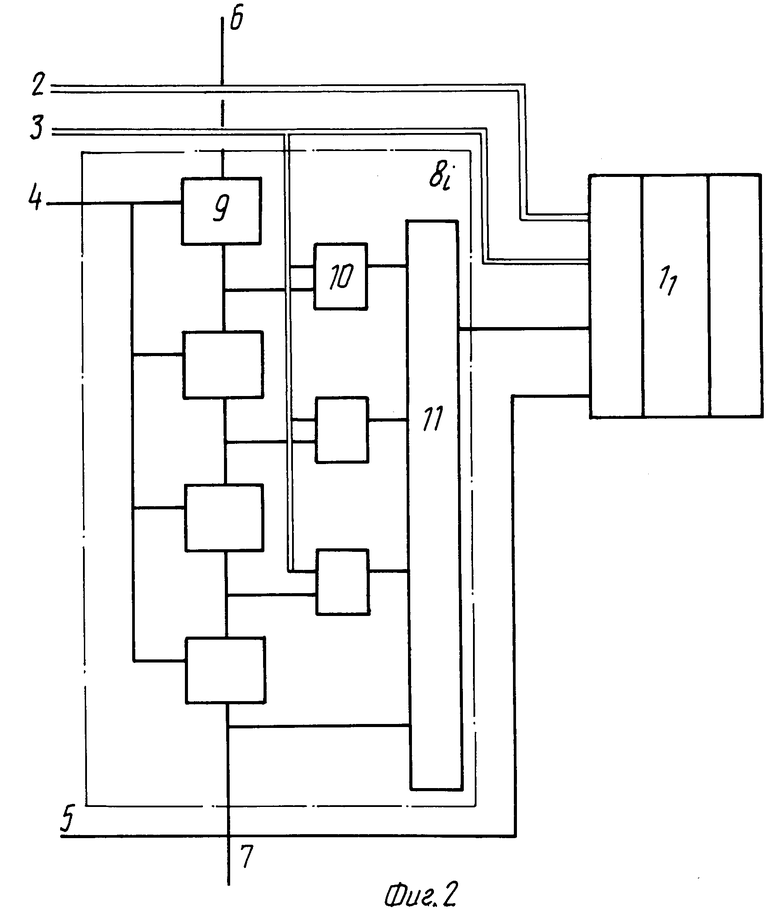

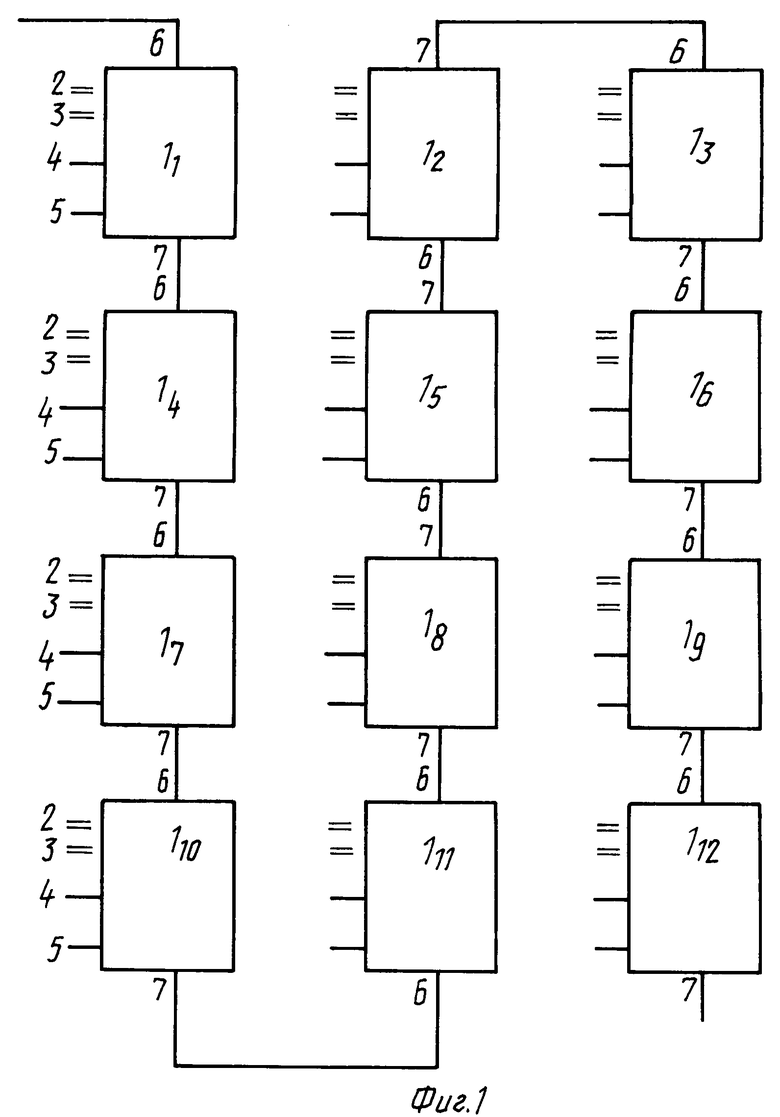

На фиг. 1 представлена структурная схема блока памяти, разделенного для примера на 12 сегментов; на фиг. 2 представлена функциональная схема сегмента памяти с соответствующей схемой дешифрации трех старших разрядов адреса.

На фиг. 1 обозначения: 1 -/i = 1, 12/ - сегменты памяти 2 - шина данных, 3 - шина адреса, 4 - вход синхронизации регистра сдвига, 5 - вход управления Запись/Чтения, 6 - информационный вход регистра сдвига, 7 - выход регистра сдвига.

На фиг. 2 обозначены: 1j, - j-ый сегмент памяти, 2 - 7 шины и входы в соответствии с обозначением на фиг.1; 8 - блок дешифрации выборки сегмента памяти, 81 - узел выборки сегментов памяти, 9 - триггеры регистра сдвига, 10 - сумматоры по модулю 2 и 11 - элемент И.

Три старших разряда адреса поступают на первый, второй и третий сумматоры по mod 2. На вторые входы этих сумматоров поступают код настройки с регистра. Четвертый разряд регистра определяет: 0 - резервное, 1 - рабочее состояние каждого из сегментов. Очевидно, что коды настроек "рабочих" сегментов - 23. Для резервных сегментов код настройки первых трех разрядов не имеет значения.

Работа предлагаемого блока памяти отличается от работы блока памяти традиционной структуры тем, что предварительно устанавливается код настройки блока дешифрации выборки сегментов памяти.

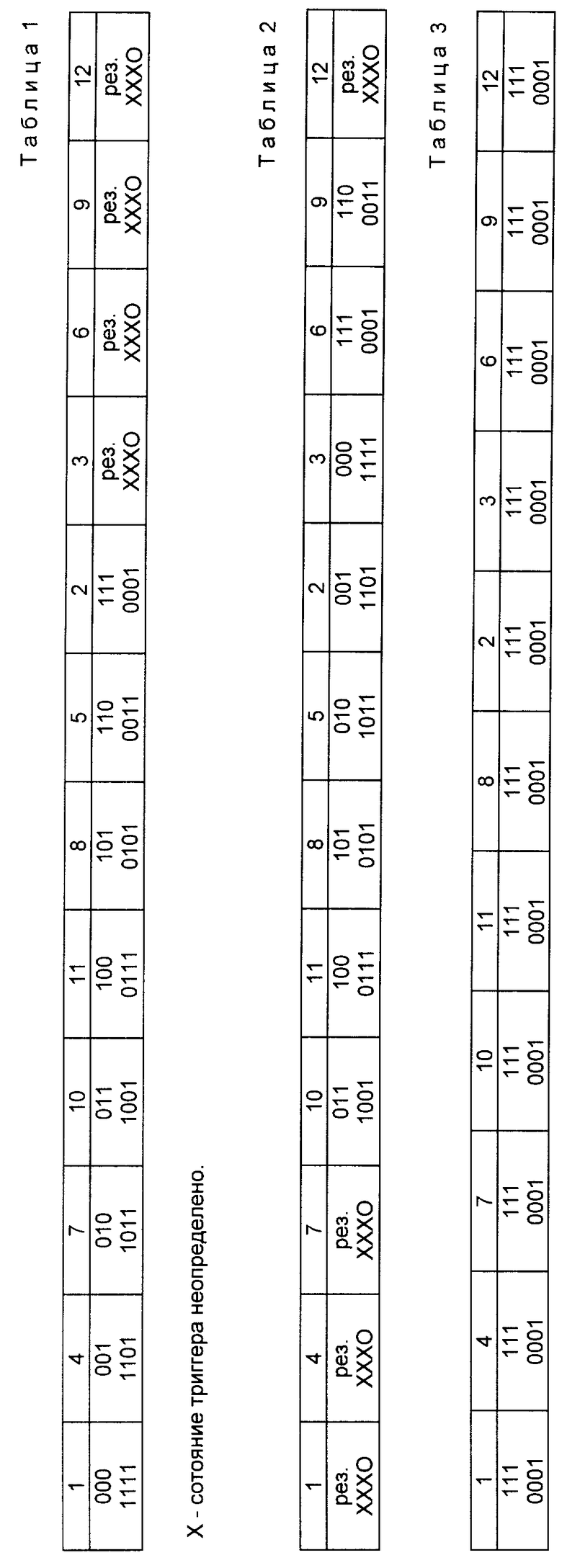

Пример 1.

Пусть необходимо установить сегменты 1, 2, 4, 5, 7, 8, 10, 11 в "рабочее", а сегменты 3, 6, 9, 12 - в резервное состояние. Причем возрастание номеров адреса "рабочих" сегментов задать в следующей последовательности: 1, 4, 7, 10, 11, 8, 5, 2.

На информационный вход в контроллере формируется код настройки 12 • 4 = 48 разрядов.

Пронумеруем разряды регистра сдвига в следующей очередности: 1, 4, 7, 10, 11, 8, 5, 2, 3, 6, 9, 12. Исходя из логики mod 2, настройка первых восьми сегментов будет соответствовать обратному коду номера от 0 до 7. Каждый четвертый разряд определяет рабочее/резервное состояние сегмента.

Код настройки приведен в табл. 1.

(1 - строка : номер сегмента; 2 - строка : три старших разряда исходного адреса; 3 - строка: код настройки).

Пример 2.

Пусть необходимо установить сегменты 2, 3, 5, 6, 8, 9, 10, 11 в "рабочее" а сегменты 1, 4, 7, 12 - в резервное состояние. Причем возрастание номеров адреса "рабочих" сегментов задать в следующей последовательности: 3, 2, 5, 10, 11, 8, 9, 6. Код настройки приведен в табл.2.

Пример 3.

Пусть необходимо обратиться одновременно ко всем сегментам (группе сегментов). Такие ситуации возможны при тестировании памяти, создании копий. Сегменты, к которым выполняется одновременное обращение, должны иметь одинаковые коды настроек. Так, если одновременно обращаться ко всем ячейкам с использованием исходного адреса с 111 в старших разрядах, тогда получим следующий код настройки (см. табл. 3).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 1993 |

|

RU2049350C1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство цифровой фильтрации | 1987 |

|

SU1446627A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ДВУХ МАТРИЦ | 1993 |

|

RU2049352C1 |

| Устройство для перемножения матриц | 1990 |

|

SU1734104A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ТРЕХ МАТРИЦ И ВЫЧИСЛЕНИЯ ДВУМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1993 |

|

RU2066878C1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1571599A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

Изобретение относится к вычислительной технике и может быть использовано для динамического перераспределения и преобразования адресов памяти при организации вычислительного процесса, для управления блоком памяти при проведении диагностики и реконфигурирования структуры в случае возникновения отказов отдельных сегментов. Данное устройство может быть использовано при построении высоконадежных вычислительных машин, а также полупроводниковых систем памяти - аналогов дисковым накопителям. Целью изобретения является создание устройства, обладающего гибким управлением адресным пространством. Поставленная цель достигается тем, что устройство содержит N сегментов памяти и блок дешифрации выборки сегментов памяти, который содержит N узлов выборки сегментов памяти. 3 табл., 2 ил.

Устройство динамического изменения адресов памяти, содержащее N сегментов памяти и блок дешифрации выборки сегментов памяти, причем вход устройства содержит группу старших и младших разрядов, группа младших разрядов адресного входа устройства соединена соответственно с разрядами адресного входа всех сегментов памяти, информационный и управляющий входы устройства соединены соответственно с информационным и управляющим входами всех сегментов памяти, группа старших разрядов адресного входа устройства соединена соответственно с разрядами адресного входа блока дешифрации выборки сегментов памяти, отличающееся тем, что блок дешифратора выборки сегментов памяти содержит N узлов выборки сегментов памяти, причем информационный вход блока дешифрации выборки сегментов памяти соединен с информационным входом первого узла выборки сегментов памяти, выход j-го узла выборки сегментов памяти (где j = 1, N - 1) соединен с информационным входом (j + 1)-го узла выборки сегментов, вход синхронизации, блок дешифрации сегментов выборки соединен с входом синхронизации всех узлов выборки сегментов памяти, выход выборки сегмента j-го узла выборки сегментов памяти является j-м выходом выборки сегмента блока дешифрации выборки сегментов памяти, каждый узел выборки сегментов памяти содержит регистр сдвига, n сумматоров по mod 2 (где n - число старших разрядов адресного входа) и элемент И, причем в самом узле выборки сегментов памяти i-й выход (где i = 1, n), выход регистра соединены соответственно с первым входом i-го сумматора по mod 2, второй вход которого соединен с i-м разрядом адресного входа узла, выход i-го сумматора по mod 2 соединен с i-м входом элемента И, (n + 1)-й вход которого соединен с выходом сдвига регистра сдвига, выход элемента И является выходом выборки сегмента узла, информационный вход и вход синхронизации регистра сдвига соединены соответственно с информационным входом и входом синхронизации узла.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника, N 1, 1990 | |||

| - М.: Мир, с | |||

| Термосно-паровая кухня | 1921 |

|

SU72A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электроника, N 5, 19 83, - М.: Мир, с | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

Авторы

Даты

1998-07-10—Публикация

1993-05-14—Подача