Изобретение относится к вычислительной технике и может быть использовано для организации многовходовой многоблочной памяти при построении многопроцессорных вычислительных систем на базе мини- и микроЭВМ.

Цель изобретения - расширение функциональных возможностей за счет обеспечения ВОЗМОЖНОСТИ ЗаПИСИ ОДНОГО

слова данных одновременно в N блоков памяти и выполнения при считывании логической операции ИЛИ над данными по любому адресу в каждом из N блоков памяти, повышение быстродействия за счет асинхронного обмена с памятью и повышение надежности системы путем выработки сигнала ошибки при обращении к несуществующей ячейке -блока памяти.

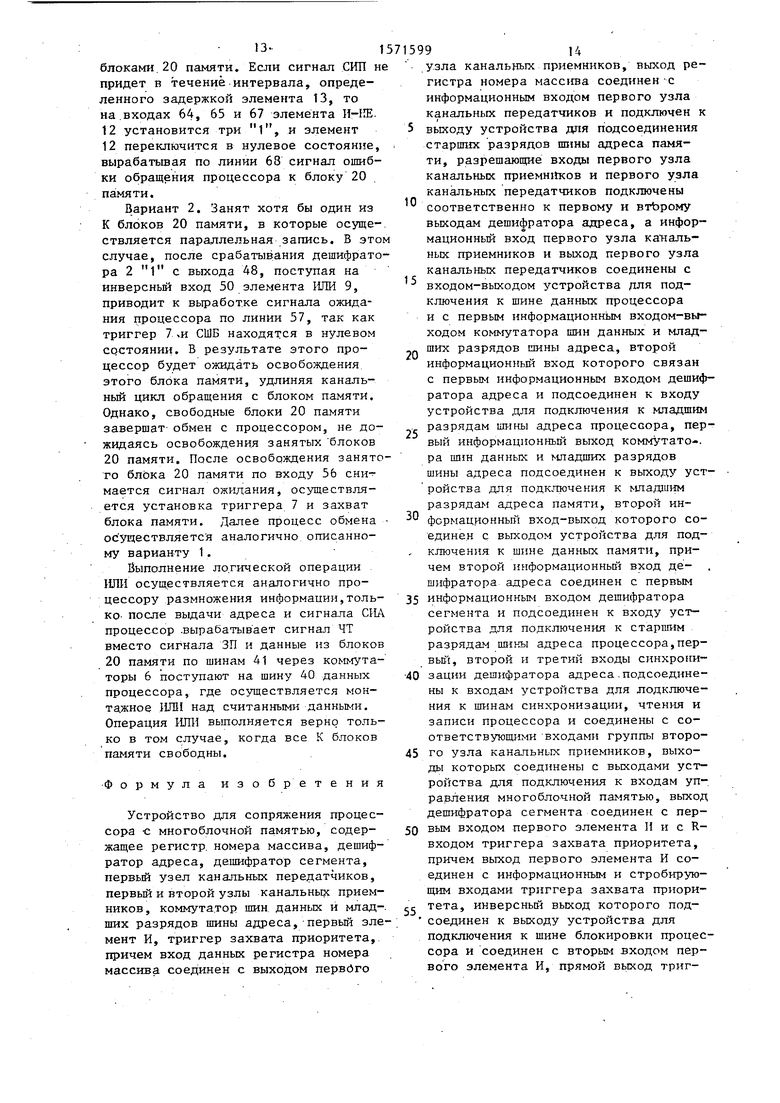

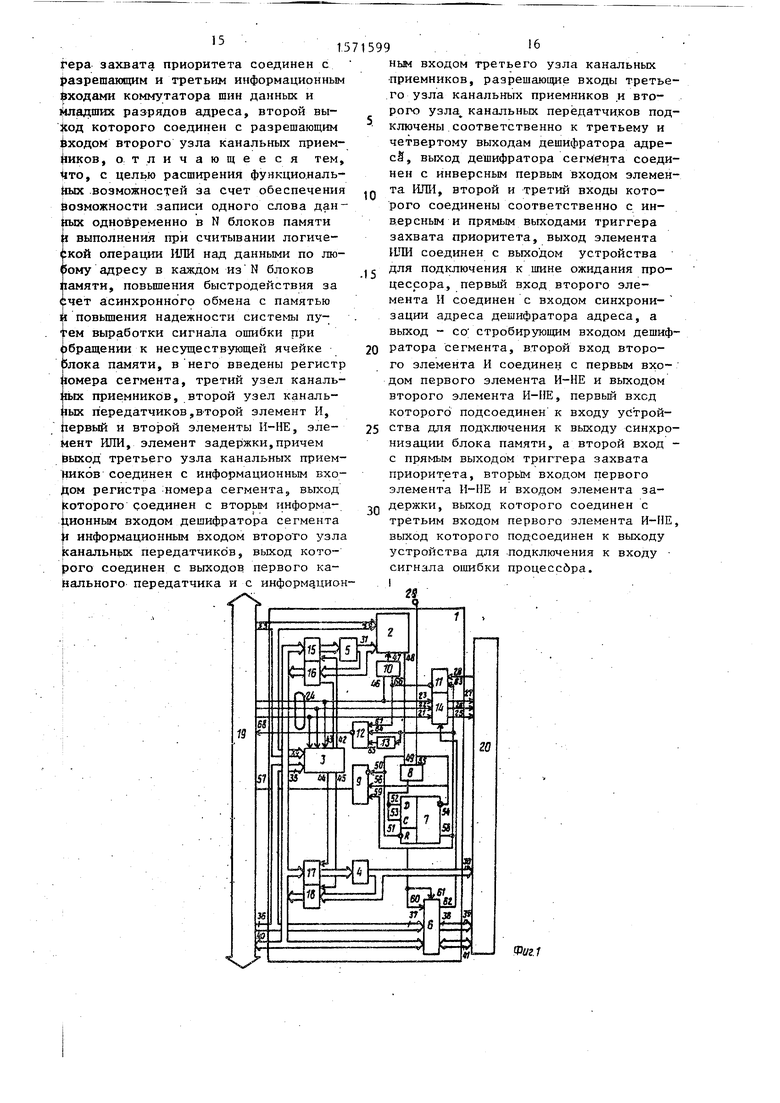

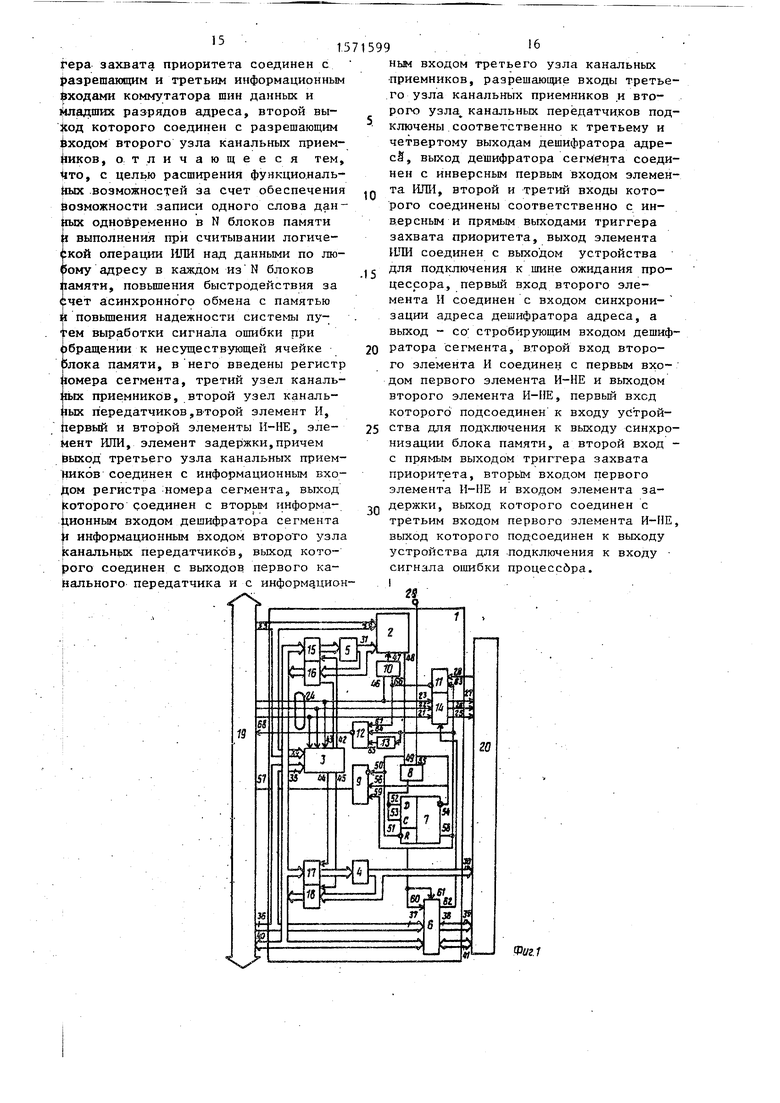

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 - структурная схема устройства многовходовой многоблочной памяти систе- . мы.

Устройство 1 содержит дешифратор 2 сегмента, дешифратор 3 адреса, регистр 4 номера массива, регистр 5 номера сегмента, коммутатор 6 шин данных и младших разрядов шины адреса, триггер 7 захвата приоритета, элемент И 8, элемент ИЛИ У, элемент И 10, элемент И-НЕ 11, элемент И-НЕ 12. Элемент 13 задержки узел 14 канальных приемников, узлы 15-18 канальных приемников и передатчиков связи с процессором , ка- нал 19 процессора, блок 20 памяти, линию 21 сигнала Запись (ЗП)5 линию 22 сигнала Чтение (ЧТ) и линию 23 сигнала Синхронизация адреса (СИА), группы управляющих входов 24 и соответствующие им линии 25-27 группы выходов сигналов обращения к блоку 20 памяти, линию 28 сигнала . подтверждения обмена (СИП) с блоком 20 памяти, линию 29 системной шины блокировки (СШБ), причем, в,ход регистра 4 номера массива соединен с выходом узла 17 канальных приемников, а выходы - со старшими разрядами шины 30 адреса блока 20 памяти и с информационными входами узла 18 канальных передатчиков, входы регистра 5 номера сегмента соединены с выходами узла 15 канальных приемни

ков, а выходы - с информационными входами узла 16 канальных передатчиков и с входами 31 дешифратора 2 сегмента,

0

5

Q

0

5

0

5

0

5

входы 32 которого соединены со старшими разрядами шины 33 адреса процессора и информационными входами 34 дешифратора 3 адреса, входы 35 которого соединены с младшими разрядами шины 36 адреса процессора и входами 37 коммутатора 6, выходы 38 которого соединены с младшими разрядами шины 39 адреса блока 20 памяти, информационные входы узлов 15 и 17 канальных приемников и выходы узлов 16 и 18 канальных передатчиков соединены с двунаправленной шиной 40 данных процессора и с первыми входами-выходами коммутатора 6, вторые входы-выходы которого соединены с двунаправленной шиной 41 данных блока 20 памяти, линии 21-23 соединены с управляющими входами дешифратора 3 адреса, выходы 42-45 которо го соединены - соответственно с разрешающими входами узлов 15-18 канальных приемников и передатчиков, линия 23 СИА соединена с входом 46 элемента И 10, выход которого соединен с управляющим входом 47 дешифратора 2 сегмента, выход 48 которого соединен с входом 49 элемента 2И 8, инверсным входом 50 элемента ИЛИ 9 и инверсным входом 51 установки в нуль триггера 7 захвата приоритета, выход элемента И 8 соединен с информационным 52 и стробичующим 53 входами триггера 7 захвата приоритета, инверсный выход 54 котор-ого соединен с линией 29 СШБ, входом 55 элемента И 8 и входом 56 элемента ИЛИ 9, выход которого соединен с входом 57 ожидания процессора, прямой выход 58 триггера 7 захвата приоритета соединен с входом 59 элемента ИЛИ-.9 и с информационным 60 и разрешающим 61 входами коммутатора 6, информационный выход 62 которого соединен с разрешающим входом узла 14 канальных приемопередатчиков, кроме того,выход 58 триггера 7 захвата приоритета соединен с входом 63 элемента И-lffi 11, входом 64 элемента И-НЕ 12 и входом элемента 13, адержки, выход которого соединен с входом 65 элемента И-НЕ 12, выход элемента И-НЕ 11 соединен с входом 66 элемента И 10 и входом 67 элемента И-НЕ 12, выход которого соединен с линией 68 сигнала ошибки прог цессора.

Устройство работает следующим образом.

51

Адресное пространство процессора разбивается на сегменты. Каждому сегменту ставится в соответствие бло 20 памяти требуемого блока. В каждом конкретном случае сегменты могут

иметь переменный размер. Блок 20 памяти состоит из стандартных одновхо- довых модулей памяти, выходы которых запараллелены и образуют выходы 69 блока 20 памяти. Объем каждого блока 20 памяти разбит на равные по объему части - банки 70 памяти, причем объе банка 70.памяти равен объему сегмента памяти.Местоположение сегмента в адресном пространстве процессора определяется содержимым регистра 5 номера сегмента.Сегмент памяти,таким образом занимает часть адресного пространства, через которую процессор имеет доступ к равному по объему массиву блока 20 памяти, номер которого определяется значением регистра 4 номера массива. Процессор соединен с блоками 20 памяти через специальные устройства 1 сопряжения, функцией ко- торых является анализ захвата блока 20 памяти другим процессором, если нет, то захват свободного блока 20 памяти и выдача на системную шину блокировки сигнала захвата приоритета для других процессоров, подключенных к данному блоку 20 памяти, выдача процессору,обратившемуся к захваченному блоку 20 памяти, сигнала ожидание процессора по линии 57, выдача сигнала ошибки по линии 68 при обращении процессора к несуществующей ячейке блока памяти, коммутация канала 19 процессора с блоками 20 памяти в момент обращения процессора к блоку общей памяти и преобразование адреса, поступающего из процессора. Таким образом, устройство 1 заменяет старшие разряды- адреса памяти, выдаваемого процессором, на содержимое регистра 4 номера массива, значение которого устанавливается- процессором программно. В определенные моменты времени содержимое регистров 4 и 5 в каждом устройстве 1 может быть различным, и процессор получает доступ к, любому набору массивов блоков 20 памяти, но по одному массиву из каждого блока 20,причем номера массивов и местоположение соответствующих им сегментов может быть произвольным и изменяется программно в процессе ре5996

шения задачи. Для подключения процессоров к одному одновходовому блоку памяти входы-выходы 69 устройств

, 1 сопряжения запараллелены н подключены к входам-вькодам блока 20 памяти, причем линии 29 устройств 1 сопряжения соединяются, образуя системную шину блокировки. Обращение

0 процессоров к общему блоку памяти может осуществляться только последовательно, когда один из процессоров захватывает общую память, другие процессоры не имеют к ней доступа. Ес5 ли память свободна, а об этом свидетельствует наличие 1 на линии 29 СШБ, то процессор, обратившись к общей памяти, захватывает наивысший приоритет, и устройство 1 сопряжения устанавливает на линии СШБ уровень О, сообщая тем самым другим процессорам, что память захвачена. Если теперь какой-либо процессор обратится к захваченной памяти, то

25

соответствующее этому процессору устройство 1 вырабатывает сигнал ожидания этого процессора по линии 57 с уровнем О, сообщая тем самым, что необходимо либо повторить обращение

к памяти, либо ожидать освобождения данного блока 20 памяти, удлиняя канальный цикл обращения к памяти. Все зависит от возможностей процессора - если процессор не может удлинять цикл обращения к памяти, то необходимо повторное обращение к памяти.

За счет разделения всей памяти на независимые блоки реализуется мно-

говходовая многоблочная разделенная память. Однако кроме разделенной памяти процессор может иметь память с обычной организацией, но в таком случае регистр 5 номера сегмента

должен настраиваться таким образом, чтобы использовались адреса, не задействованные обычной памятью. Так как процессор имеет по N сегментов, а следовательно и по N блоков памятн, где каждый из блоков памяти является общим для нескольких процессоров, то вероятность того, что в один и тот же момент времени два или более процессора обратятся к одному блоку памяти, зависит от количества

блоков памяти и при большом N является величиной незначительной, Р

Ј 1/мЧ Это значительно повышает эффективность использования общей

памяти и снижает простои процессоров, возникающих вследствие ожидания процессором освобождения захваченного другим процессором блока памяти.

Для размножения информации в К блоках 20 памяти регистры 5 номера .сегмента устройства 1; подключенных к этим К блокам памяти, настраиваются на один и тот же номер сегмента, причем номера массивов могут быть различны. Теперь при записи данных по любому адресу внутри установленного на регистрах 5 номера сегмента информация будет записана во всех К блоках 20 памяти по адресам, определяемым содержимым регистров 4 номера массива. Если же хотя бы один из К блоков 20 памяти занят, то соответствующие этим блокам памяти устройства 1 по линии 57 вырабатывают сигнал ожидания, и процессор ожидает освобожения занятых блоков 20 памяти, удлиняя канальный цикл обращения к памяти. По мере освобожения блоков 20 памяти устройства 1 захватывают освобоженные блоки памяти, устанавливая на линии 29 системной шины блокировки нулевой уровень, и снимают сигнал ожидания с линии 57. Однако, процессор будет ожидать окончания обмена со всеми К блоками 20 памяти, так как выходы элементов ИЛИ 9 всех устройств 1 выполнены по схеме с открытым коллектором и подключены к одной шине 57 ожидания процессора. Реализовано монтажное ИЛИ линий 57 ожидания всех устройств 1 сопряжения, подключенных к данному процессору. После завершения записи данных в свободные или освободившиеся блоки 20 памяти устройство 1 по сигналу подтверждения обмена СИП с блоком памяти освобождает данный блок памяти, устанавливая на СШБ единичный уровень, освобождая блоки памяти, не дожидаясь окончания обмена с другими блоками памяти или завершения обслуживания занятых блоков памяти. Таким образом реализуется асинхронный режим обмена, это также позволяет использовать-блоки памяти с различным быстродействием„ Для выполнения в режиме чтения логической операции ИЛИ над даннымя5хра нящимися в К блоках 20 памяти, регистры 5 номера сегмента также необходимо настроить на один и тот же

5

номер сегмента. Операция ИЛИ осуществляется за счет реализации монтажного ИЛИ шины 40 данных устройства 1, так как входы-выходы 71 всех устройств 1, подключенных к каналу 19 процессора, запараллелены.

Повышение быстродействия при размножении информации в К- блоках 20 памяти или при выполнении операции ИЛИ над.данными, хранящимися в К блоках памяти, составит К раз, если все К блоков были свободны,(K-Q) раз, если было обращение к занятым блокам памяти, где Q - максимальное количество процессоров уже ожидающих освобождения одного из требуемых первому процессору блоков памяти. Вероятность того, что Q 1,мала и определяется

соотношением Р

а

-

25 30

35

40

45

50

55

Использование устройства для параллельной записи информации в К блоках памяти позволяет организовать режим горячего резервирования информации, хранящейся в памяти системы. При отказе или утере информации в одном из блоков памяти информация может быть восстановлена из резервного блока или отказавший блок может быть отключен. Наличие резервных копий информации позволяет осуществлять режим мажорирования. Это значительно повышает надежность всей системы и не приводит к аварийному завершению работы системы. Кроме того, в целях повышения надежности системы используется схема формирования сигнала ошибки при обращении процессора к несуществующей ячейке блока 20 памяти. Схема формирования сигнала ошибки состоит из элементов 11-13., Если после захвата блока 20 памяти и выработки сигнала ЗП или ЧТ блок памят не выработает сигнал СИП в течение промежутка времени, определяемого элементом 13 задержки, что может означать либо обращение процессора к несуществующей ячейке блока памяти, то на выходе элемента И-НЕ 12 появится сигнал ошибки с нулевым уровнем, поступающий в канал 19 процессора по линии 68. Выходы элементов И-НЕ М всех устройств 1 также выполнены по схеме с открытым коллектором и подключены к линии 68 сигнала ошибки процессора.

В момент включения устройства 1 регистры 4 номера маггива и регистры

5 номера сегмента устанавливаются в нулевое состояние, и процессоры че- реа нулевой сегмент памяти имеют доступ к нулевым блокам 20 памяти. Перед началом обмена процессоров с многовходовой многоблочный памятью процессорам необходимо во всех устройствах 1 сопряжения установить на регистрах 4 номера массива номера требуемых массивов блоков 20, а на регистрах 5 номера сегмента - номера сегментов памяти.Для этого процессор выставляет адрес регистра 4 номера массива на шину адреса. Адрес по шинам 33 и 36 поступает на информационные входы соответственно 34 и 35 дешифратора 3 адреса. После этого процессор выдает сигнал (СИЛ) на линию 23, по которому дешифратор 3 дешифрирует адрес, установленный на шинах 33 и 36 адреса и после приема управляющих сигналов ЗП или ЧТ соответственно с линий 21 и 22 выдает единичный сигнал на один из выходов 42-45. Если на дешифратор 3 поступа- ет сигнал ЧТ,тЬ с выхода 45 единичный сигнал поступает на разрешающий вход узла 18, разрешая прохождение информации, записанной на регистре 4 на шину 40 данных процессора. В режиме ЗП процессор после сигнала СИА устанавливает необходимое значение стар старших разрядов номера массива на шину 40 и вырабатывает сигнал ЗП, по которому дешифратор 3 выдает с выхода 44 единичный сигнал на разрешающий вход узла 17, и информация с шины 40 данных процессора записывается в регистр 4. Чтение и запись в ре1 гистр 5 номера сегмента осуществляется аналогичным образом. После устаi

новки номеров массивов памяти на регистрах 4 сегментов на регистрах 5 всех устройств 1 процессов можно обратится к любой ячейке установленных массивов блоков 20 памяти. При этом процессор не ощущает разницы между работой многобяочной памятью и памятью с обычной организацией, так как задержка на устройстве 1 определяется задержкой на дешифраторе 2, элементе И 10, элементе И 8, триггере 7, коммутаторе 6 и на узле 14, которая является незначительной и не нарушает канального цикла обращения процессора к памяти.

Обращение процессора к ячейке блока 10 памяти происходит следующим образом.

0

Процессор подает на шину (33,36) адреса адрес необходимой ячейки памяти и вырабатывает сигнал СНА. Старшие разряды адреса, поступающего с шины 33 адреса, поступают на вход 32 дешифратора 2 сегмента всех устройств 1 сопряжения, подключенных к данному процессору. Сигнал СИА с линии 23 поступает на. вход 46 элемента И 10 всех устройств 1 того- же процессора. Единичный уровень на входе 66 элемента И 10 разр.ешает прохождение сигнала СИА на управляющий

5 47 вход дешифратора 2 сегмента, так как в исходном состоянии триггер 7 захвата приоритета сброшен и сигнал СИП в нулевом состоянии (соответственно входы 63 и 28 элемента

0 И-НЕ 11). С приходом сигнала СИА дешифраторы 2 сегмента сравнивают старшие разряды адреса, поступающего с шины 33 адреса процессора с разрядами регистра 5 номера сегмента, ко5 торые поступают на вход 31 дешифратора 2.

Если старшие разряды адреса совпадают с содержимым регистра 5 номера сегмента, то дешифратор 2 этого

® устройства 1 вырабатывает управляющий единичный сигнал, который с выхода 48 поступает на вход 49 элемента И 8, инверсный вход 50 элемента ИЛИ 9 и на инверсный вход 51 установки в 0|

5 триггера 7 захвата приоритета. Если на линии 29 системной шины блокировки установлен О, т.е. данный блок 20 памяти уже захвачен другим процессором, то этот О, поступая на

С вход 55 элемента И 8, блокирует установку в единичное состояние триггера 7, а также поступает на вход 56 элемента ИЛИ 12. Для нормальной работы устройства 1 необходимо, что5 бы выход 54 триггера 7 захвата приоритета был с открытым коллектором, т.е. при наличии 1 этот выход не Влиял на подключенные к нему входы, а при наличии О, этот уровень под0 держивался на входах 55 и 56 элементов 8 и 9 и на линии 29 СШБ. Так как триггер 7 еще не был установлен в 1, то уровень О с выхода 58 поступает на вход 59 элемента ИЛИ 9,

е сигнал с выхода которого с уровнем О поступает на шину 57 ожидания процессора и сообщает процессору, что для нормального продолжения уже начатого цикла, необходимо дождаться

11 15

завершения этого сигнала. Если же на линии 29 СШБ установлен уровень 1, т.е.. блок 20 памяти свободен в данный момент времени, то уровень 1 с выхода элемента И 8 поступает на информационный 52 и стробирующий 53 входы триггера 7 захвата приоритета, устанавливая его в единичное состоящие. С инверсного выхода 54 триггера 7 уровень О поступает на вход 56 элемента ИЛИ 9 и на линию 29 ШБ, сообщая другим процессорам, подключенным к данному блоку памяти, чт этот блок памяти захвачен. Процессор {захвативший блок памяти, имеет наивысший приоритет при работе с этим |блоком памяти и ни один процессор е может прервать его работу с па- тью. Сигнал ожидания процессора на нии 57 данного устройства 1 не вы- абатывается, так как на вход 59 эле :ента 9 поступает 1 с прямого вы- кода 58 триггера 7, поддерживая на линии 57 уровень 1. Т с выхода 58 триггера 7 поступает на информационный 60 и разрешающий 61 входы Коммутатора 6, коммутируя тем самым шину 40 данных и младшие разряды шины 36 адреса соответственно на шины 41 и 39 выбранного блока-20 памяти. После срабатывания коммутатора 6 сигнал с выхода 62 поступает на разрешающий вход узла 14, разрешая прохождение управляющих сигналов (ЗП, ЧТ, СИА) соответственно линий 21-23 .на одноименные линии 25-27 и далее на управляющие входы блока 20 памяти. После этого процессор устанавливает необходимую информацию на шину 40 данных и подает сигнал ЗП на линию 21. При этом информация, установленная на шине 40 данных и младших разрядах шины 36 адреса, поступает на шины 41 и 39. Сигнал ЗП поступает через узел 14 на линию 25 и далее на входы управления блока 20 памяти. По сигналу ЗП информация, установленная на шине 41 данных,записывается в ячейку блока 20 памяти, адрес которой установлен на шинах 39 и 30. Записанная в регистре 4 номера массива информация указывает на номер массива в блоке 20 памяти, а адрес, поступающий из процессора на младшие разряды шины 39 адреса, указывает адрес ячейки памяти внутри массива блока 20. Аналогично происходит чтение процессором информации из блока 20 памяти, но при

1599

12

этом процессор выдает сигнал ЧТ на лниию 22 и через узел 14 на линию 26 и вход управления блока 20. памяти. После этого блок 20 памяти устанавливает на шину 41 информацию, которую процессор считывает со своей шины 40 данных, вырабатывая сигнал ЧТ, на что блок 20 памяти отвечает сигналом СИП.

Размножение информации осуществляется следующим образом. Возмож-. ны 2 варианта.

Вариант 1. Все К блоков 20 памяти, в которые осуществляется параллельная запись, не заняты. В регистры 5 номера сегмента всех устройств 1, подключенных к требуемым К блокам памяти, записывается один и тот

Q же номер сегмента. Затем процессор выставляет на шинах 36 и 33 адреса адрес в пределах установленного номера сегмента и вырабатывает сигнал СИА. Так как все блоки 20 памяти были

C свободны, то триггеры 7 захвата приоритета всех требуемых устройств 1 устанавливаются в единичное состоя-- ние. 1м с выхода 58 триггера 7 запрещает по входу 59 элемента ИЛИ 9 выработку сигнала ожидания процессора по линии 57 и разрешает работу узла 14 канальных приемников и схемы формирования сигнала ошибки. Процессор устанавливает данные на шину 40 данных и вырабатывает сигнал ЗП по ,

5 линии 21, который поступает на входы 25 требуемых К блоков 20 памяти, и данные, установленные на шине 40 данных, и младшие разряды шины 36 адреса поступают соответственно на ши0 ны 41 и 39 указанных блоков 20 памяти. Старшие разряды адреса внутри блоков памяти могут быть различны и определяются содержимым регистров 4 номера массива. В ответ на сигнал

5 ЗП блок 20 памяти вырабатывает сигнал подтверждения обмена с памятью СИП, который с выхода элемента И-НЕ 11 запрещает по входу 67 элемента ИЛИ-ПЕ 12 выработку сигнала ошибки по линии

0 68 и с помощью элемента И 10 запрещает работу дешифратора 2 сегмента. Выход 48 дешифратора 2 переключает- -ся в нулевое состояние и сбрасывает триггер 7 захвата приоритета. Систем5 ная шина блокировки переходит в единичное состояние, разрешая обращение других процессоров к данному блоку памяти, не дожидаясь завершения операции обмена с оставшимися (К-1)-ми

0

блоками 20 памяти. Если сигнал СИП н придет в течение интервала, определенного задержкой элемента 13, то на входах 64, 65 и 67 элемента И-НЕ 12 установится три 1, и элемент 12 переключится в нулевое состояние, вырабатывая по линии 68 сигнал ошибки обращения процессора к блоку 20 памяти.

Вариант 2. Занят хотя бы один из К блоков 20 памяти, в которые осуществляется параллельная запись. В это случае, после срабатывания дешифратора 2 1 с выхода 48, поступая на инверсньй вход 50 элемента ИЛИ 9, приводит к выработке сигнала ожидания процессора по линии 57, так как триггер 7 ,и СШБ находятся в нулевом состоянии. В результате этого процессор будет ожидать освобождения этого блока памяти, удлиняя канальный цикл обращения с блоком памяти. Однако, свободные блоки 20 памяти завершат обмен с процессором, не дожидаясь освобождения занятых блоков 20 памяти. После освобождения занятого блока 20 памяти по входу 56 снимается сигнал ожидания, осуществляется установка триггера 7 и захват блока памяти. Далее процесс обмена осуществляется аналогично описанному варианту 1.

Выполнение логической операции ПЛИ осуществляется аналогично процессору размножения информации,только после выдачи адреса и сигнала СИА процессор вырабатывает сигнал ЧТ вместо сигнала ЗП и данные из блоков 20 памяти по шинам 41 через коммутаторы 6 поступают на шину 40 данных процессора, где осуществляется монтажное ИЛИ над считанными данными. Операция ИЛИ выполняется верно только в том случае, когда все К блоков памяти свободны.

Формула изобретения

Устройство для сопряжения процессора с многоблочной памятью, содержащее регистр номера массива, дешифратор адреса, дешифратор сегмента, первый узел канальных передатчиков, первый и второй узлы канальных приемников, коммутатор шин данных и младших разрядов шины адреса, первый элемент И, триггер захвата приоритета, причем вход данных регистра номера массива соединен с выходом первого

0

5

0

5

0

0

5

0

5

узла канальных приемников, выход регистра номера массива соединен с информационным входом первого узла канальных передатчиков и подключен к выходу устройства для подсоединения старших разрядов шины адреса памяти, разрешающие входы первого узла канальных приемников и первого узла канальных передатчиков подключены соответственно к первому и второму выходам дешифратора адреса, а информационный вход первого узла канальных приемников и выход первого узла канальных передатчиков соединены с входом-выходом устройства для подключения к шине данных процессора и с первым информационным входом-выходом коммутатора шин данных и младших разрядов шины адреса, второй информационный вход которого связан с первым информационным входом дешифратора адреса и подсоединен к входу устройства для подключения к младшим разрядам шины адреса процессора, первый информационный выход коммутато-. ра шин данных и младших разрядов шины адреса подсоединен к выходу устройства для подключения к младшим разрядам адреса памяти, второй информационный вход-выход которого соединен с выходом устройства для подключения к шине данных памяти, причем второй информационный вход дешифратора адреса соединен с первым 5 информационным входом дешифратора сегмента и подсоединен к входу устройства для подключения к старшим разрядам шикы адреса процессора,первый, второй и третий входы синхронизации дешифратора адреса подсоединены к входам устройства для лодключе- ния к шинам синхронизации, чтения и записи процессора и соединены с соответствующими входами группы второго узла канальных приемников, выходы которых соединены с выходами устройства для подключения к входам управления многоблочной памятью, выход дешифратора сегмента соединен с первым входом первого элемента И и с R- входом триггера захвата приоритета, причем выход первого элемента И соединен с информационным и стробирую- щим входами триггера захвата приоритета, инверсный выход которого подсоединен к выходу устройства для подключения к шине блокировки процессора и соединен с вторым входом первого элемента И, прямой выход триг-

Гера захвата приоритета соединен с разрешающим и третьим информационным Входами коммутатора шин данных и младших разрядов адреса, второй выход которого соединен с разрешающим входом второго узла канальных прием- риков, отличающееся тем, Что, с целью расширения функциональных возможностей за счет обеспечения возможности записи одного слова данных одновременно в N блоков памяти и выполнения при считывании логической операции ИЛИ над данными по любому адресу в каждом из N блоков памяти, повышения быстродействия за счет асинхронного обмена с памятью и повышения надежности системы путем выработки сигнала ошибки при обращении к несуществующей ячейке |5лока памяти, в него введены регистр номера сегмента, третий узел канальных приемников, второй узел канальных передатчиков,второй элемент И, первый и второй элементы И-НЕ, элемент ИЛИ, элемент задержки,причем Выход третьего узла канальных прием- Ииков соединен с информационным вхо- Йом регистра номера сегмента, выход которого соединен с вторым информационным входом дешифратора сегмента :я информационным входом второго узла канальных передатчиков, выход которого соединен с выходов первого канального передатчика и с информациейs

0

5

ным входом третьего узла канальных приемников, разрешающие входы третьего узла канальных приемников и второго узла канальных передатчиков подключены соответственно к третьему и четвертому выходам дешифратора адре- с&, выход дешифратора сегмента соединен с инверсным первым входом элемента ИЛИ, второй и третий входы которого соединены соответственно с инверсным и прямым выходами триггера захвата приоритета, выход элемента ИЛИ соединен с выходом устройства для подключения к шине ожидания процессора, первый вход второго элемента И соединен с входом синхрони- зации адреса дешифратора адреса, а выход - со стробирующим входом дешиф- 0 ратора сегмента, второй вход второго элемента И соединен с первым входом первого элемента И-НЕ и выходом второго элемента И-НЕ, первый вход которого подсоединен к входу устройства для подключения к выходу синхронизации блока памяти, а второй вход - с прямым выходом триггера захвата приоритета, вторым входом первого элемента И-НЕ и входом элемента задержки, выход которого соединен с третьим входом первого элемента И-НЕ, выход которого подсоединен к выходу устройства для подключения к входу сигнала ошибки процессбра.

5

30

Фиг Г

Фиг. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с многоблочной памятью | 1986 |

|

SU1319039A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1987 |

|

SU1432538A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1984 |

|

SU1236493A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для управления обменом информации процессора с внешними устройствами | 1988 |

|

SU1508223A1 |

| Устройство для сопряжения ЭВМ с линиями связи | 1988 |

|

SU1536393A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

Изобретение относится к вычислительной технике и может быть использовано для организации многовходовой многоблочной памяти при построении многопроцессорных вычислительных систем на базе мини-и микроЭВМ. Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности записи одного слова данных одновременно в N блоков памяти и выполнения при считывании логической операции ИЛИ над данными по любому адресу в каждом из N блоков памяти, повышение быстродействия за счет асинхронного обмена с памятью и повышение надежности системы путем выработки сигнала ошибки при обращении к несуществующей ячейке блока памяти. В устройство, содержащее регистр номера массива, дешифратор адреса, дешифратор сегмента, коммутатор шин данных и младших разрядов шины адреса, первый элемент И, триггер захвата приоритета, системную шину блокировки, канальные приемопередатчики связи с процессором и блоком памяти, введены регистр номера сегмента, задающий местоположение сегмента в адресном пространстве процессора, канальные приемопередатчики для связи с процессором регистра номера сегмента, элемент ИЛИ и второй элемент И, которые совместно с первым элементом И, триггером захвата приоритета и системной шиной блокировки разрешают конфликты, возникающие при одновременном обращении к памяти двух и более процессоров, подключенных через устройство к блоку общей первой и второй памяти, элементы И-НЕ и элемент задержки, позволяющие повысить надежность системы путем выдачи в процессорсигнала ошибки при обращении к несуществующей ячейке блока памяти. К каждому из процессоров системы может быть подключено несколько общих блоков памяти. Для размножения информации в K блоках памяти или выполнения в режиме чтения логической операции ИЛИ регистры номера сегмента устройств сопряжения, подключенных к этим K блокам памяти, настраиваются на один и тот же номер сегмента, причем номера массивов могут быть различны. 2 ил.

| Вероятностное устройство для решения конечно-разностных уравнений | 1984 |

|

SU1236499A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1986 |

|

SU1319039A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-15—Публикация

1988-07-12—Подача