СО

с

00

х

О5

Фи8.1

по модулю MI, счет шк 41 по модулю М, счетчик 42 по модулю М, триггеры 43-45, элемент И 46, элемент ИЛИ 47, сумматор 49, умножитель 50, генератор 51 тактовых импульсов, коммутаторы 52-54 и формирователи импульсов 56-58. Это позволяет повысить быстродействие, расширить функ Й1ональны возможности и область, применения. 10 ил., 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Вычислительное устройство | 1987 |

|

SU1432511A1 |

| Устройство для формирования широкополосного случайного процесса | 1986 |

|

SU1432514A1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

Изобретение относится к вычислительной технике и может быть ий- :пользовано в специализированных вычислительных системах. Устройство содержит мультиплексоры 1-10, блок формирования адреса 11, демультиплексор 13, блоки 14-1 7 формирования адреса, блок 18 микропрограммного управления, блоки 19-25 памяти, блок 26 запоминания информации, регистры 28-39, счетчик 40

1

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислительных системах.

Целью изобретения является повы- шение быстродействия,расширение функциональных возможностей и области применения.

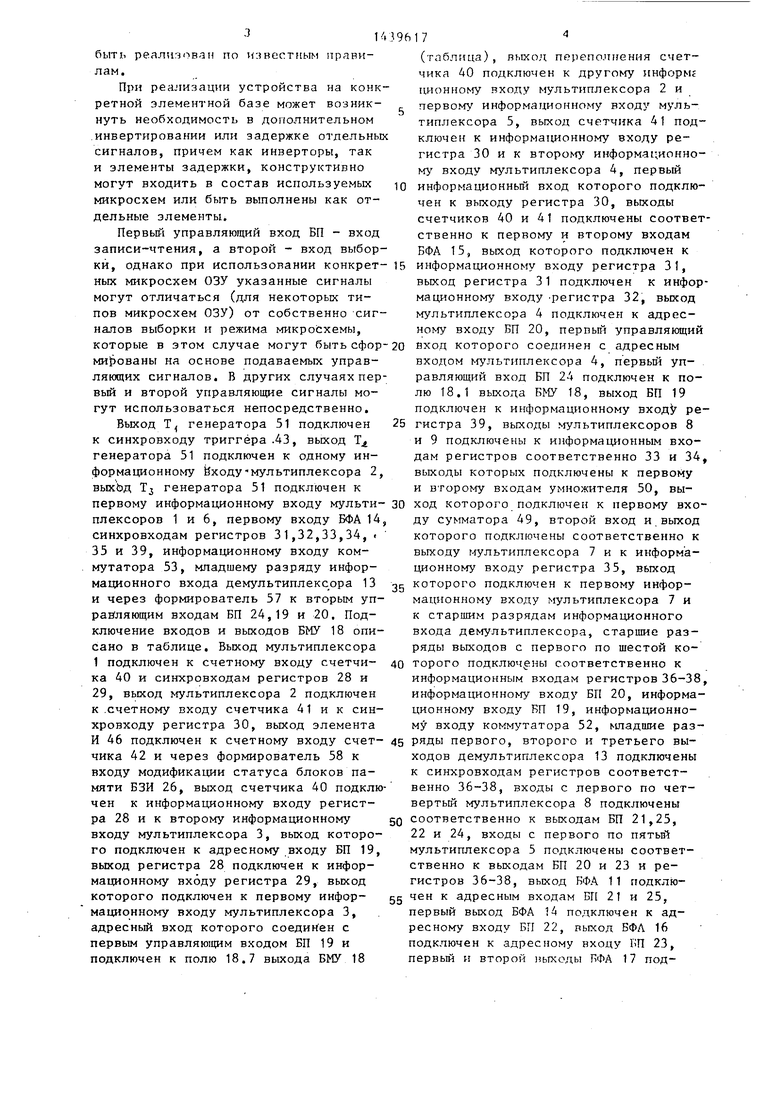

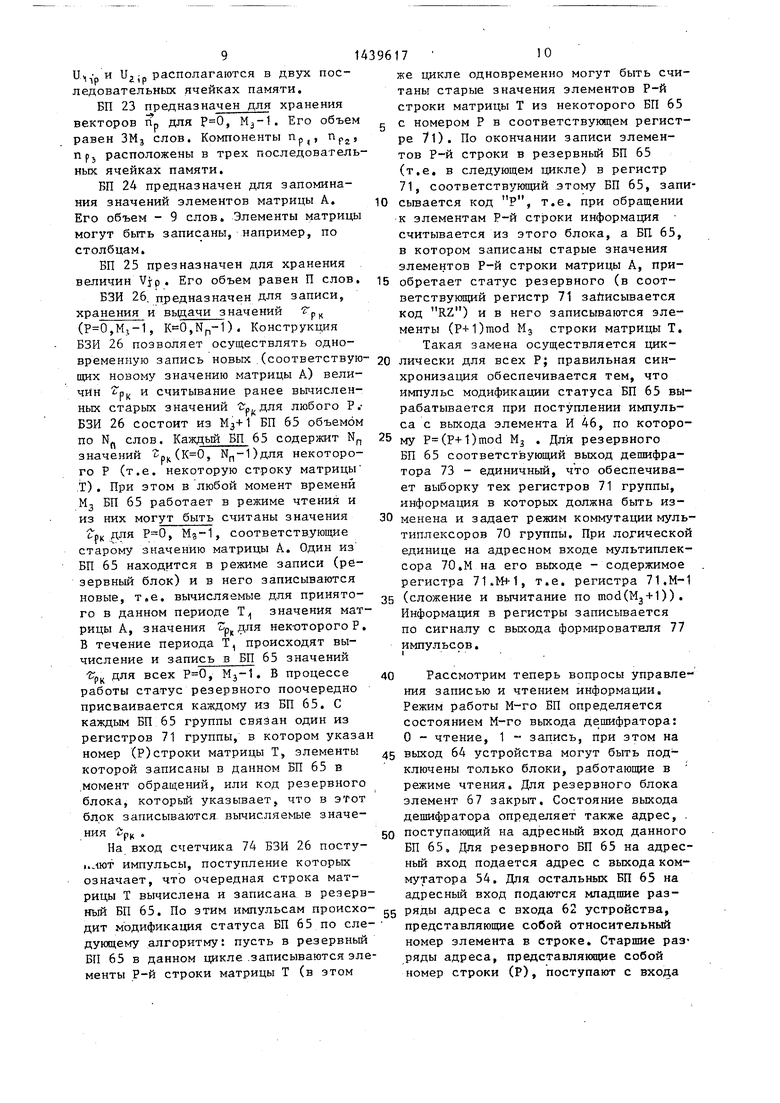

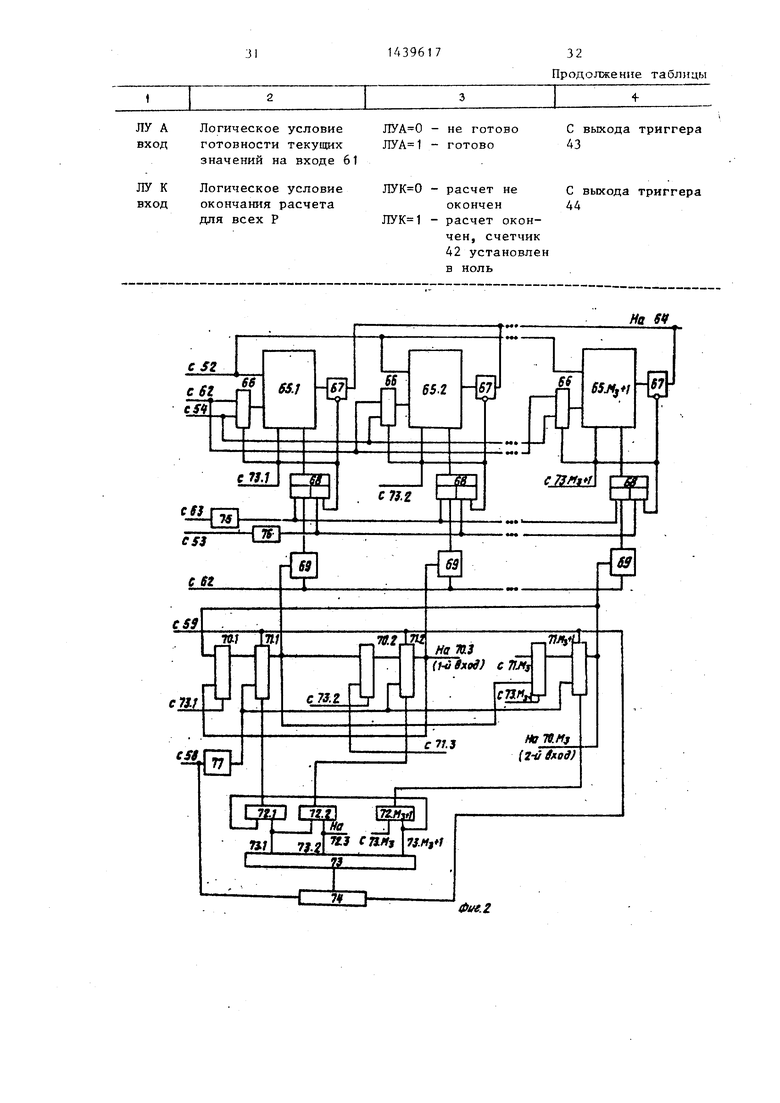

На фиг. 1 представлена функциональная схема устройства; на фиг,2 - функциональная схема блока запоминания информации; на фиг. 3 - блок микропрограммного управления; на фиг.Л-8 блоки формирования адреса с первого по пятый; на фиг, 9 - блок-схема ал- горитма работы устройства; на фиг,10- временная диаграмма генератора тактовых импульсов.

Устройство содержит мультиплексоры 1-10, блок 11 формирования адреса вход 12 логического нуля устройства, демультиплексор 13, блоки 14-17 формирования адреса, блок 18 микропрограммного управления (БМУ), выходы 18.1-18.19 блока 18, блоки 19-25 па- мяти (БП), блок 26 запоминания информации (БЗИ). первый -ВЫХОД 27 демуль- типлексора, регистры 28-39, счетчик 40 по модулю М , счетчик 41 по модулю Mg, счетчик 42 по модулю Mj, триг- теры 43-45, элемент И 46, элемент ИЛИ 47, второй выход 48 демультиплек- сора, сумматор 49, умножитель 50, генератор 51 тактовых импульсов, коммутаторы 52-54, третий выход 55 демультиплексор а, формирователи 56-58 импульсов, вход 59 начальной установки, вход 60 угла поворота системы координат устройства, группу 61 информационных входов устройства, вход 62 адреса считывания устройства, вход 63 строба чтения информации устройства, информационный выход 64 с устройства.

0 О

5

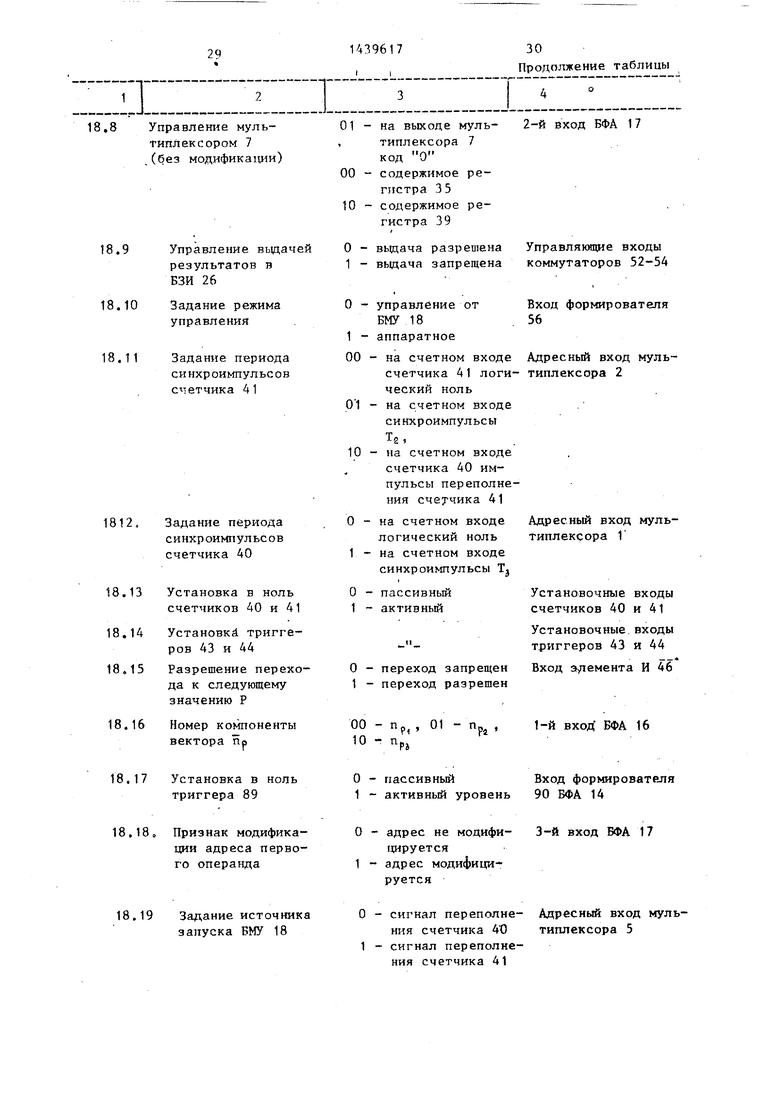

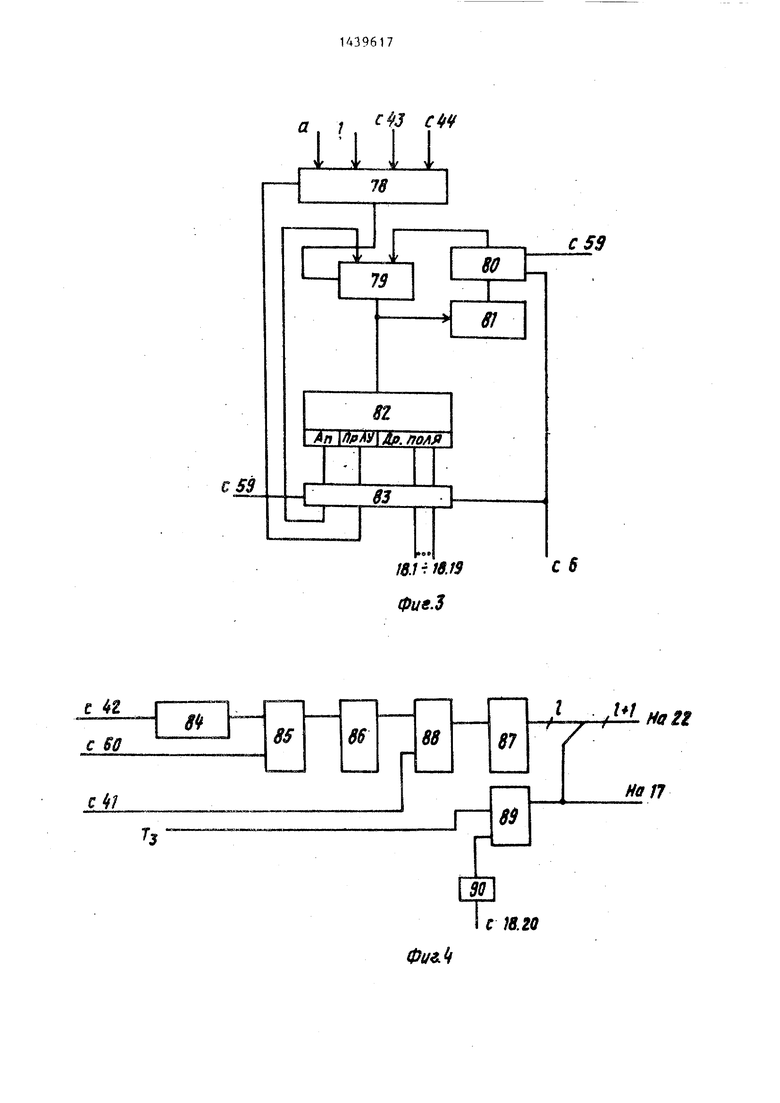

Блок 26 запоминания информации содержит группу БП 65, группу мультиплексоров 66, группу коммутаторов 67, группу элементов 2И-ИЛИ 68, группу схем 69 сравнения (количество элементов в каждой группе равно Mj -ь 1), мультиплексоры 70.1-70.Mj + 1 группы, регистры 71.1-71,Mj « 1 группы, элементы ИЛИ 72.1-72.Mj + 1 группы, дешифратор 73 с выходами 73.1-73.Mj+ 1, счетчик 74 по модулю Мз формирователи 75-77 импульсов. БМУ tS содержит мультиплексоры 78 и 79, регистр 80, узел 81 приращения, БП 82 микроко манд (МК), регистр 83 МК.

Блок 14 формирования адреса (БФА) содержит БП 84, вычитатель 85, узлы 86 и 87 свертки по модулю М, сумматор 88, триггер 89, формирователь 90 импульсов.

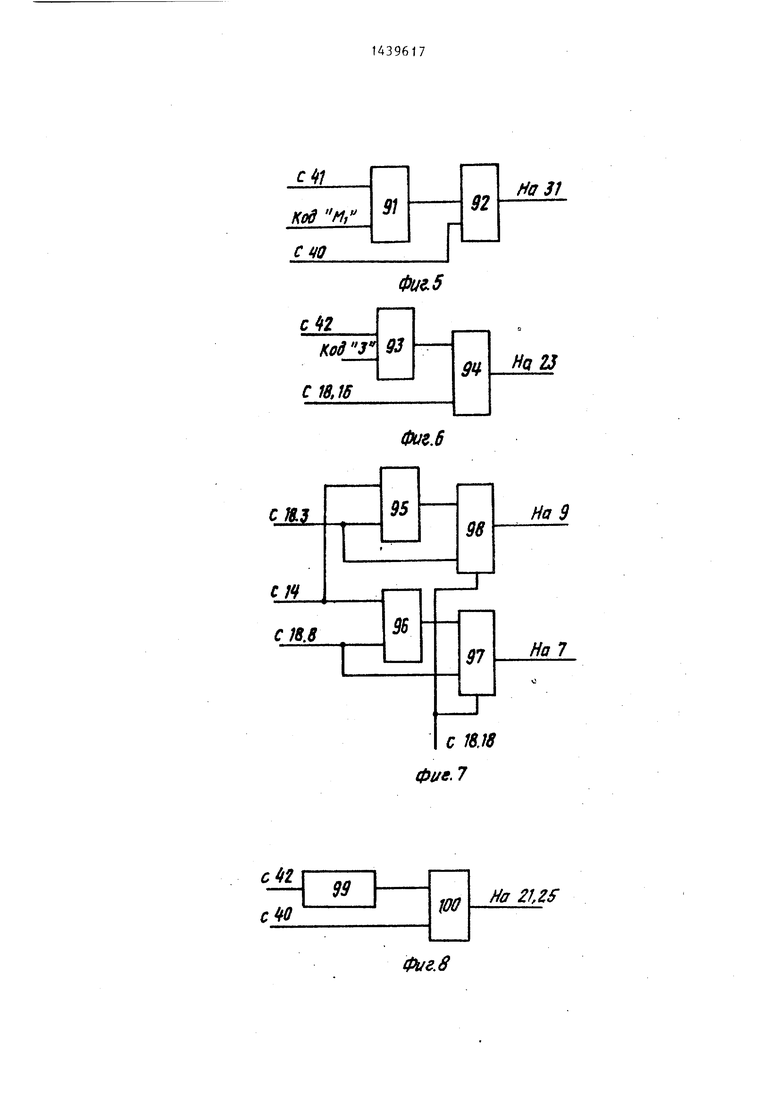

БФА 15 содержит умножитель 91 и сумматор 92,

БФА 16 содержит умножитель 93 и сумматор 94.

БФА 17 содержит сумматоры 95 и 96 и мультиплексоры 97 и 98,

Блок 11 содержит БП 99 и сумматор 100.

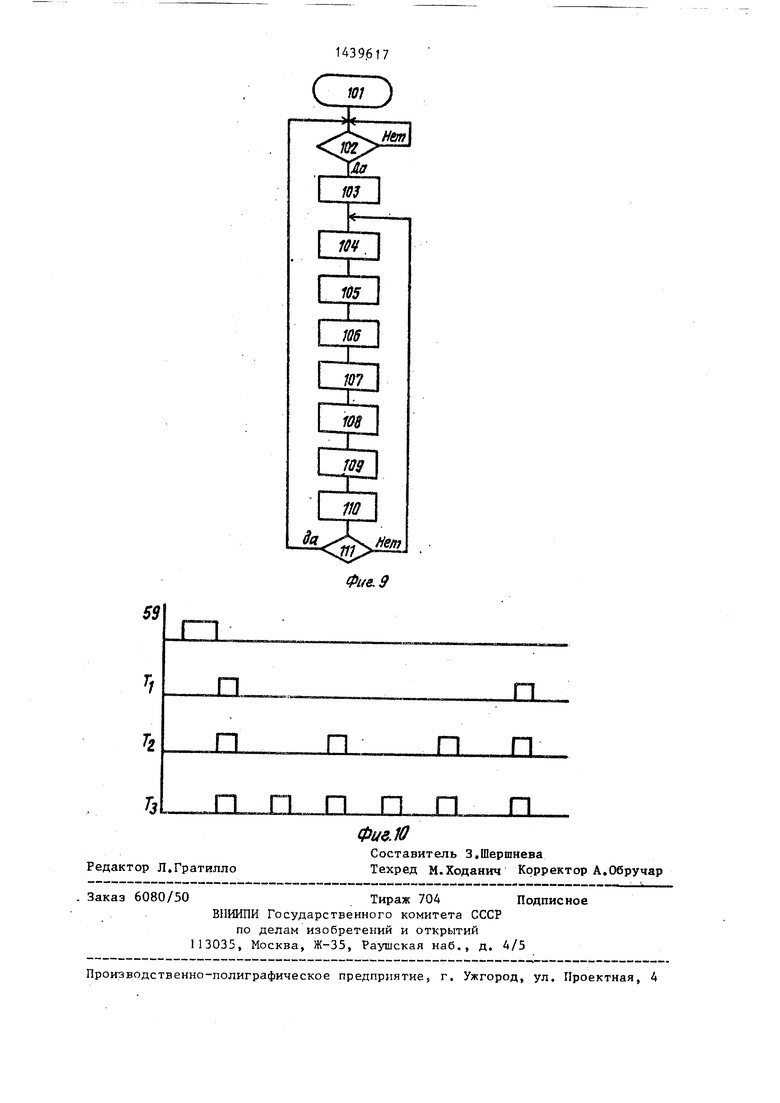

Блок-схема алгоритма включает блоки 101-111,

Узлы свертки по модулю М могут быть вьтолнены на базе сумматора по модулю М 4. с нулевым сигналом на втором входе или на базе ПЗУ; при конкретной реапизации некоторые элементы, например 87 и 88, могут быть объединены. Узел 81 может быть реализован на базе сумматора. Коммутаторы могут быть реализованы, например, на базе трехстабильных элементов К 155ЯП8, причем их разрядность определяется разрядностью передаваемой информации. Генератор 51 может

3

быть реализован по известным правилам.

При реализации устройства на конкретной элементной базе может возникнуть необходимость в дополнительном инвертировании или задержке отдельны сигналов, причем как инверторы, так и элементы задержки, конструктивно могут входить в состав используемых микросхем или быть выполнены как отдельные элементы.

Первый управляющий вход БП - вход записи-чтения, а второй - вход выборки, однако при использовании конкретных микросхем ОЗУ указанные сигналы могут отличаться (для некоторых типов микросхем ОЗУ) от собственно сигналов выборки и режима микросхемы, которые в этом случае могут быть сфор ми1)ованы на основе подаваемых управ- ляЕощих сигналов. В других случаях пер вьй и второй управляющие сигналы могут использоваться непосредственно.

Выход Т генератора 51 подключен к синхровходу триггера.43, выход Т генератора 51 подключен к одному информационному Уходу-мультиплексора 2, выхЬд Tj генератора 51 подключен к первому информационному входу мультиплексоров 1 и 6, первому входу БФА 14 синхровходам регистров 31,32,33,34, 35 и 39, информационному входу коммутатора 53, младшему разряду информационного входа демультиплексора 13 и через формирователь 57 к вторым уп- рав ляющим входам БП 24,19 и 20. Подключение входов и выходов БМУ 18 описано в таблице. Выход мультиплексора 1 подключен к счетному входу счетчика 40 и синхровходам регистров 28 и 29, выход мультиплексора 2 подключен к .счетному входу счетчика 41 и к синхровходу регистра 30, выход элемента И 46 подключен к счетному входу счетчика 42 и через формирователь 58 к входу модификации статуса блоков памяти БЗИ 26, выход счетчика 40 подключен к информационному входу регистра 28 и к второму информационному входу мультиплексора 3, выход которого подключен к адресному входу БП 19, выход регистра 28 подключен к информационному входу регистра 29, выход которого подключен к первому информационному входу мультиплексора 3, адресньй вход которого соединен с первым управляю1цим входом БП 19 и подключен к полю 18.7 выхода БМУ 18

39617

(тпблица), выход переполнения счетчика 40 подключен к другому информг UHOHHONiy входу мультиплексора 2 и с первом информационному входу мультиплексора 5, выход счетчика 41 подключен к информа1щонному входу регистра 30 и к BTopo fj информационному входу мультиплексора 4, первый 10 информационный вход которого подключен к выходу регистра 30, выходы счетчиков 40 и 41 подключены соответственно к первому и второму входам БФА 15, выход которого подключен к 15 информационному входу регистра 31, выход регистра 31 подключен к информационному входу Регистра 32, выход мультиплексора 4 подключен к адресному входу БП 20, первьй управляющий 20 вход которого соединен с адресным входом мультиплексора 4, первьпЧ уп- , равляющий вход БП 24 подключен к полю 18,1 выхода БМУ 18, выход БП 19 подключен к информационному вход ре- 25 гистра 39, выходы мультиплексоров 8 и 9 подключены к информационным входам регистров соответственно 33 и 34, выходы которых подключены к первому и второму входам умножителя 50, вы- 30 ход которого подключен к первому входу сумматора 49, второй вход и выход которого подключены соответственно к выходу мультиплексора 7 и к информационному входу регистра 35, выход 3g которого подключен к первому информационному входу мультиплексора 7 и к старшим разрядам информационного входа демультиплексора, старшие разряды выходов с первого по шестой ко- 40 торого подключены соответственно к информационным входам регистров 36-38, информационному входу БП 20, информационному входу БП 19, информационному входу коммутатора 52, младшие раз- 45 ряды первого, второго и третьего выходов демультиплексора 13 подключены к синхровходам регистров соответственно 36-38, входы с первого по четвертый мультиплексора 8 подключены 50 соответственно к выходам БП 21,25, 22 и 24, входы с первого по пятьп мультиплексора 5 подключены соответственно к выходам БП 20 и 23 и регистров 36-38, выход БФА 11 подклк - gg чен к адресным входам БП 21 и 25, первый выход БФА 14 подключен к адресному входу БП 22, пыход БФА 16 подключен к адресному входу Ш 23, первый t второй )ьгходы БФА 17 под

5U

ключены соответственно к адресным входам мультиплексоров 8 и 9, выход регистра 32 подключен к информационному входу элемента 54, выходы ком- мутаторов 52-54 подключены соответственно к входам информационному, строба записи и адреса записи БЗИ 26, входы строба чтения и адреса чтения которого подключены соответственно к входам 63 и 62 устройства, выход БЗИ 26 подключен к выходу 64 устройства, В-й вход группы 61 подключен к В-му информационному входу мультиплексора 10, (), выход которого подключен к информационному входу БП 24, выход счетчика 42 подключен JK первым входам БФА 11 и 15 и к второму входу БФА 14, третий и четвертьй входы которого подключены соответственно к входу 60 устройства и к выходу счетчика 41.;

Выход коммутатора 52 подключен к- информационным входам БП 65, выходы которых через коммутаторы 67 подключены к выходу 64 устройства, выход коммутатора 54 подключен к первым информационным входам мультиплексоро в 66, выходы которых подключены -К адресным входам соответствующих БП 65, первый управляющий вход М-го БП 65 подключен к М-му выходу дешифратора 73 и соединен с управляющим входом М-го коммутатора 67 и адресным входом М-го мультиплексора 67, а также с первым входом первой группп входов М-го элемента 2И-ИЛИ выход которого подключен к второму управляющему входу М-го БП 65, , Mj+l, первый вход второй группы М-го элемента 2И-ИЛИ подключен к выходу М-й схемы 69 сравнения, вторые входы схем 69 сравнения подключены к входу 62 устройства (старшим разрядам), мпадпше разряды входа 62 устройства подключены к вто- рым информационньм входам мультиплексоров 66, выход счетчика 74 подключен к входу дешифратора 73, М-й выход которого подключен к первому входу М-го и второму входу ((M+1)mod(M.,,+ 1))-ro элементов ИЛИ 72 и к адресному входу М-го мультиплексора 70, выход М-го элемента ИЛИ 72 подключен к входу выборки М-го регистра.71, входы начальной установки разрядов которого подключены к входу 59 устройства в соответствии с требуемым начальным состоянием, выход формирователя 58 под

ключен к счетному входу счетчика

0

5

0

25

96

40 45

30

35

17 6

и через формирователь 77 - к синхро- входам регистров 71, выход М-го мультиплексора 70 подключен к информационному входу М-го регистра 71, выход которого подключен к второму входу М-й схемы 69 сравнения, первому информационному входу ( (М+1)mod(Mj+1))-го мультиплексора 70 и к второму информационному входу ((М-1)тод(Мз+1))-го мультиплексора 70, вход 63 устройства через формирователь 75 подключен к вторым входам второй группы элементов 68, выход элемента 53 через формирователь 76 подключен к вторым входам первой группы элементов 68, вход 59 устройства подключен к входам начальной установки разрядов счетчика 74,

Допустим в пространстве заданы некоторая основная система координат (ОСК) и вращающаяся система координат (век), которая получается из ОСК . путем вращения ОСК вокруг осей ОХ, OY и OZ, причем положение ВСК относительно ОСК описывается следующим , .образом: повернем ОСК на угол f во- )круг оси OZ. Получившуюся систему ко ординат обозначим ПСК .- повернутая система координат. ПСК задает равновесное положение ВСК относительно ОСК, При этом имеют место непрерывные ко- лебания ВСК относительно ПСК (т.е. повороты на небольшие углы вокруг осей OX;,OY и OZ ПСК), которые описываются матрицей вращений А, связывающей ОСК и ВСК. В ОСК задано множество из Мд векторов Н р (пр, Ьр4, Прз), где Т - символ транспортирования, Р О, Мз -1.. С ВСК жестко связано множество из N точек, расположенных симметрично относительно оси , OZ ВСК, например, принадлежащих поверхности цилиндра или усеченной сферы. В ряде специальных задач для каждого Р требуется рассчитать N функций.:

.- -РК ,

(1)

40 45 50

55

где - радиус-вектор точки в ВСК; К.р является функцией от Р и К, , N,-1 - относительный номер точки в Р-м подмножестве точек. Сово- купность функций gf(, рассчитанных для , Мз-1 и , N„-1, образует матрицу функций Т ( p,() размерности MjxN, причем для счета каждой строки матрицы Т требуется формирование подмножества из Ы„ векторов ц.р в

Ч, сферические координаты Кр -и точки в век. Параметр . является функцией только от jp (для цилиндра) или постоянен (для сферы), параметр задает положение jp-ro кольца (для цилиндра) или параллели (для сферы), параметр задает положение ip-ro столба (для цилиндра) или .ip-r меридиана (для сферы). При этом для любых ip значение Ч /л зависит только от jp ; для любых jp значение M jp зави сйт только от 1„; для любых j.

ние

1 ; для любых только от р

Р

значен изменяЧ,-., зависит

ется с шагом дЧ. Таким образом, координаты Кр-й точки однозначно определяются значениями jp и i Параметры jp и if рассчитываются по формуле

jp Знр - J; (3)

jp ((ipH- PA PlU.M,- iUjM,(4)

где x - целая tfacTb числа Xj j 0, M,(-1 - относительный номер па- раме Р-м подмножестве; i О, Mj,- 1 - относительный номер параметра ip в Р-м подмножестве;

Л

нр

- начальное смещение по

J для смещение

заданного Р; 1цр - начальное

по i для заданного Р, рассчитанное

для Ч О.

Величины j и i рассчитываются заранее и хранятся соответственно с БП 99 и БП 84. Для случая сферы jj,,n-M в зависимости от Р, где П - количество параллелей; для цилинд- рэ JHp - 1 количество точек в одном столбе (MfH) . Параметр нре где М - количество точек в одной параллели (или количество меридианов 50 для сферы) или количество точек в одном кольце (для цилиндра). Величина ф/дЧ поступает с входа 60 устройства и задается, например, при настрой- ке устройства. Относительный номер 55 точки- в подмножестве может быть рассчитан по формуле:

К

(5)

N,

п;Л ();

зр ffpcos H jp;

(6) (7) (8)

(9)

(10)

(11)

Анализ (1)-(11) позволяет предложить следующий алгоритм расчета матрицы Т.

Расчет NP по формуле (6) и запись компонент в регистры 36-38.

Расчет Ь, „ по формуле

(12)

и запись результатов

Np,Z,p

для

в БП 19.

Расчет и, л по (11) для i О, Mj-l и запись результатов i БП 20,

Расчет

2 р по формуле

для

t всех

Vjp и,

,-1 (т.е.

(13)

. ,,.... j о, м,-1,

запись результатов в

0 5

, N

i О, Mj-l) и 5 блок 26.

Повторение всех расчетов для Р - О, Мз-1.

Вычисления в указанной последовательности осуществляются периодически 0 после записи т гкущих значений матрицы А с входов 61 устройства в БП 24.

Рассмотрим функциональное назна- |Чение блоков памяти, входящих в сос- /тав устройства. I

БП 19 предназначен для запомина- ния величин bjp, вычисленных.в соот- тетствии с (12;. Его объем равен М слов.

БП 20 предназначен для запоминания величин и,-р, вычисленных в соответствии с (11;. Его объем равен М слов.

БП 21 предназначен для хранения величин Zjp . Его объем равен П слов, (jj, О, П-1) .

БП 22 предназначен для хранении величин и,. и (-р- О, ). Его объем равен 2м слов. Величины

91

U(, p и Ujjp располагаются в двух последовательных ячейках памяти.

БП 23 предназначен для хранения векторов rip для , . Его объем равен 3Mj слов. Компоненты Пр, Пр, npj расположены в трех последовательных ячейках памяти.

БП 24 предназначен для запоминания значений элементов матрицы А. Его объем - 9 слов. Элементы матрицы могут быть записаны, например, по столбцам.

БП 25 презназначен для хранения величин Vjp. Его объем равен П слов.

БЗИ 26, предназначен для записи, хранения и вьдачи значений ,, (,MI-I, K«0,Np-1). Конструкция БЗИ 26 позволяет осуществлять одновременную запись новых , (соответствую щих новому значению матрицы А) величин Tpi и считывание ранее вычисленных старых значений С р для любого Р.- БЗИ 26 состоит из Мз+1 БП 65 объемом по Nj слов. Каждый БП 65 содержит N значений (, Ы,,-1)для некоторого Р (т.е. некоторую строку матрицы .Т). При этом в любой момент времени М БП 65 работает в режиме чтения и из них могут быть считаны значения

б ок для , Мз-1, соответствующие старому значению матрицы А. Один из БП 65 находится в режиме записи (резервный блок) и в него записываются новые, т.е. вычисляемые для принятого в данном периоде Т значения матрицы А, значения р нек-оторого Р . В течение периода Т, происходят вычисление и запись в БП 65 значений

Й РЦ для всех , Mj-l. В процессе работы статус резервного поочередно присваивается каждому из БП 65. С каждым БП 65 группы связан один из регистров 71 группы, в котором указан номер (Р)строки матрицы Т, элементы которой записаны в данном БП 65 в .момент обращений, или код резервного блока, которьй указывает, что в этот блок записываются вычисляемые значения .

На вход счетчика 74 БЗИ 26 посту- 1.ЛЮТ импульсы, поступление которых означает, что очередная строка матрицы Т вычислена и записана в резерв- ньй БП 65. По зтим импульсам происходит модификация статуса БП 65 по следующему алгоритму: пусть в резервный БП 65 в данном цикле .записываются элементы Р-й строки матрицы Т (в этом

17

10

5

0 5 О

5

0

5

0

5

же цикле одновременно могут быть считаны старые значения элементов Р-й строки матрицы Т из некоторого БП 65 с номером Р в соответствующем регистре 71). По окончании записи элементов Р-й строки в резервный БП 65 (т.е. в следующем цикле) в регистр 71, соответствующий этому БП 65, запи- сьшается код Р, т.е. при обращении к элементам Р-й строки информация считывается из этого блока, а БП 65, в котором записаны старые значения элементов Р-й строки матрицы А, приобретает статус резервного (в соответствующий регистр 71 записывается код RZ) и в него записываются элементы (P+1)mod Mj строки матрицы Т. Такая замена осуществляется циклически для всех Р; правильная синхронизация обеспечивается тем, что импульс модификации статуса БП 65 вырабатывается при поступлении импульса с выхода элемента И 46, по которому P(P+1)mod Mj . Для резервного БП 65 соответствующий выход дешифратора 73 - единичный, что обеспечивает выборку тех регистров 71 группы, информация в которых должна быть изменена и задает режим коммутации мультиплексоров 70 группы. При логической единице на адресном входе мультиплексора 70,М на его выходе - содержимое регистра 71.Mf1, т.е. регистра 71.М-1 (сложение и вычитание по mod(M3+1)). Информация в регистры записывается по сигналу с выхода формирователя 77 импульсов.

Рассмотрим теперь вопросы управления записью и чтением информации. Режим работы М-го БП определяется состоянием М-го выхода дешифратора: О - чтение, 1 - запись, при этом на выход 64 устройства могут быть подключены только блоки, работающие в режиме чтения. Для резервного блока элемент 67 закрыт. Состояние выхода дешифратора определяет также адрес, . поступающий на адресный вход данного БП 65, Для резервного БП 65 на адресный вход подается адрес с выхода коммутатора 54. Для остальных БП 65 на адресньй вход подаются младшие разряды адреса с входа 62 устройства, представляющие собой относительный номер элемента в строке. Старшие разряды адреса, представлякяцие собой номер строки (Р), поступают с входа

II143

62 устройства па первые входы схем 69 сравнения группы.

Адреса с входа 62 или с выхода коммутатора 54 сопровождаются стробами соответственно с входа 63 устройства и с выхода коммутатора 53. Стробы через формирователи 75 и 76 подаются на первые входы элементов И элемента 2И-ИЛИ, При этом для резервного блока 65 памяти строб с выхода формирователя 75 проходит так, как соответствую- ПЦ1Й разряд дешифратора - в единице. Строб чтения с выхода формирователя ,75 проходит на вход выборки того ВП 65, в который в момент обращения записана требуемая строка. При наличи (сигналов записи-чтения и выборки про- |исходит запись (чтение) информации, Формирователи 75 и 76 предназначены для обеспечения требуемых параметров импульса на входе выборки блока памя- ,ти, а также обеспечивают задержку «мпульса, необходимую для устойчивой записи информации, формирователь 77 1обеспечивает надежную модификацию |статуса блоков,

Рассмотрим примеры реализации БФА, WA 11 предназначен для адресации блоков 21 и 25 памяти, БП 99 содержит зйачения , вычисленные для всех Р, Сумматор 100 осуществляет расчет по формуле (3),

БФА 14 презназначен для адресации блока 22 памяти.

БП 84 содержит значения , вы

численные для всех Р,

БФА 14 работает следующим образом: при заданной организации БП 22 адрес величины U,j равен 2ip, адрес вели- чины Uji-p равен 2ip + 1 , Элементы 84-88 осуществляют расчет ip. Формирование удвоенного значения осуществляется монтажно-сдвигом влево на один разряд. Младпмй разряд адреса формирует- ся на счетном триггере 89 который обеспечивает выборку и,;- и Uj,- за два последовательных такта 1. Правильная последовательность выборки об ее-, печивается начальной установкой триг- гера 89,,

БФА 15 формирует адрес записи рк в БЗИ 26, TpedyeMb адрес вычисляется в соответствии с (5),

БФА 16 формирует адрес компонент вектора п-в соответствии с вьфаже- нием А ЗР -ь С, где С - значение поля 18,16,

j- 5 0 5

0

5

0 5

1712

БФА 11,15 и 16 могут быть легко реализованы на базе ПЗУ,

БФА 17 формирует адреса, поступаю- щие на адресные входы мультиплексоров 7 и 9,

В зависимости от значения управляющего сигнала 18,18 БФА 17 или про- пускает без изменения на адресйые входы мультиплексоров 7 и 9 значения, заданные в полях соответственно 18,8 и 18,3 БМУ, или модифицирует их с периодом Tj в соответствии с состоянием триггера 89, Модификация заключается в прибавлении содержимого триггера 89 к значениям, заданным в полях 18,8 и 18,3

Рассмотрим функциональное назна- .чение полей БМУ 18,

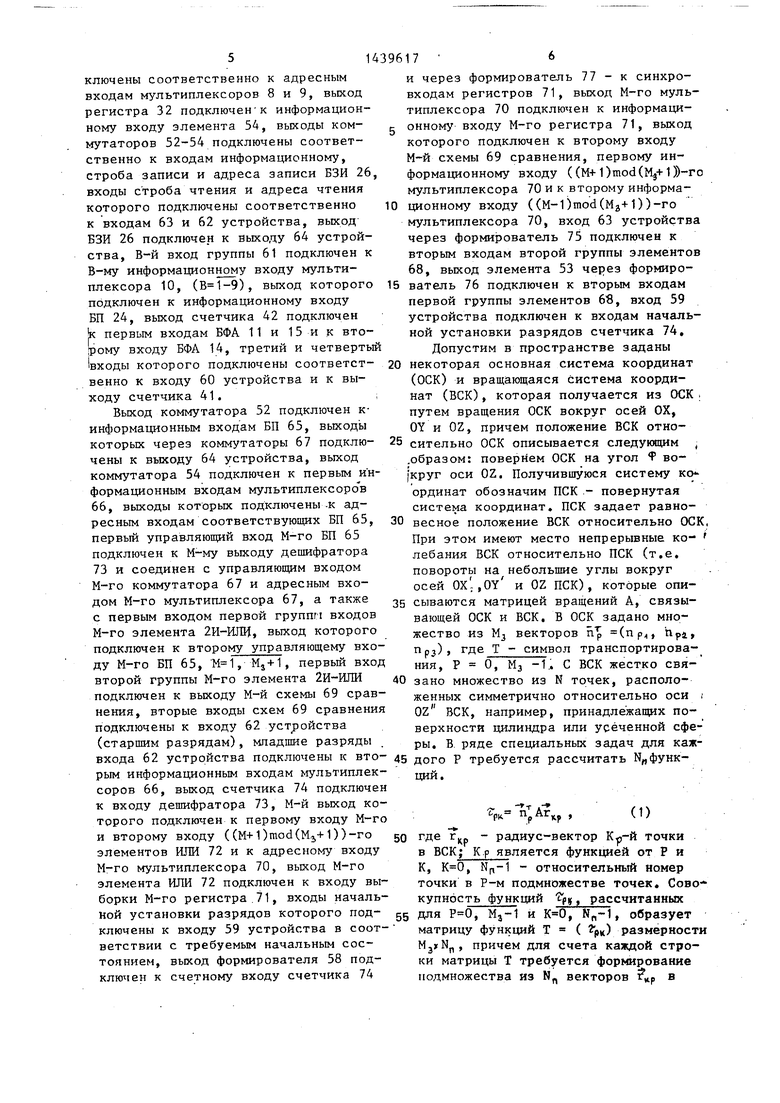

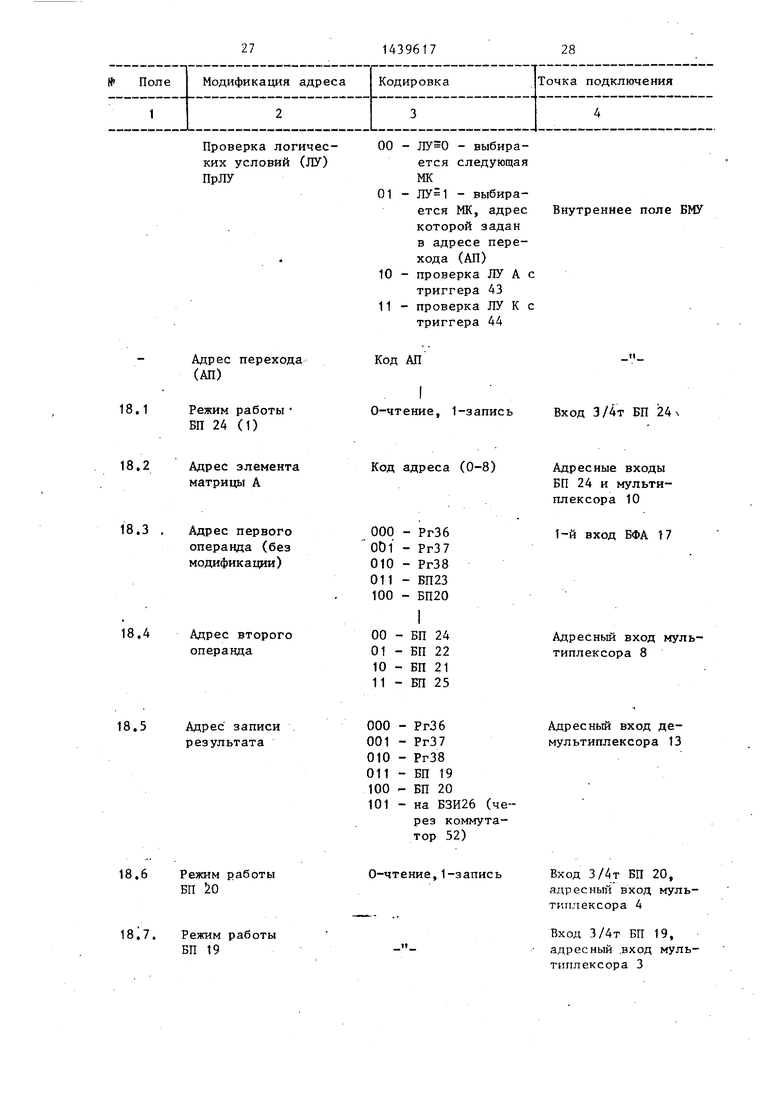

В таблице приведен пример кодировки полей микрокоманд (МК),

Микропрограмма работы устройства составляется в соответствии с -блок- схемой алгоритма (фиг,9) с использованием введенной кодировки МК,

Блоки алгоритма (фиг,9) имеют следующий смысл:

101- начальная установка устройства;

102- проверка: - ; .

103- прием матрицы А;

104- расчет вектора Npj

105- задание режима для расчета

bjp ; управление передается аппаратным средствам;

106- расчет и запоминание bj- для

j 0,М,-1, возврат управления БМУ 18; задание режима для расчета

107108109110111и ,-р , управление передается аппаратным средствам; расчет и запоминание U для всех , Mj-1, возврат управления БМУ 18; задание режима для расчета f.,j, управление передается аппаратным средствам; расчет и запоминание р для всех , N„-1, , возврат управления БМУ 18; проверка; - ,

55

В дальнейшем при описании работы устройства используется введенная кодировка, причем выражение 18, означает, что поле 18.Н принимает значение ххх, В целях упрощения указываются только поля, наиболее сущест

13lA

вениь е в рас.смятриЛяемом такте. При этом значения остальных нолей в данном такте могут принимать значения из числа допустимых (таблица) и не противоречащих значениям полей, указанных явно.

Устройство работает следующим образом,

В устройстве реализован следующий npHHTi in управления: общее управление работой устройства и вычислительным процессом осуществляет БМУ 18, однак часть вычислений, характеризующаяся большим количеством повторяющихся операций, выполняется под управлением аппаратных средств. Для перехода к такому режиму вычислений очередная МК БМУ 18 задает необходимую кoм tyтa- цию операндов и результата, требуе- мую частоту синхроимпульсов и другие необходимые параметры и блокирует прохождение синхроимпульсов на син- хровход БМУ 18. БМУ 18 приостанавливает свою работу до тех пор, пока не закончится требуемый цикл вычислений (при этом на его выходе находится МК задающая необходимый режим вычислений) . По окончании цикла сигнал запуска устанавливает триггер 45 в еди- ницу и на синхровход БМУ 18 поступает очередной синхроимпульс, выбираго1 1;ий следующую МК,

Работа устройства осуществляется в соответствии с алгоритмом.

По сигналу начальной установки (НУ), поступающему с входа 59 устройства, который может вырабатываться при включении питания или подаваться в требуемые моменты времени, элемен- ты устройства устанавливаются в начальное состояние: триггер 45 устанавливается в единицу, регистры 80 и 83 БМУ 18 - нулевое состояние, генератор 51 - в начальное состояние, счетчик 74 - в состояние Mj, регистры 71.1,...,71.Mj, 71.Mj+1 - в состояния соответственно О,1,..., Mj-1, RZ, где RZ - код резервного блока памяти, не совпадающий ни с одним из кодов ,

Такая начальная установка регистров и счетчика может быть достигнута за счет соответствующей коммутации сих нала НУ по входам установки в еди ницу или установки в ноль требуемых разрядов.

По окончании сигнала НУ с выходов генератора 51 начинают поступать син171/,

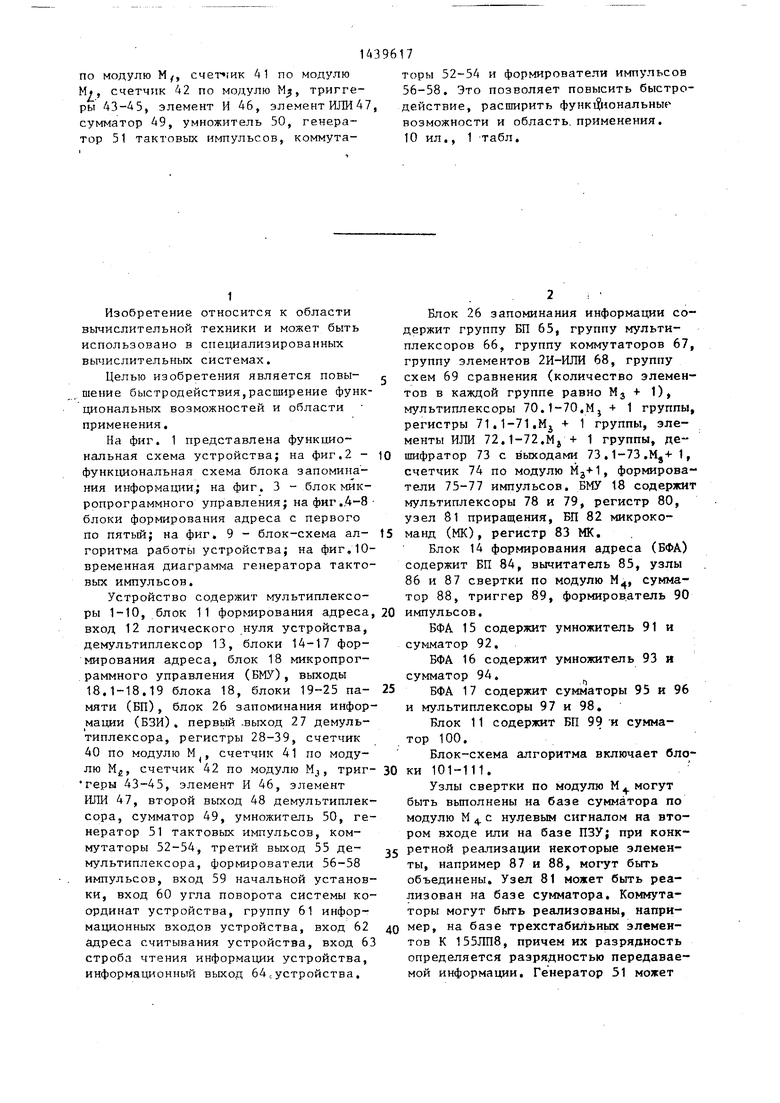

хроимпульсы 7 , Т , Tj . Величина периода Т, достаточна для выпо.чнсния операций приема нового зн°ачения матрицы Л и вьржсления матрицы Т, величина периода Tii достаточна для выполнения операции вида на элементах 49 и 50 с учетом совмещенного с нькислениями фop иpoвaния адреса и выборки операндов из памяти, (фиг.10). По синхроимпульсу Тз на- выход БМУ 18 поступает первая микрокоманда, которая обеспечивает проверку ЛУА с вькода триггера 43. При это ПрЛУ5 10, АЛ адрес первой микрокоманды блока 18. 18. 18. 18. 18.. Если (триггер 43 в нуле), то выбирается следующая МК, которая осуществляет безусловный переход на Ж проверки ЛУА (ПрЛУ 01, All - адрес первой Ж блока 102 ) т.е. переход по адресу, заданному в поле АП на первую МК блока 103. Синхроимпульс Т устанавливает триггер 43 в единицу, вследствие чего счетчик 42 устанавливается в ноль, по синхроимпульсу Tj осуществляется пь реход на первую МК блока 103. Блок 103 содержит последовательность Ж, в результате выполнения которой осуществляются прием новых значений матрицы А и сброс триггеров 43 и 44, Последовательность содержит 9 МК, в которых заданы следунщие значения полей: 18. 18.2: код адреса от О до 18. 18, 18. 18. 18. 18.. Таким образом, триггеры 43 и 44 обнуляются, БП 24г,- в режиме записи, информация с входов 61 выбирается в соответствии со значением адреса записи (18.2) и записывается в БП 24 по сигналу с выхода формирова теля 57 импульсов. После приема новых значений матрицы А начинается вьшол- нение блока 104, который содержит последовательность Ж, обеспечивающую расчет компонент вектора Np (в данном случае, ) . Поля Ж принимают следующие значения: 18. ПрЛУ:

00j 18.2: код адреса от О до 8 18. 18. 18. 18.18: 0| 18.13. 18. 18.15. 18.,01,10; 18, 18.8: 00, 18., 001, 010:

Поля 18.2, 18.6, 18.8 и Т8.5 при вьтолнении блока 104 принимают раз1 5 личн ые значения п разных тактах Т,

что и указан при описании формата МК. Такие обозначения используются и в дальнейшем.

Таким образом, БП 24 - в режиме чтения, информация с выхода БП 2А записывается в регистр 33 (адрес считывания задается в поле 18,2); информация с выхода БП 23 считывается по адресу, формируемому в БФЛ 1б, и записывается в регистр 34. Результаты вычислений записываются в регистр 35 и через демультиплексор 13 в один из регистров 36-38. Демультиплексор 13 коммутирует на информационные входы регистров 36-38 информацию с выхода регистра 35, а на синхровходы регистров 36-38 - синхроимпульсы Тз. При этом коммутация на входы регистров осуществляется в тех тактах, когда в регистр 33 записаны значения, соответственно р. Np и N. , что обеспечивает правильную запись и хранение значений компонен; вектора N. I При расчете вектора Np важную роль (играет также мультиплексор 7, который при вычислении Компонент вектора по- дae на один из входов сумматора 49 или нулевой код с входа 12 устройст- ва, или значение частичной суммы с выхода регистра 35.

В качестве примера рассмотрим вы-

По очередному синхроимпульсу Tj осуществляется переход к блоку 105. На выходе БШ 18 появляется МК, зад ния режима поля которой принимают сл дующие значения;поле 18.10 устанавли вается в единицу, что приводит и к установке в ноль триггера 45 и подключает логический ноль на синхровхо ЕМУ 18, поля 18. 18. 18. 18. (на адресный вход БП 19 подключен регистр 29); 18. 18. 18. 18. 18.4: 10; 18. 18.9: 1; 18.5: 18.. Таким образом, информация с выхода БП 21 записывается в регист 33, в регистр 34 записывается N-, н одном входе сумматора 49 - нулевой код. Адрес БП 21 формируется на БФЛ П аналогично oпиcaннo y, результат вычисление Np . По синхроимпульсу Tj на 5 числений записывается в БП 19 через

адресный вход БП 24 поступает адрес

демультиплексор 13 по сигналу с вьрсо да формирователя 57. На счетный вход счетчика 40 поступают синхроимпульсы с выхода мультиплексора 1, вследстви 40 чего счетчик изменяет свое состояние от О до , т.е. j 0.,.М,-1, что обеспечивает расчет всех bjp для заданного Р. По сигналу переполнения счетчика 40 триггер 45 устанавливает

элемента а

м

а адресньй вход БП 23 - адрес с выхода БФА 16, по которому выбирается Пр. Следующим синхроимпульсом значения а,, и Пр заносятся в регистры 33 и 34 соответственно. На выходе мультиплексора 7 - нулевой код. По следующему синхроимпульсу в регистры 33 и 34 заносятся значения а и

Пр2, а в регистр 35 - значение п

которое через мультиплексор 7 подается на один из входов сумматора 49. В следующем такте в регистры 33 и 34 заноPI

Ji

и п

рз + а

в регистр 2 Прг. косятся значения а

35 - значение а ир

торое через мультиплексор 7 подается

на один из входов сумматора 49,

По следующему синхроимпульсу в регистр 35 записывается результат вьгчис

1( р1 pfl

лений - Np, а

+ Пр, , домультиплексор 13 подключает регистр 35 на вход регистра 36. Следующий синхроимпульс записывает в регистр 36 значение Np и отключает

ю15 20зо

i

43961716

регистр 36 по входу (таким образом NP, в регистре 36 хранится до тех пор, пока не будет рассчитано Np, для

25

следующего Р), аналогично вьт1сляются значения Npj . Для повышения быстродействия допустимо совмещение записи результата вычислений и вычисл- ния первого произведения для следующей компоненты.

По окончании выполнения последовательности МК блока 104 в регистры 36-38 записаны значения соответственно N р , р2 Рз Счетчики 40 и 41 установлены в ноль.

По очередному синхроимпульсу Tj осуществляется переход к блоку 105. На выходе БШ 18 появляется МК, задания режима поля которой принимают следующие значения;поле 18.10 устанавливается в единицу, что приводит и к установке в ноль триггера 45 и подключает логический ноль на синхровход ЕМУ 18, поля 18. 18. 18. 18. (на адресный вход БП 19 подключен регистр 29); 18. 18. 18. 18. 18.4: 10; 18. 18.9: 1; 18. 18.. Таким образом, информация с выхода БП 21 записывается в регистр 33, в регистр 34 записывается N-, на одном входе сумматора 49 - нулевой код. Адрес БП 21 формируется на БФЛ П аналогично oпиcaннo y, результат числений записывается в БП 19 через

демультиплексор 13 по сигналу с вьрсо- да формирователя 57. На счетный вход счетчика 40 поступают синхроимпульсы с выхода мультиплексора 1, вследствие чего счетчик изменяет свое состояние от О до , т.е. j 0.,.М,-1, что обеспечивает расчет всех bjp для заданного Р. По сигналу переполнения счетчика 40 триггер 45 устанавливаететсясленоPI 15 ся в единицу, что подключает синхроимпульсы Tjна синхровход БМУ 18, При этом в регистр 28 записан адрес последнего вычисляемого bjp, а в регистр 33 - последнее значение Z,c,. По следующему синхроимпульсу Т вычислений записывается адрес 29, а

Jf 0 дующему синхроимпульсу Tj результат

в регистр 35,

записи переписывается в регистр на выходе БМУ 18 появляется следующая МК, блокирую1цпя прохождение 5 cинxpoи fflyльcoв на счетный вход счетчика 40 (18.12: 0), поле 18. поле 18. (т.е. БИ 19 продолжает находиться в режиме ланиси), последний результат Ь чяписывается в БП

1714

19 по сигналу с выхода формирователя 57, запущенного этим синхроимпульсом. В следующей МК поле 18., что исключает запись недостоверной инфор- нации. Таким образом, в БП 19 записаны все требуемые для заданного Р значения bj«. В соответствии с алгоритмом (блок 107) очередная МК задает режим расчета U;- . Указанная МК долж- на поступать по синхроимпульсу Tj, синхронному с Tj, При необходимости, так как МК детерминирована, это условие легко соблюдается введением холостой МК для пропуска одного так- та, МК режима задает следующие параметры: поле 18.10 устанавливается в единицу; 18., 18. 18. 18. 18. 18.6: 1 (при этом на адресном входе БП 20 адрес с выхо- да регистра 30), поле 18. поле 18.17 устанавливается .в единицу, что устанавливает в ноль триггер 89, 18.3: 000; 18.8: 00| 18.4: 01| 18.5: 100; 18.9: 1; 18.15: 0. Та- КИМ образом на синхровходе ЕМУ 18 - логический ноль, на синхровход счетчиков 41 и 40 подключены соответственно синхроимпульсы Tj, Tj, БФА 17 работает в режиме модификации, на информационные входы регистров 33 и 34 подключены соответственно БП 22 и регистр Зб на одном входе сумматора 49 - содержимое регистра 35, счетчик 41 - в нуле, на адресном входе БП 22, так как счетчик 41 и триггер 89 - в нуле, БФА 14 вырабатывает адрес элемента для соответствующего заданному Р, которое определяется состоянием счетчика 42, и i 0 (i: состояние счетчика 41).Следующий синхроимпульс Тз записывает в регистр

33 считанное значение U

пр

в регистр

34 - значение Nf, триггер 89 устанавливается в единицу. При этом БФА 17 модифицирует адреса операндов, вследе ствие чего на выходе мультиплексора 9 появляется содержимое регистра 37, на выходе мультиплексора 7 - нулевой код на адресном входе БП 22 - адрес следующей ячейки памяти, в которой записано значение и2{р(для того же самого i). Следующим синхроимпульсом Tj (синхронным с Tj) в регистр 35 запи- с ывается значение U. , Np, в регист ры 3-3 и 34 - знячепия соответственно

триггер 89 устанавливается один из входов сумматора 49 коммутируется содержимое регистра 35.

U2,«Np,,

в ноль, на один из входов сумматора 49

7

18

Импульс Тз увеличивает содержимое счетчика 41 на единицу, что обеспечивает формирование адреса для выборки

и

5 0 5 0 5 0

соответствующего следующему

5

5

O

iip значению i.

По следующему импульсу Tj в регистр 35 записывается результат: , (для данного i), а в регистры 33 и 34 - операнды, необходимые для вычислений по следующему i. Запись результата вычислений в БП 20 осуществляется по сигналу с выхода формирователя 57 (правильный результат записывается во втором такте Т периода Tg).

Дальнейшие вычисления осуществляют- ся аналогично для всех i,T.e. ,M2-1 Рассмотрим завершение вычислений по данному режиму.

В последнем цикле по i синхроим- пульс Та с выхода мультиплексора 2 записывает в регистр 30 адрес последнего вычисляемого значения U, p и вызывает импульс переполнения счетчика 41, который устанавливает в единицу триггер 45. Следующий импульс Tj записывает в регистр 35 последнее вычисленное значение , запускает формирователь 57, сигнал с выхода ко- .торого записывает последний вычисленный результат в БП 20, а также вызывает появление следующей Ж на выхо- де БМУ 18, в которой поля 18. 18. 18. 18. 18,12: 0| т.е. счетчики 40 и 41 - в нулевом состоянии, на выходах мультиплексоров 1 и 2 - логические нули, БП 20 в режиме записи. Таким образом, в БП 20 записаны всё вычисленные значения , после чего следующей Ж БП 20 переводится в режим чтения. В соответствии с алгоритмом оче |едная МК задает режим расчета Yo (бЛок 109). Ее поля принимают следующие значения: поле 18,10 устанавливается в единицу, 18. 18, 18.3: 100; 18.8: 10; 18.18, 18.5: 101; 18.15: 1; 18. 18, 18. 18. 18. 18.19: 1.

На синхровходе БМУ 18 - логический ноль, разрешена выдача вычисляемых значений в БЗИ 26, на входы ре- . гистров 33 и 34 поступает информация с выходов соответственно БП 25 и БП 26, на один из входов сумматора 49 подключен регистр 39, регистр 35 через демультиплексар 13 подключен на вход коммутатора 52, БФА 17 не моди19143

фицирует адреса, разрешен переход к следующему значению Р по импульсу переполнения счетчика 41, на адресных входах БП 19 и 20 - содержимое счетчиков соответственно 40 и 41, на син- хровходах которых соответственно син

хроимпульс Tj и импульс переполнения счетчика 40.

На адрес 1ьк входах БП 19, 25 и 20 адреса, по которым на выходы блоков выбираются значения соответственно Ь{„, Vio и U;n . Параметр У;„ выбирает.jp, V jp и и-р . Параметр Vjp ся из БП 25 по адресу, формируемому БФА 11 на основе значения j (счетчик 40) и значения Р (счетчик 42). Параметры bjp и U;. выбираются по их относительным номерам (соответственно j и i) .в подмножестве для заданного Р, так как адреса записи указанных параметров и определялись как их относительные номера.

Таким образом, следующий синхроимпульс Т записывает в регистр 39 значение Ь-р, в регистр 33 - значение Vjp и в регистр 34 - значение , счетчик 40 увеличивает свое состояние на единицу и, следовательно, из БП 19 и 25 выбираются параметрыЬ и Vjp,, . Из БП 20 выбирается параметр .

Очередной синхроимпульс Т запиРассмотрим завершение цикла. Очередной импульс Т вызывает переполнение счетчика 41, записывает в регистр 39 последнее значение (по j) bjp, в регистр 34 - последнее (по i) значение и в регистр 33 - послед10 нее (по j) значение Vjp. ИмпуЛьс переполнения счетчика 41 устанавливает в единицу триггер 45, через элемент И 46 увеличивает содержимое счетчика 42 на единицу, а также запускает фор15 мирователь 58 импульсов. На синхро- вход ЕМУ 18 подключены синхроимпульсы Т . Очередной синхроимпульс Tj записывает в регистр 35 последнее высывает в регистр 35 значение

20 к появлению следующей МК на выходе БМУ 18, Сигнал с выхода формирователя 76, запущенного этим импульсом, записывает с БЗИ 26 последнее.вычисленное значение, после чего импyhьc

25 с выхода формирователя 58 модифицирует статус блоков 65 памяти БЗИ 26 (это обеспечивается соответствующей задержкой в формирователе 58 импульса с выхода элемента И 46). В очеред30 ной МК производится проверка окончания расчета по всем Р. Ее поля, принимают значения: 18. 18. 18.15:-0,- 18. 18. , АП адрес первой МК бловычисленное для j и ip , а в р егист- ка 102 . Б следующей КК заданы знары 39, 33 и 34 значения с выходов соответственно БП 19, 25 и 20 Вычисляется функция для JP+ 1 и ip. Аналогично рассчитываются значе- ния Tpij для заданного i и всех ,M/-1. Импульс переполнения счетчика 40 увеличивает состояние- счетчика 41 на единицу и далее расчет производится для всех , М -1 аналогично описан- ному. Ра.счет производится для всех , Mji-1; для каждого значения i расчитывается М, значений С , Запись результатов вычисления в БЗИ 26 производится следующим образом: информация с выхода регистра 35 через де- мультиплексор 13 и коммутатор 52 поступает на информационный вход БЗИ 26, на вход адреса записи которого через коммутатор 54 поступает адрес, фор40

45

50

чения: , АП адрес первой МК блока t04 ,

Если расчет для всех Р заверщен, то импульс переполнения счетчика. 42 установил в единицу триггер 44, т.е. и осуществляется переход на первую МК блока 102 и при поступлении очередного импульса Т, устройство работает аналогично описанному.

Если расчет не завершен, то и следующая Ж осуществляет переход на первую микрокоманду блока 104. Процесс повторяется

Формула изобретения

Устройство для вычисления матрицы функций, содержащее умножитель, сумматор, три регистра, блок микропрогмируемый БФА 15 и задержанный на ре- , .р. раммного управления, первый блок фор-,

J f,

гистрах 31 и 32, что обеспечивает соответствие адреса записи и записы ваемого значения; запись информации производится по синхроимпульсу Тз,

мирования адреса и два блока памяти, причем выход первого регистра подключен к входу первого сомножителя умножителя, выход, сумматора .подключен

20

проходящему через коммутатор 53 на вход строба записи БЗИ 26,

Рассмотрим завершение цикла. Очередной импульс Т вызывает переполнение счетчика 41, записывает в регистр 39 последнее значение (по j) bjp, в регистр 34 - последнее (по i) значение и в регистр 33 - последнее (по j) значение Vjp. ИмпуЛьс переполнения счетчика 41 устанавливает в единицу триггер 45, через элемент И 46 увеличивает содержимое счетчика 42 на единицу, а также запускает формирователь 58 импульсов. На синхро- вход ЕМУ 18 подключены синхроимпульсы Т . Очередной синхроимпульс Tj записывает в регистр 35 последнее вы0

5

0

чения: , АП адрес первой МК блока t04 ,

Если расчет для всех Р заверщен, то импульс переполнения счетчика. 42 установил в единицу триггер 44, т.е. и осуществляется переход на первую МК блока 102 и при поступлении очередного импульса Т, устройство работает аналогично описанному.

Если расчет не завершен, то и следующая Ж осуществляет переход на первую микрокоманду блока 104. Процесс повторяется

Формула изобретения

Устройство для вычисления матрицы функций, содержащее умножитель, сумматор, три регистра, блок микропрогмирования адреса и два блока памяти, причем выход первого регистра подключен к входу первого сомножителя умножителя, выход, сумматора .подключен

211

к информационному входу второго регистра, выход третьего регистра подключен к входу второго сомножителя умножителя, отличающееся тем, что, с целью повышения быстро- |действия, расширения функциональньрс возможностей, и области применения, в него введены три счетчика, девять ре- гистро.в, четыре блока формирования адреса, пять блоков памяти, блок запоминания информации, десять Мультиплексоров, демультиплексор, генератор тактовых импульсов, три триггера, элемент ИЛИ, три коммутатора, элемент И и три формирователя импульсов, причем первый выход генератора тактовых иьтульсов подключен к синхровхо- ду первого триггера, выход которого подключен к входу первого логического условия блока микропрограммного управления, вход второго логического условия которого подключен к выходу второго триггера, синхровход которого подключен к выходу переполнения первого счетчика, информационные входы первого и второго триггеров подключены к входу логической единицы устройства, второй выход генератора тактовых импульсов подключен к син- хровходам регистров с первого по пятый и к младшему разряду информационного входа демультиплексора, а таклсе через первьп формирователь импульсов - к первому управляющему входу первого блока памяти вход начальной установки устройства, подключен к входам начальной установки блока микропрограммного управления и генератора тактовых импульсов, В-й информацион- ньм вход группы устройства подключен к Р-му информационному входу первого мультиплексора, (,9), выход которого подключен к информационному входу первого блока памяти, второй управляющий вход которого соединен с выходом режима работы первого блока памяти блока микропрограммного управления, адресньй вход первого блока памяти соединен с адресным входом первого мультиплексора и с выходом адреса элемента матрицы А блока микропрограммного управления, выход первого блока паг4яти подключен к первому й нформа1;ионному входу второго мульти плексора, адресньй вход которого подключен к выходу адреса второго операнда блока микропрограммного управления, выхоц второго мультиплексора

0

5

0

5

96

5

17,22

11 Дклн1чен к 1нфop aп tc)HH( входу т. регмг. гра, (i;i умножителя подключен к входу первотч) - огтеранда сумматора, вхоп второго операнда которого подключен к выходу третьего мультиплексора, выход которого подключен к старшим разрядам информа- ijjioHHoro входа демультиплексора, адресный вход Kotoporo подключен к выходу адреса записи результата блока микропрограммного управления, старшие разряды выходов с первого по третий демультиплексора подключены соответственно к информационным входам шестого, седьмого и ВОСЬМОГО регистров, синхровходы которых подключены соответственно к младшему разряду первого, второго и третьего выходов демультиплексора, выходы регистров с meci oro по восьмой подключены соответственно к информационным входам с первого по третий четвертого мультиплексора, четвертьй информационный вход и выход которого подключены соответственно к вьтходу второго блока памяти и к информацион ному входу первого регистра, выходы второго и третьего счетчиков подключены соответственно к первому и второму входам первого блока формирования адреса, выход которого подключен к информационному входу четвертого регистра, выход которого подключен к информационному входу пятого регистра, выход первого счетчика подключен к первому входу второго блока формирования адреса, второй вход и выход которого подключены соответственно к выходу номера 0 компоненты вектора iTp блока микропрограммного управления и к адресному входу второго, блока памяти, первый и второй информационные входы третьего мультиплексора подключены соответственно к выходу второго регистра и к входу логического нуля устройства, выход третьего блока памяти подключен к пятому информационному входу четвертого мультиплексора, адресный вход которого подключен к первому выходу третьего блока формирования адреса, второй выход которого подключен к адресному входу третьего мультиплексора, третий информационный вход которого подключен к выходу девятого регистра, четвертый, пятьй и шестой выходы старших разрядов демультиплексора подключены соответственно к ин- формату онным входам третьего и чет0

5

5

0

1зе1 тог о блоков памяти и к иИформаци- OHiiONfy входу первого KOMNtyTaTopa, второй выход геГ.ератора тактовых импульсов подключен к первому входу четвертого блока формирования адреса, син- хровходу девятого регистра, первым информащтонным входам пятого и шестого мультиплексоров и к информационному входу второго коммутатора, выхо первого формирователя импульсов подключен к вторым управлягопщм входам третьего и четвертого блоков памяти, третий выход генератора тактовых импульсов подключен к первому информационному входу седьмого мультиплексора, выходы пятого, шестого и седьмого блоков памяти подключены соответственно, к второму, третьему и четвертому информационным входам второ- го -мультиплексора, выход пятого блока формирования адреса подключен к адресным входам пятого и шестого блоков памяти, первый выход четвертого блока формирования адреса подключен к адресному входу седьмого блока памяти, вход логического нуля устройства подключен к.вторым информационным входам пятого, шестого и седьмого fyльтиплeкcopoв, адресные входы которых подключены соответственно к полю задания периода синхроимпульсов для второго счетчика блока микропрограммного управления, выходу третьего триггера и к полю задания периода синхроимпульсов для третьего счетчика блока микропрограммного управления, выход шестого мультиплексора подключен к синхровходу блока микропрограммного управления, выход переполнения второго счетчика подключен к третьему информационному входу седьмого мультиплексора и к первоиу информационному входу восьмого мультиплексора, выход переполнения третьего счетчика подключен к первому входу элемента И и к второму информационному входу восьмого мультиплексора, выход которого подключен к первому входу элемента ИЛИ, второй вход и выход которого подключены соответственно к входу начальной установки устрой ства и к синхровходу третьего триггера, адресный вход восьмого мультиплексора подключен к полю задания источника запуска блока микропрограмм- ного управления выхода блока микропрограммного управления, информационный вход третьего триггера подключен

17 2.

к входу логической единицы устройства, поле задания управления выхода блока микропрограммного управления, через второй формирователь импульсов подключено к входу установки 13 О третьего триггера, поле ус тановки триггеров выхода блока MitKpo- программного управления подключено

к входам установки в О первого и второго триггеров, выход первого триггера подключен к входу установки в О первого счетчика, выход которого подключен к первому входу пятого

блока формирования адреса и к второму входу четвертого блока формирования адреса, третий, четвертый, пятый входы и второй выход которого подключены соответственно к входу угла поворота системы координат устройства, выходу третьего счетчика, полю установки в О триггера выхода блока микропрограммного управления и к первому входу третьего блока формирйвания адреса, Btopoti, третий и четвер- Tbtfi входы которого подключены соответственно к полям адреса первого операнда, управлением мультиплексором и признака модификации адреса первого

операнда выхода блока микропрограммного управления, поле разрешения перехода к следующему значению Р (Р - размер матрицы) выхода блока микропрограммного управления подключено к

второму входу элемента И, выход которого подключен к счетному входу первого счетчика и через третий формирователь импульсов к входу модификации статуса блоков памяти блока запоминания информации, выход седьмого мультчплексора подключен к счетному входу третьего счетчика и к синхровходу десятого регистра, выход которого подключен к первому информационному входу девятого мультиплексора, второй информационньп вход которого соединен с информационным входом десятого регистра и подключен к выходу третьего счетчика, выход девятого

мультиплексора подключен к адресному входу третьего блока памяти, первьй управляющий вход которого соединен с адресным входом девятого мультиплексора и подключен к полю режима

работы второго блока памяти выхода блока микропрограммного управления, выход пятого мультип. тсксора подклюен к счетному входу второго счетчиа и к синхровходам одиннадцатого и

25

двенадцатого регистров, выход второго -счетчика подключен к информационному входу одиннадцатого регистра,

первому информационному входу деся

того муль ; иплексора и к второму входу пятого блока формирования адреса, входы началкной установки счетчиков второго и третьего подключены к соответствующему полю выхода блока микро- программного управления, выход одиннадцатого регистра подключен к информационному входу двенадцатого регистра, выход которого подключен к второму информационному входу десятого мультиплексора, выход которого подключен к адресному входу четвертого блока памяти, первый управляюпщй вход которого соединен с адресным входом десятого мультиплексора и подключен к полю управления мультиплексором вы- .хода блока микропрограммного управления, выход четвертого блока памяти подключен к информационному входу девятого регистра, выход пятого регист- ра подключен к информационному входу третьего коммутатора, управляющие входы первого, второго.и третьего коммутаторов подключены к полю- управления выдачей результатов в блок за- поминания информации выхода блока микропрограммного управления, вьпсоды первого, второго и третьего коммута- .торов подключены соответственно к информационному входу, входу строба за- писи и входу адреса записи блока запоминания информации,, входы строба чтения, адреса чтения и выход которого подключены соответственно к входам строба чтения информации и адреса счи тывания устройства и к информационному выходу устройства, вход начальной установки устройства- подключен к входу начальной установки блока запоминания информации, причем блок запоми- нания информации содержит группу блоков памяти, две группы мультиплексоров, группу коммутаторов, группу элементов 2И-Ш1И, группу схем сравнения, группу регистров, группу элементов ИЛИ, дешифратор, счетчик по модулю М,,+ 1, три формирователя импульсов, причем информационные входы блоков памяти группы подключены к информационному входу блока, входы модифи- кации статуса блоков памяти блока подключены к счетному входу счетчика по модулю Mj+l и через первый форо

IQ1520 25ЗО540 45go gg 3961726

мирователь импульсов блока - к син- хровходам регистров группу, старшие разряды входа адреса чтения блока Г1од- ключены к первым входам схем сравнения группы, выход счетчика по модулю Мз+1 подключен к входу дешифратора, М-й выход которого подключен к первому входу М-Го и к второму входу (M+1)mod(M3- -1)l-го элементов ИЛИ группы (, ) , к первому управляющему входу М-го блока памяти труппы, адресному входу М-го мультиплексора первой группы, управляющему входу М-го коммутатора группы, первому входу первой группы входов М-го элемента 2И-ШШ группы, адресному входу М-го мультиплексора второй группы, вы ход которого подключен к информационному входу М-го регистра группы, выход которого подключен к первому информационному входу (M+1)mod(Mj+1 )| - го мультиплексора второй группы, второму информационному входу(М-1) mod (Mj-b1)-ro мультиплексора второй группы, второму входу М-й схемы сравнения группы, выход которой подключен к первому входу второй группы входов М-го элемента 2И-ИЛИ, выход которого подключен к второму управляющему входу М-го блока памяти группы, выход М-го элемента ИЛИ группы подключен к входу выборки М-го регистра группы, вход; начальной установки блока подключен к входам начальной установки разрядов регистров группы и счетчика по модулю Мз+1 в соответствии с требуемым начальным состоянием, вход стро- ба чтения блока через второй формирователь импульсов блокаг,подключен к вторым входам второй группы входов элементов 2И-1ИЛИ, вход строба запи- |си блока через третий формирователь импульсов блока подключен к вторым входам первой группы входов элементов 2И-ИЛИ, вход адреса записи блоки подключен к первым информационным входам мультиплексоров первой группы, вторые информационные входы мультиплексоров первой группы.подключены к младшим разрядам входа адреса чтения блока, выход М-го мультиплексора первой группы подключен к адресному входу М-го блока памяти группы, выход которого подключен к информационному входу М-го коммутатора, выход которого подключен к информационному входу блока.

Проверка логических условий (ЛУ) ПрЛУ

Адрес перехода (АП)

БП 24 (1)

18,2Адрес элемента

матрицы А

18,3 , Адрес первого операнда (без модификации)

18,4 Адрес второго операнда

18,5 Адрес записи результата

18,6 Режим работы БП 0

18,7, Режим работы БП 19

- выбирается следующая МК

- выбирается МК, адрес которой задан в адресе перехода (АП)

проверка ЛУ А с

триггера 43

проверка ЛУ К с

триггера 44

Внутреннее поле БМУ

Код АП

0-чтение, 1-записьВход 3/4т БП :24

адреса (0-8)

РгЗб Рг37 Рг38 БП23 БП20

Адресные входы БП 24 и мультиплексора 10

1-й вход БФА 17

БП 24 БП 22 БП 21 БП 25

Адресный вход мультиплексора 8

РгЗб

Рг37

Рг38

БП 19

БП 20

на БЗИ26 (через коммутатор 52)

Адресный вход де- мультиплексора 13

Вход 3/4т БП 20, адресньш вход мультиплексора 4

Вход 3/4т БП 19, адресный .вход мультиплексора 3

8,8 Управлет е мультиплексором 7 ,(без модифика1Ц1и)

Управление вьщачей результатов в БЗИ 26

Задание режима управления

Задание периода синхроимпульсов ст-тетчика 41

Задание периода синхроимпульсов счетчика 40

Установка в ноль счетчиков 40 и 41

Установки триггеров 43 и 44

Разрешение перехода к следующему значению Р

Номер компоненты вектора Пр

01 - на выходе муль,типлексора 7

код О

00 - содержимое регистра 35

10 - содержимое регистра 39

0- вьщача разрешена

1- выдача запрещена

0- управление от

БМУ 18

1- аппаратное

00 - на счетном входе счетчика 41 логический ноль

01 - на счетном входе синхроимпульсы

Тг. 10 - на счетном входе

счетчика 40 импульсы переполнения счеучика 41

0- на счетном входе

Логический ноль

1- на счетном входе

синхроимпульсы Tj

0- пассивньш

1- активньй

0- переход запрещен

1- переход разрешен

00 - Пр, 01 - пр , 10 - npj

18,17 Установка в ноль триггера 89

18,18, Признак модификации адреса первого операнда

2-й вход БФА 17

Управляющие входы коммутаторов 52-54

Вход формирователя 56

Адресньй вход мультиплексора 2

Адресный вход мультиплексора 1

пассивньш

активньй

переход запрещен

переход разрешен

Установочные входы счетчиков 40 и 41

Установочные.входы триггеров 43 и 44

Вход ЭтПемента И 46

00 - Пр, 01 - пр , 10 - npj

1-й вход БФА 16

0- пассивньй Вход формирователя

1- активный уровень 90 БФА 14

адрес не модифии1Ируется

адрес моди(Ьицируется

3-й вход БФА 17

сигнал переполнения счетчика 4Х)

сигнал переполнения счетчика 41

Адресный вход мультиплексора 5

eSZ

ess

w дл/

em V

c7J.2

ГтгТ}

j I «

7M

W

«J ГЯЯ, 7i.M,ff

czo

42 установлен в ноль

На Sit

SSJIytj

таг

тяг

Mr J

f c/ вход)

cwt

-77.5

НаПНу

(2ч/ fxoffJ

Фие.г

a ; J

у

.ПОЛЯ

CS9

Г. 8 .Л

5

80

CS

с Je.20

Фи

сиз

с 18.8

Фие.5

Фие.6

95

98

На 9

96

97

На 7

с 18,18 фие. 7

Фиг.8

СЮ

| Устройство умножения матрицы на вектор | 1984 |

|

SU1226484A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Юэн Ч | |||

| и др | |||

| Микропроцессорные системы и их применение при обработке сигналов | |||

| М.:, 1986, с.237, - рис,7.14. | |||

Авторы

Даты

1988-11-23—Публикация

1987-03-23—Подача