W 27 28 3

S5 3J

52.

S4

t

(Л

4

со

СО

а

00

Фие.}

с S3

I J

управления, блоки 19-24 памяти, счетный триггер 25, блок 26 запоминания информации, регистры 27-39, счетчики по модулю М 40,- по модулю Mj 41, по модулю Mj 42, триггеры 43-45, элемент И 46, элемент ,ИЛИ 47, сумматоры 48,-49, умножитель 50, генератор 51 тактовых импульсов, коммутаторы 52-54, вычитатель 55, формирователи

143

I J

1439618

56-58 импульсов, вход 59 начальной установки устройства, вход 60 информационных входов устройства, входы адреса считьтания 62,.строба чтения 63 устройства, информацион}Шй выход 64 устройства. Поставленная цель достигается за счет структурно-алгоритмических решений, реализованных в устройстве, 9 ил,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Вычислительное устройство | 1987 |

|

SU1432511A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для формирования широкополосного случайного процесса | 1986 |

|

SU1432514A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных системах о Целью изобретения является повышение быстродействия, расширение функциональных возможностей и области применения Устройство содержит мультиплексоры 1-12, демуль- типлексор 13,- блоки 14-17 формирования адреса, блок 18 микропрограммного

1

Изобретение относится к области вычислительной техники и может быть использовано в специализированных вычислительных системах о

Целью изобретения является повышение быстродействиЯр расширение функциональных возможностей и области применениЯо

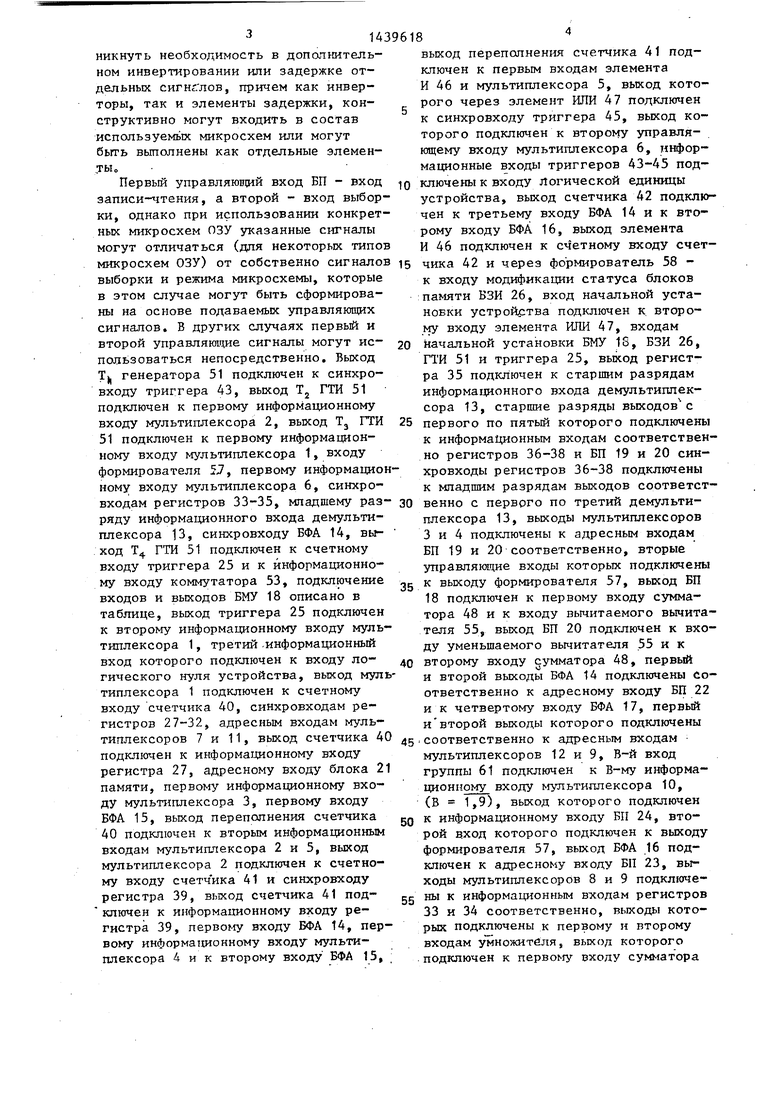

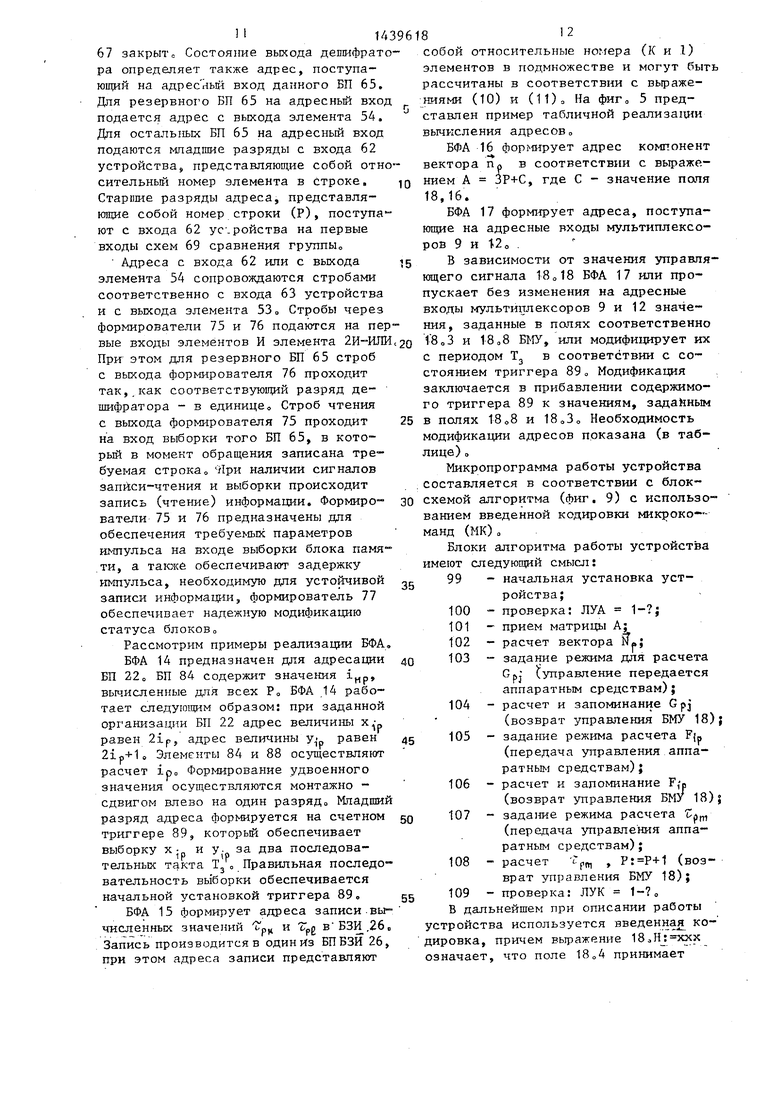

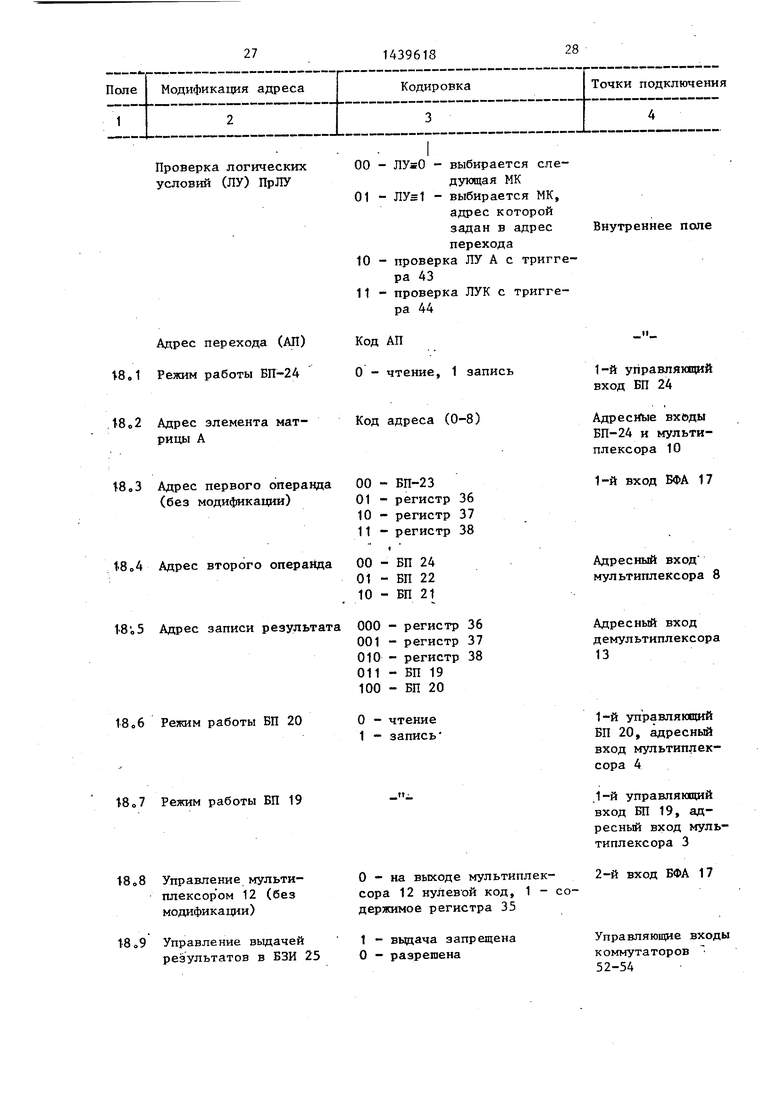

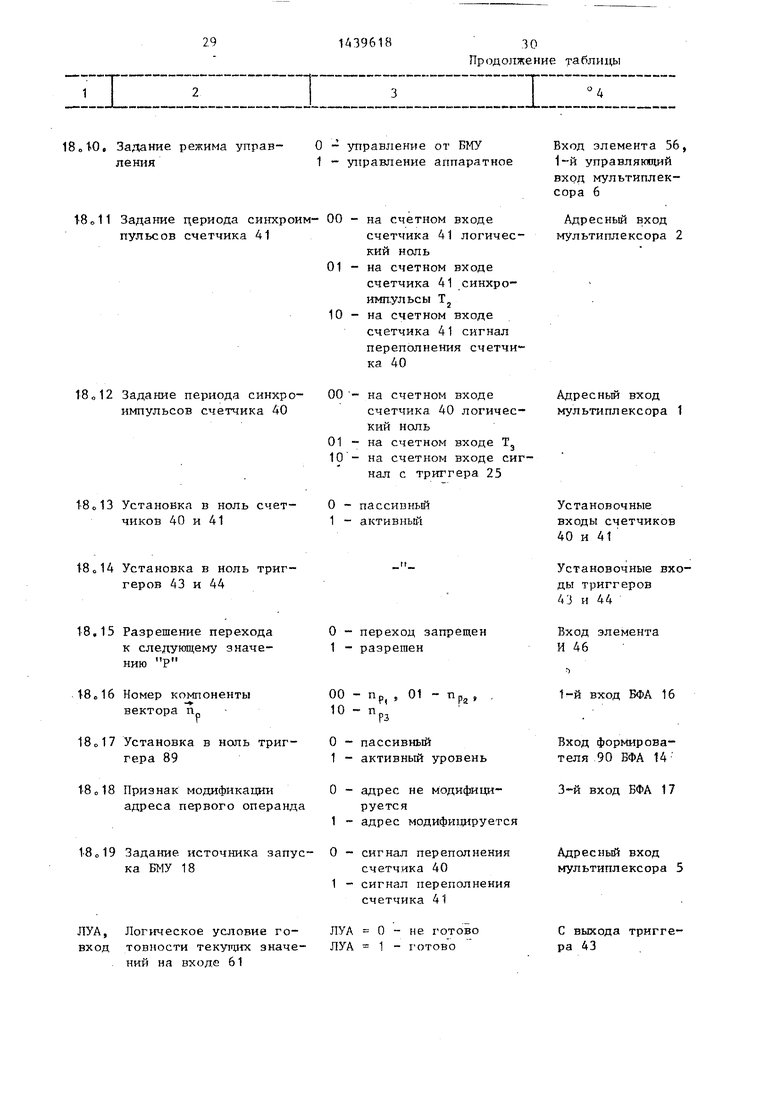

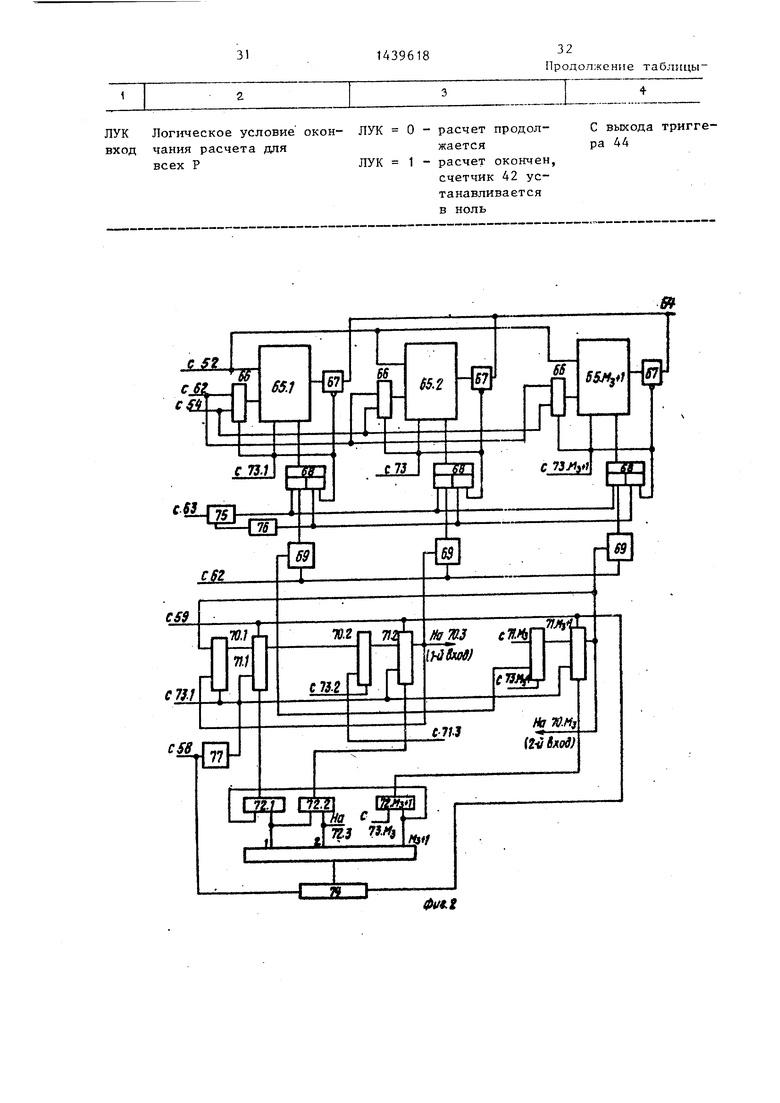

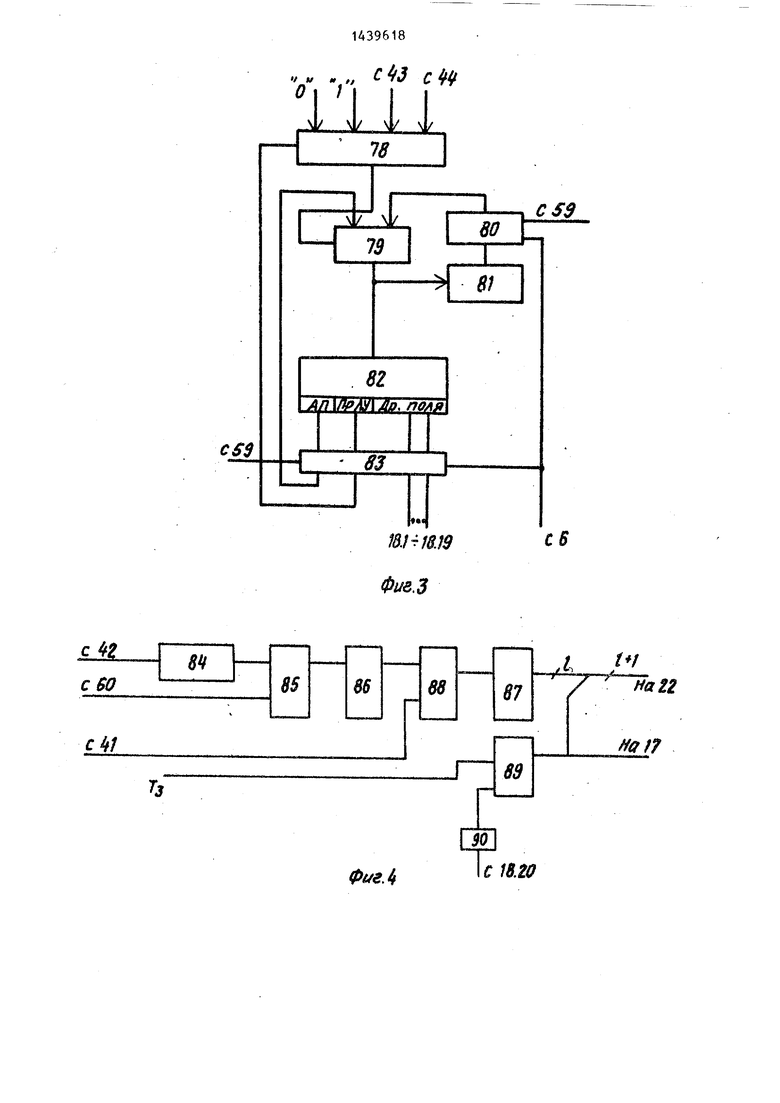

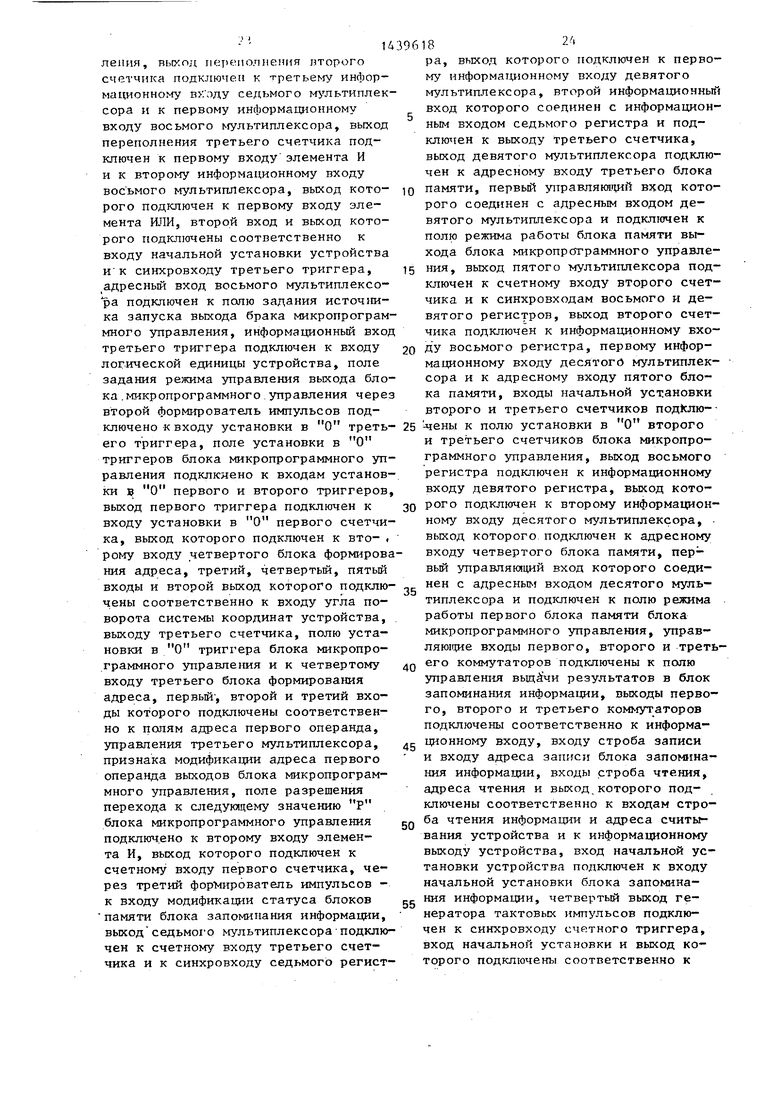

На фиг о 1 представлена функциональ ная схема устройства; На фиг.2 - функциональная схема блока запоминания информации; на фиг„ 3 - блок микропрограммного управления; на фигс,4- 7 - блоки формирования адреса; на

фиг о 8 - временная диаграмма работы генератора тактовых импульсов; на фиг о 9 - блок-схема алгоритма работы устройства

Устройство содержит мультиплексо- ры 1-12, демультиплексор 13, блоки 14-17 формирования адреса, блок 18 микропрограммного управления (БМУ), блоки 19-24 памяти,(БП), счетный . триггер 25, блок 26 запоминания инфор мации (ВЗИ), регистры 27-39, счетчик 40 по модулю М, счетчик 41 по моду лю Mj, счетчик 42 по модулю М, триггеры 43-45, элемент И 46, элемент ИЛИ 47, сумматоры 48 и 49, умножи- тель 50, генератор 51 тактовых импульсов (ГТИ), коммутаторы 52-54, вычитатель 55, формирователи 56-58 импульсов, вход 59 начальной установки устройства, вход 60 угла поворота систе- мы координат устройства, группа 61 информационных входов устройства, вход 62 адреса считывания устройства, вход 63 строба чтения информации устройства, информационный выход 64., устройства БЗИ содержит группу БП 65

группу мультиплексоров 66, группу ком- мутаторов 67, группу элементов 2И-ИЛИ 68, группу схем 69 сравнения (количество элементов в каждой группе равно ), мультиплексоры 70е1-70оМз+ группы, регистры 71о1-71оМз+1 группы элементы ИЛИ 72о1-72.Мз+1 группы, дешифратор 73 с выходами 73.1-73,Мэ+1, счетчик 74 по модулю Mg+l, формирова тапи 75-77 импульсов.

БМУ содержит мультиплексоры 78 и 79, регистр 80, узел 81 приращения, блок 82 памяти микрокоманд,- регистр 83 микрокоманд

Блок 14 формирования адреса (БФА) содержит блок 84 памяти, вычитатапь 85, узлы 86 и 87 свертки по модулю N4, сумматор 88, триггер 89, формирователь 90 импульсов.

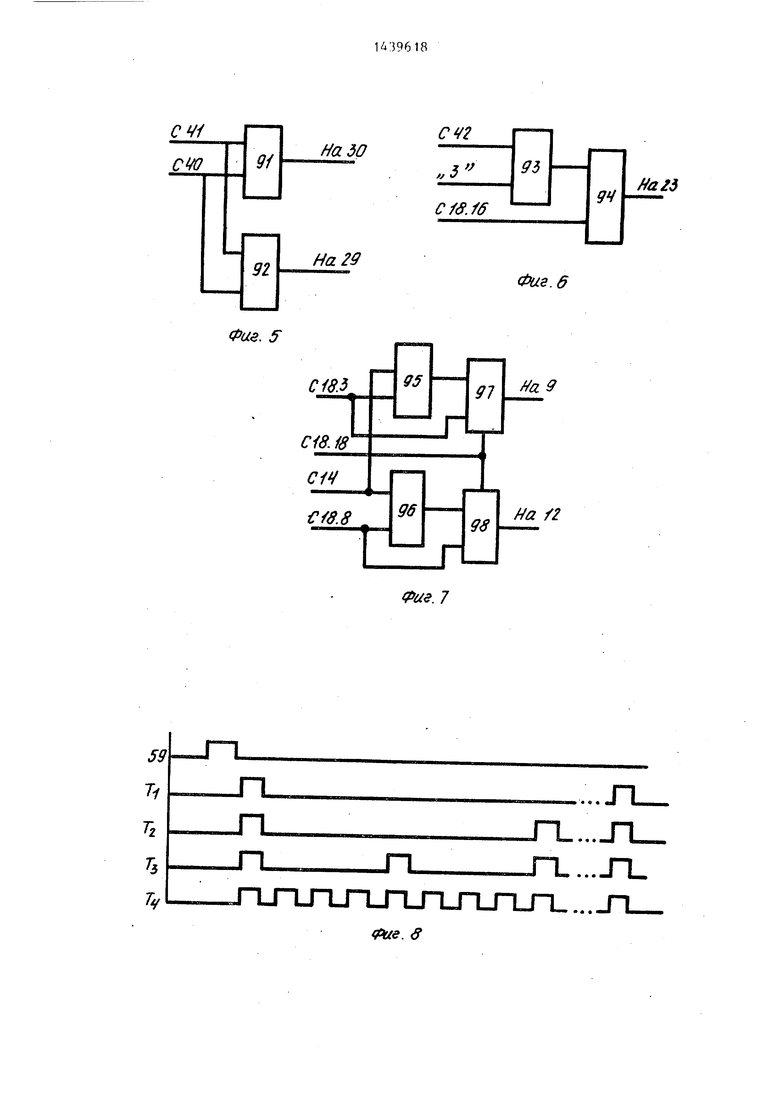

БФА 15 содержит БП 91 и 92„

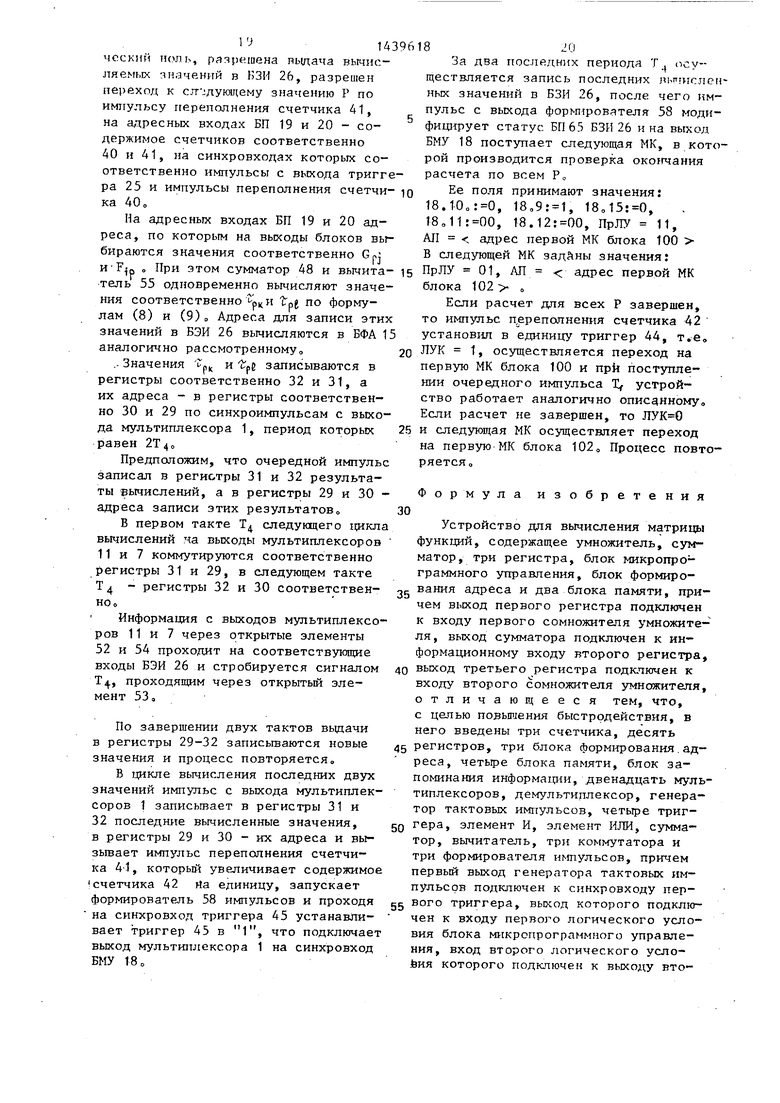

БФА ,16 содержит умножитель 93 и сумматор 94

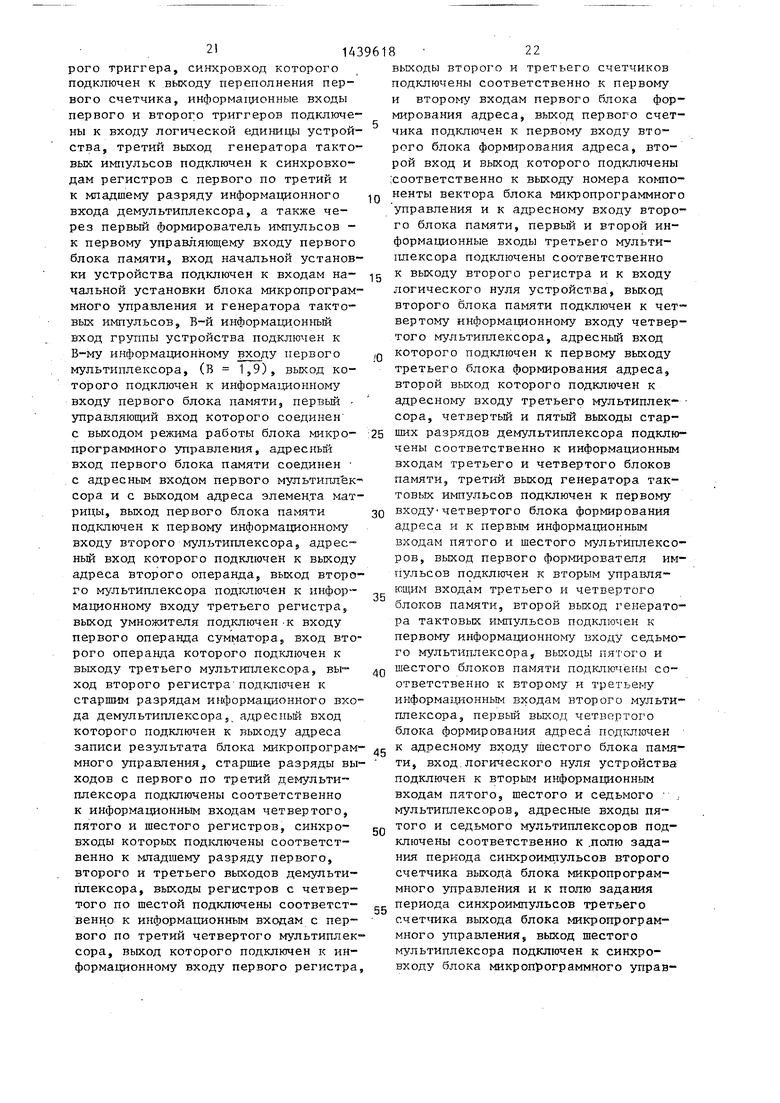

БФА 17 содержит сумматор 95, сумматор 96 по модулю 2 и мультиплексоры 97 и 98.

Узлы свертки по модулю М могут быть выполнены на базе сумматора по модулю М с нулевым сигналом на втором входе или на базе ПЗУ, при конкретной реализации некоторые элементы, например 87 и 88, могут быть объединены, узел 81 может бьп-ь реализован на базе сумматора, коммутаторы могут быть реализованы, например, на базе трехстабильных элементов К155ЛП8, причем их разрядность опре- деляется разрядностью передаваемой информации.

При реализации устройства на конкретной элементной базе может возникнуть необходимость в дополнительном инвертировании или задержке отдельных сигналов, причем как инверторы, так и элементы задержки, конструктивно могут входить в состав используемьк микросхем или могут быть вьшолнены как отдельные элементы

Первый управляющий вход БП - вход записи-чтения, а второй - вход выборки, однако при использовании конкретных микросхем ОЗУ указанные сигналы могут отличаться (для некоторых типов

микросхем ОЗУ) от собственно сигналов 15 чика 42 и через формирователь 58 выборки и режима микросхемы, которые в этом случае могут быть сформированы на основе подаваемых управляющих сигналов, В других случаях первьй и второй управляклцие сигналы могут ис- пользоваться непосредственно. Выход Т|1 генератора 51 подключен к синхровходу триггера 43, выход Т ГТИ 51 подключен к первому информационному входу мультиплексора 2, выход Т ГТИ 51 подключен к первому информационному входу мультиплексора 1, входу формирователя 57, первому информационному входу мультиплексора 6, синхрок входу модификации статуса блоков памяти БЗИ 26, вход начальной установки устройх:тва подключен к. второму входу элемента ИЛИ 47, входам начальной установки БМУ 18, БЗИ 26, ГТИ 51 и триггера 25, выход регистра 35 подключен к старшим разрядам информационного входа демультиппек- сора 13, старшие разряды выходов с первого по пятый которого подключены к информационным входам соответствен но регистров 36-38 и БП 19 и 20 син- хровходы регистров 36-38 подключены к младшим разрядам выходов соответст

входам регистров 33-35, младшему раз- зо венно с первого по третий демульти- ряду информационного входа демульти- плексора 13, синхровходу БФА 14, вы- ход Т ГТИ 51 подключен к счетному входу триггера 25 и к информационному входу коммутатора 53, подключение входов и выходов БМУ 18 описано в таблице, выход триггера 25 подключен к второму информационному входу мультиплексора 1, третий -информационный вход которого подключен к входу логического нуля устройства, выход мультиплексора 1 подключен к счетному входу счетчика 40, синхровходам регистров 27-32, адресным входам мультиплексоров 7 и 11, выход счетчика 40 g подключен к информационному входу регистра 27, адресному входу блока 21 памяти, первому информационному входу мультиплексора 3, первому входу БФА 15, выход переполнения счетчика 40 подключен к вторым информационным входам мультиплексора 2 и 5, выход мультиплексора 2 подключен к счетному входу счетч ика 41 и синхровходу регистра 39, счетчика 41 подключен к информационному входу регистра 39, первому входу БФА 14, первому информационному входу мультиплексора Дик второму входу БФА 15, ;

плексора 13, выходы мультиплексоров 3 и 4 подключены к адресным входам БП 19 и 20 соответственно, вторые управляклдие входы которых подключены

35 к выходу формирователя 57, выход БП 18 подключен к первому входу сумматора 48 и к входу вычитаемого вычита теля 55, выход БП 20 подключен к вхо ду уменьшаемого вычитателя 55 и к

40 второму входу сумматора 48, первый и второй выходы БФА 14 подключены Со ответственно к адресному входу БП 22 и к четвертому входу БФА 17, первьй и второй выходы которого подключены соответственно к адресным входам мультиплексоров 12 и 9, В-й вход группы 61 подключен к В-му информа- ционному входу мультиплексора 10, (В 1,9), выход которого подключен к информационному входу БП 24, второй вход которого подключен к выходу формирователя 57, выход БФА 16 подключен к адресному входу БП 23, выходы мультиплексоров 8 и 9 подключены к информационным входам регистров 33 и 34 соответственно, выходы которых подключены к первому и второму входам умножителя, выход которого подключен к первому входу сумматора

50

55

выход переполнения счетчика 41 подключен к первым входам элемента И 46 и мультиплексора 5, выход которого через элемент ИЛИ 47 подключен к синхровходу триггера 45, выход которого подключен к второму управляющему входу мультиплексора 6, информационные входы триггеров 43-45 под- ключенык входу логической единицы устройства, выход счетчика 42 подключен к третьему входу БФА 14 и к второму входу БФА 16, выход элемента И 46 подключен к сметному входу счетк входу модификации статуса блоков памяти БЗИ 26, вход начальной установки устройх:тва подключен к. второму входу элемента ИЛИ 47, входам начальной установки БМУ 18, БЗИ 26, ГТИ 51 и триггера 25, выход регистра 35 подключен к старшим разрядам информационного входа демультиппек- сора 13, старшие разряды выходов с первого по пятый которого подключены к информационным входам соответственно регистров 36-38 и БП 19 и 20 син- хровходы регистров 36-38 подключены к младшим разрядам выходов соответст венно с первого по третий демульти-

венно с первого по третий демульти-

плексора 13, выходы мультиплексоров 3 и 4 подключены к адресным входам БП 19 и 20 соответственно, вторые управляклдие входы которых подключены

к выходу формирователя 57, выход БП 18 подключен к первому входу сумматора 48 и к входу вычитаемого вычита- теля 55, выход БП 20 подключен к входу уменьшаемого вычитателя 55 и к

второму входу сумматора 48, первый и второй выходы БФА 14 подключены Соответственно к адресному входу БП 22 и к четвертому входу БФА 17, первьй и второй выходы которого подключены соответственно к адресным входам мультиплексоров 12 и 9, В-й вход группы 61 подключен к В-му информа- ционному входу мультиплексора 10, (В 1,9), выход которого подключен к информационному входу БП 24, второй вход которого подключен к выходу формирователя 57, выход БФА 16 подключен к адресному входу БП 23, выходы мультиплексоров 8 и 9 подключены к информационным входам регистров 33 и 34 соответственно, выходы котоых подключены к первому и второму входам умножителя, выход которого одключен к первому входу сумматора

514

49, выход которого подключен к информационному входу регистра 35, выход которого подключен к первому информационному входу мультиплексора 12, второй информаищонньй вход и выход которого подключен соответственно к входу нулевого кода устройства и к второму входу сумматора 49, выходы коммутаторов 52-54 подключены соот- ветственно к входам информационному, строба записи и адреса записи БЗИ 26, входы строба чтения, адреса чтения и выход которого подключены соответственно к входам 63 и 62 и выходу 64 устройства о

Выход коммутатора 52 подключен к информационным.входам БП 65, выходы которых через коммутаторы 67 под- ключены к выходу 64 устройства, выход элемента 54 подключен к первым информционным входам мультиплексоров 66, выходы которых подключены к адресным входам соответствующих БП 65, первьй управляющий вход М-го БП 65 подключен к М-му выходу дешифратора 73 и соединен с управляющим входом М-го коммутатора 67 и адресным входом М-го мультиплексора 66, а также с первым вхо- дом первой группы входов М-го элемента 2И-ИЖ, выход которого подключен к второму управляющему входу М-го БП 65, , Mg+l, первьш вход второй группы М-го элемента 2И-ИЛИ подклю- чен к выходу М-й схемы 69 сравнения, вторые входы схем 69- сравнения подключены к входу 62 устройства (старшим разрядам), младшие разряды входа 62 устройства подключены к вторым информационным входам мультиплексоров 65, выход счетчика 74 подключен к входу дешифратора -735 М-й выход которого подключен к первому входу М-го и второму входу(М+1) mod (М,, + 1)}-го элементов ИЛИ 72 и к адресному входу М-го мультиплексора 70, выход М-го элемента ИЛИ 72 подключен к входу выборки М-го регистра 71, входы начальной установки разрядов которого подключены к входу 69 устройства в соответствии с требуемым начальным состоянием, выход формирователя 58 подключен к счетному входу счетчика 74 и через формирователь 77 - к син- хровходам регистров 71, выход М-го мультиплексора 70 подключен к информационному входу М-го регистра 71, выход которого подключен к второму

18 6

входу М-й схемы 69 сравнения, первому ,инфор/ ационному входу (M-t-1) mod (Mj + OI-ro мультиплексора 70 и к второму информационному входу f(M-1) :-mod (Mjj + DJ-ro мультиплексора 70, вход 63 устройства через формирователь 75 подключен к вторым входам второй группы элементов 68, выход элемента 53 через формирователь 76 подключен к вторым входам первой группы элементов 68, вход 59 устройства подключен к входам начальной установки разрядов счетчика 74,

Допустим.в пространстве заданы некоторая основная система координат (ОСК) и вращакщаяся система координат (век), которая получается из ОСК путем -вращения ОСК вокруг осей ОХ, OYnOZ, причем положение IJCK относительно ОСК описывается следуюпщм образом: повернем ОСК на угол Ф вокруг оси OZo Получившуюся систему координат обозначим пек - повернутая система координат, пек задает положение, относительно которого совершаются непрерывные колебания ЪСК (т„ео по- вороты на небольшие углы вокруг осей ОХ, OY и OZ пек), которые описываются матрицей вращений А, связывающей ОСК и век, в ОеК задано множество из М,

векторов п (пр, Пр,, Пр), где Т - символ транспортирования;. 0, . С век жестко связано множество из N точек, например, принадлежапц1Х поверхности цилиндра, образующие которого (столбцы) параллельны оси OZ ВСКо В ряде специальных задач для каждого Р требуется рассчитать N функций:

Т рт П рАГ

Мр

(1)

где г

„р - радиус - вектор Гор-и точки в ВСК; тр является функцией от Р и m m О, - относительный номер тр-й точки в Р-м подмножестве точек. Совокупность функций tpm, рассчитанных для Р О, Mj-1 ит О, N„-1, образует матрицу функций Т („с,) размерности ,,, причем для расчета каждой строки матрицы Т требуется формирование подмножества из N., век2ftI

-Ч

торов г

(

в соответствии со следующими соотношениями о

Предполагается, что множество из N точек образовано совокупностью из М д столбов по NC, точек в каждом, причем угол между соседними столбами равен Д и начало координат ВСК

71439618

расположено симметрично отяоситепьно элементов столба Подмножество из точек для заданного Р образуется совокупностью из Mj столбов (тое. N MjNj.). таким, что

N

Gpj

p (()inodM4+i)modM (2) F

P де 1

P

15

-номер столба, входящего IQ в состав Р-го подмножества;

-относительный номер данного столба в Р-м подмно- жестве, i О,

-начальное смещение по i для заданного Р, рассчитанное для Т 0;

ф/д Q J - значение, поступающее с входа 60 устройства, которое задается, например, при настройке устройства.

ся

нр

то оп

20

К

Параметр i,,,, рассчитьшается зара -нрнее и хранится в БП 84., Величина i

Р

может принимать значения от О до Мд.-1о Таким образом, рассчет по формуле (2) позвог,яет для любого Р сфор- миррвать подмножество из Nf, векторов

Р 25

При i О, Mj-1 и j О, М,-1

параметры К и 1 в совокупности покрывают все множество значений m

г , необходимое для вычисления Р-Й

ВСКс

В этом случае выполняются соотношения

.р

. 0,Nn-1 ,т.е. по формулам (10) или (11) 30 можно рассчитать относительный номер ст)оки матрицы То любой точки подмножества.

Пусть Кр-й элемент является j-M Предлагается следующий алгоритм элементом ip-x-o столба,, а 1р-й эле- расчета мат)ицы Т

мент - элементом ip-ro столба, симмет- Расчет Np по формуле (5) и запись ричным j-му относительно начада коор- 5 компонент Np , Nр и Nр в регистры динат по оси 07. ВСК 36-38 соответственно

Расчет О pi по формуле (6) для всех j О, М,-1 ( 0) и запись результатов в БП 19 о

4Q Расчет F,-p ро формуле (7) для всех i С, M,j-1 (всех столбов Р-го подмножества) и запись результатов в БП 20,, Расчет tpn и tpg по формулам (8) и (9) и запись результатов в БЗИ 26. 45 Повторение перечисленных расчетов для всех Р О, Mj-lo

Вычисления в указанной последовательности осуществляются периодически после записи текущих значений матрицы А с входов 61 устройства в БП 24. Рассмотрим функциональное назначение блоков памяти, входящих в состав устройства,

БП 19 предназначен для запомина- gc ния величин Rpj , вычисленных в соответствии с (6) для заданного Р. Его объем - М( слов о

БП 20 предназначен для запомина(xjpYjp z-j) ;(3)

р у;р Р

где X. , у, - декартовы координаты столба в ВСК, значения которых зави сят от i и Р; ZJ - декартова координата j-ro элемента столба; -zj - декартова координата элемента столба, сим- метрш ного j-му относительно начала коор- динат по оси OZ ВСКо

50

Параметр j

Nc 2

, если N четное и М

О, М,-1,-где М,

()72,

если N. - нечетное,

С

Введем обозначения

nf-A (Np,

Np,, Np);

Np,

(5) (6) (7)

С учетом (1) и (3)-(7) выполняются соотношения

(8)

рк F;p + Gpj ;

/V

ре FI P - Gpj

(9)

15

Относительные номера Кр-й и 1в-й точек в Р-м подмножестве могут быть определены по формулам

20

К

iNp + М - 1 + J, N - нечетное;

(10)

iN + М, + J,

N - четное

1 iN, + М, - 1 - j .

(11)

25

При i О, Mj-1 и j О, М,-1

параметры К и 1 в совокупности покрывают все множество значений m

50

ния величины F , пьмисленной в соответствии с (7) для заданного Р,, Его объем - Mj слово

БП 21 предназначен -для хранения величин ZJ для j. О, М,-1, Тов. для хранения неотрицательных компонент Его объем - М, слов.

БП 22 предназначен для хранения величин и для всех ip . 0,Mq-1 .Объем БП 21 равен 2М/( слов. Комтоненты Х и у. располагаются в двух последовательных ячейках памяти о

БП 23 предназначен для хранения векторов йр для всех Р О, M,j-1o Его объем равен ЗМ слов о Компоненты вектора для заданного Р располага ются в памяти в трех последовательных ячейках,

БП 24 предназначен для запоминания значений элементов матрицы А, его объем - 9 слов. Элементы матри- цы могут.быть записаны, например, по столбцамо

БЗИ 26 предназначен дпя записи, хранения и выдачи значений (Р О, Mj-l, m О, Nri-Do Конструкция БЗИ 26 позволяет осуществлять одновременную запись новых (соответ- ствуюпщх новому значению матрицы А) величин и считьтание ранее вы численных (старых) значений pni для любого Ро

БП 19, 20 и 24 представляют собой ОЗУ, БП 21-23 могут быть реализованы на ПЗУ (или ОЗУ в режиме )

БЗИ 26 состоит из БП 65 объемом по NP, слов.

Каждый БП 65 одержит Nf, значений (т О, ) для некоторого Р (т„ее некоторую строку матрицы Т) При этом в любой момент времени М БП 65 работают в режиме чтения и из них могут быть

считаны значения т:.

fni

для Р

40 ратора 73 - единичный, что обеспе вает выбор1ш тех регистров 71 гр пы, информация в которых должна б изменена и задает режим коммутаци мультиплексоров 70 группы При ло

0,M.j-15соответствующие старому значению матрицы АО Один из БП 65 находит- 45 ческой единице на адресном входе

ея в режиме записи (резервный блок) и в него записываются новые, Тое вычисляемые для принятого в данном периоде Т, значения матрицы А, значе™ ния , для некоторого Р„ В течение периода Tj происходят вычисление и

мультиплексора 70оМ на его выходе содержимое регистра 71оМ+1, иначе регистра 71оМ-1 (сложение и вычит ние по mod(Mj+1)o Информация в ре 50 гистры записывается по сигналу с хода формирователя 77 импульсов,,

Рассмотрим теперь вопросы управления записью и чтением информации, Режим работы М-го БП определяется

запись в БП 65 значений 7ргп для всех Р О, Mj-1o В процессе работы статус резервного поочередно присваивается каждому из БП 65. С каждым БП 65 55 .состоянием М-го выхода дешифратора: группы связан один из регистров 71 О - чтение 1 - запись, хфи этом на группы, в котором указан номер (Р) выход 64 устройства могут быть подклю- строки матрицы Т, элементы которой чены только блоки, работагацие в режиме записаны в данном БП 65 в момент об- чтения. Для резервного блока элемент

1439618

10

ращения при коде резервного блока, который указьшает, что в этот блок

записываются вычисляемые значения / -рт

На вход счетчика 75 БЗИ 26 поступают импульсы, поступление которых означает, что очередная строка матрицы Т вычислена и записана в резервный БП 65„ По этим импульсам происходит модификация статуса БП 65 по следзтощему алгоритму: пусть в резерв- ньй БП 65 в данном цикле записываются элементы Р-й строки матрицы Т (в этом

же цикле одновременно могут быть считаны старые значения элементов Р-й строки матрицы Т из некоторого БП 65 с номером Р в соответствующем регистре 71). По окончании записи

элементов Р-й строки в резервньй

БП 65 ( в следукщем цикле) в регистр 71, соответствзтощий этому БП65, записывается код Р, Тоес при обращении к элементам Р-й строки информация считывается из этого блока, БП 65, в котором записаны старые значения элементов Р-й строки матрицы А, приобретает статус резервного (в соответствующий регистр 71 записывается код PZ) и в него записьшают- ся элементы (P+DmodM строки матрицы То Такая замена осуществляется циклически для всех Р, правильная синхронизация обеспечивается тем,

что импульс модификазщи статуса БП 65 вырабатывается при поступлении импульса с выхода элемента И 46, по которому Р (P+OmodM. Для резервного БП 65 соответствующий выход дешиф-

ратора 73 - единичный, что обеспечивает выбор1ш тех регистров 71 группы, информация в которых должна быть изменена и задает режим коммутации мультиплексоров 70 группы При логической единице на адресном входе

мультиплексора 70оМ на его выходе - содержимое регистра 71оМ+1, иначе - регистра 71оМ-1 (сложение и вычитание по mod(Mj+1)o Информация в ре- 0 гистры записывается по сигналу с вьН хода формирователя 77 импульсов,,

Рассмотрим теперь вопросы управления записью и чтением информации, Режим работы М-го БП определяется

114

67 закрыто Состояние выхода дешифратра определяет также адрес, поступающий на адрес ньй вход данного БП 65. Для резервного БП 65 на адресньй вхо подается адрес с выхода элемента 54. Дпя остальных БП 65 на адресный вход подаются младшие разряды с входа 62 устройства, представляющие собой отн сительный номер элемента в строке, Стариме разряды адреса, представляющие собой номер строки (Р), поступают с входа 62 ус -ройства на первые входы схем 69 сравнения группы,

Адреса с входа 62 или с выхода элемента 54 сопровождаются стробами соответственно с входа 63 устройства и с выхода элемента 53„ Стробы через формирователи 75 и 76 подаются на первые входы элементов И элемента 2И-ИЯИ При этом для резервного БП 65 строб с выхода формирователя 76 проходит так,,как соответствующий разряд дешифратора - в единице,, Строб чтения с выхода формирователя 75 проходит на вход выборки того БП 65, в который в момент обращения записана требуемая строка наличии сигналов записи-чтения и выборки происходит запись (чтение) информации. Формиро- ватели 75 и 76 предназначены для обеспечения требуемых параметров импульса на входе выборки блока памяти, а так.же обеспечивают задержку импульса, необходимую для устойчивой записи информации, формирователь 77 обеспечивает надежную модификацию статуса блоков

Рассмотрим примеры реализации БФА, БФА 14 предназначен для адресации БП 22о БП 84 содержит значения вьмисленные для всех Ро БФА 14 работает следугашим образом: при заданной организации БП 22 адрес величины равен 2ipj адрес велртчины у. равен 2ip+1o Элементы 84 и 88 осуществляют расчет ipo Формирование удвоенного значения осуществляются монтажно - сдвигом влево на один разряд Младший разряд адреса формируется на счетном триггере 89, которьй обеспечивает выборку х- и У р за два последовательных такта Tj Правильная последовательность вы борки обеспечивается начальной установкой триггера 89.

БФА 15 формирует адреса записи.вычисленных значений и Tpg в БЗИ,26с Запись производится в одиниз БПБЗИ 26, при этом адреса записи представляют

812

собой относительные номера (К и 1) элементов в подмножестве и могут быть рассчитаны в соответствии с выражениями (10) и (11), На фиг о 5 представлен пример табличной реализащш вычисления адресов

БФА 16 форшфует адрес компонент вектора ПА в соответствии с выражением А ЗР+С, где С - значение поля 18,16.

БФА 17 формирует адреса, поступающие на адресные входы мультиплексоров 9 и t2o .

В зависимости от значения управляющего сигнала 18 Л8 БФА 17 или пропускает без изменения на адресные входы мультиплексоров 9 и 12 значения , заданные в полях соответственно 18о3 и 18о8 ЕМУ, или модифицирует их с периодом Tj в соответствии с состоянием триггера 89 о Модификация заключается в прибавлении содержимого триггера 89 к значениям, заданным в полях 18о8 и 18,3о Необходимость модификации адресов показана (в табице) „

Микропрограмма работы устройства составляется в соответствии с блок- схемой алгоритма (фиг. 9) с использованием введенной кодировки микроко-- манд (МК)о

Блоки алгоритма работы устройства меют следующий смысл:

99- начальная установка устройства;

100- проверка: ЛУА

101- прием матрицы А;

102- расчет вектора М«,;

103 задание режима для расчета

Gr,: (управление передается аппаратным средствам);

104- расчет и запоминание Gрj

(возврат управления БМУ 18);

105- задание режима расчета F{p

(передача управления аппаратным средствам);

106- расчет и запоминание Р, в

(возврат управления БМУ 18);

107- задание режима расчета Сл

(передача управления аппаратным средствам);

108- расчет р, , (возврат управления БМУ 18);

109- проверка: ЛУК 1-

В дальнейшем при описании работы стройства используется введенная коировка, причем выражение значает, что поле 18„4 принимает

значение ххх. В упрощения ука- зьга.аются только поля, наиболее существенные в рассматриваемом такте, При этом значения остальных полей в данном такте могут принимать значе шя из числа допустимых (таблица) и не противоречащих значениям полей, указанных явноо

Устройство работает следующим об- разомо

В устройстве реализован следующий принцип управления: общее управление работой устройства и вычислительным процессом осуществляет БМУ 18, однако часть вычислений, характеризующихся большим количеством повторяюиц1хся операщтй, выполняется под управлением аппаратных средств. Для перехода к такому режиму вычислений очередная МК БМУ 18 задает необходимую ког гмута ,цию операндов и результата, требуему частоту синхроимпульсов и другие не-;- обходимые параметры и блокирует прохождение синхроимпульсов на синхро- вход БМУ 18. БМУ 18 приостанавливает . свою работу до тех пор, пока не за-- кончится требуемый цикл вычислений (при этом на его выход-е находится микрокоманда, задающая необходимьш режим вычислений) По окот1ании цикла сигнал запуска устанавливает триггер 45 в единицу и на синхровход БМУ 18 поступает очередной синхроимпульс, выбираю1гщй следующую МКо

Работа устройства осуществляется в соответствии с алгоритмом

По сигналу начальной установки (НУ), поступающему с входа 59 устройства , который может вьграбатываться при включении питания или подаваться в требуемые моменты времени, элементы устройства устанавливаются в на чальное состояние: триггер 45 - в единицу, регистры 80 и 83 БМУ 18 - в нулевое состояние, генератор 51 - в начальное состояние, счетчик 74

в состояние Mj , регистры 71о 1с,

1,, 7иМз + 1 - ственно О, 1, 0.0, ..j

9 о о }

71сМ, , 7КМ, + 1 - в состояния соответМ.1 Р7 3

где RZ - код резервного блока памяти, не совпадающий ни с одним из кодов O+Mj-fc

Такая начальная установка регистров и счетчика может быть достигнута за счет соответствующей коммутации сигнала НУ по входам установки в единицу или установки в ноль требуемых разрядов

По окончании сигнала НУ с выходов генератора 51 начинают поступать син- хроиьтульсы Т , Т , Т.,, Т. Бапичина периода Т, достаточна дпя выгголнения операций приема нового значеш-тя матрицы 4 и вычисления матрицы Т, величина периода Т достаточна для выполнения операции вида ах + b на элементах 49 и 50 с учетом совмещенного с вычислениями формирования адреса .и выборки операндов из памяти, (фиго 8), величина Т такова, что за время 21 рассчитываются и записываются в БЗИ 26 знач ения и -fi о По синхроимпульсу Tj на выход БМУ 18 поступает первая МК, которая обеспечивает проверку ЛУА с выхода триггера 43с При этом ПрЛУ5 10, АП адрес первой МК блока 101, 18„10: 0 18.,18,, 18., 18., триггер 45 - в единице. На синхровходе БМУ 18 - синхроимпульсы Т. Если (триггер 43 в нуле), выбирается СПедующая МК, которая осуществляет безусловный переход на МК проверки ЛУА (, АП -г адрес .первой МК блока 100), т,е„ переход по адресу, заданному в поле АП на первую

МК блока 101 о Синхроимпульс Т,- устанавливает триггер 43 в единицу, вследствие чего счетчик 42 устанавливается в ноль, по синхроимпульсу Tj осуществляется переход на первую МК блока 101 о Блок 101 содержит последова-

теиьность МК, в результате выполнения которой осуществляются прием новых значений матрицы А и сброс триггеров 43 и 44, Последовательность содержит

40 9 МК, в которых заданы следующие значения полей: 18с10: 0, , 1-8о2: код адреса от О до. 8 18с 1 : 1, 18о14: 1, 18., 18„12: 00, 18„15: 0, 18„19: 1. Таким образом,

45 триггеры 43 и 44 обнуляются, БП 24 - в режиме записи, информация с входов 61 выбирается в соответствии со значением адреса записи (18.2) и записывается в БП 24 по сигналу с выхода

50 формирователя 57 импульсов После приема новых значений матрицы А начинается выполнение блока 102, который содержит последовательность МК, обеспе шваюр ую расчет компонент век55 тора NP (в данном случае Р 0.) . Поля МК принимают следующие значения: 18„10: 0; ПрЛУ: 00; 18„2: -С код адреса от О до 8 ; 18о1: 0; 18,4: 00; 18, 18. 18о13:г1;

18о14: 0; 18о15: 0; 18„16:.00, 01, 10 ; 18„9: 1; 18.,1 ; 18,5: 100, 001, 010 о Поля 18о2, 18о 16, 18о8 и 18.5 при выполнении блока 102 принимают различные значения в разных тактах Т. Такие обозначения используются и Е дальнейшем. Таким Образом БП 24 - в режиме чтепор, пока не будет рассчитано Np для следующего Р), аналогично вычисляются значения Np,j и Np Для повыния, информация с выхода БП 24 запи- 10 шения быстродействия допустимо совсывается в регистр 33 (адреса считывания задается в.попе 18.2); информация с выхода БП 23 считьтается по адресу, формируемому в БФА 16, и записывается в регистр 34о Результаты вычислений записываются в регистр. 35 и через демультиплексор 13 в один из регистров 36-38 о Демультиплексор 13 коммутирует на информационные входы регистров 36-38 информацию с выхода регистра 35, а на синхровходы регистров 36-38 - синхроимпульсы Тз о При этом коммутация на входы регистров 36-38 осзпцествляется в тех тактах, когда в регистр 35 записаны значения соответственно Np , Р2 Рэ Обеспечивает правильную запись и хранение значений компонен вектора Np

При расчете вектора Np важную роль играет также мультиплексор 12, которьй при вычислении компонент вектора подает на один из входов сумма- тора 49 или нулевой код с входа нулевого кода устройства, или значение

Таким образом, информация с выхо да БП 21 записывается в регистр 33, в регистр 34 записывается , на

частичной суммы с выхода регистра 35о gg одном входе сумматора 49 - нулевой

В качестве примера рассмотрим вычисление N р о По синхроимпульсу Tj на адресный вход БП 24 поступает адрес элемента а , а на адресньй вход БП

код. Адрес БП 21 формируется на сче чике 40, результат вычислений запис вается в БП 19 через демультиплексо 13 по сигналу с выхода формировате23 - адрес с выхода БФА 16, по кото- 40 ля 57„ На счетньй вход счетчика 40

рому выбирается п л о Следующим синхроимпульсом значения а,, и п заносятся в регистры 33 и 34 соответственно о На выходе г-гультиплексора 12 - нулевой код По следующему синхроимпульсу в регистры 33 и 34 заносятся значения a и п i а в регистр 35 - значение а, п которое через мультиплексор 12 подается на один из

входов сумматора 49 В следующем так- 50 на синхровход БМУ 18 При этом в

те в регистры 33 и 34 заносятся значения а, и Пр, в регистр 35 - значение а2,Пр2, которое через мультиплексор 12 подается на один из входов сумматора 49

По следуюплему синхроимпульсу в регистр 35 записывается результат вычисления Np, ag п

+ а,,п

я рг

демультиплексор 13 под1слю-

регистр 27 записан адрес последне вычисляемого Gp: , а в регистр 33 последнее значение Z . По следующ синхроимпульсу Tj результат вычи 55 лений записьтается в регистр 35, рес переписьшается в регистр 28, на выходе БМУ 18 появляется следу ющая МК, блокирующая прохождение синхроимпульсов на счетньй вход с

16

регистр 35 на вход регистра 36.

Следующий синхроимпульс записьшает в регистр 36 значение и отключает регистр 36 по входу (таким образом

N

Р1

в регистре 36 хранится до тех

пор, пока не будет рассчитано Np для следующего Р), аналогично вычисляются значения Np,j и Np Для повышения быстродействия допустимо совмещение записи результата вычислений и вычисления первого произведения для следующей компоненты.

По окончании выполнения последо15 вательности МК блока 102 в регистры 36-38 записаны значения соответственно Np , Npj Счетчики 40 и 41 установлены в ноль По очередному синхроимпульсу Тд осуществляется пе20 реход к блоку 103. На выходе ЕМУ 18 появляется МК, задания режима поля которой принимают следующие значения поле 18 о 10 устанавливается в единицу, что приводит к установке

25 в ноль триггера 45 и подключает логический Ноль на синхровход ЕМУ 18, поля 18. 18„12: 01} 18о11: 00; 18о7: 1 (на адресный вход БП 19 подключен регистр 28); 18, 18,18г

30 0; 18,3; 11; 18о8: 0; 18о4: 10;

18о5: 011; 18„15: 0; 18.13:

Таким образом, информация с выхода БП 21 записывается в регистр 33, , в регистр 34 записывается , на

gg одном входе сумматора 49 - нулевой

код. Адрес БП 21 формируется на счетчике 40, результат вычислений записывается в БП 19 через демультиплексор 13 по сигналу с выхода формироватепоступают синхроимпульсы Т с выхода мультиплексора 1, вследствие чего счетчик изменяет свое состояние от О до , Тоео j О, , что 45 обеспечивает расчет всех Gp- для заданного Р По Сигналу переполнения счетчика 40 триггер 45 устанавливается в единицу, что подключает синхроимпульсы с вькода мультиплексора 1

регистр 27 записан адрес последнего вычисляемого Gp: , а в регистр 33 - последнее значение Z . По следующему синхроимпульсу Tj результат вычис- 55 лений записьтается в регистр 35, адрес переписьшается в регистр 28, а на выходе БМУ 18 появляется следующая МК, блокирующая прохождение синхроимпульсов на счетньй вход счетчнкя АО (18 „ 1 2 : 00;, поле 18.10:0, поле 18о (т.Со БП 19 продолжает находиться в режиме записи), на син- хроиходе ВМУ 18 - CHHxpoHNmyHbCbi Т , последний результат Cpj записывается в ВП19 по сиг налу с выхода формирс ва- теля 57, запущенного этим синхроим- пульсомс В следунлцей МК поле 18о7: 0, что исключает запись недостоверной информации,, Таким образом, в БП 19 записаны все требуемые д/ш заданного Р значения В соответствии с алгоритмом (блок 105) очередная МК задает режим расчета F,. о Указанная МК должна поступать по синхроимпульсу Tj, синхронному с Tjо При необходимости, так как микропрограмма де- термирована, это условие легко соблю5

я рег истр 35 Записывается зилмение , в регистры 33 и ЗД -- значения соответственно У- и Нр,, , триггер 89 устанавливается в моль, на

один из входов сумматора 49 руется содержимое регистра 35 Импульс Tj увеличивает содержимое счетчика 41 на единицу, что обеспечивает

Q формирование адреса для выборки х л,, соответствующего следующему значению io

По с.аедующем импульсу Т в регистр 35 записывается результат FТ5 (для данного i), а в регистры 33 и 34 - операнды, необходимые для вычислений по следующему io Запись результата вычислений в БП20 осущест - вляется по сигналу с вькода формиродается введением холостой МК для про- 20 вз.теля 57 (правильный результат запуска одного такта МК режима задает следую1 5ие параметры: поле 18о10 устанавливается в единицу, 18о9: 1, 18о15: 0, 18,19;1, 18о11: 01, 18„12: 01, 18о7: 0, 18„6: 1 (при этом на адресном входе ВП 20 адрес с выхода регистра 39), поле 18о18:1, поле 1.8о17 устанавливается в единицу, что устанавливает в ноль триггер 89,

писывается во втором такте Т пери ода ) о ДальнеЙ1иие ; вычисления осуществляются аналогично дпя всех i ,

Рассмотрим завершеТо вс i - о,

25 кие вычислений по данному режиму В последнем цикле по i синхроимпульс Т с выхода мультиплексора 2 записывает в регистр 39 адрес последнего вьиисляемого значения вызывает

18,, 18.8: 1, 18., 18.5г 106, 30 импульс переполнения счетчика 41, ко- 18.15: 0„торый устанавливает в единицу триггер 45о На синхровходе ВМУ 18 - син35

Таким образом на синхровходе ВМУ 18 - логический ноль, ВФА 17 работает в режиме модификации, на информационные входы регистров 33 и 34 под- ключе:ны соответственно ВП 2-2 и регистр 36, на одном входе сумматора 49 - содержимое регистра 35, счетчик 41 - в нуле, на адресном входе БП 22, так как счетчик 41 и триггер 89 - в нуле, ВФА 14 вырабатывает адрес элемента для ip, соответствующего заданному Р, которое определяется состоянием счетчика 42 и i О (i: состояние счетчика 41 ), Следующий синхроимпульс Т записывает в регистр 33 считанное значение X rt в регистр 34 - значение Np, триггер 89 устанавливается в единицу, При этом ВФА 17 модифицирует адреса опера щов, вследствие чего на выходе мультиплексора 9 появляется содержимое регистра 37, на выходе мультиплексора 12 - нулевой код, на адресном входе ВП 22 - адрес следуклцей ячейки памяти, в которой записано значение у. (для того же самого i о) . Следукядим синхро1 тульсом Т (си1гхронным с Т„)

хроимпульсы Tj с выхода мультиплексора 1 о Следующий импульс Т., записьша- ет в регистр 35 последнее вычисленное значение , запускает формирователь 57, сигнал с выхода которого записывает последний вьмисленный результат в ВП 20, а: также вызывает

40 появлени:е следуклцей МК на выходе

ВМУ, в которой поля , 18.13: 1, 18,, 18., 18„12: 00, . Тое счетчики 40 и 41 в нулевом состоянии, на выходах мультиплексоров

45 1 и 2 - логические нули, ВП 20 - в режиме записи, на синхровходе ЕМУ 18 - синхроимпульсы Таким образом в ВП 20 записаны все вычисленные значения F-p , после чего следующей МК ВП 20 переводится в режим чтения В соответствии с алгоритмом очередная МК задает режим расчета 7р (блок 107) о Ее поля принимают следуклцие значения: поле 18 10 устанавливается в единицу; 18, 18. 18. 18о6; 0; 18. 18, 18о14: 0; 18„19: 1„ Триггер 45 устанавливается в ноль. Таким образом, на синхровходе БМУ 18 логи50

я рег истр 35 Записывается зилмение , в регистры 33 и ЗД -- значения соответственно У- и Нр,, , триггер 89 устанавливается в моль, на

один из входов сумматора 49 руется содержимое регистра 35 Импульс Tj увеличивает содержимое счетчика 41 на единицу, что обеспечивает

формирование адреса для выборки х л,, соответствующего следующему значению io

По с.аедующем импульсу Т в регистр 35 записывается результат F(для данного i), а в регистры 33 и 34 - операнды, необходимые для вычислений по следующему io Запись результата вычислений в БП20 осущест - вляется по сигналу с вькода формировз.теля 57 (правильный результат записывается во втором такте Т пери ода ) о ДальнеЙ1иие ; вычисления осуществляются аналогично дпя всех i ,

Рассмотрим завершеТо вс i - о,

5

хроимпульсы Tj с выхода мультиплексора 1 о Следующий импульс Т., записьша- ет в регистр 35 последнее вычисленное значение , запускает формирователь 57, сигнал с выхода которого записывает последний вьмисленный результат в ВП 20, а: также вызывает

0 появлени:е следуклцей МК на выходе

ВМУ, в которой поля , 18.13: 1, 18,, 18., 18„12: 00, . Тое счетчики 40 и 41 в нулевом состоянии, на выходах мультиплексоров

5 1 и 2 - логические нули, ВП 20 - в режиме записи, на синхровходе ЕМУ 18 - синхроимпульсы Таким образом в ВП 20 записаны все вычисленные значения F-p , после чего следующей МК ВП 20 переводится в режим чтения В соответствии с алгоритмом очередная МК задает режим расчета 7р (блок 107) о Ее поля принимают следуклцие значения: поле 18 10 устанавливается в единицу; 18, 18. 18. 18о6; 0; 18. 18, 18о14: 0; 18„19: 1„ Триггер 45 устанавливается в ноль. Таким образом, на синхровходе БМУ 18 логи0

I - 14396

чоский ноль, ряярелрена вычисляемых значений в КЗИ 26, разрешен переход к ся дукяцему значению Р по импульсу переполнения счетчика 41, на адресных входах БП 19 и 20 - содержимое счетчиков соответственно 40 и 41, синхровходах которых соответственно импульсы с выхода триггера 25 и импульсы переполнения счетчи- ю ка 40„

На адресных входах БП 19 и 20 адреса, по которым на выходы блоков выбираются значения соответственно G

PJ

о При этом сумматор 48 и вычита- 15 тель 55 одновременно вычисляют значения соответственно tpt по формулам (8) и (9)о Адреса для записи этих значений в БЭИ 26 вычисляются в БФА 15 аналогично рассмотренному,20

,- Значения 1,, и записываются в регистры соответственно 32 и 31, а их адреса - в регистры соответственно 30 и 29 по синхроимпульсам с выхода мультиплексора 1, период которьк 25 равен 2X40

Предположим, что очередной импульс записал в регистры 31 и 32 результаты вычислений, а в регистры 29 и 30 - адреса записи этих результатов 30

В первом такте Т следующего 1щкла вычислений 7ia выходы мультиплексоров 11 и 7 коммутируются соответственно регистры 31 и 29, в следующем такте Т 4 регистры 32 и 30 соответствен- д но о

Информация с выходов мультиплексоров 11 и 7 через открытые элементы 52 и 54 проходит на соответствующие входы БЭИ 26 и стробируется сигналом 40 Т., проходящим через открытый элемент 53,

По завершении двух тактов вьщачи в регистры 29-32 записываются новые g значения и процесс повторяется

В дакле вычисления последних двух значений импульс с выхода мультиплексоров 1 записьтает в регистры 31 и 32 последние вычисленные значения, Q в регистры 29 и 30 - их адреса и вызывает импульс переполнения счетчика 4-1, который увеличивает содержимое счетчика 42 Иа единицу, запускает формирователь 58 импульсов и проходя д на синхровход триггера 45 устанавли- вает триггер 45 в 1, что подключает выход мультиплексора 1 на синхровход БМУ 18 о

18

За два последних периода Т. псу-е- ю

15 5 20

25

30

д

40

g

Qд

ществляется запись последних яь гислом- ных значений в БЗИ 26, после чего импульс с выхода формтрователя 58 модифицирует статус БП 65 БЗП 26 и на выход БМУ 18 поступает следующая МК, в которой производится проверка окоггчания расчета по всем Р,

Ее поля принимают значения: 18., 18,, 18о15: 0, , 18., ПрЛУ 11, АИ адрес первой МК блока 100 В следующей МК задйны значения: ПрЛУ 01, АП адрес первой МК блока 102 о

Если расчет для всех Р завершен, то импульс переполнения счетчика 42 установил в единицу триггер 44, т.е, ЛУК 1, осуществляется переход на первую МК блока 100 и при поступлении очередного импульса Х устройство работает аналогично описанному, Если расчет не завершен, то и следующая МК осуществляет переход на первую МК блока 102 Процесс повторяется

Формула изобретения

Устройство для вычисления матрицы функций, содержащее умножитель, сумматор, три регистра, блок микропрограммного управления, блок формирования адреса и два блока памяти, причем вьсход первого регистра подключен к входу первого сомножителя умножите- ля, выход сумматора подключен к информационному входу второго регистра, выход третьего регистра подключен к входу второго сомножителя умножителя, отличаю ще еся тем, что, с целью повышения быстродействия, в него введены три счетчика, десять регистров, три блока формирования.адреса, четыре блока памяти, блок запоминания информа1р1и, .двенадцать мультиплексоров, демультиплексор, генератор тактовых импульсов, четыре триггера, элемент И, элемент ИЛИ, сумматор, вычитатель, три коммутатора и три формирователя иьтульсов, причем первый выход генератора тактовых импульсов подключен к синхровходу первого триггера, выход которого подключен к входу первого логического условия блока микропрограммного управления, вход второго логического усло- йия которого подключен к выходу вто

рого триггера, синхровход которого подключен к выходу переполнения первого счетчика, информационные входы первого и второго триггеров подключены к входу логической единицы устройства, третий выход генератора тактовых импульсов подключен к синхровхо- дам регистров с первого по третий и к младшему разряду информационного входа демультиплексора, а также через первый формирователь импульсов - к первому управляющему входу первого блока памяти, вход начальной установки устройства подключен к входам начальной установки блока микропрограммного зт равления и генератора тактовых импульсов, В-й информационньй вход группы устройства подключен к В-му информационному коцу первого мультиплексора, (В 1;,9), выход которого подключен к информационному входу первого блока памяти, первьш - управляющий вход которого соединен с выходом режима работы блока микропрограммного управления, адресный вход первого блока памяти соединен , с адресным входом первого мультилл ек- сора и с выходом адреса элемента матрицы, выход первого блока памяти подключен к первому информационному входу второго мультиплексора, адресный вход которого подключен к выходу адреса второго операнда, выход второго мультиплексора под1 :лючен к информационному входу третьего регистра, выход умножителя подключен -к входу первого операнда сумматора, вход второго операнда которого подключен к выходу третьего мультиплексора, выход второго регистра подклктчен к старшим разрядам информационного входа демультиплексораj адресньй вход которого подключен к выходу адреса записи результата блока микропрограм много управления, старшие разряды вы ходов с первого по третий демульти™ плексора подключены соответственно к информационным входам четвертого, пятого и шестого регистров, синхро- входы которых подключены соответственно к младшему разряду первого, второго и третьего выходов демультиплексора, выходы регистров с четвертого по шестой подключены соответст™ венно к информационным входам с первого по третий четвертого мультиплексора, выход которого подключен к информационному входу первого регистра

0

5

. О

5

с

0

35

40

50

55

выходы второго и третьего счетчиков подключены соответственно к первому и второму входам первого блока формирования адреса, выход первого счетчика подключен к первому входу второго блока формирования адреса, второй вход и выход которого подключены ;соответственно к выходу номера компоненты вектора блока микропрограммного управления и к адресному входу второго блока памяти, первьш и второй информационные входы третьего мульти- 1 шексора подключены соответственно к выходу второго регистра и к входу логического нуля устройства, выход второго блока памяти подключен к четвертому информационному входу четвертого мультиплексора, адресньй вход которого подключен к первому выходу третьего блока формирования адреса, второй выход которого подключен к адресному входу третьего мультиплек- сора, четвертый и пятый выходы старших разрядов демультиплексора подключены соответственно к информационным входам третьего и четвертого блоков памяти, третий выход генератора тактовых импульсов подключен к первому ВХОДУ четвертого блока формирования адреса и к первым информационным входам пятого и шестого мультиплексоров, выход первого формирователя импульсов подключен к вторым управляющим входам третьего и четвертого блоков памяти, второй выход генератора тактовых импульсов подключен к первому информационному входу седьмого мультиплексора, выходы пят ого и шестого блоков памяти подключены соответственно к второму и третьему информационным входам второго мультиплексора, первый вькод четвертого блока формирования адреса подключен к адресному входу шестого блока памяти, вход,логического нуля устройства подключен к вторыг- информационным входам пятого, шестого и седьмого ; ., мультиплексоров, адресные входы пятого и седьмого мультиплексоров подключены соответственно к .полю задания периода синхроимпульсов второго счетчика выхода блока микропрограммного управления и к полю задания периода синхроимпульсов третьего счетчика выхода блока микропрограммного отравления, выход шестого мультиплексора подключен к синхро- входу блока микропрограммного управ14

лепня, вькод пс 1 еполибМ1ия второго счетчика подключен к третьему информационному ву. оду седьмого м льтиплек сора и к первому информащюнному входу восьмого мультиплексора, выход переполнения третьего счетчика подключен к первому входу элемента И и к второму информационному входу восьмого мультиплексора, выход которого подключен к первому входу элемента ШШ, второй вход и выход которого подключены соответственно к входу начальной установки устройства И к синхровходу третьего триггера, адресный вход восьмого мультиплексо- ра подключен к палю задания источника запуска выхода брака микропрограммного управления, информационный вход третьего триггера подключен к входу логической единицы устройства, поле задания режима управления выхода блока .микропрограммного управления через второй формирователь импульсов подключено к входу установки в О третьего триггера, поле установки в О триггеров блока микропрограммного управления подклкнено к входам установки в О первого и второго триггеров, вьгход первого триггера подключен к входу установки в О первого счетчика, выход которого подключен к вто- рому входу четвертого блока формирования адреса, третий, четвертый, пятый входы и второй выход которого подключены соответственно к входу угла поворота системы координат устройства, выходу третьего счетчика, полю установки в О триггера блока микропрограммного управле1шя и к четвертому входу третьего блока формирования адреса, первьй , второй и третий входы которого подключены соответственно к полям адреса первого операнда, управления третьего мультиплексора, признака модификации адреса первого операнда выходов блока микропрограммного управления, поле разрешения перехода к следующему значению Р блока микропрограммного управления подключено к второму входу элемента И, выход которого подключен к счетному входу первого счетчика, через третий формирователь импульсов - к входу модификации статуса блоков памяти блока запоминания информации, выход седьмого мультиплексора подключен к счетному входу третьего счетчика и к синхровходу седьмого регист-

961824

ра, выход которого подключен к первому информащюнному входу девятого мультиплексора, второй информационньй вход которого соединен с информационным входом седьмого регистра и подключен к выходу третьего счетчика, выход девятого мультиплексора подключен к адресному входу третьего блока

1Q памяти, первый уттравляющий вход которого соединен с адресным входом девятого мультиплексора и подк.л1сгчен к полю режима работы блока памяти выхода блока микропрсуграммного управле15 ния, выход пятого мультиплексора подключен к счетному входу второго счетчика и к синхровходам восьмого и девятого регистров, вькод второго счетчика подключен к информационному вхо20 ДУ восьмого регистра, первому информационному входу десятого мультиплексора и к адресному входу пятого блока памяти, входы начальной установки второго и третьего счетчиков подКлю-

25 -чены к полю установки в О второго и третьего счетчиков блока микропрограммного управления, выход восьмого регистра подключен к информационному входу девятого регистра, выход кото0 рого подключен к второму информационному входу десятого мультиплексора, . выход которого подключен к адресному входу четвертого блока памяти, пер- вьй управляющий вход которого соединен с адресным входом десятого мультиплексора и подключен к полю режима работы первого блока памяти блока микропрограммного управления, управ- ляю1чие входы первого, второго и третьQ его коммутаторов подключены к полю управления выдачи результатов в блок запоминания информации, выходы первого, второго и третьего коммутаторов подключены соответственно к информа-

g ционному входу, входу строба записи и входу адреса записи блока запоминания информации, входы строба чтения, адреса чтения и выход которого подключены соответственно к входам строд ба чтения информации и адреса считывания устройства и к информационному выходу устройства, вход начальной установки устройства подключен к входу начальной установки блока запоминаg ния информации, четвертый вькод генератора тактовых импульсов подключен к синхровходу счетного триггера, вход начальной установки и вькод которого подключены соответственно к

35

входу начальной установки устройства и к третьему информационному входу пятого мультишшксора, выход которого подключен к третьему информационному входу пятого мультиплексора, выход которого подключен к третьему информационному входу шестого мультиплексора, синхровходам регистров с десятого по тринадцатый и адресным входам одиннадцатого и двенадцатого fyльтиплeкcopoв выходы которых подключены соответственно к информационным входам первого и третьего коммутаторов, информационный вход второго коммутатора подключен к четвертому выходу генератора тактовых импульсовj выход третьего блока памяти подютю- чен к входу первого операнда второго сумматора и к входу уменьшаемого вы читателя, выход четвертого блока памяти подключен к входу второго операнда второго сумматора и к входу вычитаемого вычитателя, выход вычи- тателтя, выход второго сумматораа пер вьй и второй выходы первого блока формирования адреса подключены соответственно к информационным входам регистров с десятого по тринадцатьй, выходы которых подключены соответственно к первому и второму информа- 1ЩОННЫМ входам одиннадцатого мультиплексора и .к первому и второму и}1фор™ мационным входам двенадцатого ryльти плексора, поле задания режима ттрав™ ления блока микропрограммного управления и выход третьего триггера подключены соответственно к первому и второму адресным входам шестого мультиплексора, причем блок запоминания информации содерлдат группу блоков памяти, две группы мультиплексоров, грзшпу коммутаторов,- группу элементов группу схем сравненияj группу регистров, группу элементов HJli, дешифратор 5 счетчик, три фор ми-

рователя импульсов, причем информационные входы блоков памяти группы подключены к информационному входу .блока, вход .модифнкащи статуса блоков памяти блока подключен к счетному входу сче гчика через первьй форми рователь импульсов блока к синхровхо дам регистров группы, старшие разряды входа адреса чтения блока подклю™ чены к первым схем сравнения

выходу блока

группы, выход счетчика по модулю подключен к входу дешифратора, М-й выход которого подклю1{ен к пepвo гy входу М-го и к второму входу L(M+I) mod (Mg + 1)го элементов ИЛИ группы, М 1, Mj-i-1, к первому управляющему входу М-го блока памяти группы, адресному входу М-го мультиплексора первой группы, управляющему входу М-го коммутатора группы, первому входу первой группы входов .М-го элемента 2И-ИЛИ группы, адресному входу М-го мультиплексора второй

группы, вьЕкод которого подключен к информационному входу M-rt) регистра группы, выход которого подключен к первому информационному входу ЦМ+1) mod (Mj + 1)-го мультиплексора второй ,

группы, второму инфopмaIJJioннoмy входу ) mod (l Ij+1) мультиплексора второй группы, второму входу М-й схемы сравнения группы, выход которой подключен к первому входу

второй группы входов М-го элемента 2И-ИЛИ, выход которого подключен к второму управляющему входу М-го блока памяти группы, выход М-го элемента ИЛИ группы подключен к входу выборки М-го регистра группы, вход начальной установки блока подключен к входам начальной установки разрядов регистров грз ппы и счетчика по модулю Mg+l в соответствии с требу

емьм начальным состоянием, вход стро- ба чтения блока через второй формирователь импульсов блока подключен к вторым входам второй группы входов элементов 2И-ИЛИ5 вход строба записи блока через третий формирователь импульсов блока подключен к вторым входам первой грухтпы входов элементов 2И-1 ШИр вход адреса записи блока подкл.ючен к первым информационным

входам мультиплексоров первой группы, вторые информационные входы мульти- плексоров первой группы подклинены к младпмм разрядам входа адреса чтения блока, выход мультиплексора первой группы подключен к адресному входу М-го блока памяти группы, выход которого подключен к икформацион - иому входу Мго коммутатора, выход которого подключен к информационному

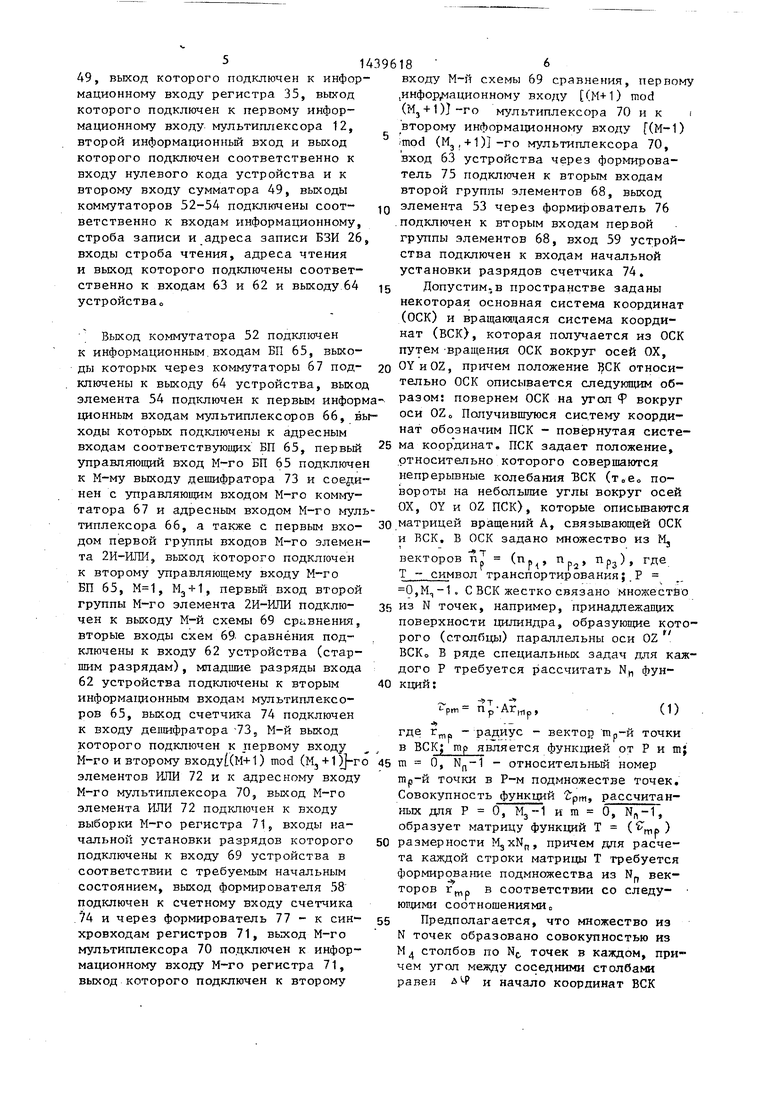

Проверка логических условий (ЛУ) ПрЛУ

Адрес перехода (АЛ) I S.I Режим работы БП-24

18 в2 Адрес элемента матрицы А

t8o3 Адрес первого операнда (без модификации)

18о4 Адрес второго операйда

Адрес записи результата 000 - регистр 36

001 - регистр 37

010- регистр 38

011- БП 19 100 - БП 20

18об Режим работы БП 20

1807 Режим работы БП 19

Управление мульти- плексор ом 12 (без модификации)

Управление выдачей

результатов в БЗИ 25

ЛУзО - выбирается следующая МК

- выбирается МК,

адрес которой задан в адрес перехода

проверка ЛУ А с триггера 43

проверка ЛУК с триггера 44

П

тение, 1 запись

дреса (0-8)

БП-23

регистр 36

регистр 37

регистр 38

БП 24

БП 22 БП 21

Внутреннее поле

1-й управляющий вход БП 24

Адресною БП-24 и мультиплексора 10

1-й вход БФА 17

Адресный вход мультиплексора 8

Адресный вход

демультиплексора

13

чтение

запись

.

на выходе мультиплек12 нулев ой код, 1 - соимое регистра 35

вьщача запрещена разрешена

1-й управляющий БП 20, адресный вход мультиплексора 4

1-й управляющий вход БП 19, адресный вход мультиплексора 3

2-й вход БФА 17

Управляющие входы коммутаторов 52-54

1439618

zi:

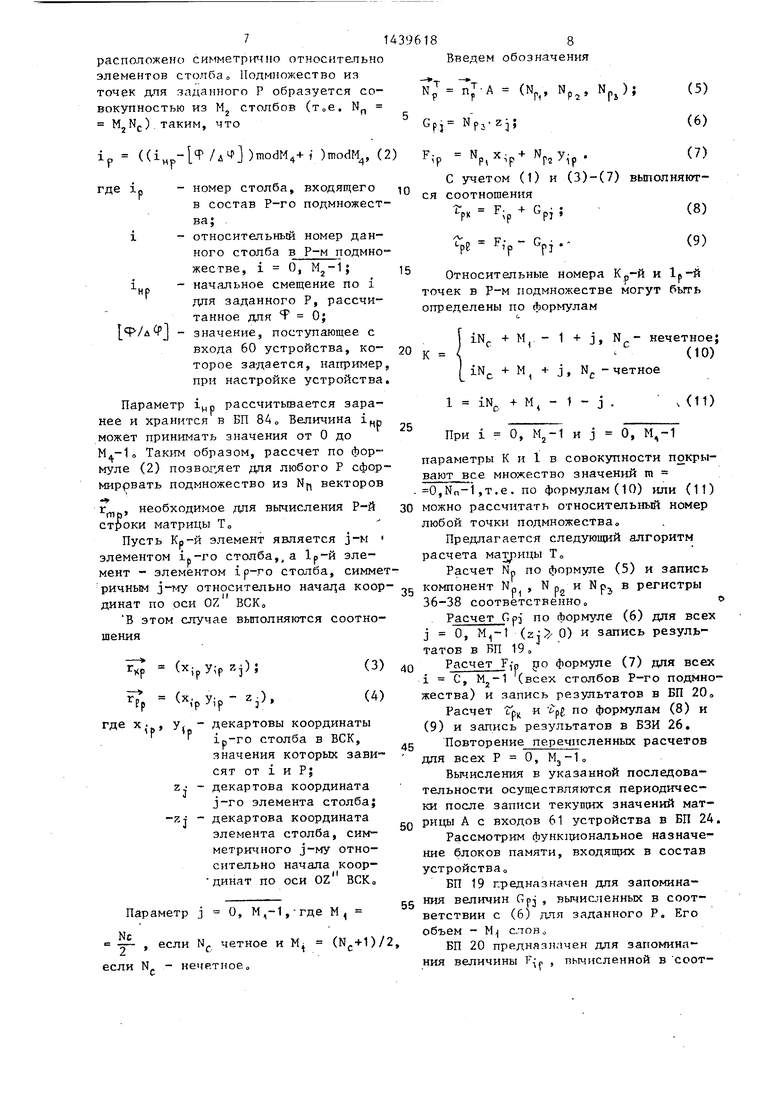

ISoW, Задание режима управления

0- управление от БМУ

1- управление аппаратное

11 Задание дериода синхроим- 00 пульсов счетчика 41

на счетном входе счетчика 41 логический ноль

01 - на счетном входе

счетчика 41 синхроимпульсы Tj

10 - на счетном входе

счетчика 41 сигнал переполнения счетчика 40

00 - на счетном входе

счетчика 40 логический ноль

01 - на счетном входе Т 10 - на счетном входе сигнал с триггера 25

18 о 13 Установка в ноль счетчиков 40 и 41

0- пассивный

1- активный

18 о 14 Установка в ноль триггеров 43 и 44

0- переход запрещен

1- разрешен

триг

ии

еранда

запус

00 - пр , 01 - прз, , 10 - Пр

0- пассивный

1- активный уровень

0- адрес не модифицируется

1- адрес модифицируется

0- сигнал переполнения

счетчика 40

1- сигнал переполнения

счетчика 41

Логическое условие го- товности текупцсх значений на входе 61

ЛУА О - не готово ЛУА 1 - готово

30

Продолжение таблицы

4

I

Вход элемента 56, 1-й управляющий вход мультиплексора 6

Адресный вход мультиплексора 2

Адресньй вход мультиплексора 1

Установочные входы счетчиков 40 и 41

Установочные входы триггеров 43 и 44

Вход элемента И 46

1-й вход БФА 16

Вход форьшрова- теля 90 БФА 14

3-й вход БФА 17

Адресный вход мультиплексора 5

С выхода триггера 43

ЛУК Лопсческое условие окон- ЛУК О вход чания расчета для

всех РЛУК 1

CS$

f

TO.J

тол

П1

C7lf

т.

с 73.2

CS8

713 7Щ

- Я ь

С выхода триггера 44

ffsm сп

(Ы)

TlJtf

Г

eJM

f-7fl

НаПМ,

(2-uSxoi}

I

f& f

«f

V. . .. l/ w l 1/

u

, поля

рж

cS$

19

80

CS$

81

,

рж

83

ШгШ

С6

Фие.З

Фе/е.4

I /А

cw

9i

Надо

92

Ha 29

Фае. 5

Ci8.

Ci8.18

€ /e.e

Maid

Фиг. 6

I

9S

91

f/a9

I

96

9S

a /2

Фие. 7

Фие. в

Pus. 9

| Устройство умножения матрицы на вектор | 1984 |

|

SU1226484A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Юэн Чо и дро Микропроцессорные системы и их применение при обработке сигналов Мо, 1986, Со 237, , рис о 7,14. | |||

Авторы

Даты

1988-11-23—Публикация

1987-03-23—Подача