Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно триггерное устройство (см. авторское свидетельство СССР N 1706362 от 02.04.90, МКИ Н 03 К 3/037, "Триггерное устройство", А.И. Еремин, Г. И. Шишкин, опубл. 28.08.97, Бюл. N 24), содержащее запоминающий элемент, состоящий из конденсатора и резистора, один вывод которого через конденсатор подключен к общей шине. Первый и второй входы первого элемента ИЛИ-НЕ соединены соответственно с первым установочным входом устройства и выходом второго элемента ИЛИ-НЕ, первый и второй входы которого соединены соответственно со вторым установочным входом устройства и прямым выходом D-триггера, тактовый вход которого соединен с выходом третьего элемента ИЛИ-НЕ, первый и второй входы которого соединены с первыми входами соответственно первого и второго элементов ИЛИ-НЕ. Выход двунаправленного ключа соединен с информационным входом D-триггера и другим выводом резистора, вход - с выходом первого элемента ИЛИ-НЕ, а управляющий вход - с выходом элемента И-НЕ, первый и второй входы которого соединены соответственно с выходом третьего элемента ИЛИ-НЕ и с дополнительным входом устройства.

Недостатком известного триггерного устройства является сложность схемной реализации, обусловленная необходимостью использования тактируемого D-триггера и большого количества элементов, а также необходимостью формирования на дополнительном входе непрерывной последовательности импульсов.

Известно триггерное устройство (см. патент РФ N 1276222 от 28.06.85, МКИ Н 03 К 3/286, "Триггерное устройство (первый вариант)", А.Я. Рыбаков, Г.И. Шишкин, опубл. 27.01.95, Бюл. N 3), выбранное в качестве прототипа и содержащее первый и второй элементы ИЛИ-НЕ (И-НЕ), первые входы которых соединены с соответствующими установочными входами устройства, запоминающий элемент, состоящий из конденсатора и резистора, первый вывод которого соединен с первым выводом упомянутого конденсатора, второй вывод которого подключен к нулевой шине. Второй вход первого элемента ИЛИ-НЕ (И-НЕ) соединен с выходом второго элемента ИЛИ-НЕ (И-НЕ), а выход - со вторым выводом резистора. Прямой выход тактируемого D-триггера соединен со вторым входом второго элемента ИЛИ-НЕ (И-НЕ), а D-вход - с первым выводом резистора. Первый и второй входы третьего элемента ИЛИ-НЕ (И-НЕ) соединены с соответствующими установочными входами устройства, а выход - с тактовым входом D-триггера.

Недостатками известного триггерного устройства являются сложность схемной реализации, обусловленная необходимостью использования тактируемого D-триггера, и низкая помехоустойчивость, обусловленная отсутствием устойчивости к перерывам в питании.

Задачей, решаемой предлагаемым изобретением, является создание триггерного устройства, обладающего простотой схемной реализации и повышенной помехоустойчивостью к перерывам в питании.

Технический результат, заключающийся в упрощении схемной реализации и повышении помехоустойчивости к перерывам в питании, достигается тем, что в триггерном устройстве, содержащем первый и второй элементы ИЛИ-НЕ (И-НЕ), первые входы которых соединены соответственно с входами сброса и установки триггерного устройства, второй вход первого элемента ИЛИ-НЕ (И-НЕ) соединен с выходом второго элемента ИЛИ-НЕ (И-НЕ), а выход - с входом запоминающего элемента, второй элемент ИЛИ-НЕ (И-НЕ) снабжен третьим входом, соединенным с входом сброса триггерного устройства, второй вход второго элемента ИЛИ-НЕ (И-НЕ) соединен с выходом запоминающего элемента. Кроме того, запоминающий элемент содержит конденсатор, два резистора и инвертор, вход которого соединен с входом запоминающего элемента и через первый резистор - с выходом запоминающего элемента, а выход - через последовательно соединенные второй резистор и конденсатор - с выходом запоминающего элемента.

Указанная совокупность признаков позволяет упростить схемную реализацию за счет исключения тактируемого D-триггера, обеспечить помехоустойчивость к перерывам в питании за счет исключения возможности быстрого разряда конденсатора запоминающего элемента через входные и выходные цепи элементов, а также повысить помехоустойчивость по входу за счет увеличения инерционности запоминающего элемента.

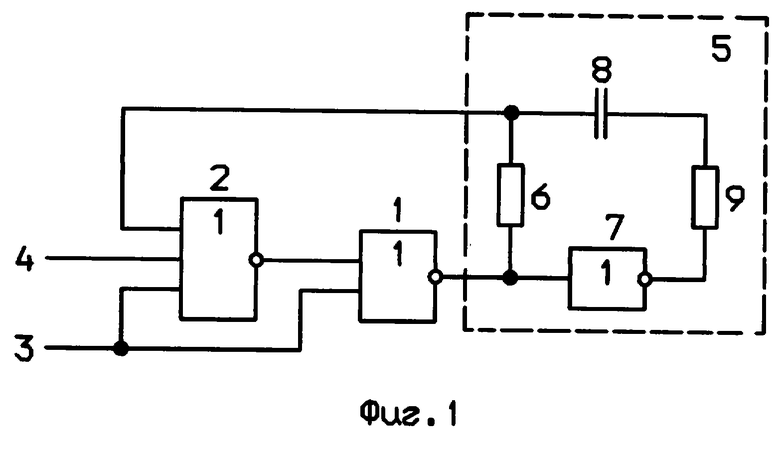

На фиг.1 приведена принципиальная схема триггерного устройства.

На фиг.2 - второй вариант реализации запоминающего элемента.

На фиг.3 -третий вариант реализации запоминающего элемента.

Триггерное устройство (см. фиг.1) содержит первый 1 и второй 2 элементы ИЛИ-НЕ, первые входы которых соединены соответственно с входом 3 сброса и входом 4 установки триггерного устройства. Второй вход элемента ИЛИ-НЕ 1 соединен с выходом элемента ИЛИ-НЕ 2, а выход - с входом запоминающего элемента 5. Второй и третий входы элемента ИЛИ-НE 2 соединены соответственно с выходом запоминающего элемента 5 и входом 3 триггерного устройства. В первом варианте исполнения запоминающий элемент 5 содержит резистор 6, первый вывод которого соединен с входом инвертора 7 и является входом запоминающего элемента 5, а второй вывод является выходом запоминающего элемента 5 и подключен к первому выводу конденсатора 8, второй вывод которого соединен с первым выводом резистора 9, второй вывод которого подключен к выходу инвертора 7.

Во втором варианте исполнения запоминающего элемента 5 (фиг.2) последний содержит резистор 10, первый вывод которого является входом запоминающего элемента 5, второй вывод соединен с первым выводом конденсатора 11 и первым выводом резистора 12, второй вывод которого является выходом запоминающего элемента 5. Второй вывод конденсатора 11 подключен к общей шине.

В третьем варианте исполнения запоминающего элемента 5 (фиг.3) последний содержит резистор 13, первый вывод которого является входом запоминающего элемента 5, второй вывод является выходом запоминающего элемента 5 и подключен к первому выводу резистора 14, второй вывод которого соединен с первым выводом конденсатора 15, второй вывод которого подключен к общей шине.

Триггерное устройство работает следующим образом.

Допустим, что на входе инвертора 7 и первом выводе конденсатора 8 присутствует уровень логического "0", на выходе инвертора 7 и втором выводе конденсатора 8 присутствует уровень логической "1", на входах сброса 3 и установки 4 - уровень логического "0", на входе первого 1 и втором входе второго 2 элементов ИЛИ-НЕ присутствует уровень логического "0", а на выходе элемента ИЛИ-НЕ 2 - уровень логической "1".

При поступлении импульса положительной полярности на вход 3 сброса изменяется только состояние выхода элемента ИЛИ-НЕ 2, а состояние выхода элемента ИЛИ-НЕ 1 не изменяется и запоминающий элемент 5 сохраняет состояние логического "0". По окончании входного импульса элемент ИЛИ-НЕ 2 возвращается в исходное состояние и запоминающий элемент 5 не изменяет своего состояния.

При поступлении единичного импульса на вход 4 установки триггерного устройства изменяется состояние элементов ИЛИ-НЕ 1, 2 и инвертора 7, при этом начинается перезаряд конденсатора 8. Если за время действия импульса конденсатор 8 перезарядится, то по окончании импульса элементы ИЛИ-НЕ 1, 2 не возвратятся в исходное состояние и в запоминающий элемент 5 будет записана логическая "1".

Если длительность импульса недостаточна для перезарядки конденсатора 8, то по окончании импульса устройство возвратится в исходное состояние.

Переключение триггерного устройства из состояния логической "1" в состояние логического "0" происходит аналогично.

Вместо элементов ИЛИ-НЕ 1, 2 могут быть использованы элементы И-НЕ, при этом функционирование устройства происходит аналогично описанному, но на установочные входы необходимо подавать нулевые импульсы, вход 3 является входом установки, а вход 4 - входом сброса.

Вход 3 сброса имеет приоритет по сравнению с входом 4 установки триггерного устройства, поэтому при синхронной подаче входных импульсов на входы 3 и 4 триггерное устройство по окончании входных импульсов устанавливается в состояние логического "0", если элементами 1, 2 являются элементы ИЛИ-НЕ.

Вход 4 сброса имеет приоритет по сравнению с входом 3 установки триггерного устройства, поэтому при синхронной подаче входных импульсов на входы 3 и 4 триггерное устройство по окончании входных импульсов устанавливается в состояние логической "1", если элементами 1, 2 являются элементы И-НЕ.

Изготовлен лабораторный макет триггерного устройства на микросхемах серии 564. Испытания макета подтвердили работоспособность заявленного устройства и его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1996 |

|

RU2123232C1 |

| ПОМЕХОСТОЙКОЕ ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106056C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1997 |

|

RU2123233C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2178617C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1999 |

|

RU2180985C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2212095C1 |

| СДВИГАЮЩИЙ РЕГИСТР | 1995 |

|

RU2105357C1 |

Изобретение относится к импульсной технике. Технический результат заключается в упрощении схемной реализации и увеличении помехоустойчивости к перерывам в питании. Триггерное устройство (ТУ) содержит первый (1) и второй (2) элементы ИЛИ-НЕ или И-НЕ. Первый вход элемента (1) с третьим входом элемента (2) и первый вход элемента (2) соединены соответственно с установочными входами (3) и (4) ТУ. Второй вход элемента (1) соединен с выходом элемента (2), а выход - с входом запоминающего элемента (5), выход которого соединен с вторым входом элемента (2). 1 з.п.ф-лы, 3 ил.

| ТРИГГЕРНОЕ УСТРОЙСТВО (ЕГО ВАРИАНТЫ) | 1985 |

|

RU1276222C |

| Триггерное устройство (его варианты) | 1982 |

|

SU1045354A1 |

| RU 2053593 C1, 27.01.1996 | |||

| GB 1345858, 06.02.1974. | |||

Авторы

Даты

2003-08-27—Публикация

2001-05-08—Подача