Данное изобретение относится к коммутационной системе для выполнения асинхронного режима передачи и способу коммутации ячеек в ней для служб комплексного представления информации. Данная заявка основывается на заявке Кореи N 56581/1995.

В комплексном представлении информации имеют место разнообразные характеристики нагрузки (скорость передачи данных, пакетность и т.п.) и отличия по качеству (задержка передачи, изменения величины задержки передачи, потеря данных и т.п.). Помимо этого, для условий комплексного представления информации требуются конфигурация двухпунктовая, радиальноузловая многопунктовая, узловая многопунктовая. В одном виде обслуживания может быть одинарное соединение и множественное. Обычные сети, такие как телефонная сеть общего пользования (ТСОП) и пакетная телефонная сеть общего пользования (ПТСОП), конструируются для соответствия только определенному обслуживанию с заданным форматом. Поэтому они не могут предлагать обслуживание с комплексным представлением информации. В связи с этим для служб комплексного представления информации требуется коммутационная система нового формата и этому должны предшествовать разработки в разных областях, составляющих эту новую схему, - от аппаратов до системы коммутации/передачи. В настоящее время Международный Союз Электросвязи (МСЭ) в целях текущей стандартизации утверждает асинхронный режим передачи (АРП) (АТМ) в качестве наиболее соответствующего метода, предлагаемого для служб с характеристиками, аналогичными службами комплексного представления информации.

В АРП предлагаются разнообразные коммутационные схемы. Во-первых, по способу разделения канала передачи информации: есть типы с разделением во времени и пространстве. С точки зрения топологии имеются следующие типы: кольцевой, шинный и решетчатый. Согласно размещению или применению используемого буфера имеются следующие типы: с входным буфером, общим буфером, рассеянным буфером и выходным буфером. Они могут сочетаться.

Структура коммутационной схемы АРП с разделением пространства в основном имеет форму решетки, такую как схема Баньяна или перемычная схема, и самомаршрутизацию, в которой ячейки в коммутационной схеме сами найдут свой пункт назначения (порты входа коммутационной схемы) в соответствии с работой аппаратуры.

Но эта структура должна иметь буфер, так как большинство этих структур предполагает внутреннее блокирование. Все виды коммутационной схемы АРП, включая типы с разделением в пространстве и времени, также должны иметь буфер на своем выходе ввиду их конфликта, возникающего в порте вывода.

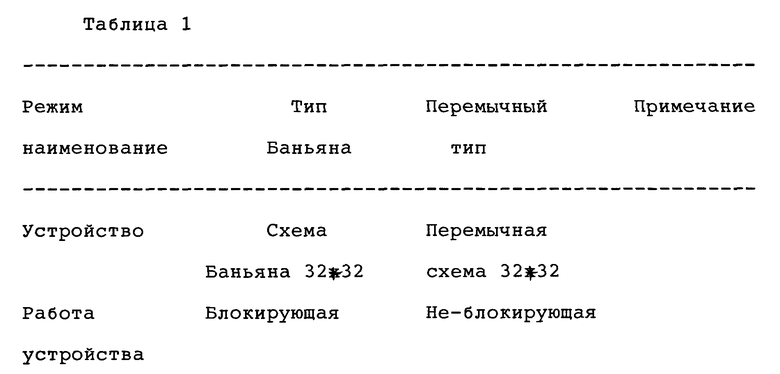

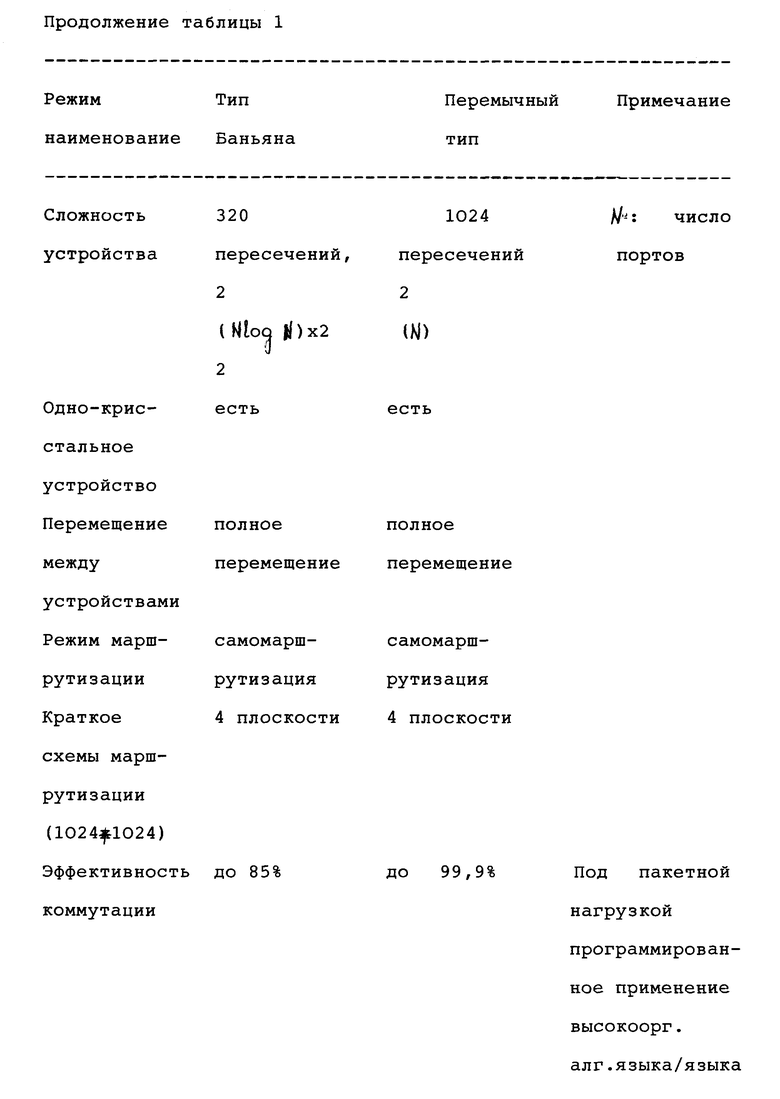

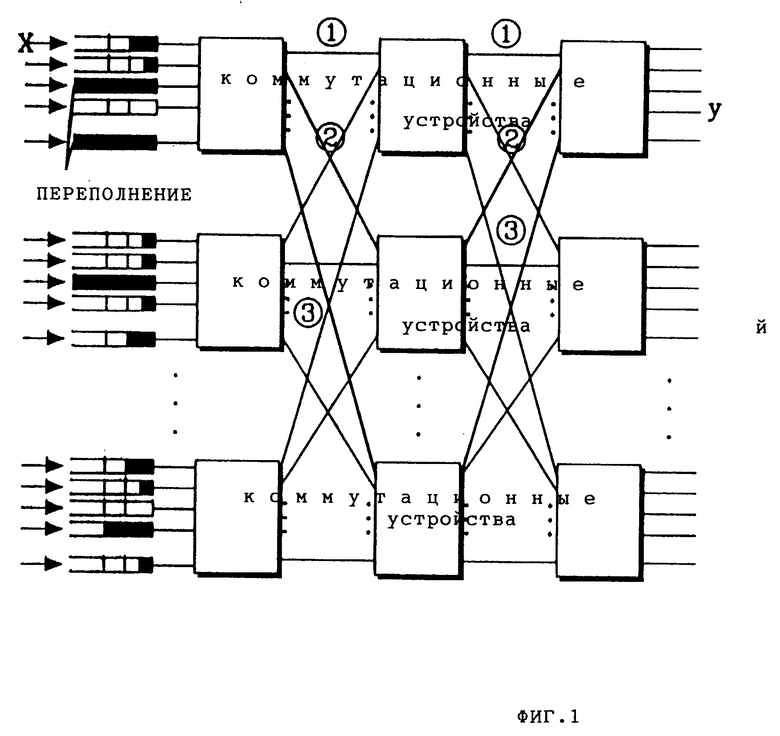

Имеется два типа буфера: тип специализированного буфера, который изображен в фиг. 1, и тип совместно используемого буфера, который изображен в фиг. 2. В соответствии со способом их действия входной буфер используется в коммутационной схеме с разделением пространства. Обычно большей частью используют специализированный буфер. Преимущество этих типов рассеянного буфера заключается в их легкой эксплуатации. Но их недостаток в том, что буфер, используемый для соответствующих портов коммутационной схемы, является фиксированным и поэтому нагрузка (ячейки (блоки передаваемой информации)) не рассеивается по портам коммутационной схемы в целом. Если происходит неправильное распределение, то переполнение входными данными происходит в любом порте, как это изображено в фиг.1.

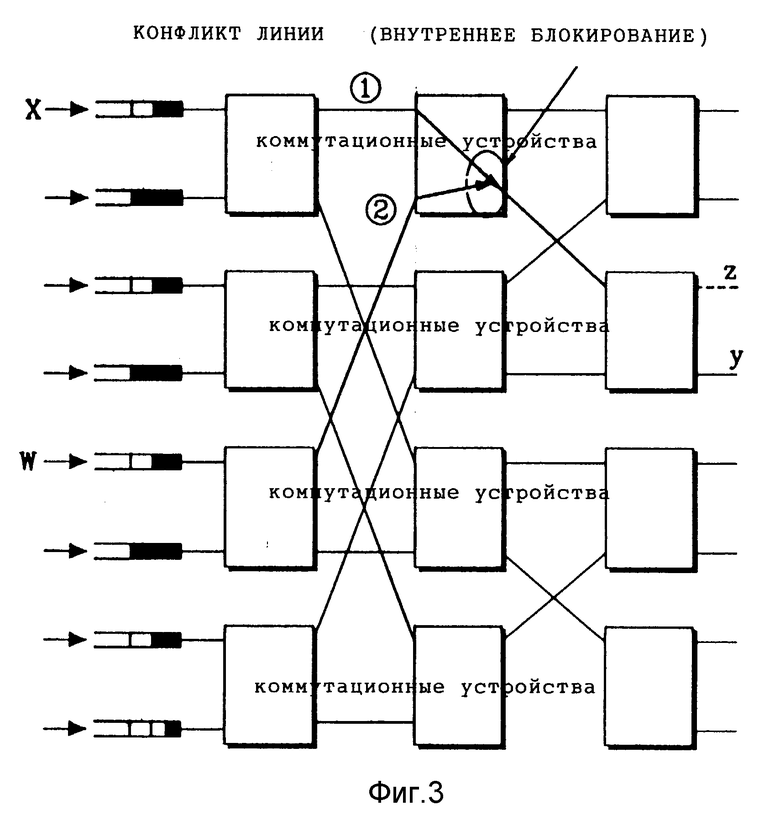

В коммутационной схеме АРП внутренний маршрут между портом ввода и портом вывода имеет структуру единого маршрута или множественных маршрутов. Как изображено в фиг. 1, между портом ввода X и портом вывода Y можно сделать коммутационные устройства маршрута вывода в (1), (2) и (3). Здесь в случае единого маршрута может происходить внутреннее блокирование, как это изображено в фиг. 3, и поэтому из-за потерь ячеек могут ухудшиться рабочие показатели. Фиг.3 изображает конфигурацию схемы Баньяна объемом 8•8 с единым маршрутом. В этом изображении предлагается пример передачи ячеек по маршруту передачи ячеек из порта вывода x к порту вывода y, и из порта ввода W к порту вывода Z. В этом случае ячейки конфликтуют на втором этапе коммутационных устройств, тем самым вызывая внутреннее блокирование. Коммутационная схема с единым маршрутом имеет простую внутреннюю маршрутизацию и ее легко эксплуатировать несмотря на внутреннее блокирование. В случае многомаршрутной коммутационной схемы вероятность внутреннего блокирования мала, но управление маршрутизацией для множественных маршрутов слишком сложное, чтобы его можно было бы применять с большим объемом коммутационных устройств. Причина этого заключается в том, что скорость управления коммутационной схемой для маршрутизации не доходит до скорости передачи ячейки.

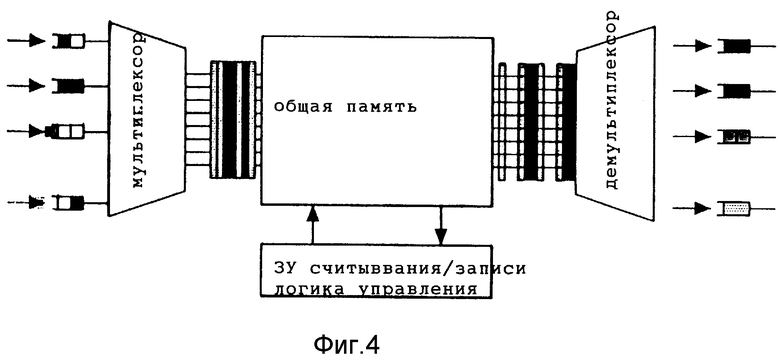

В случае, когда многомаршрутная коммутационная схема с разделением в пространстве выполняется с совместно используемым буфером в качестве входного буфера, как изображено в фиг.2, переполнение входных данных, вызванное в буфере рассеянного типа, можно устранить. Фиг.4 изображает пример коммутационной схемы с общей памятью, имеющей внутреннюю восьмибитовую параллельную структуру. Коммутационная схема с общей памятью (с разделением во времени) имеет простую структуру выполнения коммутации по тому же принципу, что и коммутационное устройство обычной коммутационной системы, изображенной в фиг. 4. Но в АРП, где скорость передачи составляет сотни Мб/сек, невозможно выполнить большой объем коммутационной схемы несмотря на параллельную передачу, поскольку ее скорость передачи гораздо быстрее, чем скорость действия памяти. Согласно сегодняшней технологии полупроводниковых устройств наибольший выполняемый размер коммутационной схемы находится в пределах объема 8•8 в случае восьмибитовой параллельной передачи данных.

Как указано выше, обычная технология АРП предпочитает легковыполнимый режим из числа: режимов с разделением во времени/разделением в пространстве, использования буфера, единого маршрута/множественных маршрутов в разработанной или предполагаемой сейчас коммутационной схемы АРП. Но обычная коммутационная схема АРП имеет следующие трудности.

В случае с разделением во времени ее емкость ограничена коммерчески доступным временем выборки памяти. Например, в восьмибитовой параллельной схеме АРП размер изготовляемой коммутационной схемы составляет 4-8 портов.

Во-вторых, для коммутационной схемы с множественными маршрутами маршруты маршрутизации являются множественными от порта ввода к порту вывода, поэтому для каждого вызова необходим анализ, чтобы не вызвать внутреннее блокирование в коммутационной схеме. Но этот способ предполагает слишком усложненный алгоритм управления и его невозможно осуществить, так как коммутационная схема становится крупнее.

В-третьих, в случае выполнения входного буфера в виде специализированного буфера, который назначают для каждого порта ввода, в коммутационной схеме с входным буфером и разделением в пространстве вероятность переполнения буфера возрастает в соответствии с входными характеристиками нагрузки, в результате чего из-за потери ячеек ухудшается качество обслуживания. Помимо этого эффективность использования буфера настолько низкая, что стоимость буфера должна увеличиться, чтобы рабочие показатели смогли быть на уровне режима с совместно используемым буфером.

Соответственно задача данного изобретения заключается в обеспечении коммутационной системы и способа коммутации асинхронного режима передачи для службы комплексного представления данных.

Другой задачей данного изобретения является обеспечение коммутационной системы с разделением в пространстве и способа повышения скорости коммутации коммутационной системы асинхронного режима передачи с помощью совместно используемого буфера и с единым маршрутом.

Еще одна задача данного изобретения заключается в обеспечении устройства и способа устранения внутреннего блокирования в коммутационной системе асинхронного режима передачи путем выполнения схем множественной маршрутизации.

Еще одна задача данного изобретения заключается в обеспечении устройства и метода обработки комплексно представляемой информации путем выполнения схемы копирования ячейки в коммутационной системе асинхронного режима передачи.

Еще одна задача данного изобретения заключается в обеспечении коммутационной системы и способа предотвращения конфликтов порта вывода путем анализирования маршрута вывода ячеек от коммутационной системы асинхронного режима передачи и обратного их отправления.

И еще одна задача данного изобретения заключается в обеспечении единообразной структуры ячеек, коммутируемых в коммутационной системе асинхронного режима передачи.

Для выполнения задач данного изобретения предлагается коммутационная система для выполнения асинхронного режима передачи, содержащая входной буфер для запоминания входных ячеек, входную коммутационную схему, составленную имеющими заданный размер обращенными коммутационными устройствами Баньяна и имеющую порты ввода и вывода, причем порты вывода подключены между входными буферами, а входная коммутационная схема выполняет функцию выборки и суммирования, при этом число введенных ячеек суммируют в ней в направлении от портов ввода к портам вывода, а адрес входного буфера передают в направлении от порта вывода к порту ввода в соответствии с числом суммированных ячеек, кроме того, входная коммутационная схема передает и запоминает входные ячейки во входном буфере в соответствии с результатом, вычисленным из функции выборки и суммирования, а также предусмотрена коммутационная схема копирования, составленная имеющими заданный размер обращенными коммутационными устройствами Баньяна и имеющая порты ввода, соединенные с входным буфером, причем коммутационная схема копирования выполняет функцию выборки и суммирования, при этом число скопированных в ней ячеек суммируют в направлении от портов ввода к портам вывода, а индекс копирования, соответствующий числу скопированных ячеек, передают в направлении от порта вывода к порту ввода, причем коммутационная схема копирования копирует и передает ячейки, выведенные из входного буфера, согласно результату, вычисленному из функции выборки и суммирования, предусмотрена также коммутационная схема обратной связи, составленная коммутационными устройствами заданного размера и имеющая порты ввода, соединенные с коммутационной схемы копирования, причем коммутационная схема копирования принимает отправленные обратно ячейки и сохраняет их до следующего цикла ячеек, далее предусмотрены таблица маршрутизации для запоминания данных в целях преобразования и замены данных для маршрутизации ячеек и контроллер маршрутизации/обратной связи для приема ячеек, выведенных из коммутационной схемы копирования, и ячеек, отправленных обратно из коммутационной схемы обратной связи, для маршрутизации-управления входными ячейками и отправленными обратной ячейками в соответствии с таблицей маршрутизации, и для обратного отправления ячеек, бывших в конфликте в портах вывода, а также коммутационные схемы маршрутизации, в которых множество коммутационных схем, составленных перемычными коммутационными устройствами заданного размера, соединены параллельно, причем коммутационные устройства коммутируют-выводят введенные ячейки и разделитель ячейки, соединенный с портами ввода коммутационных устройств маршрутизации, причем разделитель разделяет маршрутизированные-выведенные ячейки на число маршрутизирующих схем и передает их к коммутационным схемам маршрутизации, и наконец предусмотрен объединитель ячеек, соединенный с портами вывода коммутационных схем маршрутизации, причем объединитель объединяет и выводит ячейки, разделенные и выведенные из портов вывода коммутационных схем маршрутизации.

Способ выполнения коммутационной системы для выполнения асинхронного режима передачи зависит от того, как эксплуатируют различные элементы (режимы), или от того, какие элементы используют. В данном изобретении предлагается коммутационная система с разделением в пространстве, имеющая совместно используемый входной буфер и единый маршрут. Данное изобретение выполняют с разделением в пространстве по той причине, что разделение во времени имеет фундаментальную проблему ограниченного времени выборки памяти. В случае внутреннего блокирования в коммутационной системе единого маршрута снижаются рабочие показатели. Но в данном изобретении схемы маршрутизации обеспечиваются во множестве, чтобы гарантировать 100% их рабочих показателей. Кроме этого, в данном изобретении применен совместно используемый входной буфер, чтобы все порты ввода совместно использовали этот буфер. Поэтому эффективность использования входного буфера составляет 100%, а потери ячеек снижаются даже для буферов одинаковых размеров, таких как рассеянные буферы. Соответственно данное изобретение относится к типу с буферами с разделением в пространстве решетчатого типа, и к типу со смешанным буфером ввода/вывода. Для предотвращения внутреннего блокирования и конфликтов в порте вывода данное изобретение использует буферы как для этапов ввода, так и вывода.

Данное изобретение и присущие ему преимущества будут более понятны при обращении к следующему ниже подробному описанию вместе с прилагаемыми чертежами, в которых аналогичные обозначения указывают одни и те же или аналогичные компоненты.

Фиг. 1 - структура многомаршрутной, с разделением в пространстве коммутационной системы, имеющей буферы, специализированные для ее портов ввода,

Фиг. 2 - структура многомаршрутной, с разделением в пространстве коммутационной системы, имеющей буфер, совместно используемый ее портами ввода,

Фиг. 3 - пример коммутационной схемы с единым маршрутом (например, схема Баньяна объемом 8•8), в которой обуславливается внутреннее блокирование ячеек.

Фиг.4 - пример коммутационной схемы с общей памятью.

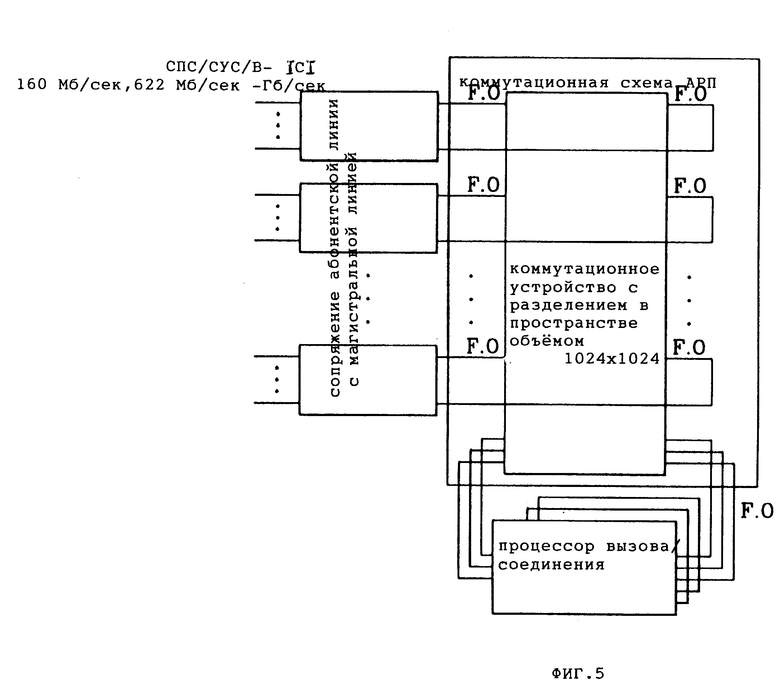

Фиг.5 - структура коммутационной системы АРП.

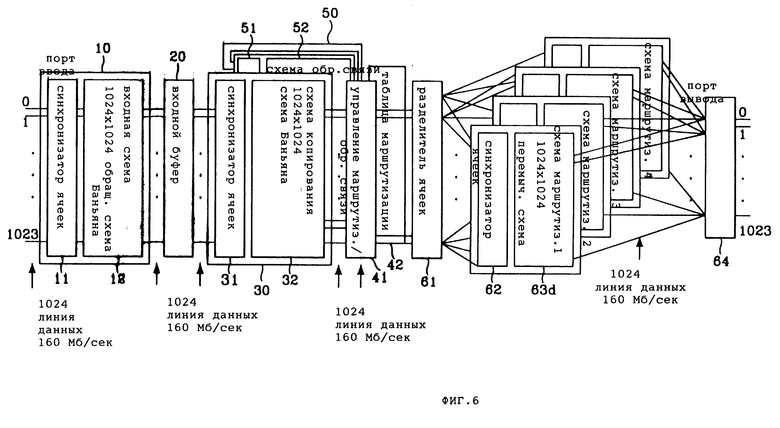

Фиг.6 - конфигурация коммутационной системы АРП, выполненной в соответствии с данным изобретением по фиг. 5.

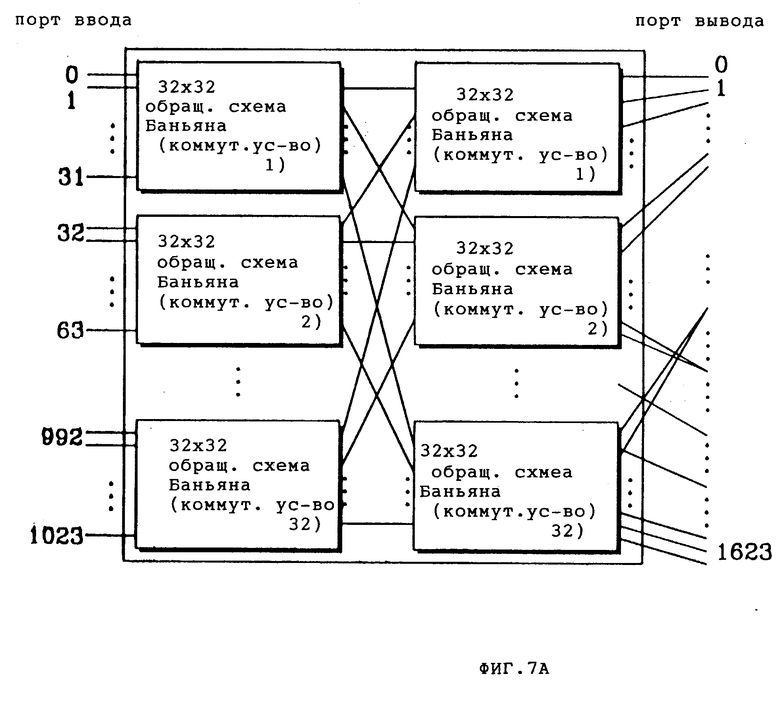

Фиг. 7А - пример, в котором входную схему фиг. 6 формируют в обращенной схеме Баньяна объемом 1024•1024.

Фиг. 7В - пример, в котором коммутационное устройство фиг.7А формируют в обращенной схеме Баньяна объемом 32•32.

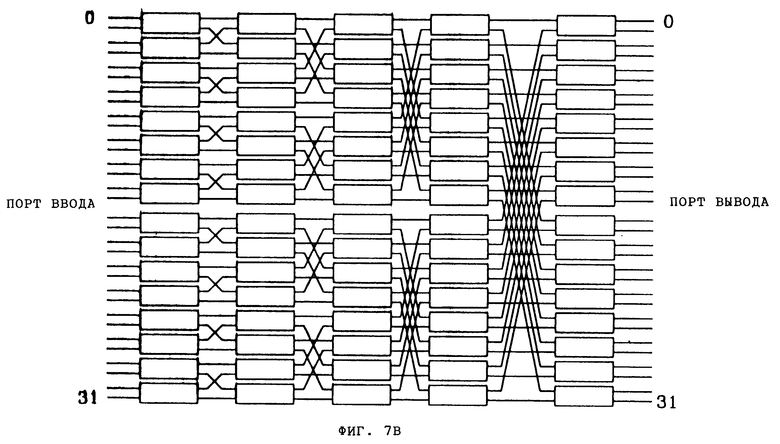

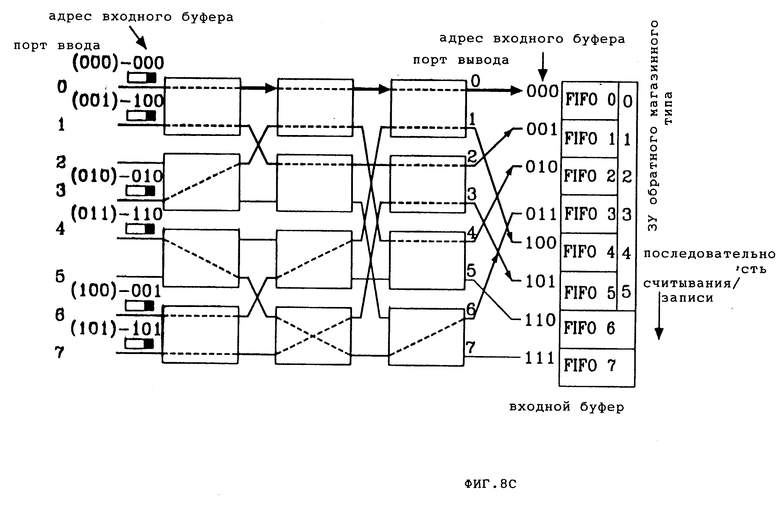

Фиг.8А - первый этап функции выборки и суммирования, в котором суммируют число ячеек, введенных из входной схемы, - на примере входной схемы объемом 8•8.

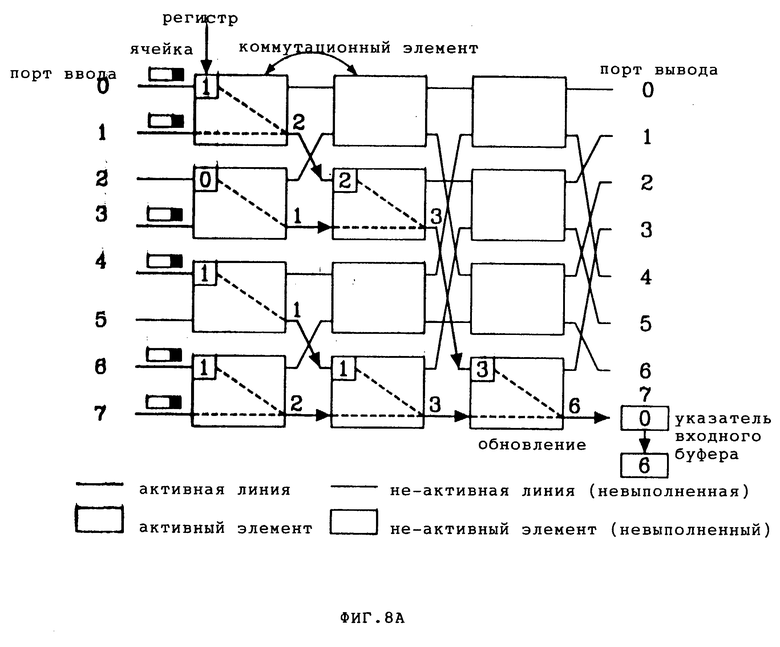

Фиг. 8В - второй этап функции выборки и суммирования, в котором адрес входного буфера передают из входной схемы, - на примере входной схемы объемом 8•8.

Фиг. 8С - этап передачи ячеек после функции выборки и суммирования во входной схеме, - на примере входной схемы объемом 8•8.

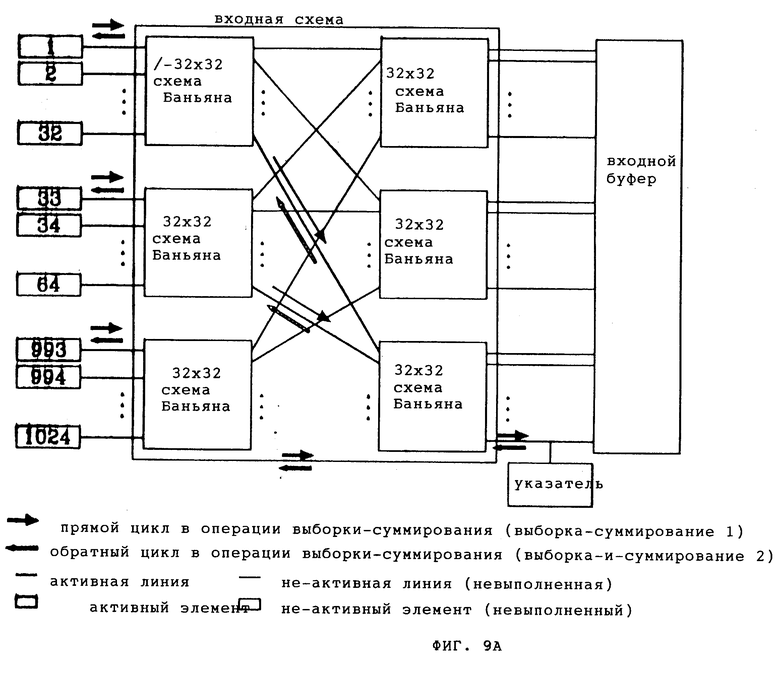

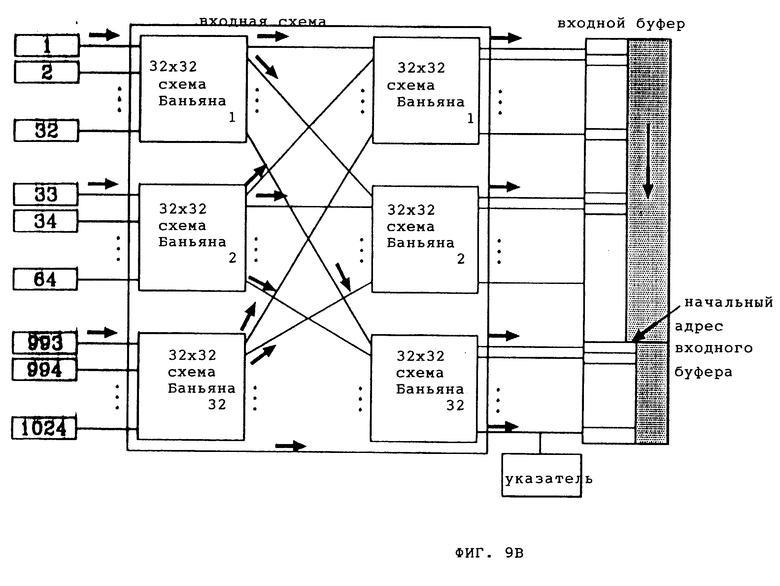

Фиг. 9А - процедура выполнения функции выборки и суммирования во входной схеме объемом 1024•1024.

Фиг. 9В - процедура выполнения функции передачи ячеек во входной схеме объемом 1024•1024.

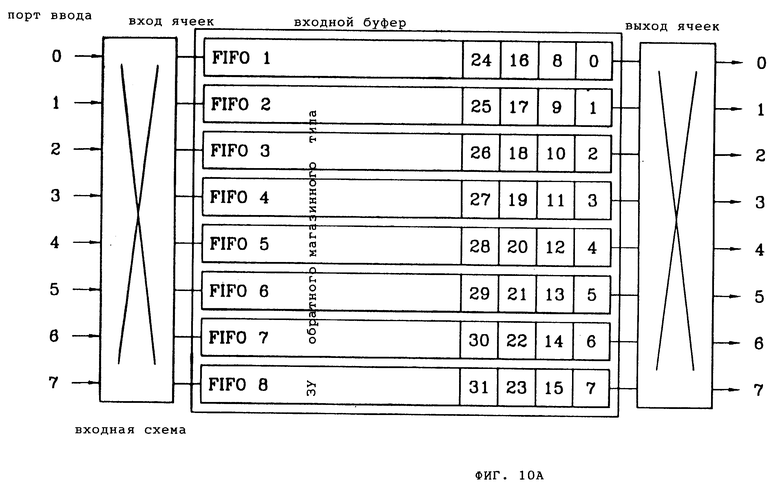

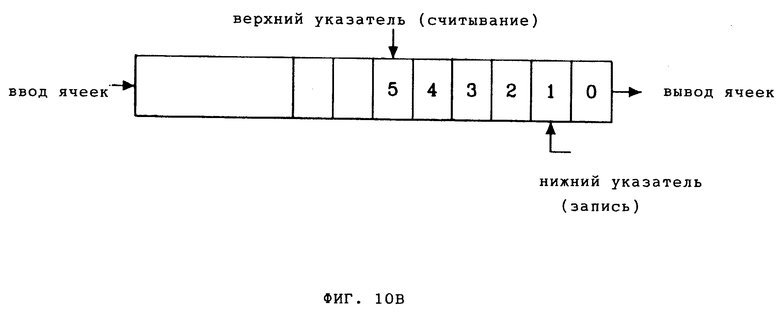

Фиг. 10А - структура входного буфера фиг. 6 - на примере входной схемы объемом 8•8.

Фиг.10В - принципиальная структура входного буфера, изображенного в фиг. 10А.

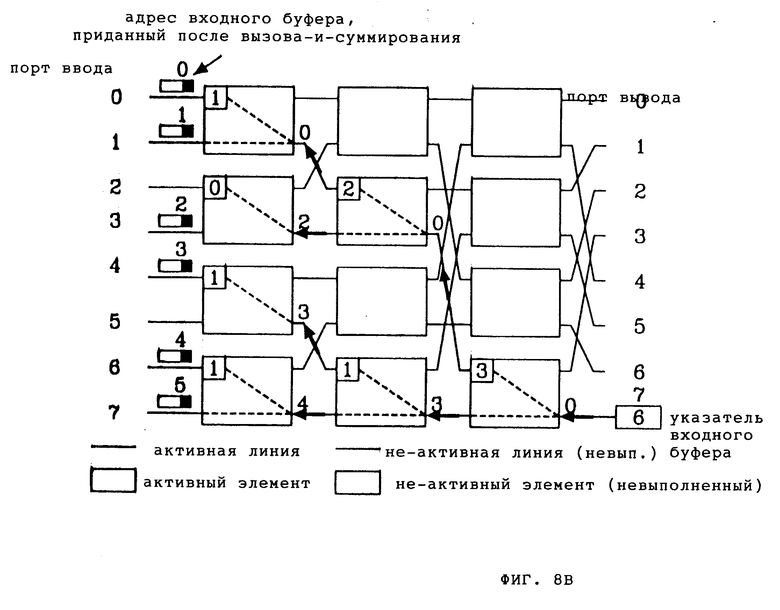

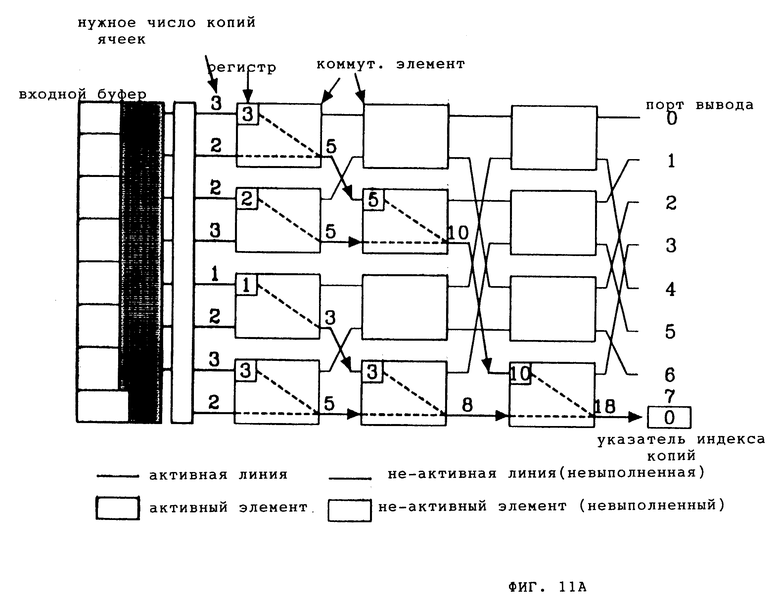

Фиг.11А - процедура выполнения первого этапа функции выборки и суммирования, в которой число копий ячеек суммируют в схеме копирования, - на примере схемы копирования объемом 8•8.

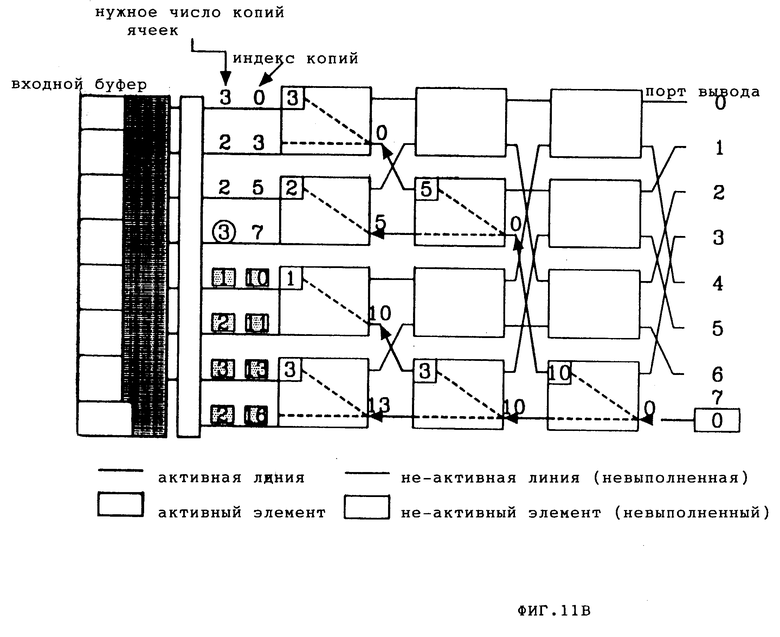

Фиг.11В - процедура выполнения второго этапа функции выборки и суммирования, в котором индекс копии передают в схему копирования, - на примере схемы копирования объемом 8•8.

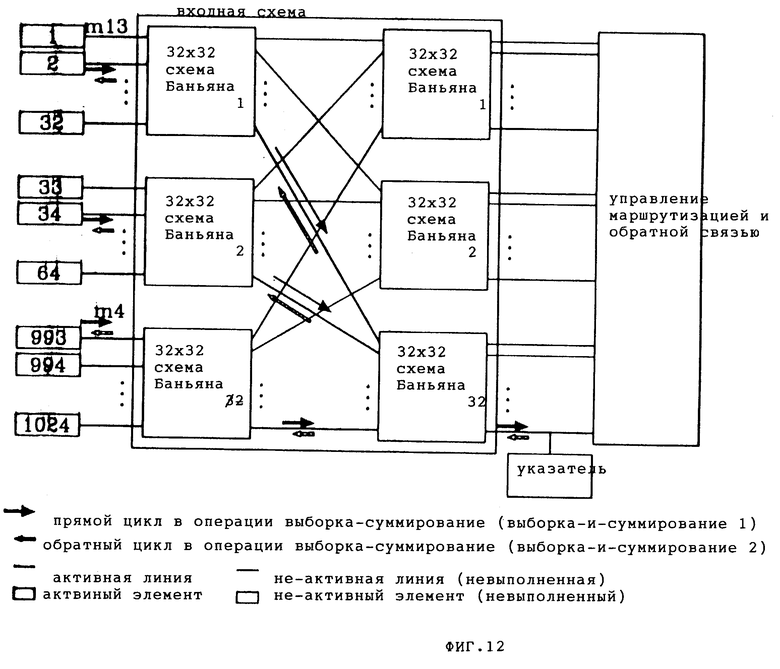

Фиг. 12 - процедура выполнения функции выборки и суммирования, в которой суммируют число копий ячеек, а индекс копирования передают в схему копирования, - на примере схемы копирования объемом 1024•1024.

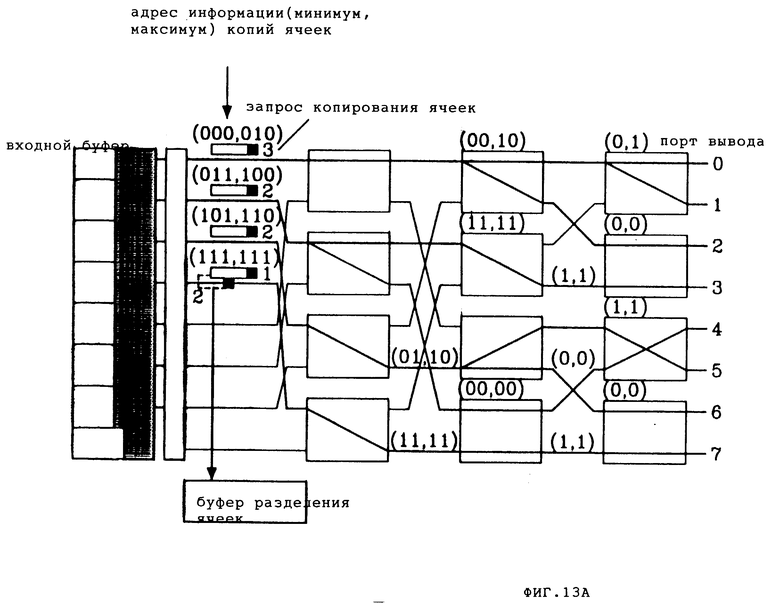

Фиг. 13А - схема, объясняющая функцию копирования ячеек после функции выборки и суммирования в схеме копирования объемом 8•8.

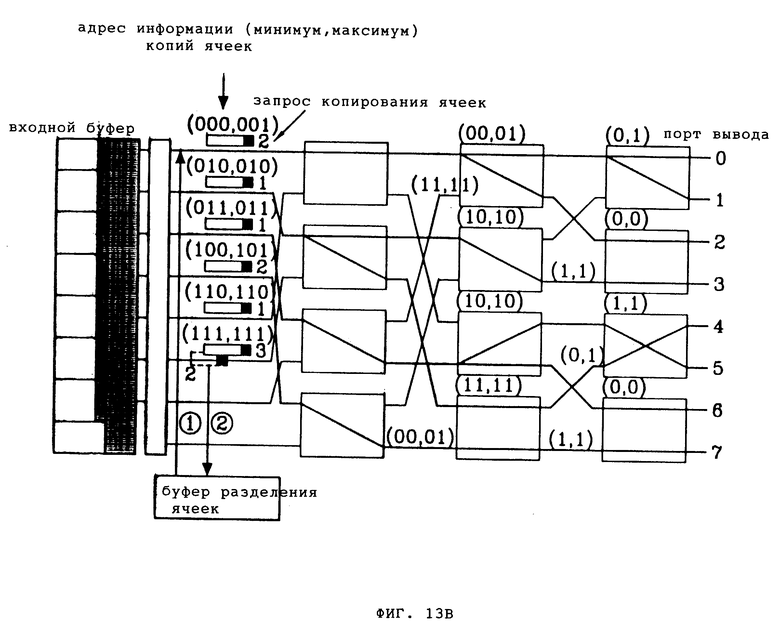

Фиг.13В - процедура копирования ячеек на следующем этапе после процедуры фиг. 13А в схеме копирования объемом 8•8 для объяснения функции копирования ячеек после функции выборки и суммирования.

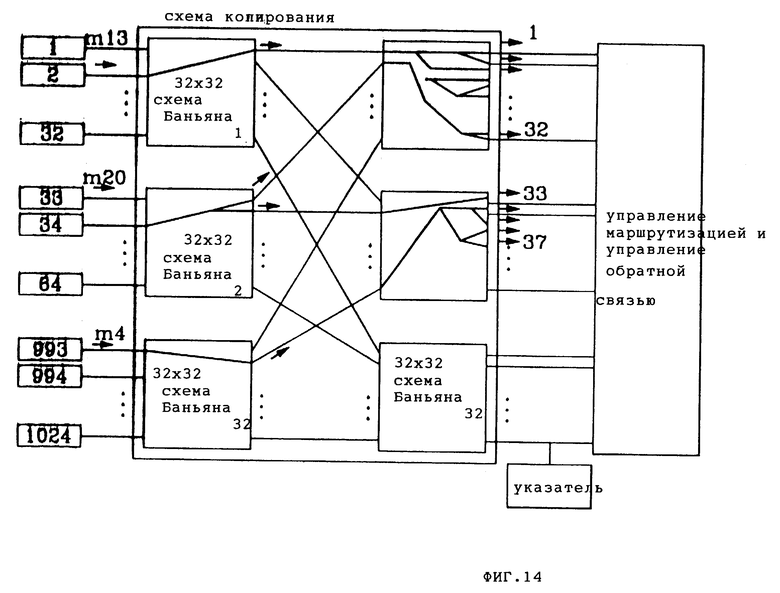

Фиг. 14 - процедура копирования введенных в данное время ячеек в схеме копирования объемом 1024•1024 для объяснения функции копирования ячеек после функции выборки и суммирования.

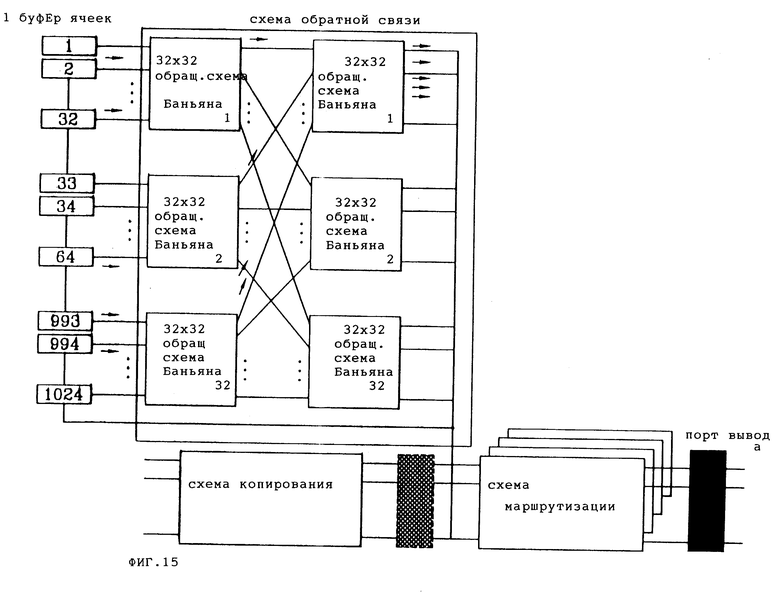

Фиг.15 - конфигурация схемы обратной связи объемом 1024•1024 по фиг.6.

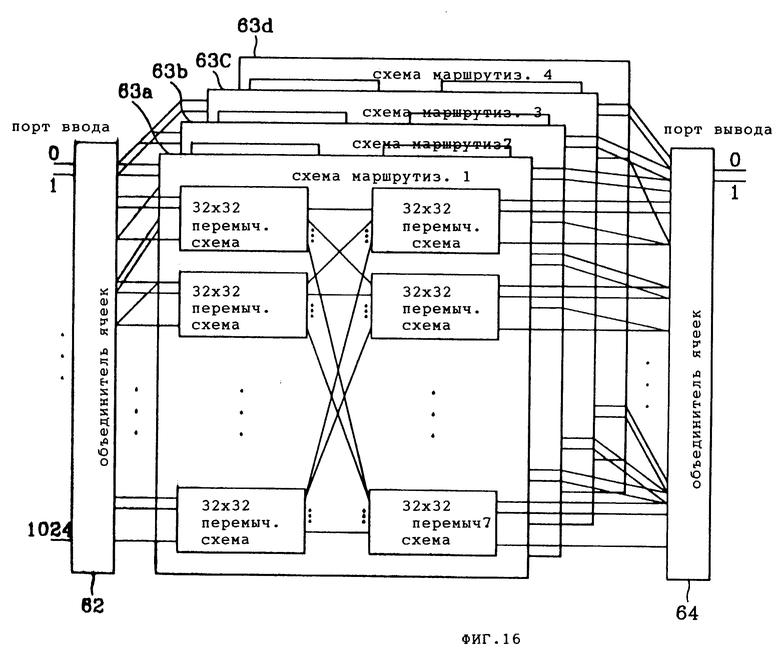

Фиг.16 - конфигурация четырех параллельных схем маршрутизации по фиг. 6.

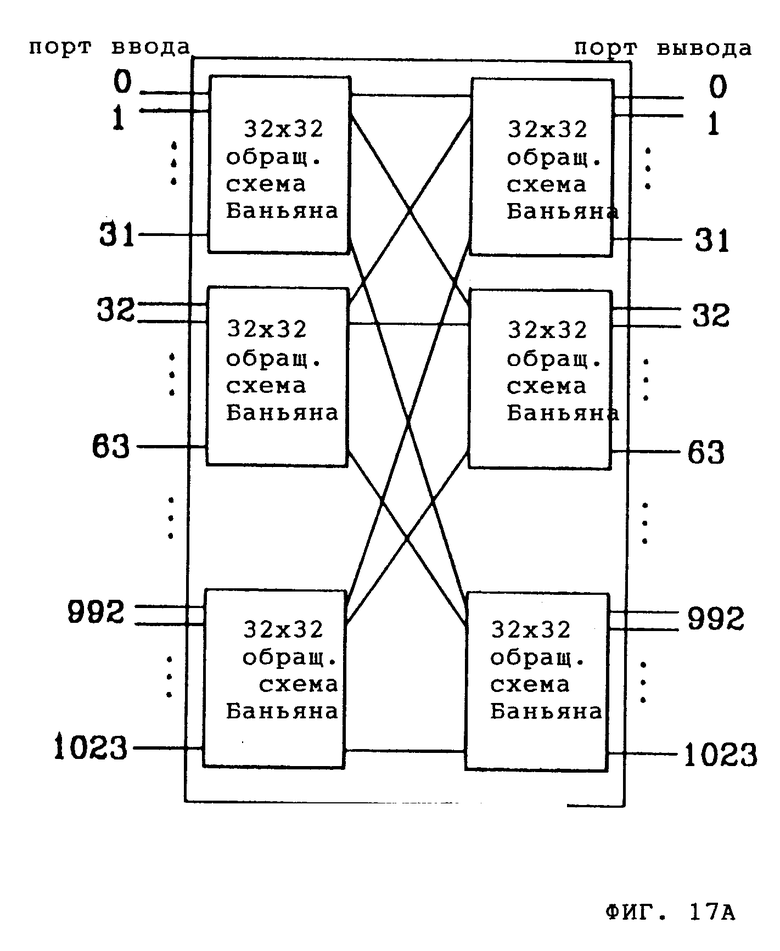

Фиг.17А - пример схем маршрутизации, выполненных в типе Баньяна.

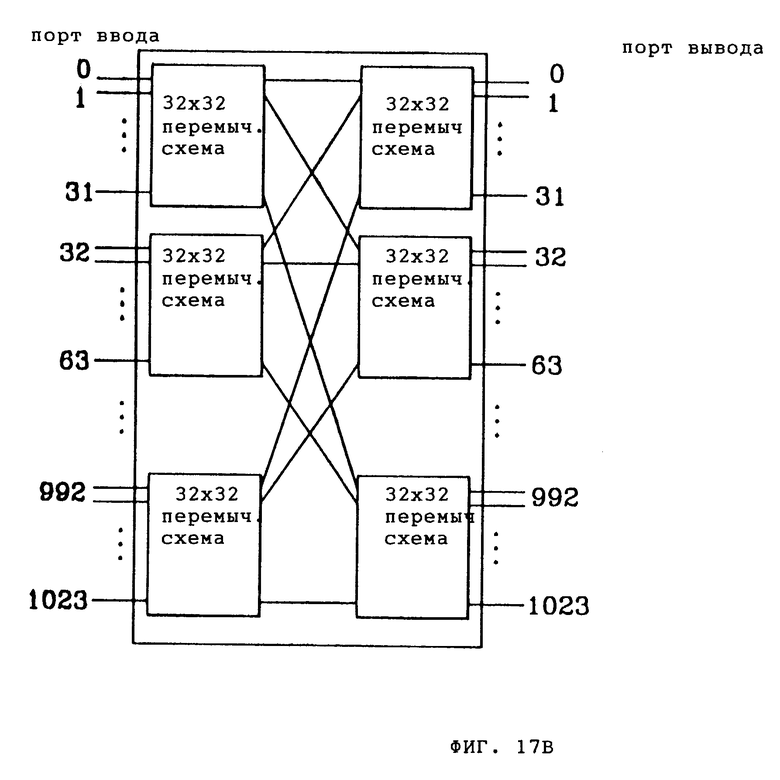

Фиг. 17В - пример схем маршрутизации в перемычном типе в соответствии с данным изобретением.

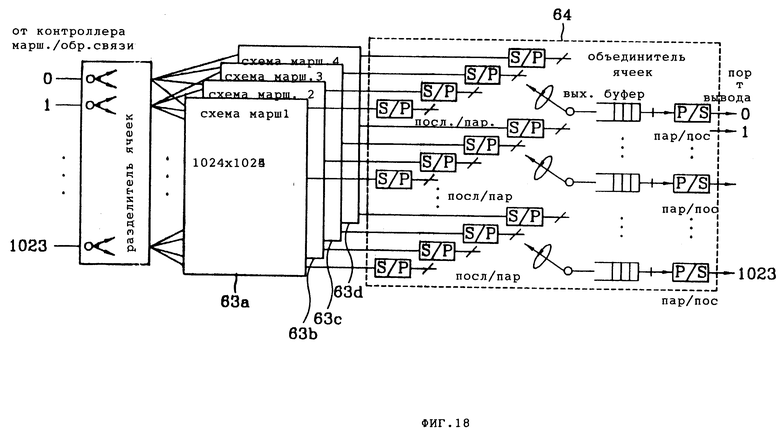

Фиг. 18 - структура разделителя ячеек, схем маршрутизации и объединителя ячеек в соответствии с данным изобретением.

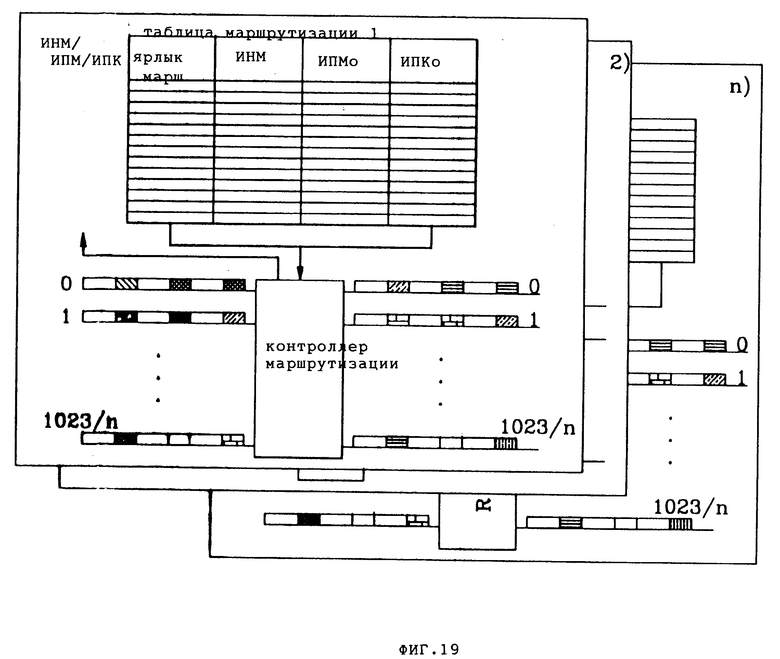

Фиг. 19 - структура таблицы маршрутизации фиг.6 и преобразования заголовков ячеек.

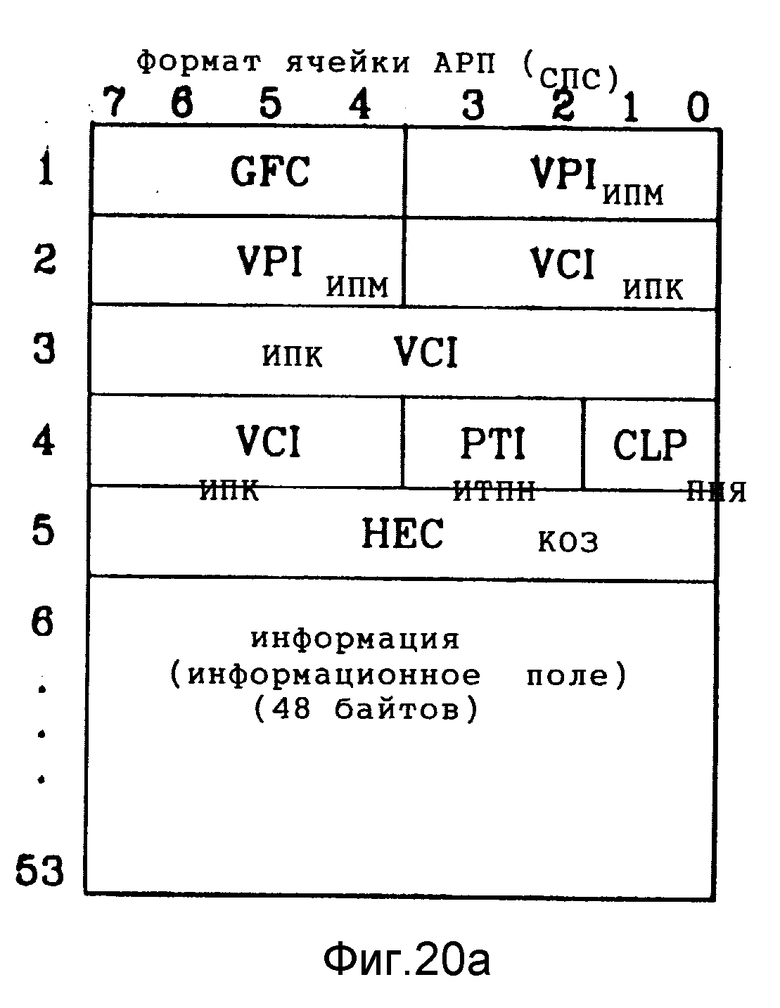

Фиг.20А - структура заголовка ячейки в СПС АРП.

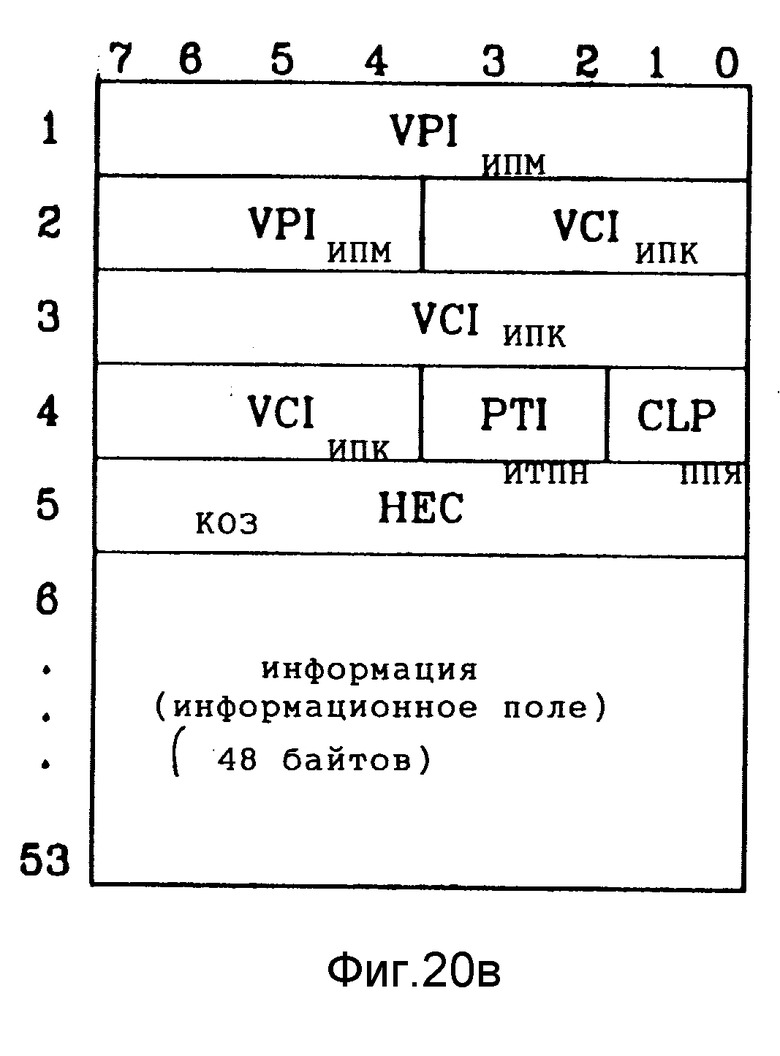

Фиг.20В - структура заголовка ячейки в СУС АРП.

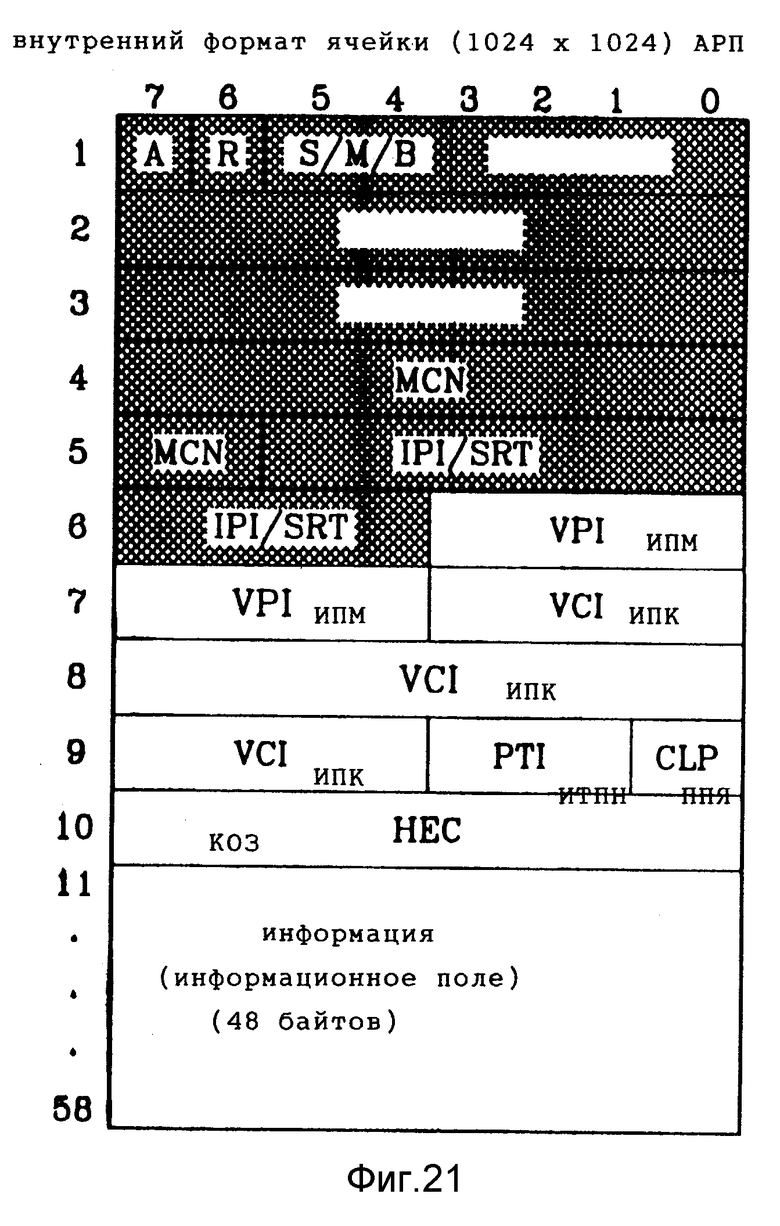

Фиг. 21 - структура заголовка ячейки, переданного в коммутационной схеме АРП в соответствии с данным изобретением.

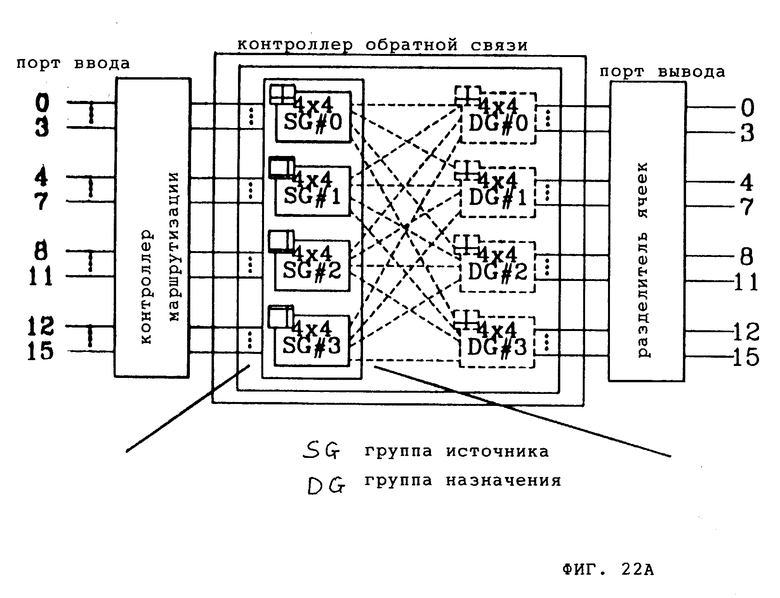

Фиг. 22А - функция предотвращения внутреннего блокирования схем маршрутизации - на примере схемы маршрутизации 16•16.

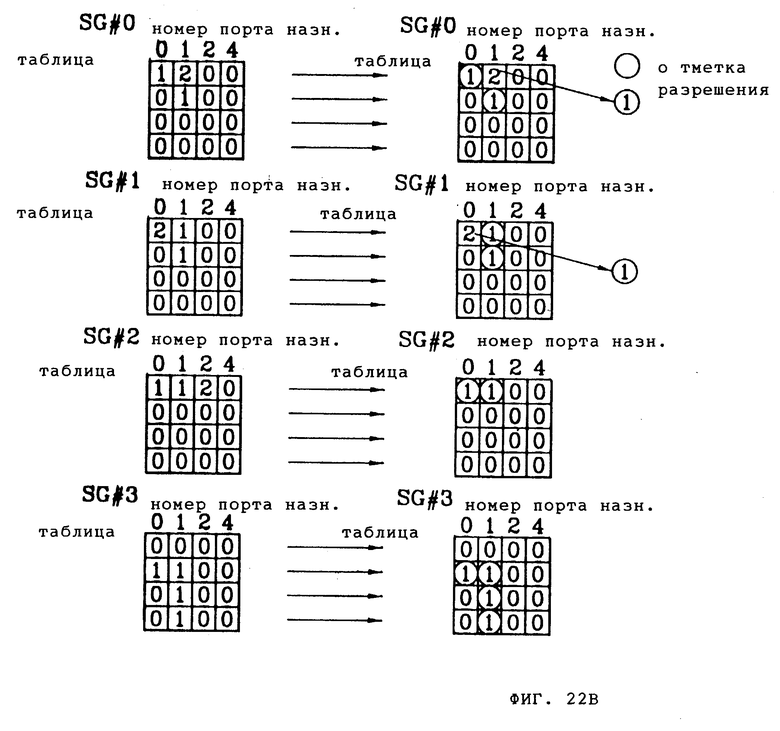

Фиг.22В - процедура предотвращения внутреннего блокирования в фиг.22А.

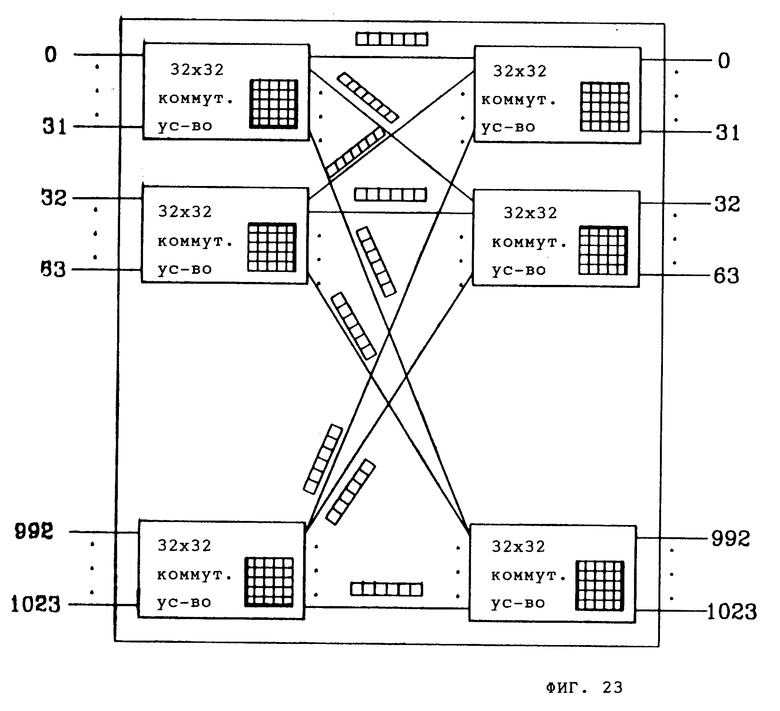

Фиг. 23 - функция предотвращения конфликта порта вывода в схемах маршрутизации - на примере схемы маршрутизации 1024•1024.

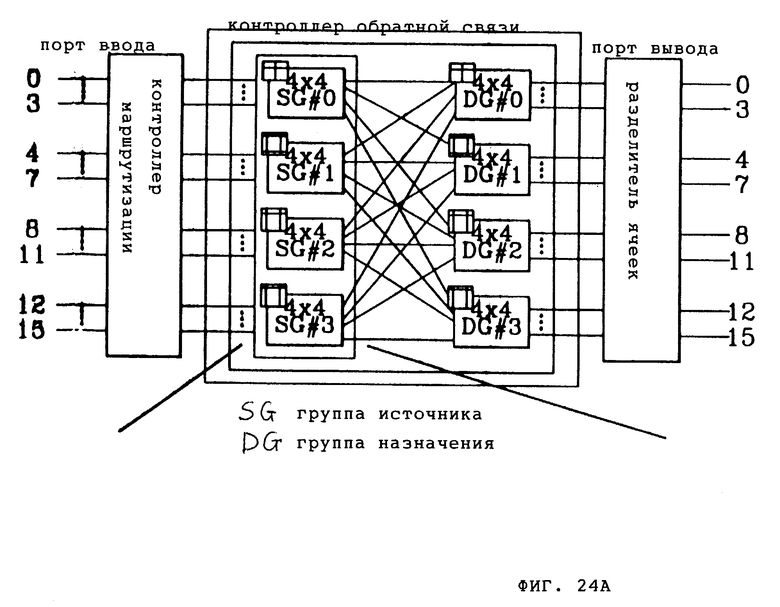

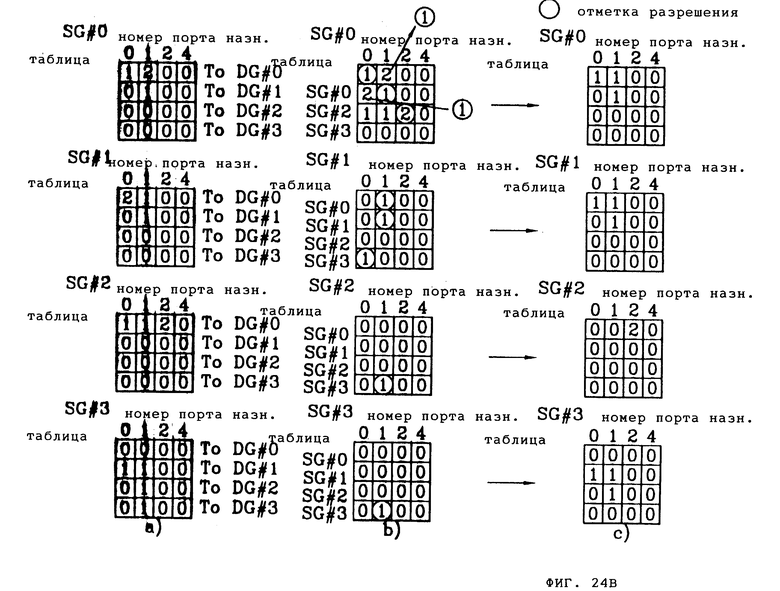

Фиг.24А - функция предотвращения конфликта порта вывода в схемах маршрутизации - на примере схемы маршрутизации 16•16.

Фиг.24В - процедура предотвращения конфликта порта вывода в фиг.24А.

Фиг.25 - процедура запоминания ячеек в выходном буфере по схемам маршрутизации - на примере схемы маршрутизации 1024•1024.

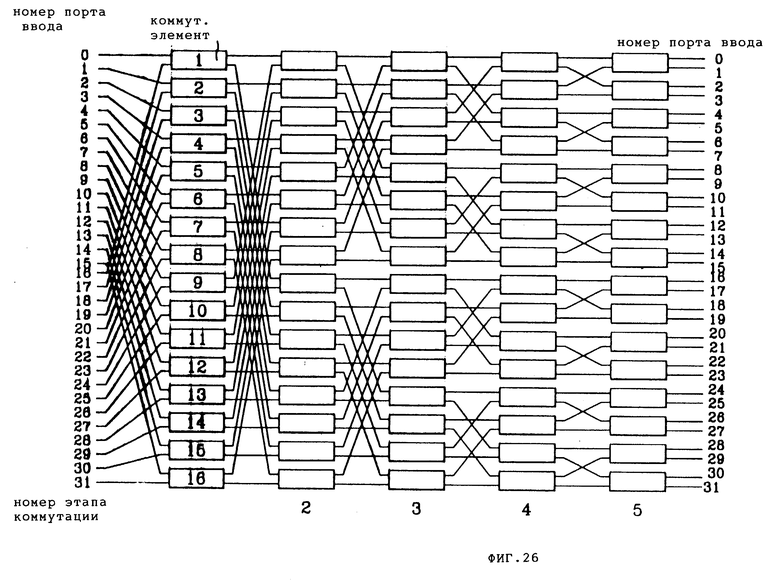

Фиг. 26 - структура коммутационных устройств Баньяна согласно данному изобретению - на примере коммутационного устройства Баньяна объемом 32•32.

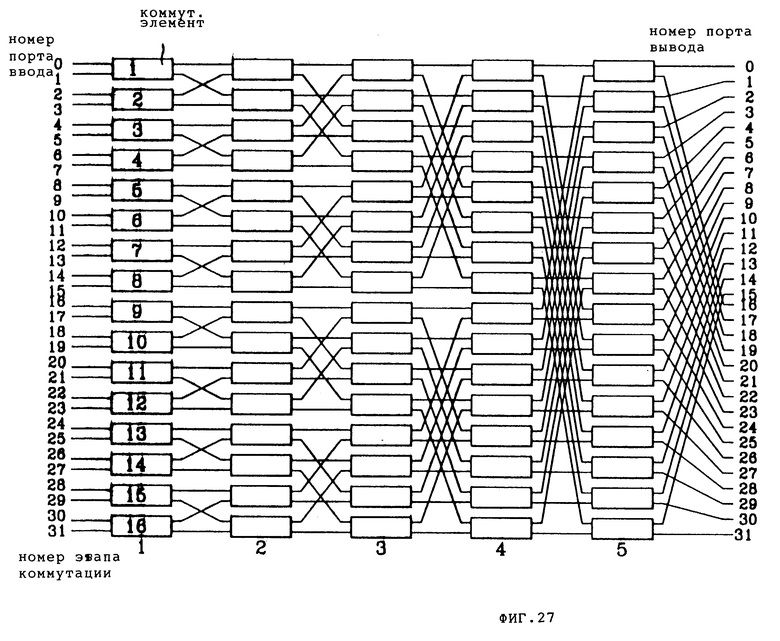

Фиг. 27 - структура обращенного коммутационного устройства Баньяна по данному изобретению - на примере обращенного коммутационного устройства Баньяна объемом 32•32, и

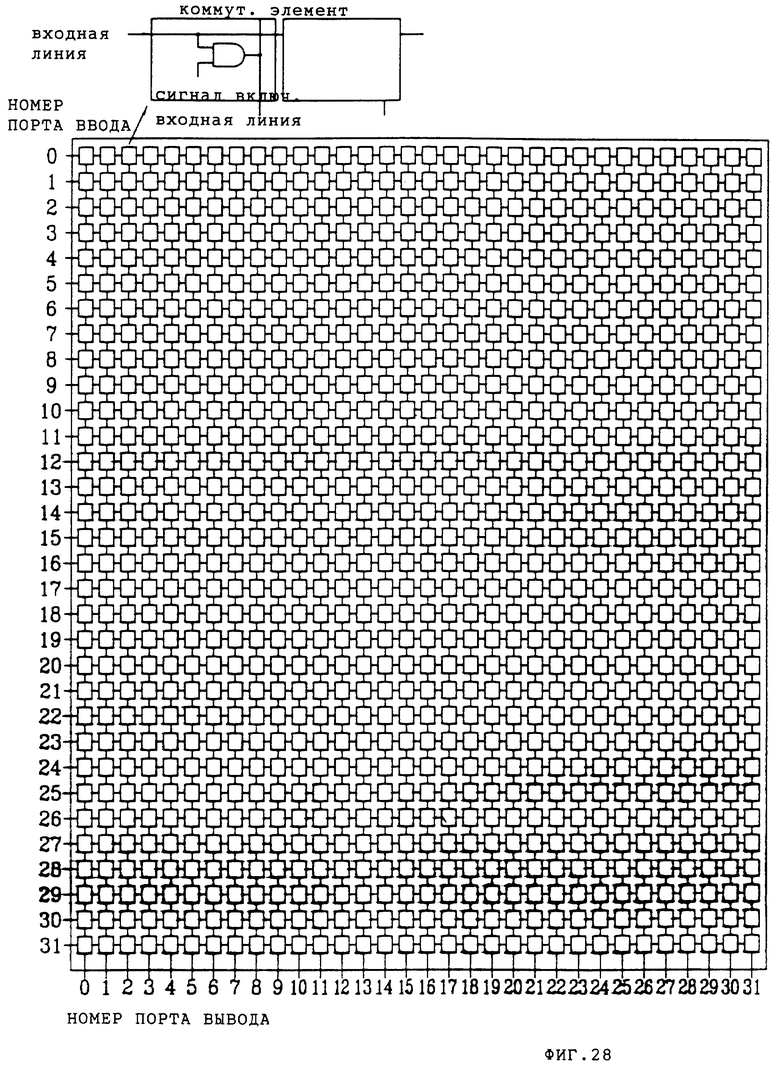

Фиг. 28 - структура перемычного коммутационного устройства по данному изобретению - на примере перемычного коммутационного устройства 32•32.

Подробное описание предпочтительного варианта осуществления

Фиг.5 изображает коммутационную систему АРП.

Предпочтительное осуществление данного изобретения предполагает структуру, функцию и выполненное устройство коммутационной схемы АРП (далее: коммутационная схема АРП или коммутационная схема), используемой в коммутационной системе АРП одного из компонентов схемы АРП. В этом изобретении предполагается, что коммутационная схема имеет объем 1024•1024.

Коммутационная система АРП составлена в основном из сопряжения абонентской линии с магистральной линией, коммутационной схемы АРП и процессора вызова/соединения, как изображено в фиг. 5.

Сопряжение абонентской линии с магистральной линией соединяет абонентскую и магистральную линии связи и выполняет различные функции коммутации ячеек АРП в коммутационной системе АРП. В коммутационной системе АРП используют 53 байта блока передачи информации, называемого ''ячейкой", и коммутацию выполняют в блоке ячеек в коммутационной схеме АРП.

Коммутационная схема АРП выполняет коммутационную функцию и многовещательную функцию для передачи входных ячеек к их заданным пунктам назначения. Информацию назначения (маршрутный ярлык) ячеек определяет процессор выборки/соединения, когда вызов установлен, и передают к соединителю абонента с магистральной линией связи. В области ячеек, введенных в сопряжение абонентской линии с магистральной линией, информацию маршрутизации записывают для каждой ячейки на основе информации назначения. Согласно записанной информации самомаршрутизацию выполняют в коммутационной схеме АРП. Многовещательная функция является функцией, выполняемой в случае передачи ячеек к по меньшей мере двум принимающим сторонам от одной передающей стороны, для чего требуется процесс копирования необходимого количества ячеек.

Функция процессора выборки/соединения предполагает управление (сигнализацию. . .) вызовом/соединением, управление маршрутизацией, эксплуатацию/сопровождение (ЭС) и управление ресурсами. Часть управления/сопровождения выполняет общее управление работой в коммутационной системе, такой как установка/отбой вызова по внутренней связи между процессорами более низкого уровня, находящимися в сопряжении абонентской линии с магистральной линией, функции АРП и общее сопровождение системы.

Как изображено на фиг. 6, коммутационная схема АРП коммутационной системы АРП по данному изобретению имеет входную схему, схему копирования, схему обратной связи, схему маршрутизации, периферийную логику для выполнения их функций, входной буфер, имеющий память, и коммутационное устройство с разделением в пространстве.

Коммутационная схема АРП представлена на примере с объемом 1024•1024 и выполнением ее функций. Соответствующие субсхемы, образующие такие коммутационные схемы, как входные схемы, схемы копирования, схемы обратной связи и маршрутизации, составлены коммутационными устройствами объемом 32•32. Для входной схемы и схемы обратной связи используют обращенную схему Баньяна. Для схемы копирования используют схему Баньяна. Для схемы маршрутизации можно использовать разнообразные коммутационные схемы, но здесь для легкости выполнения и обеспечения хороших рабочих показателей используют перемычную схему, в которой внутреннее блокирование не возникает.

Структура коммутационной схемы АРП по данному изобретению разделена на входную схему 12, схему копирования 32, схему обратной связи 52 и схему маршрутизации 63. Каждую из схем выполняют коммутационными устройствами объемом 32•32 на двух этапах. Здесь коммутационные устройства входной схемы 12 и схемы обратной связи 52 используют обращенную схему Баньяна, коммутационное устройство схемы копирования 52 использует схему Баньяна, и коммутационное устройство схемы маршрутизации 63 использует перемычную схему. В случае выполнения коммутационной схемы АРП согласно фиг. 6 с объемом 1024•1024 схема Баньяна и обращенная схема Баньяна сохраняют свои свойства даже несмотря на то, что коммутационные устройства объемом 32•32 состоят из двух этапов. Но перемычная схема не может сохранять внутреннее неблокирование. В этом случае блокирование можно вызвать внутри схемы маршрутизации 63, и ее рабочие показатели снижаются. Для устранения этого недостатка используют множество схем маршрутизации, например в данном изобретении четыре 63a-63d

В фиг. 6 синхронизаторы ячеек 11, 31, 51 и 62, расположенные спереди схем 12, 32, 52 и 63, используют потому, что синхронизация нужна на уровне бита и ячейки. Синхронизация необходима по той причине, что входная скорость ячеек, введенных в соответствующие схемы, равна 160 Мб/сек и схемы могут помещаться в физически разных местоположениях.

На фиг. 6 синхронизаторы ячеек 11, 31, 51 и 62 расположены на входном этапе коммутационного устройства 32•32 соответствующих схем 12, 32, 52 и 63. Синхронизаторы ячеек выполняют синхронизацию битов со скоростью и синхронизацию ячеек со скоростью 160 Мб/сек.

Входная схема 12 использует обращенную схему Баньяна 1024•1024 и она состоит из 64 коммутационных устройств (обращенных схем Баньяна объемом 32•32). Входную схему 12 подключают между синхронизатором ячеек 11 и входным буфером 20, и она выполняет функции выборки и суммирования входных ячеек и функцию запоминания входных ячеек во входном буфере 20.

Входной буфер (входная очередь) 20 запоминает входные ячейки, выведенные из входной схемы 12. Размер входного буфера 20 определяется размером порта ввода и входными ячейками (1024 • х ячеек = ххх ячеек)

Схема копирования 32 использует схему Баньяна 1024•1024 и она состоит из 64 коммутационных устройств (схемы Баньяна объемом 32•32). Схему копирования 32 подключают между синхронизатором ячеек 31 и контроллером маршрутизации/обратной связи 41, и она выполняет функцию выборки и суммирования ячеек и функцию копирования ячеек.

Схема обратной связи 52 использует обращенную схему Баньяна 1024•1024, и состоит из 64 коммутационных устройств (обращенные схемы Баньяна 32•32). Схема обратной связи 52 подключена между синхронизатором ячеек 51 и контроллером маршрутизации/обратной связи 41, и выполняет вызов и суммирование отправленных обратно ячеек и функцию копирования ячеек.

Таблица маршрутизации 42 запоминает информацию маршрутизации (ИПМ/ИПК, ярлык маршрутизации) ячеек в коммутационном устройстве АРП. Контроллер 41 маршрутизации/обратной связи принимает ячейки из схемы копирования 32 и схемы обратной связи 52, и управляет маршрутизацией входных ячеек в соответствии с информацией маршрутизации таблицы маршрутизации 42. Управление маршрутизацией контроллера 41 маршрутизации/обратной связи выполняет функцию обеспечения информации маршрутизации (ИПМ/ИПК) и ярлыка самомаршрутизации для заголовка входной ячейки. Управление обратной связью выполняет внутреннее блокирование коммутационной схемы АРП и конфликта порта вывода.

Разделитель ячеек 51 выполняет функцию разделения ячеек, выведенных из схемы копирования 32 и схемы обратной связи 52. В данном изобретении разделитель ячеек 51 разделяет и передает входные ячейки к схемам множественной маршрутизации в целях предотвращения внутреннего блокирования коммутационной схемы АРП и конфликта порта вывода. Предполагается, что в данном изобретении используют четыре схемы маршрутизации 63а-63d. Схемы маршрутизации состоят из перемычных схем 1024•1024 и 64 коммутационных устройств (переменные схемы 32•32). Схемы маршрутизации выполняют самомаршрутизацию. Объединитель ячеек 64 запоминает ячейки, выведенные из схем маршрутизации 6За-63d в выходном буфере портов, и выводит их.

Структура и функция соответствующих схем будут описаны ниже со ссылкой на фиг. 6.

Входная схема 12 выполняет функцию выборки и суммирования, в которой входным буфером 20 для запоминания ячеек, введенных из портов ввода, управляют в целях совместного использования портами ввода. В соответствии с функцией выборки и суммирования все входные ячейки портов ввода принимают адрес входного буфера 20, в котором они должны быть запомнены, и запоминаются во входном буфере 20 в соответствии с адресом после входной схемы 12. Входной буфер 20 является совместно используемым буфером, а не специализированным буфером, поэтому он обладает хорошей эффективностью использования и очень эффективен при пакетной нагрузке. Ячейки, запомненные во входном буфере 20, передают в схему копирования 32 в последовательности их запоминания. Имеет место ограничение числа ячеек, передаваемых в схему копирования 32 от входного буфера 20 во время коммутации. Это происходит, когда число ячеек, скопированных в предыдущем цикле ячеек, превышает емкость схемы копирования 32, или когда обратно отправленные ячейки присутствуют в схеме обратной связи 52.

Схему копирования 32 используют для службы вещательных передач или множественного вещания. Схема копирования 32 выполняет функцию копирования необходимого числа ячеек, если ячейки, принятые из входного буфера 20, являются ячейками вещательной передачи или множественного вещания. Здесь число копий ячеек указывается в заголовке ячейки в виде минимума, максимума. Алгоритм копирования ячеек в режиме разделения ячеек используют в схеме копирования 32 сообразно с этим значением. Минимум и максимум вычисляют по результату выборки и суммирования и числу копий, нужных для соответствующих ячеек в схеме копирования 32. Если сумма числа копированных ячеек превышает емкость схемы копирования 32, то превышающие ячейки выбирают и суммируют и вводят обратно в схему копирования 32 в следующем цикле ячеек, и пока их не считывают из входного буфера 20.

Схему обратной связи 52 используют для обратного отправления ячеек, которые должны пройти схемы маршрутизации 63 в том же цикле ячеек, кроме ячеек, не вызывающих внутреннее блокирование или конфликт порта вывода при прохождении по схемам маршрутизации 63. Отправленные обратно ячейки обратной связи подвергаются процедуре прохождения по схемам маршрутизации 63 вместе с ячейками, принятыми по схеме копирования 32, в следующем цикле ячеек. Контроллер маршрутизации/обратной связи 41 управляет приданием приоритета обратно отправленным ячейкам. Схема обратной связи 52 использует буфер одной ячейки на один порт на входном этапе схемы обратной связи, чтобы задержать обратно отправленные ячейки на один цикл ячейки.

Контроллер 41 маршрутизации/обратной связи состоит из контроллера маршрутизации и контроллера обратной связи. Контроллер маршрутизации контроллера 41 маршрутизации/обратной связи выполняет функцию придания ярлыка маршрутизации ячейками, проходящих по схемам маршрутизации 63, и такую функцию маршрутизации ячеек, как преобразование заголовка ячейки. Ярлык маршрутизации используют в самомаршрутизации, в которой ячейки при помощи аппаратуры осуществляют поиск предназначенного им порта вывода по схемам маршрутизации 63. Преобразование заголовка ячеек является функцией преобразования заголовка входных ячеек, в результате чего информацию о заголовках ячеек, выведенную из ее собственного узла, используют в маршрутизации следующего узла. Относящиеся к маршрутизации значения, такие как ярлык маршрутизации и информация преобразования заголовков ячеек, обновляют контроллером вызова/соединения фиг. 5, когда установлен вызов/соединение, и запоминают в таблице маршрутизации 42 до тех пор, пока соответствующий вызов/соединение не будет разъединен.

Контроллер обратной связи контроллера маршрутизации/обратной связи 41 выполняет функцию предотвращения потери ячеек из-за внутреннего блокирования или конфликта порта вывода в схемах маршрутизации 63. Функцию управления обратной связью выполняют для каждого цикла ячеек, и ячейки, которые не смогли пройти по схемам маршрутизации 63, отправляют в схему обратной связи 52. Число ячеек, проходящих по схемам маршрутизации 63, для всех портов вычисляют для каждого цикла ячеек. Это значение указывает число ячеек, переданных без внутреннего блокирования или конфликта портов ввода в схемах маршрутизации 63a-63d. Здесь внутреннее блокирование означает, что конфликт происходит по внутреннему маршруту даже когда ячейки, введенные в схему, требуют разные порты вывода. Конфликт порта вывода означает, что входные ячейки конфликтуют в порте вывода даже когда их передают без внутреннего блокирования, если для входных ячеек требуется один и тот же порт вывода.

Разделитель ячеек 61 распределяет ячейки по схемам маршрутизации 63a-63d в целях предотвращения внутреннего блокирования и конфликта порта вывода в схемах маршрутизации 63, когда проходящие по схемам маршрутизации ячейки 63 вводят в соответствии с управлением обратной связью.

В схемах маршрутизации 63 выполняют фактическую коммутацию ячеек. Входные ячейки из сети копирования 32 и сети обратной связи 52 самомаршрутизируются аппаратурой и передаются к нужному порту вывода по схемам маршрутизации 63. Здесь схему маршрутизации 1024•1024 используют в таком виде, в каком перемычные схемы 32•32 формируют в два этапа как коммутационные устройства. Эта схема маршрутизации не является неблокирующей сетью и поэтому может снижать рабочие показатели по причине внутреннего блокирования в коммутационной схеме. Поэтому в данном изобретении для увеличения входного/выходного маршрута коммутационной схемы АРП и для осуществления управления обратной связью до ввода ячеек в схемы маршрутизации в целях устранения внутреннего блокирования формируют четыре параллельных схемы маршрутизации 63a-63d. Благодаря этому предотвращается ухудшение работы коммутационной схемы. Несмотря на то, что внутреннее блокирование устраняют из схем маршрутизации 63, рабочие показатели коммутационной схемы АРП ограничиваются 58% из-за конфликта порта вывода. Соответственно рабочие показатели коммутации приближаются к 100%, если схемы маршрутизации 63 сформированы параллельно и во множестве и имеют управление обратной связью, а коммутационная схема АРП устраняет внутреннее блокирование и применяет управление конфликтом порта вывода. Формирование схем маршрутизации 63а-63d объемом 1024•1024 с коммутационными устройствами 32•32 увеличивает количество аппаратуры и имеет множественные маршруты между портами ввода и портами вывода схемы. Поэтому при маршрутизации ячеек управлять 1024 портами трудно.

Объединитель ячеек 64 запоминает ячейки, выведенные из схем маршрутизации 63-63d в выходном буфере и выводит их на заданной скорости. Используемый выходной буфер имеет очень низкую производительность по сравнению с входным буфером, поскольку этот буфер в противоположность входному буферу является специализированным для соответствующих портов вывода.

Ниже следует подробное описание функций входной схемы 12, схемы копирования 32, схемы 52 обратной связи и схемы маршрутизации 63. В данном изобретении предполагается, что объем коммутационной схемы АРП - 1024•1024. Поэтому общие функции коммутационной схемы АРП, такие как функция выборки и суммирования, копирования ячеек и маршрутизация, должны выполняться для всей схемы 1024•1024, а не для схем коммутационного устройства. Коммутационная схема АРП по данному изобретению выполнена входной сетью 12, сетью копирования 32, сетью обратной связи 52 и сетью маршрутизации 63. Чтобы быть выведенными окончательно, входные ячейки должны пройти по меньшей мере три схемы из числа указанных схем. Действие коммутационной схемы АРП целиком объясняется конкретно с ее разделением на входную схему, схему копирования 32, схему обратной связи 52 и схему маршрутизации 63.

Входная схема 12 выполняет функцию выборки и суммирования и передачи ячеек для эффективного использования входного буфера 20, когда ячейки запоминают во входном буфере 20. Передачу ячеек выполняют обращенной схемой Баньяна 1024•1024. Функцию выборки и суммирования можно выполнять в обращенной схеме Баньяна, поскольку она имеет принципиально одинаковую структуру, что и обращенная схема Баньяна. Но функцию выборки и суммирования выполняют аппаратурой отдельно от обращенной схемы Баньяна, поскольку для этого не требуется вся обращенная схема Баньяна, и она не предназначается для передачи ячеек, как во входной схеме 12. Входная схема 12 выполнена коммутационными устройствами обращенных схем Баньяна 32•32 на двух этапах, как показано на фиг. 7А, в целях облегчения выполнения аппаратуры. Обращенная схема Баньяна 32•32 имеет структуру, изображенную в фиг.7В. Ниже следует подробное описание входной схемы 12.

В соответствии с функцией выборки и суммирования входной схемы 12 обеспечивают буферный адрес, где хранится сама ячейка, поэтому все ячейки, принятые в портах ввода коммутационной схемы АРП, запоминают последовательно во входном буфере 20. Здесь обеспечивают адрес буфера и поэтому буфер 20 совместно используют все порты ввода. В процессе обеспечения адреса буфера необходим бит, указывающий, имеют ли порты ввода активные ячейки или нет, и биты, в которых записывают адрес входного буфера. Эти виды информации записывают в заголовок ячейки. Функцию выборки и суммирования выполняют в виде "конвейера" для каждого цикла ячеек вместе с функцией передачи ячеек. Функцию выборки и суммирования для входных ячеек в n-м цикле выполняют в (n-1)-м цикле. В n-м цикле выполняют выборку и суммирование ячеек, введенных в (n+1)-м цикле.

Фиг. 8А и 8В изображают процедуру запоминания входных ячеек во входном буфере 20 на примере, когда имеется шесть входных ячеек и указателем буфера ввода является "0" - относительно единой передачи в объеме 8•8. Указатель входного буфера 20 представляет начальный адрес входного буфера 20, в котором ячейки запоминают для текущего в данное время цикла. Далее, со ссылкой на фиг.8А и 8В следует описание первого и второго этапов выполнения функции выборки и суммирования входной схемы 12.

Во-первых, со ссылкой на фиг.8А первый этап функции выборки и суммирования, который является процедурой суммирования ячеек из порта ввода в порт вывода, происходит следующим образом. Здесь элементы коммутации указаны как просто "элементы".

Когда ячейка, введенная в порт ввода более высокого уровня, имеется на первом этапе элемента 2•2 входной схемы 12, в регистре элемента записывают число "1" независимо от того, принимает или не принимает ячейку порт ввода более низкого уровня. Ввод ячеек в порты ввода более высокого и более низкого уровня элемента первой ступени суммируют для направления к порту вывода более низкого уровня. Эту величину вводят в элемент, соединенный со вторым этапом.

Таким же образом, как и на первом этапе, относительно ячеек, введенных в элемент на втором этапе, число ячеек, введенных в порт ввода более высокого уровня, записывают в регистре элемента, а ячейки, введенные в порты более высокого уровня и более низкого уровня, суммируют и затем направляют к порту вывода более низкого уровня. Это значение вводят в элемент, подключенный к третьему этапу.

Также на третьем этапе относительно ячеек, введенных в элемент, число ячеек, введенных в порт ввода более высокого уровня, записывают в регистре элемента, а ячейки, введенные в порты ввода более высокого уровня и более низкого уровня, суммируют и затем направляют к порту вывода более низкого уровня.

После изложенного выше процесса результат суммирования вводов ячеек выводят к низшему порту на окончательном этапе, как показано в фиг.8А. Это последнее значение суммируют со значением регистра указателя входного буфера 20, и результат запоминают снова в регистре указателя входного буфера. Это значение указывает начальный адрес входного буфера в следующем цикле ячеек. В примере фиг. 8А значение указателя предшествующего этапа предполагается равным "0", шесть ячеек снова вводят, в результате чего значение указателя обновляется до шести.

Во-вторых, ссылаясь на фиг. 8В, второй этап функции выборки и суммирования, который является процедурой передачи адреса входного буфера 20 из порта вывода в порт ввода, выполняется следующим образом.

Равное "0" значение указателя, запомненное в предыдущем цикле ячеек, вводят низшим портом вывода на последней стадии и передают к элементу второго этапа через порт ввода более высокого уровня. Через порт ввода более низкого уровня переданное значение суммируют со значением, записанным в регистре элемента на первом этапе выборки и суммирования, направляют к элементу второго этапа.

Элемент второго этапа передает значение, принятое от третьего этапа, к элементу первого этапа, через порт ввода более высокого уровня. Через порт ввода более низкого уровня переданное значение суммируют со значением, записанным в регистре элемента на первом этапе выборки и суммирования, и направляют к элементу первого этапа.

В элементе первого этапа значение, принятое со второго этапа, передают к порту ввода более высокого уровня. Это значение суммируют со значением, записанным в регистре элемента на первом этапе выборки и суммирования, и направляют к порту ввода более низкого уровня.

После изложенной выше процедуры ячейки общих портов ввода принимают адрес входного буфера 20, где они должны быть запомнены. Ячейки принимают свои адреса 0, 1, 2, 3, 4 и 5 входного буфера последовательно из ячейки самого высокого порта портов ввода, в которые введены ячейки, так как входных ячеек шесть в фиг. 8В. Фиг.8А и 8В изображают процедуру суммирования числа ячеек на первом этапе и процедуру передачи адреса входного буфера на втором этапе, когда выполняют входную схему 8•8. Фиг.9А изображает первый и второй этап выборки и суммирования во входной схеме 12 объемом 1024•1024.

В-третьих, после первого и второго этапов выборки и суммирования выполняют передачу ячеек, как в фиг.8С. Ссылаясь на фиг.8С, передача ячеек входной схемы 12 осуществляют таким образом, чтобы все ячейки получили свои адреса входного буфера, в которых они должны быть запомнены, от функции выборки и суммирования, и затем они используются в качестве ярлыка маршрутизации ячеек, которые должны пройти обращенную схему Баньяна. Здесь для ярлыка маршрутизации поток битов, полученный в функции выборки и суммирования, не используют без изменения, а его последовательность битов должны быть изменена для входных ячеек, которые должны пройти без внутреннего блокирования в обращенной схеме Баньяна. Если результатом выборки и суммирования является (b1, b2 и b3), то последовательность ярлыка маршрутизации, использованная в обращенной схеме Баньяна, становится (b1, b2 и b3). Процедура запоминания ячеек во входном буфере посредством входной схемы в соответствии с ярлыком маршрутизации, полученным указанным выше методом, изображена в фиг.8С.

Фиг. 8С изображает процедуру передачи ячеек в соответствии с адресами входного буфера, задействованными выполнением функции выборки и суммирования, когда выполняют входную схему 8•8. Фиг.9В изображает процедуру передачи ячеек во входной схеме 12 объемом 1024•1024.

Далее следует объяснение конфигурации и действия входного буфера 20 (очередь входа). Входной буфер 20 запоминает ячейки, переданные по входной схеме 12, имеющей конфигурацию, изображенную в фиг.10А. Фиг.10А изображает конфигурацию входного буфера 20 в случае коммутационного устройства 8•8. Фиг. 10В изображает принципиальную структуру входного буфера 20, изображенного в фиг.10А.

В фиг. 10В нижний указатель указывает начальное положение адресов входного буфера 20, где запомнены вновь введенные ячейки. Верхний указатель указывает начальное положение адресов, в которых считывают ячейки, запомненные во входном буфере 20. Верхним и нижним указателями управляют в соответствии с состоянием ввода/вывода ячеек. Фиг.10А изображает адресную последовательность памяти обратного магазинного типа, образующую входной буфер 20. Как изображено в фиг.10А, все порты ввода совместно используют все ЗУ обратного магазинного типа, в то время как каждый из портов не использует заданное ЗУ обратного магазинного типа. Для совместного использования буферов входная схема 12 выполняет функцию выборки и суммирования в качестве предэтапного действия. Ячейки, введенные в коммутационную схему АРП, запоминают во входном буфере 20 и считывают последовательно в целях передачи в схему копирования 32 для каждого цикла ячеек.

Далее излагается объяснение конфигурации и действия схемы копирования 32. Схема копирования 32 выполняет функцию выборки и суммирования и функцию копирования для копирования ячеек. Максимальное число ячеек, скопированных схемой копирования 32 в течение одного цикла ячеек, определяют согласно емкости схемы копирования 32. Если число скопированных ячеек превышает емкость схемы копирования, то превышающие ячейки копируют в следующем цикле ячеек. Здесь можно осуществить разделение ячеек, при этом разделении копируют часть подлежащих копированию ячеек. В этом случае остальные ячейки разделения предполагается скопировать в следующем цикле ячеек. Функция выборки и копирования схемы копирования 32 выполняют той же аппаратурой, что и аппаратура входной схемы 12. Для этой функции копирования ячеек используют схему Баньяна. Далее следует подробное описание схемы копирования 32, которая выполняет упомянутую выше функцию.

Далее излагается объяснение функции выборки и суммирования схемы копирования 32. Функция обеспечения числа копирования ячеек всем ячейкам, введенным в соответствующие порты ввода, выполняется функцией выборки и суммирования схемы копирования 32. Заголовку ячейки, необходимой для выполнения функции выборки и суммирования, нужен бит, указвывающий число копирования ячеек, и биты, в которых должка быть записана информация для копирования. Информацией, полученной от функции выборки и суммирования, управляют для выполнения функции самого копирования с помощью алгоритма копирования. Это копирование выполняют (в виде минимума, максимума) с помощью числа копирования соответствующих ячеек и числа копирования обеих ячеек.

Фиг. 11А и 11В изображают обращенную схему Баньяна 8•8 для объяснения процедуры выборки и суммирования в схеме копирования 32. В фиг.11А и 11В предполагается, что ячейки вводят в восемь портов, когда указатель индекса копирования является "0", а число копирования ячеек, необходимое для соответствующих портов - 3, 2, 2, 3, 1, 2, 3, 2. Здесь число копирования ячейки включает само себя (ячейку источника копирования). Указатель индекса копирования указывает число ячеек, отправленных обратно в цикле ячеек предшествующего этапа, и обновляется для каждого цикла схемой обратной связи 52. Это число является числом, зарезервированным для того, чтобы ячейки, отправленные обратно в цикле ячеек предыдущего этапа, прошли по схемам маршрутизации 63а-63d в первую очередь. Максимальное число скопированных ячеек является числом, в котором зарезервированное число ячеек вычитают из общего числа портов.

Функция выборки и суммирования схемы копирования 32 является следующей.

Фиг.11А изображает первый этап функции выборки и суммирования, в которой число скопированных ячеек суммируют из порта ввода в порт вывода схемы копирования 32. Операцию суммирования числа скопированных ячеек выполняют следующий образом.

Если имеется ввод ячеек в порт более высокого уровня на первом этапе элемента 2•2 схемы копирования, то копирующее число нужных ячеек записывают в регистр элемента независимо от того, принимает или не принимает ячейку порт ввода более высокого уровня. Числа скопированных ячеек, введенных в порты более высокого уровня и более низкого уровня элемента первого этапа, суммируют и направляют к порту вывода более низкого уровня. Это значение вводят в элемент, подключенный ко второму этапу. Также па втором этапе тот же процесс, что и на первом этапе, выполняют в отношении значения (указывающего число ячеек), введенного в элемент. Третий этап выполняет тот же процесс, что и упомянутый. После указанной процедуры числа копирования ячеек, нужные для всех введенных ячеек, суммируют и выводят к низшему порту на окончательном этапе. Это значение не используется в качестве указателя функции выборки и суммирования в течение следующего цикла ячеек в схеме копирования 32 - в противоположность входной схеме 12. Указатель индекса копирования обновляется значением, принятым в схеме обратной связи для каждого цикле ячеек.

Фиг.11В изображает второй этап функции выборки и суммирования, на котором индекс копирования передают из порта вывода в порт ввода схемы копирования 32. Действие передачи индекса копирования выполняют изложенным ниже образом.

В низшем элементе третьего этапа значение (например, "0"), запомненное в указателе индекса копирования, суммируют со значением, записанным в регистре элемента на первом этапе процесса выборки и суммирования, и отправляют к элементу второго этапа по порту ввода более низкого уровня. Указатель "0" передают к элементу второго этапа по порту ввода без изменения.

Элемент второго этапа передает значение, введенное с третьего этапа, к элементу первого этапа по порту ввода. Через порт ввода более низкого уровня переданное значение суммируют со значением, записанным в регистре элемента во время первого этапа процесса выборки и суммирования, и направляют к элементу первого этапа.

Элемент первого этапа передает значение, принятое от второго этапа, к порту ввода более высокого уровня, суммирует это значение со значением, записанным в регистр элемента на первом этапе, и отправляет результат к порту ввода более низкого уровня.

После выполнения изложенной выше процедуры все ячейки принимают число портов вывода схемы копирования, из которой выводят окончательно скопированную ячейку для соответствующих ячеек на основе числа копирования ячеек, нужного для них самих. В фиг. 11В ячейки принимают 0, 3, 5, 7, 10, 11, 13, 16, начиная с ячейки высшего порта.

В одном цикле ячеек максимальное число копирования ячеек то же, что и число портов схемы копирования. Поэтому в примере фиг. 11В можно скопировать только максимум восемь ячеек. Соответственно в отношении ячеек, введенных в первый, второй и третий порты, можно скопировать и передать столько ячеек, сколько нужно. Но в отношении ячеек, введенных в четвертый порт, можно передать только его собственные, а остальные копируют и передают в следующем цикле ячеек. Этот случай называется "разделением", в котором копирование ячеек, нужное одной ячейке, выполняют в нескольких циклах ячеек. В фиг. 11В: (3) является разделением ячеек и вводом в высший порт схемы копирования 32 в следующем цикле ячеек. Разделенные ячейки запоминают в буфере разделения и выводят в высший порт схемы копирования 32 в следующем цикле ячеек. Это делается для того, чтобы разделенные ячейки затем последовательно не разделялись. В фиг. 11В ячейку, отмеченную пунктирной линией в ее числе копирования, вводят в следующий цикл копирования ячеек, поскольку она превышает максимальное число копирования схемы копирования 32. Значение, в котором число отправленных обратно ячеек вычтено из максимального числа копирования ячеек, содержащего ячейки, отправленные обратно в предыдущем цикле ячеек, является фактической наибольшей копируемой емкостью в цикле ячеек.

Как объяснялось выше, фиг. 11А и 11В изображают пример схемы копирования объемом 32 8•8. В соответствии с этими чертежами функция выборки и суммирования схемы копирования 32 выполняет первый этап суммирования числа ячеек, скопированных из порта ввода в порт вывода, и второй этап передачи индекса копирования суммированных ячеек из порта вывода в порт ввода. Фиг. 12 изображает первый и второй этапы функции выборки и суммирования в схеме копирования 32 объемом 1024•1024. В фиг. 12 сплошная линия указывает процедуру суммирования числа скопированных ячеек, то есть прямой цикл операции выборки и суммирования. Пунктирная линия изображает процедуру передачи индекса копирования, то есть обратный цикл в операции выборки и суммирования.

После функции выборки и суммирования в схеме копирования 32 выполняют копирование ячеек. Фиг.13А изображает копирование ячеек на данном (n) этапе схемы копирования 32 объемом 8•8. Фиг.13В изображает копирование следующего (n+1)-го этапа в схеме копирования 32 объемом 8•8.

Копирование ячеек должно копировать ячейки, введенные из схемы копирования 32 после функции выборки и суммирования. Значение для выполнения копирования ячеек в схеме копирования 32 вычисляют на основе индекса копирования, полученного выполнением функции выборки и суммирования. Это значения вычисляют для каждой ячейки, введенной в схему копирования 32, и записывают в заголовок ячеек. Затем информацию копирования ячеек, использованную для алгоритма копирования ячеек, указывают как (минимальное, максимальное) значение и передают посредством заголовка ячейки. Здесь индекс копирования, полученный от функции выборки и суммирования, становится минимумом, а значение, в котором число копирования суммируют с индексом копирования, становится максимумом. Информация копирования (минимум, максимум) состоит из log2 N битов соответственно, в случае, когда схема копирования 32 выполнена N•N. В том случае, когда схема копирования 32 выполнена 1024•1024, для информации копирования нужно 10 битов. Изображено копирование ячеек, выполненное в схеме Баньяна объемом 8•8. В фиг.13А информация копирования ячеек представлена как ((min. 1, min.2, min.3), (max.1, max.2, max.3)), для удобства объяснения копирования ячеек.

Согласно фиг. 1ЗА на первом этапе схемы копирования 32 сравнивают первые биты min.1 и max.1 информации копирования ячеек (min.1, min.2, min.3), (max. 1, max. 2, max.3). Если они разные, то ячейки копируют и направляют к обоим портам вывода. Ячейки вывода подвергаются тому же процессу на втором этапе, а информацией копирования ячеек, использованной на втором этапе, управляют следующим образом.

- Информация копирования ячеек для ячеек, выведенных к каналу более высокого уровня: (min.2, min.З), (1,1),

- Информация копирования ячеек для ячеек, выведенных к каналу более низкого уровня: (0,0), (max.2, max.З)

Если min. 1 и max. 1 идентичны, то входные ячейки не копируют, и этот случай разделяют на два вида по значению 0 или 1. Здесь информацию копирования ячеек корректируют в информацию копирования (min.2, min.3), (max.2, max.3) - в обоих случаях первые биты аннулируют.

В случае 0 - ячейки передают к каналу вывода более высокого уровня.

- в случае 1 - ячейки передают к каналу вывода более низкого уровня.

На втором этапе ячейки, введенные с первого этапа, подвергают тому же процессу, что и на первом этапе, а информацию копирования ячеек, использованную на третьем этапе, корректируют в порядке, изложенном ниже.

- В случае выполнения копирования ячеек - информация копирования ячеек, переданных к каналу более высокого уровня: (min.3,1)

2 в случае выполнения копирования ячеек - информация копирования ячеек, переданных к каналу более низкого уровня: (0, max. 3)

- Если копирование ячеек не производится - информация копирования ячеек: (min.3, max.3).

На окончательном этапе выполняют тот же процесс, что упомянутый выше, и необходимое число скопированных ячеек выводят последовательно с высшего канала на окончательном выходном этапе схемы копирования.

Фиг. 13В изображает процедуру копирования остальных ячеек, разделенных в предыдущем цикле ячеек, в высшем порте схемы копирования 32 в следующем цикле ячеек. Разделенные ячейки, полученные в данном цикле ячеек, и число копирования запоминают в буфере разделенных ячеек и затем вводят в высший порт схемы копирования 32 в следующем цикле для их копирования. В фиг. 13В: (1) является ячейкой, разделенной в предыдущем (n) цикле ячеек и введенной в высший порт в цикле n+1. Ячейки, разделенные в цикле ячеек n+1, такие как (2), снова запоминают в буфере разделенных ячеек.

Копирование ячеек схемы копирования 32 выполняют таким образом, что информацию копирования ячеек получают из индекса копирования, полученного выполнением функции выборки и суммирования, и затем копируют ячейки, введенные из информации копирования ячейки. Фиг.14 изображает действие копирования ячеек в схеме копирования 32, когда формируют схему копирования 32 объемом 1024•1024.

Схему обратной связи 32 выполняют той же аппаратурой, что и входную схему 12. Фиг. 15 изображает схему обратной связи 52 объемом 1024•1024. Схема обратной связи 52 запоминает входные ячейки в буфере обратной связи размером в одну ячейку для каждого порта, находящегося на переднем этапе, для одного цикла ячеек, и выводит ячейки последовательно из порта вывода более высокого уровня схемы обратной связи 52 без участка памяти, как изображено в фиг. 15. Это делается для повышения приоритета передачи, когда ячейки, проходящие схему обратной связи 52, вводят в схемы маршрутизации 63a-63d в следующем цикле ячеек. Этот процесс тот же, что и функция выборки и суммирования и передача ячеек во входной схеме 12. В схеме обратной связи 52 указатель буфера в функции выборки и суммирования начинается всегда с 0 для каждого цикла ячеек. Здесь ячейки, подлежащие обратному отправлению, выбирают контроллером обратной связи контроллера маршрутизации/обратной связи 41 для каждого цикла ячеек. Информацию об обратной связи вычисляют для каждого цикла ячеек в соответствии с функцией управления обратной связью. Когда в контроллере 41 маршрутизации/обратной связи выполняют управление обратной связью, в схемы маршрутизации 63а-63d вводят только ячейки, которые не вызовут потерю по причине конфликта порта вывода. Схема обратной связи 52 обеспечивает указатель, используемый в функции выборки и суммирования схемы копирования 32 для каждого цикла ячеек.

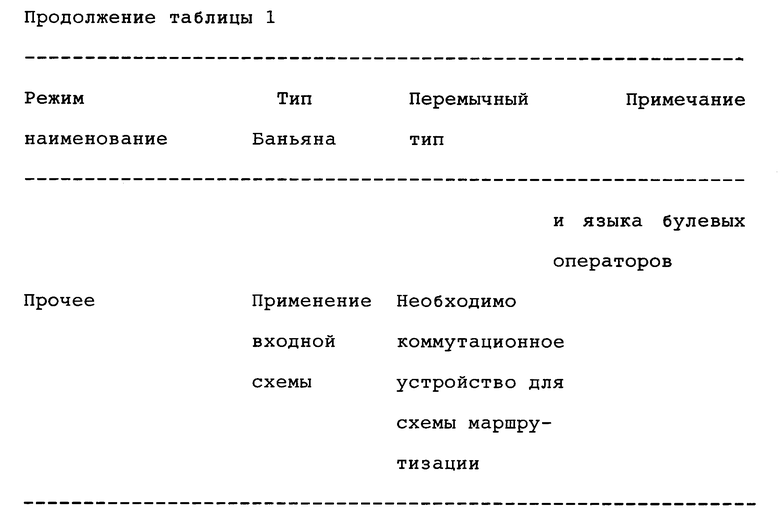

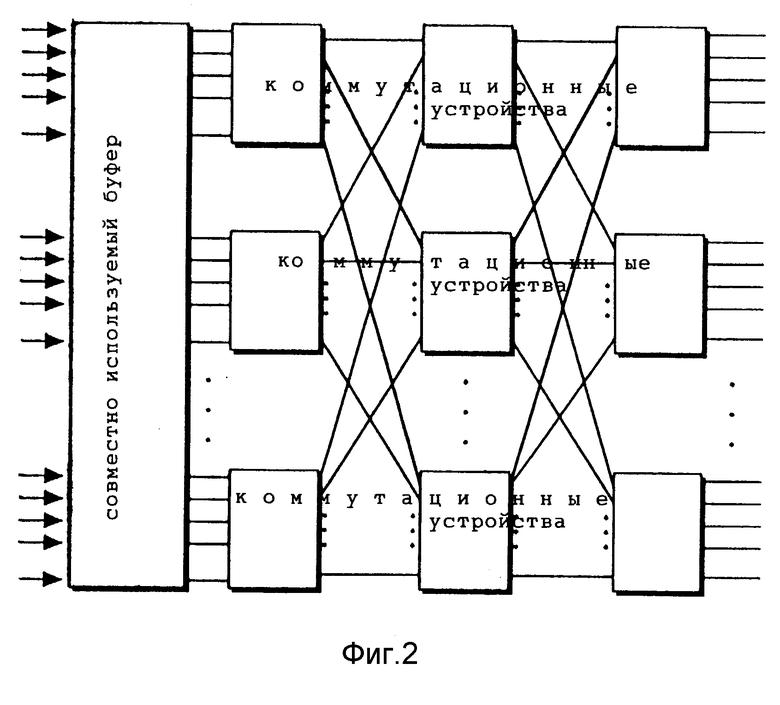

Схему маршрутизации 63 выполняют во множестве, чтобы предотвратить конфликт порта вывода. В данном изобретении предполагается, что сеть 1024•1024, имеющая перемычные схемы 32•32 на двух этапах, выполнена с четырьмя параллельно- соединенными схемами маршрутизации 63-63d. Если перемычная схема используется для схемы маршрутизации 63, она очень эффективна в коммутации несмотря на то, что объем аппаратуры, используемой для коммутационного устройства, становится больше, чем для схемы Баньяна. Поэтому перемычную схему используют для схемы маршрутизации 63. Фиг.17А изображает пример схемы маршрутизации 63, составленной схемами Баньяна. Фиг.17В изображает пример схемы маршрутизации 63, составленной перемычными схемами. Приводимая ниже таблица 1 отображает различие между случаями, в которых схема маршрутизации выполнена схемой Баньяна или перемычной схемой. Если схему 1024•1024 формируют коммутационными устройствами объемом 32•32, как показано в фиг. 17А и 17В, то коммутационные устройства в принципе имеют одинаковую структуру в обоих случаях,кроме внутренней структуры и рабочих показателей.

В данном изобретении предполагается, что схема маршрутизации 63 объемом 1024•1024 выполнена в соответствии с изображением в фиг.16 и что четыре схемы маршрутизации используют для улучшения рабочих характеристик коммутационной схемы АРП. В соответствии с результатами моделирования с помощью схем маршрутизации 63а-63d, как изображено на фиг. 16, установлено, что эффективность обработки ячеек составляет 95% и приближается к 100% в том случае, когда регулировку внутреннего блокирования и конфликта порта вывода схем маршрутизации 63 выполняют наряду с управлением входного буфера 20 и выходного буфера (не показан).

Если множество схем маршрутизации 63 выполнены параллельно, то разделение ячеек и объединение ячеек надо выполнять вместе, так же как и маршрутизацию. Для этого разделитель ячеек 62 и объединитель ячеек 64 используют вместе. Разделитель ячеек 62 используют для распределения ячеек по схемам маршрутизации 63а-63d, а объединитель ячеек 64 объединяет ячейки, достигшие соответствующего порта вывода из схем маршрутизации 63a-63d.

Ниже объясняется маршрутизация с соответствующей общей структурой. Фиг. 18 изображает конфигурацию разделителя ячеек 62 и объединителя ячеек 64 с схемами маршрутизации 63а-63d. Ячейки, которые подвергают регулировке внутреннего блокирования и конфликта порта вывода контроллером маршрутизации в контроллере маршрутизации/обратной связи 41, разделяют разделителем ячеек 62 и передают к схемам маршрутизации 63a-63d. Здесь ячейки распределяют по четырем схемам маршрутизации последовательно согласно регулировке внутреннего блокирования и конфликта порта вывода схем маршрутизации 63a-63d. Входные ячейки самомаршрутизируются к портам вывода схем маршрутизации 63a-63d, а множественные ячейки, переданные к этому же порту вывода схем маршрутизации 63a-63d, запоминают в выходном буфере объединителя ячеек 64 и затем выводят последовательно.

Разделитель ячеек 62 распределяет ячейки, введенные в соответствующие порты, в сети маршрутизации, как изображено на фиг. 18, в результате чего их передают без внутреннего блокирования и конфликта порта вывода. Информацию разделения ячеек получают от предотвращения конфликта порта вывода и предотвращения внутреннего блокирования схемы маршрутизации.

Объединитель ячеек 64 запоминает множественные ячейки, выведенные в тот же порт схем маршрутизации 63а-63d, в выходном буфере объединителя ячеек 64, как изображено на 18, и затем передает их последовательно. Ячейки, выведенные из схем маршрутизации 63а-63d, запоминают в выходном буфере селектором для последовательного выбора активных ячеек после их последовательного/параллельного преобразования. Здесь термин "активные ячейки" означает, что они действительно переданы к порту вывода. Последовательно/параллельное преобразование выполняют для понижения скорости запуска аппаратуры. Ячейки, выведенные из схем маршрутизации 63а-63d, являются последовательными данными 160 Мб/сек и их скорость должна быть увеличена, когда их выводят одновременно. Но в данное время при имеющейся сейчас аппаратуре выполнить это трудно.

Управление маршрутизацией в контроллере 41 маршрутизации/обратной связи далее описано со ссылкой на таблицу маршрутизации. Управление маршрутизацией включает в себя придание ярлыка маршрутизации и преобразование заголовка ячеек. Ярлык маршрутизации используют для передачи всех ячеек в их соответствующие порты вывода по схемам маршрутизации 63а-63d. Здесь ярлык маршрутизации получают от относящейся к маршрутизации информации, такой как таблица маршрутизации 42, с помощью идентикатора предполагаемого маршрута (ИПМ) (VPI)/идентификатора предполагаемого канала (ИПК) [VCI] и идентификатора порта ввода. Информация ярлыка маршрутизации, запомненная в таблице маршрутизации 42, обновляется процессором управления вызова/соединения (фиг.5) всякий раз, когда запрошен вызов, и должна выполнять управление маршрутизацией 1024/n ячеек в одном цикле ячеек одновременно. Преобразование заголовка ячеек преобразует ячейки, маршрутизированные и переданные другому узлу по коммутационной схеме АРП, в информацию, используемую в маршрутизации в другом узле. Эта информация содержит ИПМ/ИПК заголовка ячеек, идентификатор типа полезной нагрузки (ИТПН) и приоритет потери ячеек (ППЯ).

Далее следует описание таблицы маршрутизации 42 и формата ячеек. Таблицу маршрутизации 42 используют для запоминания информации маршрутизации ячеек, которую запоминают в таблице 42 процессором управления вызовом/соединением фиг. 5 всякий раз, когда установлен вызов/соединение и его состояние сохраняется до отбоя. Таблица маршрутизации 42 имеет структуру, которая изображена в фиг. 19. Как изображено в фиг. 19, таблица маршрутизации 42 состоит из ярлыка маршрутизации и информации преобразования заголовка ячеек для соответствующих ячеек. Ярлык маршрутизации ячеек находят обращением к идентификатору соединения единого вещания (ИПМ/ИПК), идентификатору соединения множественного вещания и числу порядка копирования. Конкретную структуру и содержание таблицы маршрутизации 42 нужно более подробно рассматривать вместе со структурой и функцией заголовка ячейки, используемого в коммутационной схеме АРП, и конкретным режимом маршрутизации.

Структура заголовка ячеек, используемого в коммутационной схемке АРП, выполнена согласно изображениям в фиг.20А и 20В. Здесь фиг.20А изображает заголовок ячейки в АРП-сопряжении "пользователь-схема" (СПС) [UNI]. Фиг.20В изображает заголовок ячейки в АРП-сопряжении узла схемы (СУС)

Данное изобретение предполагает, что структура заголовка ячейки коммутационной схемы АРП используется согласно фиг.21. В структуре заголовка ячейки, изображенного в фиг. 21, "А" является участком для запоминания одного бита, указывающего активность или неактивность ячейки. S/M/B (одинарное вещание/множественное вещание/вещательная передача), состоящее из двух битов, является участком для запоминания битов, указывающих службы одинарного вещания/множественного вещания/вещательной передачи. "Copy info." из 20 битов является участком для запоминания информации копирования ячеек, указывающей минимум и максимум, нужные для копирования ячеек, MCN (число копий множественного вещания) из 10 битов является участком для запоминания информации, указывающей число скопированных ячеек. IPI/SPT (идентификатор порта ввода/ярлык самомаршрутизации) из 10 битов является участком для запоминания информации для идентифицирования порта ввода коммутационной схемы, в которую вводят ячейки, и для обеспечения ярлыка маршрутизации после управления маршрутизацией, ИПМ (VCI) из восьми битов является участком для запоминания информации идентификации предполагаемого маршрута. ИПК (VCI) из 16 битов является участком для запоминания информации идентификации предполагаемого канала. PTI (ИТПН) из трех битов является участком для запоминания информации идентификации типа полезной нагрузки. CLP (ППЯ) из одного бита является участком для запоминания информации приоритета потери ячеек. НЕС (коррекция ошибок заголовка) [КОЗ] из восьми битов является участком для запоминания информации коррекции ошибок заголовка.

На примере фиг. 21 объясняются различные виды информации, приданной заголовку ячейки, используемому во внутренней коммутационной схеме, и их функции.

Бит "А" указывает, активна или неактивна ячейка. /S/M/B указывает, к какому обслуживанию относится ячейка: одинарному вещанию, множественному или вещательной программе. Поле Copy info. указывает информацию (адрес min, max), которая требуется в копии ячейки. MCN используют, чтобы различать множественные скопированные ячейки. Скопированные ячейки различают, чтобы можно было осуществлять их соответствующее управление маршрутизацией, поскольку их передают в различные пункты назначения. IPI/SPT является полем для идентификации порта ввода коммутационной схемы, в которую вводят ячейки, и для обеспечения ярлыка маршрутизации после управления маршрутизацией. Заголовок ячейки, используемый в коммутации и изображенный в фиг.20А и 20В, и различные стандартные функции преобразования заголовка ячейки выполняют в сопряжении СПС АРП и СУС АРП.

Далее следует описание предотвращения внутреннего блокирования и предотвращения конфликта порта вывода схем маршрутизации 63. Эти функции выполняют контроллером 41 маршрутизации/обратной связи. В основном предпочтительно выполняют две функции, но одну из них можно выборочно использовать в соответствии с требованиями рабочих характеристик схемы коммутации. Конкретно можно выбрать только предотвращение внутреннего блокирования или предотвращение конфликта порта вывода, либо можно использовать обе функции. Но для улучшения рабочих характеристик следует выполнять обе функции. Поскольку рабочие характеристики коммутации снижаются без внутреннего блокирования схемы маршрутизации 63, даже если используют схемы множественной маршрутизации и осуществляют управление конфликтом порта вывода, и это также происходит с конфликтом порта вывода, даже если предотвращают внутреннее блокирование схемы маршрутизации. В данном изобретении эти два вида функций осуществляют вместе. Сначала осуществляют предотвращение внутреннего блокирования схем маршрутизации 63 и затем с помощью результата - предотвращение конфликта порта вывода. Перед предотвращением конфликта порта вывода устраняют внутреннее блокирование схемы маршрутизации.

Контроллер маршрутизации/обратной связи 41 перед одним циклом ячеек вычисляет число ячеек, которые вызывают внутреннее блокирование схемы маршрутизации и конфликт порта вывода. Если полученное значение превосходит число ячеек, которые могут пройти без внутреннего блокирования или конфликта порта вывода в одном цикле ячеек, то число превысивших ячеек отправляют обратно в сеть обратной схемы 52, а не вводят в схемы маршрутизации 63. Ячейки, переданные к схеме обратной связи 52, снова "соревнуются" с ячейками, введенными в схемы маршрутизации 63 в следующем цикле после задержки одного цикла в схеме обратной связи 52. Здесь осуществляют контроль, чтобы в первую очередь были переданы отправленные ранее обратно ячейки - это делается для сохранения порядка передачи ячеек в пределах предполагаемого соединения со службой АРП. Осуществляют контроль приоритета, благодаря которому ячейки, введенные в порты более высокого уровня схем маршрутизации 63, имеют приоритет. Согласно этой функции допущенные к передаче в схемы маршрутизации 63 ячейки передают разделителю ячеек 62 и ячейки рассеивают по схемам маршрутизации 63а-63d. Соответствующие функции подробно объясняются ниже.

Во-первых, излагается описание предотвращения внутреннего блокирования схем маршрутизации 63. Сети маршрутизации 63 не являются неблокирующими схемы, поскольку схемы маршрутизации объемом 1024•1024 формируют на двух этапах перемычными коммутационными устройствами 32•32. Это ухудшает рабочие характеристики коммутации из-за внутреннего блокирования схем маршрутизации 63 и требует функцию предотвращения внутреннего блокирования схем маршрутизации 63.

На фиг.22А две схемы маршрутизации 63, имеющих коммутационные устройства объемом 4•4, формируют параллельно с объемом 16•16. На этом чертеже элемент, расположенный на первом этапе, обозначают как "группа источника" (SG), элемент назначения, расположенный на втором этапе - как "группу назначения" (DG).

Для предотвращения внутреннего блокирования необходима таблица, запоминающая, какой для соответствующих элементов коммутации необходим порт вывода, нужный для ячеек. Эта таблица разделена на участки согласно соответствующим элементам назначения. Разделенные участки в свою очередь разбиты на сегменты, соответствующие числу портов вывода. Фиг.2 2В изображает процедуру осуществления предотвращения внутреннего блокирования, когда схемы маршрутизации 63 сформированы в соответствии с фиг.22А.

Ссылаясь на фиг. 22В, далее излагается объяснение процедуры предотвращения внутреннего блокирования. В коммутационном элементе (SG) первого этапа местонахождение портов вывода, нужных для входных ячеек, разделено на числа группы назначения и порта вывода, которые записаны в таблицу.

В случае, когда ячейки, для которых нужна одна и та же группа назначения (DG) для соответствующих рядов таблицы, превышают две ячейки, разрешение входа (ack) дают только двум, начиная с первой ячейки соответствующих рядов, а остальным разрешения входа не дают. После этой функции в схемы маршрутизации 63 вводят разрешенное число ячеек и распределяют их по схемам маршрутизации 63а-63d разделителем ячеек 62.

Далее следует объяснение функции предотвращения конфликта порта вывода.

Если множество ячеек, которым нужен один и тот же порт вывода схем маршрутизации 63, присутствует в одном и том же цикле ячеек, то эти ячейки конфликтуют в порте вывода, вследствие чего происходит потеря ячеек. Во избежание этого до ввода ячеек в схемы маршрутизации 63 нужно осуществлять предотвращение конфликта порта вывода. Коммутационная схема АРП данного изобретения использует четыре схемы маршрутизации 63а-63d, в результате чего четыре ячейки одновременно поступают в один и тот же порт вывода, если в схемах маршрутизации 63a-63d нет внутреннего блокирования. Фиг.23 изображает концепцию управления конфликтом порта вывода в схемах маршрутизации 63 объемом 1024•1024. Как изображено на фиг. 23, конфликт порта вывода в принципе имеет ту же функцию и структуру, что и предотвращение внутреннего блокирования схем маршрутизации 63.

Фиг. 24А и 24В представляют пример схем маршрутизации 63 объемом 16•16, использующих коммутационные устройства 4•4 для функции вычисления числа ячеек конфликта порта вывода. В том случае, когда схемы маршрутизации 63 используют как на фиг. 24А, две ячейки можно передать одновременно в один и тот же порт. В примере фиг.24А результат предотвращения внутреннего блокирования схем маршрутизации 63, полученный как в фиг.22А и 22В, не используют в вычислении числа ячеек конфликта порта вывода.

В соответствии с фиг.24А и 24В процесс вычисления числа ячеек конфликта порта вывода разделяется на три этапа.

Первый этап осуществляют в элементе SG.

Элементы коммутационного устройства первого этапа записывают в таблицу, при этом нужные для входных ячеек порты вывода указываются элементом назначения и числом порта вывода.

В элементе первого этапа записанное в таблицу назначение порта вывода передают соответствующему элементу назначения.

Второй этап осуществляют в элементе DG.

В элементе назначения четыре значения, принятые от элементов первого этапа, запоминают в их собственной таблице. Число ячеек, которым нужен выход к одному и тому же порту, не должно превышать ограниченное число (в фиг.24А - максимум два), которое контролируется на четырех этапах.

В первом ряду таблицы суммируют число ячеек и разрешение входа указывается до тех пор, пока значение результата суммирования не превысит два. Если запрос вывода в конкретный порт равен по меньшей мере двум и только один из них может быть выведен, его изменяют на 1 и указывают с разрешением ввода (первый этап).

Во втором ряду число разрешения ввода первого ряда суммируют для каждого участка порта вывода (соответствующие колонки таблицы), и разрешение ввода указывается до тех пор, пока значения суммирования не превысит 2 (второй этап).

В третьем ряду два этапа выполняют для первого и второго рядов (третий этап).

В четвертом ряду два этапа выполняют для первого, второго и третьего рядов (четвертый этап).

После четырех этапов результат передают к соответствующему SG. Первый ряд результата вычисления направляют к SG1, второй - к SG2, третий ряд - к SG3, и четвертый ряд - к SG4. Третий этап выполняют в элементе SG.

SG, которая принимает результат от элемента назначения, допускает ячейки в количестве, разрешенном для ввода в схемы маршрутизации 63, из числа ячеек, которым нужен один и тот же порт, а остальные ячейки вводят в сеть обратной связи 52.

Далее следует объяснение разделения ячеек.

При осуществлении предотвращения внутреннего блокирования и конфликта порта вывода ячейки, введенные в схемы маршрутизации 63, контролируют с помощью результата, ячейки, допущенные к схемам маршрутизации 63, рассеивают разделителем ячеек 62, чтобы не обусловить внутреннее блокирование и конфликт порта вывода. В отношении ячеек, введенных в соответствующие порты схем маршрутизации 63, разрешение ввода дается такому числу ячеек, которое равно параллельному числу схем маршрутизации 63 из числа ячеек, в которых происходит внутреннее блокирование и конфликт порта вывода. Только для ячеек, соответствующих числу ячеек, допущенных к вводу, их распределяют последовательно по схемам маршрутизации 63a-63d.

Фиг.25 изображает процедуру запоминания ячеек, выведенных из схем маршрутизации 63 в выходном буфере. Функция выходного буфера далее описывается со ссылкой на фиг. 25.

Выходной буфер используют для приема ячеек, выведенных из одного и того же порта схем маршрутизации 63а-63d одновременно в одном и том же цикле ячеек. Свой буфер предназначается каждому выходному буферу. Поэтому этот буфер по эффективности применения уступает входному буферу 20, совместно используемому всеми портами.

Далее описывается структура коммутационных устройств.

Коммутационная сеть с разделением в пространстве, аналогичная коммутационной схеме АРП согласно данному изобретению, значительно увеличивает количество аппаратуры и при этом объем коммутационной схемы возрастает. При выполнении коммутационной схемы большой емкости ее разделяют на коммутационные устройства, которые изготавливают с небольшой аппаратурной емкостью. Кроме этого, следует учитывать способ выполнения всей коммутационной схемы с помощью их сочетания, и коммутационную схему нужно конструировать с минимальным числом видов коммутационных устройств в целях экономичности и облегчения аппаратного осуществления. В этих целях коммутационные устройства должны обладать модульностью. С модульностью коммутационных устройств становится возможной правильная компоновка всей коммутационной схемы и облегчается ее аппаратное осуществление. Без модульности коммутационных устройств между коммутационными устройствами нет единства и коммутационные устройства с различными структурами должны использоваться во множественности. Это усложняет всю конфигурацию коммутационной схемы. Вид коммутационных устройств и аппаратная усложненность зависят от наличия модульности. Для правильной компоновки коммутационных устройств на этапе межсоединения коммутации необходимо перемещение портов ввода коммутационной схемы АРП.

Ниже следует описание способа осуществления коммутационных устройств.

Коммутационную сеть АРП в соответствии с данным изобретением формируют входной схемой 12, схемой копирования 32, схемой обратной связи 52 и схемой маршрутизации 63. Для входной схемы 12 и схемы обратной связи используют схему Баньяна. Для схемы копирования 32 используют обращенную схему Баньяна. Для схемы маршрутизации 63 используют перемычную схему. Здесь обращенная схема Баньяна выполняется изменением направления ввода и вывода схемы Баньяна. Схема Баньяна имеет три характеристики, указанные ниже. Между портом ввода и портом вывода имеется единый маршрут. Во-вторых, есть маршруты ко всем портам вывода от порта ввода. В-третьих, между портом вывода и портом ввода нет маршрута.

При формировании схемы Баньяна объемом 1024•1024 или обращенной схемы Баньяна согласно данному изобретению объем коммутационного устройства должен быть 32•32, и для сохранения свойств схемы должно быть два этапа. В конфигурации коммутационной схемы АРП объемом 1024•1024, если не используют коммутационное устройство 32•32 (в том случае, когда оно расширено как перемычная схема, использующая схему объемом 16•16 или 64•64), то вся коммутационная схема не может иметь характеристики схемы Баньяна или обращенной схемы Баньяна. Это не дает никаких преимуществ коммутационной схемы АРП, и схемой трудно управлять.

Количество аппаратуры всей коммутационной схемы определяется объемом коммутационных устройств. В данном изобретении объем коммутационного устройства определен в размере 32•32 исходя из существующей полупроводниковой технологии, скорости обработки сигнала печатными платами и числа выводов входов/выходов. Фиг.26 изображает конфигурацию схемы Баньяна объемом 32•32. Схема Баньяна 32•32 имеет 32 порта ввода и порта вывода и формируется на пяти этапах. Каждый этап выполнен из 16 элементов объемом 2•2. Фиг.27 изображает конфигурацию обращенной схемы Баньяна объемом 32•32. Обращенная схема Баньяна объемом 32•32 та же, что и схема Баньяна объемом 32•32 фиг. 26, в которой порты ввода и вывода используют в обращенном порядке.

Перемычная схема 32•32, используемая в качестве коммутационных устройств схемы маршрутизации 63, имеет такую же структуру, как и в фиг. 28, и является неблокирующим коммутационным устройством в противоположность схеме Баньяна и обращенной схеме Баньяна.

Как описано выше, коммутационная схема АРП в соответствии с данным изобретением имеет следующие характеристик. Во-первых, входной буфер совместно используется всеми портами ввода, благодаря чему буфер используется эффективно. Во-вторых, предотвращают переполнение буфера и в свою очередь устраняется потеря ячеек. В-третьих, ячейки не запоминают интенсивно в определенном буфере, тем самым задержка передачи ячеек сведена к минимуму. В-четвертых, создана возможность высокоскоростной коммутации ячеек с хорошими рабочими показателями. В-пятых, входную схему, схему копирования и схему обратной связи можно выполнить в одной и той же структуре. В-шестых, хотя коммутационная схема является одномаршрутной, используют множественные коммутационные схемы в целях многомаршрутной работы, тем самым устраняя трудность маршрутного управления в многомаршрутной коммутационной схеме.

Поэтому нужно иметь в виду, что данное изобретение не ограничено раскрытым здесь конкретным осуществлением в качестве оптимального пути реализации данного изобретения, данное изобретение, напротив, не ограничивается конкретными осуществлениями данного описания, за исключением прилагаемой формулы изобретения,

Изобретение относится к коммутационной системе для выполнения асинхронного режима передачи и способу коммутации ячеек в ней. Технический результат заключается в обеспечении коммутации асинхронного режима передачи при комплексном представлении данных. Система включает в себя входной буфер, входную коммутационную схему, выполняющую функцию выборки и суммирования, коммутационную схему копирования, выполняющую функцию выборки и суммирования, коммутационную схему обратной связи, принимающую отправленные обратно ячейки и сохраняющую их до следующего цикла ячеек, таблицу маршрутизации для запоминания данных для преобразования и замены данных для маршрутизации ячеек, контроллер маршрутизации и обратной связи, маршрутизирующий-управляющий входными ячейками и отправленными обратно ячейками согласно таблице маршрутизации, коммутационные схемы маршрутизации, разделитель ячеек, разделяющий ячейки, маршрутизированные-выведенные в число маршрутизирующих схем, и передающий их к коммутационным схемам маршрутизации, и объединитель ячеек, объединяющий и выводящий ячейки, разделенные и выведенные из портов вывода коммутационных схем маршрутизации. 4 з.п. ф-лы, 28 ил., 1 табл.