Изобретение относится к схемам, которые используют структуру JTAG для сканирования поверхности раздела, в частности к схемам, имеющим выход тракта передачи дискретных данных, управляемый через посредство тестового регистра JTAG.

Описание родственной области техники

Хорошо известный способ тестирования комплексной интегральной схемотехники, например, на печатной плате, описан в стандарте сканирования поверхности раздела 1149.1 IEEE, разработанном JTAG (Международной рабочей группой по испытаниям соединений), включенном в эту заявку ссылкой. Осуществление этого стандарта предусматривает конструирование компонентов (например, интегральных схем) для последовательного тестирования сканированием поверхности раздела путем обеспечения элементов сдвигового регистра в виде цепи для образования пути по периферии компонента интегральной схемы.

Общая концепция тестирования, при использовании JTAG, заключается в смещении последовательных данных в и через ряд компонентов интегральной схемы для возбуждения схемотехники в ней или для формирования предварительно определенных выходных сигналов этой схемотехники. По этой причине, данные, генерируемые компонентами интегральной схемы или принимаемые на входах компонентов интегральной схемы, смещаются из компонентов интегральной схемы в задающую тестовую схему JTAG.

Если поток данных, возвращаемый в задающую тестовую схему, является не таким, которого ожидают, то нарушение нормальной работы в интегральной схеме обнаруживается тестовой схемой. Тщательный компьютерный анализ отклонений в потоке данных может локализовать любое нарушение нормальной работы в интегральной схеме.

В некоторых случаях желательно изолировать один кристалл или один или более соединений тракта (передачи дискретных данных) кристалла на печатной плате от остальной схемотехники на печатной плате. Например, кристалл интегральной схемы может иметь внутреннюю интерфейсную схемотехнику шины памяти, интерфейсную схемотехнику шины периферийного межсоединения компонента, интерфейсную схемотехнику шины микропроцессора и так далее, которые обеспечивают соединения между схемотехникой в кристалле интегральной схемы и различными каналами связи на печатных платах. Тестовая схемотехника JTAG в кристалле интегральной схемы, как правило, содержит сдвиговый регистр JTAG данных сканирования поверхности раздела, включающий в себя ячейку битов данных, соответствующую каждому из соединений ввода-вывода тракта передачи дискретных данных на кристалле интегральной схемы. Кроме того, сдвиговый регистр данных сканирования поверхности раздела содержит одну или более ячеек битов разрешения выхода тракта передачи дискретных данных. Каждая ячейка битов разрешения выхода тракта передачи дискретных данных в цепи сдвигового регистра данных сканирования поверхности раздела разрешает выход для всего или части тракта передачи дискретных данных, соединенного с кристаллом интегральной схемы (например, шины микропроцессора, шины периферийного межсоединения компонента, шины памяти и так далее). Таким образом, например, ячейка битов разрешения выхода тракта передачи дискретных данных будет связана с адресной шиной тракта передачи дискретных данных периферийного межсоединения компонента; другая ячейка ((прим.пер.) в оригинале текста описания на английском языке, вероятно, ошибочно пропущено слово "ячейка") битов разрешения выхода тракта передачи дискретных данных, будет связана с управляющей шиной тракта передачи дискретных данных периферийного межсоединения компонента и так далее. Если соответствующая ячейка битов разрешения выхода устанавливается до соответствующего адекватного значения, то выход всей интерфейсной схемотехники адресной шины тракта передачи дискретных данных периферийного межсоединения компонента (или управляющей интерфейсной схемотехники тракта передачи дискретных данных печатной платы и так далее) разрешен из кристалла интегральной схемы. Аналогичным образом, если ячейка битов разрешения выхода в сдвиговом регистре данных сканирования поверхности раздела устанавливается до неразрешающего значения, то интерфейс адресной шины всего тракта передачи дискретных данных периферийного межсоединения компонента перейдет в режим высокого импеданса, так что сигналы не могут быть переданы из кристалла интегральной схемы через интерфейс адресной шины периферийного межсоединения компонента. Безусловно, квалифицированному в этой области техники специалисту будет очевидно, что множество ячеек битов разрешения выхода сдвигового регистра данных сканирования поверхности раздела может быть использовано для контроля частей интерфейса тракта передачи дискретных данных, так что, например, 16 битов адресной шины периферийного межсоединения компонента может быть под контролем одного разрешения выхода, другие 16 битов - под контролем другого разрешения выхода и так далее. Аналогичным образом, для контроля всего тракта передачи дискретных данных периферийного межсоединения компонента может быть использован один бит разрешения выхода в сдвиговом регистре данных сканирования поверхности раздела.

Если кристалл интегральной схемы должен быть изолирован от одной или более шин, соединенных с кристаллом интегральной схемы, то обычная тестовая схема JTAG предусматривает загрузку бита данных для каждой ячейки битов в регистре JTAG данных сканирования поверхности раздела через весь кристалл интегральной схемы. Таким образом, если, например, с кристаллом интегральной схемы соединяется четыре отдельные 64-битовых шины и каждая шина имеет одну соответствующую ячейку битов разрешения выхода в сдвиговом регистре данных сканирования поверхности раздела кристалла, то все 260 тестовых битов сдвигового регистра данных сканирования поверхности раздела (4•64+4) будут загружены в сдвиговый регистр данных сканирования поверхности раздела прежде, чем будет установлена каждая ячейка битов разрешения выхода тракта передачи дискретных данных. В самом худшем случае все четыре шины должны быть блокированы так, чтобы остальные 256 ячеек в регистре данных JTAG имели соответствующие значения. Таким образом, обычная система может быть очень неэффективной, поскольку биты данных должны быть смещены в сдвиговом регистре данных сканирования поверхности раздела помимо четырех ячеек битов разрешения выхода сдвигового регистра данных сканирования поверхности раздела. Эта ситуация усложняется тем, что сдвиговый регистр данных сканирования поверхности раздела может быть соединен последовательно с другими сдвиговыми регистрами данных сканирования поверхности раздела кристалла на печатной плате или печатных платах.

Альтернативный способ изолирования интегральной схемы от других схем на печатной плате предусматривает переведение всего кристалла в режим высокого импеданса, при использовании команды "HIGHZ", загружаемой в регистр команд JTAG. Хотя такой способ смягчает вышеупомянутую проблему неэффективности блокирования шин, такое решение позволяет блокировать либо все, либо не блокировать ни одной шины.

Однако в некоторых случаях применения требуется, чтобы отдельные шины интегральной схемы были разрешены, тогда как другие блокированы. Например, поскольку многие интегральные схемы имеют КМОП-структуру, важно, чтобы по меньшей мере одна схема на данной шине была разрешена для возбуждения шины, поскольку схемы, имеющие КМОП-структуру, как правило, плывут в режиме высокого импеданса. По этой причине, если все схемы, имеющие КМОП-структуру, на шине переведены в состояние высокого импеданса, то нет схемы, которая возбуждала бы шину до некоторого определенного состояния, и шина будет плавать, так что возможно, что шина будет плавать в каком-либо среднем состоянии между высоким логическим уровнем и низким логическим уровнем. Такое плавающее состояние нежелательно, поскольку вход КМОП-структуры, который принимает плавающий входной сигнал, может иметь оба входных транзистора, которые частично в состоянии соединять силовой провод с землей, что приводит к перегреву и возможно к разрушению КМОП-транзисторов. Следовательно, при блокировании соединения тракта передачи дискретных данных интегральной схемы, соединенной с множеством шин, иногда желательно возбуждать одну или более из остальных шин, соединенных с интегральной схемой, так, чтобы не плавали те шины, которые в настоящее время не подвергаются тестированию. По этой причине для некоторых случаев применения непригодна система JTAG, которая переводит либо все, либо не переводит ни одного из соединений тракта передачи дискретных данных на интегральной схеме в режим высокого импеданса.

Краткое изложение сущности настоящего изобретения Одним аспектом настоящего изобретения является структура тестовой схемы JTAG для избирательного разрешения и блокирования периферийных соединений с интегральной схемой. Структура содержит регистр фиксации данных сканирования поверхности раздела, который содержит множество ячеек битов данных, имеющих электрическую связь с периферийными соединениями и с множеством ячеек битов разрешения выхода. Каждая из ячеек битов разрешения выхода используется для разрешения выхода битов данных, хранимых в множестве ячеек битов данных. Сдвиговый регистр данных сканирования поверхности раздела соединяется с регистром фиксации данных, так что содержимое сдвигового регистра параллельно загружается в регистр фиксации данных. Сдвиговый регистр содержит ячейки битов данных сдвигового регистра, которые соответствуют множеству ячеек битов данных в регистре фиксации данных. Сдвиговый регистр содержит ячейки битов разрешения выхода сдвигового регистра, которые соответствуют ячейкам битов разрешения выхода в регистре фиксации данных. Ячейки битов разрешения выхода сдвигового регистра сгруппированы в тесной логической близости в сдвиговом регистре так, чтобы ячейки битов разрешения выхода сдвигового регистра, были разнесены меньшим числом ячеек сдвигового регистра, чем число ячеек битов данных, разрешенных каждой из ячеек битов разрешения выхода. Переключательная (коммутационная) схема обеспечивает путь через ячейки битов разрешения выхода сдвигового регистра в тесной логической близости, когда коммутационная схема находится в первом состоянии. Переключательная (коммутационная) схема обеспечивает путь через ячейки битов разрешения выхода сдвигового регистра и ячейки битов данных сдвигового регистра, когда переключательная (коммутационная) схема находится во втором состоянии.

Предпочтительно, чтобы ячейки битов разрешения выхода сдвигового регистра были соединены последовательно и в логической близости друг к другу. Предпочтительно также, чтобы переключательная (коммутационная) схема содержала мультиплексор. В особенно предпочтительных вариантах осуществления настоящего изобретения переключательная (коммутационная) схема соединяется с выходом JTAG.

Другим аспектом настоящего изобретения является способ избирательного разрешения и блокирования периферийных соединений с интегральной схемой, используя тестовую схему JTAG сканирования поверхности раздела. Способ предусматривает соединение элементов разрешения выхода и элементов битов тестовых данных в последовательном сдвиговом регистре сканирования поверхности раздела так, чтобы первый путь проходил через элементы разрешения выхода и элементы битов тестовых данных, а второй путь проходил только через элементы разрешения выхода. Информация, хранимая в элементах разрешения выхода избирательно разрешает электрическую связь между элементами битов тестовых данных и периферийными соединениями. Способ дополнительно предусматривает формирования потока битов, используемого для тестирования сканирования поверхности раздела JTAG; выбор между первым и вторым путями; и смещение сформированного потока битов через последовательный сдвиговый регистр данных сканирования поверхности раздела.

Краткое описание чертежей

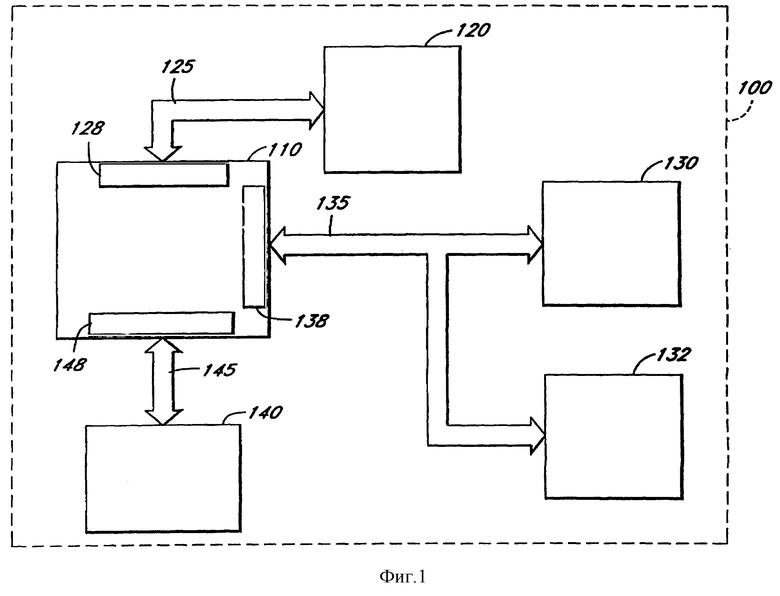

Фиг. 1 - упрощенная принципиальная блок-схема печатной платы, содержащей кристалл интегральной схемы, имеющий интерфейсы с множеством шин на печатной плате.

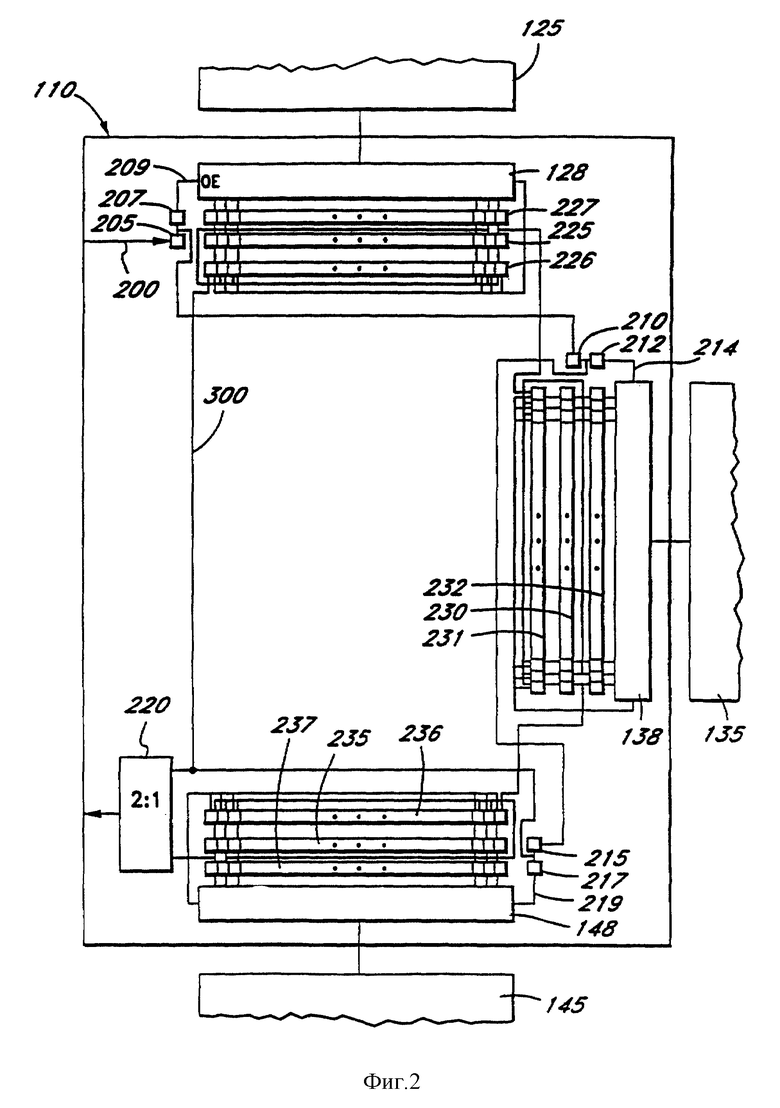

Фиг. 2 - принципиальная блок-схема, на которой более подробно иллюстрируется кристалл интегральной схемы, показанной на фиг.1.

Фиг. 3 - принципиальная блок-схема, на которой подробно показана схемотехника JTAG. когда схемотехника JTAG соединяется с интерфейсом тракта передачи дискретных данных.

Подробное описание предпочтительного варианта осуществления настоящего изобретения

На фиг. 1 представлена сильно упрощенная принципиальная блок-схема, на которой показано множество интегральных схем, соединенных на печатной плате 100. Характерно, что первая интегральная схема 110 соединяется со второй интегральной схемой 120 через посредство шины 125 периферийного межсоединения компонента и интерфейса 128 периферийного межсоединения компонента. Первая интегральная схема 110 дополнительно соединяется с третьей интегральной схемой 130 и четвертой интегральной схемой 132 через посредство шины 135 микропроцессора и интерфейса 138 микропроцессора. Интегральная схема 110 соединена с запоминающим устройством 140 через посредством шины 145 памяти и интерфейсом 148 запоминающего устройства. Например, интегральная схема 120 преимущественно содержит шунт периферийное межсоединение компонента - периферийное межсоединение компонента, интегральные схемы 130, 132 предпочтительно содержат мультипроцессоры, а запоминающее устройство 140 предпочтительно содержит матрицу динамических запоминающих устройств с произвольной выборкой.

В процессе работы, интегральная схема 110 имеет связь с различными схемными элементами 120, 130, 132, 140, смонтированными на печатной плате 100 через посредство шин 125, 135, 145. При необходимости тестирования шины 135 микропроцессора при использовании JTAG и выходных данных из интегральной схемы 130, для защиты схемотехники в интегральной схеме 110 от интерференции с тестированием JTAG необходимо изолировать выходы интегральной схемы 110 от шины 135 микропроцессора. То есть интерфейс 138 микропроцессора интегральной схемы 110 должен быть переведен в режим высокого импеданса так, чтобы его входные триггеры JTAG могли получать выходные тестовые данные JTAG из интегральной схемы 130.

Как кратко описано выше, одним из вариантов было бы перевести всю интегральную схему 110 в режим высокого импеданса так, чтобы в режим высокого импеданса перешли интерфейс 128 периферийного межсоединения компонента, интерфейс 138 микропроцессора и интерфейс 148 запоминающего устройства. Однако такой способ может оказаться непрактичным, если существует необходимость возбуждения интегральной схемой 110 либо шины 125, либо шины 145. То есть, например, если интегральная схема 120 имеет КМОП-структуру, имеющую интерфейс с шиной 125 периферийного межсоединения компонента, которая также находится в режиме высокого импеданса или принимает входной сигнал, то шина 125 периферийного межсоединения компонента будет плавать, поскольку нет схемы, которая бы возбуждала шину 125. В этом случае было бы необходимо перевести в режим высокого импеданса только интерфейс 138 микропроцессора, тогда как интерфейс 128 периферийного межсоединения компонента использовать для возбуждения шины 125 периферийного межсоединения компонента. Как указано выше, обычные способы достижения этого могут потребовать сотни смещений в регистрах данных JTAG для установления только пары битов разрешения выхода в регистрах данных JTAG.

На фиг. 2 представлена упрощенная принципиальная блок-схема, которая в соответствии с настоящим изобретением иллюстрирует некоторые из интегральных компонентов интегральной схемы 110. Цепь и схемотехника сканирования поверхности раздела в интегральной схеме 110 специально предназначены для преодоления недостатков предшествующих схем. Характерно, что в соответствии с настоящим изобретением, тестовая схема JTAG имеет такую компоновку, чтобы каждая из ячеек разрешения выхода в сдвиговом регистре данных сканирования поверхности раздела JTAG была связана друг с другом (например, в смежных ячейках в сдвиговом регистре данных сканирования поверхности раздела JTAG) так, чтобы биты разрешения выхода, используемые для управления режимом импеданса интерфейсов 128, 138, 148, могли быть смещены за минимально требуемое время (то есть без смещения в любую из других ячеек сдвигового регистра данных сканирования поверхности раздела).

Таким образом, как показано на фиг.2, линия 200 ввода данных JTAG (JTAG DIN) непосредственно соединяется с ячейкой 205 разрешения выхода сдвигового регистра данных. Ячейка 205 сдвигового регистра соединяется с триггером 207 для фиксации бита данных, смещенного в ячейке 205, как только соответствующее значение смещено в ячейке 205. Триггер 207 в свою очередь соединяется с линией 209 разрешения тестового выхода JTAG интерфейса 128 периферийного межсоединения компонента. Бит данных, хранимый в триггере 207, передается к интерфейсу 128 периферийного межсоединения компонента по линии 209 для разрешения или блокирования выходов всего интерфейса 128 шины периферийного межсоединения компонента в примере, показанном на фиг.2, если находится в режиме тестирования JTAG. Однако очевидно, что для избирательного контроля частей выхода шины 125 периферийного межсоединения компонента, может быть использовано множество битов разрешения их выхода (это также справедливо для всех других шин). Вторым элементом в сдвиговом регистре данных является ячейка 210 разрешения выхода, которая последовательно соединяется с ячейкой 205 (то есть ячейка 210 является следующей смещаемой ячейкой после ячейки 205). Ячейка 210 разрешения выхода регистра данных также соединяется с триггером 212, который в свою очередь соединяется посредством линии 214 с тестовым выходом JTAG, разрешающим интерфейс 138 микропроцессора. Так же, как и в случае с интерфейсом 128 шины периферийного межсоединения компонента, бит разрешения выхода в триггере 212 используется для разрешения или блокирования выходов для всей шины 135 микропроцессора, если находится в режиме тестирования JTAG. Наконец, ячейка 215 разрешения выхода сдвигового регистра последовательно соединяется с ячейкой 210, так что три ячейки 205, 210 и 215 разрешения выхода сдвигового регистра расположены смежно друг другу. Ячейка 215 разрешения выхода также соединяется с триггером 217, который в свою очередь соединяется по линии 219 с тестовым выходом JTAG, разрешающим интерфейс 148 шины памяти. И в этом случае, бит разрешения выхода, удерживаемый в триггере 217, может быть использован для разрешения или блокирования всего интерфейса 148 шины памяти, если находится в тестовом режиме JTAG.

Выход ячейки 215 сдвигового регистра данных сканирования поверхности раздела соединяется со входом мультиплексора 220 2:1 (2:1 MUX), а также с первым элементом в сдвиговом регистре 224 данных сканирования поверхности раздела, образованном мультиплексором 226 и триггерами 225 задержки. Должно быть очевидным, что используемая в этом устройстве ячейка в сдвиговом регистре 224 данных сканирования поверхности раздела состоит из одного из мультиплексоров 226 вместе с соответствующим триггером 225 задержки. Сдвиговый регистр 224 данных сканирования поверхности раздела является частью регистра данных JTAG сканирования поверхности раздела и предназначен специально для обеспечения тестовых данных для регистра 227 фиксации данных выхода сдвигового регистра данных сканирования поверхности раздела и к линиям на шине 125 периферийного межсоединения компонента через посредство интерфейса 128 периферийного межсоединения компонента. Данные из шины 125 периферийного межсоединения компонента могут быть введены во входной мультиплексор 226 сканирования поверхности раздела, которые могут быть загружены в сдвиговый регистр 225 сканирования поверхности раздела для сбора тестовых входных данных. Соединение между сдвиговым регистром 225 данных и шиной 125 периферийного межсоединения компонента будет более подробно описано ниже со ссылкой на фиг. 3. Соединением выхода ячейки 215 сдвигового регистра с мультиплексором 220 и сегментом 224 сдвигового регистра данных сканирования поверхности раздела обеспечивают два возможных пути для данных JTAG, которые вводят по линии 200 связи. Характерно, что если требуется управление только битами разрешения выхода, связанными с каждым из интерфейсов 128, 138 148, то самый короткий возможный путь для данных JTAG обеспечивается по линии 200, через ячейки 205, 210, 215 сдвигового регистра и мультиплексор 220. Однако, если также требуется обновить или стробировать весь сдвиговый регистр данных сканирования поверхности раздела. то тестовые данные могут быть смещены через часть (200, 128, 138 и 148) разрешения выхода, а затем через остальные секции ввода-вывода сдвигового регистра данных сканирования поверхности раздела (то есть через сдвиговые регистры 225, 230 и 235). Затем они могут быть смещены через второй вход мультиплексора 220. Данные из шины 135 микропроцессора и шины 145 памяти могут быть введены в соответственно входные мультиплексоры 231, 236 сканирования поверхности раздела. Мультиплексоры 231, 236 так же, как мультиплексор 226, могут быть загружены соответственно в сдвиговых регистрах 230, 235 сканирования поверхности раздела для сбора тестовых входных данных. В этом случае обеспечивается эффективное управление разрешениями выхода, связанными с каждым из интерфейсов 128, 138, 148 посредством электрического соединения сегментов сдвигового регистра данных сканирования поверхности раздела для разрешений выхода в тесной логической близости друг к другу через посредство вышеописанных соединений JTAG, так что ячейки сдвигового регистра данных сканирования поверхности раздела, управляющие разрешениями выхода, могут быть логически изолированы от других сегментов сдвигового регистра JTAG данных сканирования поверхности раздела.

Для квалифицированных в этой области техники специалистов безусловно должно быть очевидным, что конфигурация, приведенная на фиг.2, является только примером, так что в соответствии с настоящим изобретением могут быть также использованы другие возможные конфигурации, которые предусматривают группирование ячеек разрешения выхода сдвигового регистра данных сканирования поверхности раздела в тесной близости. Кроме того, для обхода некоторых из регистров 225, 230 и 135 данных на пути прохождения через сдвиговый регистр данных сканирования поверхности раздела может быть установлен ряд переключательных схем. Такие модификации отображены, например, в вышеуказанном документе (IEEE 1149.1). Также очевидно, что аналогично сдвиговому регистру 225 сдвиговые регистры 230, 235 способны параллельно загружать данные в соответствующие регистры 232, 237 фиксации данных. Регистры 227, 232 и 237 фиксации данных могут быть использованы для тестирования схемотехники, которая соединяется с шиной 125 периферийного межсоединения компонента, шиной 135 микропроцессора и шиной 145 памяти соответственно.

На фиг. 3 представлена принципиальная блок-схема, на которой детализировано соединение между сдвиговым регистром 225 данных и шиной 125 периферийного соединения компонента через регистры 227 фиксации данных, мультиплексор 231 и интерфейс 128 периферийного межсоединения компонента. Как показано на фиг.3, входные биты JTAG смещают по линии 300 на вход сдвигового регистра 224 данных сканирования поверхности раздела JTAG и из выхода ячейки в регистре 225 по линии 305 связи. Смещение битов данных через их сдвиговый регистр 230 осуществляют под управлением синхросигнала, обеспечиваемого по линии 315 связи от управляющей логики 310 JTAG. Управляющая логика 310 принимает тестовый сигнал синхронизации и тестовый сигнал режима по линиям 312, 314 соответственно. Управляющая логика 310 обеспечивает синхронизированный выходной сигнал по линии 315, захваченный выходной сигнал 316, обновленный выходной сигнал 320 и обновленный сигнал 317, как хорошо известно в этой области техники. Раздельные обновленные сигналы (320 и 317) позволяют тестовым выходным данным в регистре 227 оставаться неизменными при обновлении разрешений выхода только через посредство укороченного режима сдвигового регистра данных сканирования поверхности раздела.

Как только все соответствующие биты тестовых данных JTAG смещены в сдвиговый регистр 225 данных под управлением сигнала DR-CLOCK, данные захватываются в регистре 227 фиксации данных под управлением обновленного выходного сигнала, передаваемого по линии 320 связи. То есть каждый из битов данных в сдвиговом регистре 225 параллельно загружается в регистр 227 фиксации данных. Для простоты на фиг.3 показаны только две контактные площадки, которые соединяются с выходными контактными площадками через посредство интерфейса 128 периферийного межсоединения компонента.

Каждая тестовая схема JTAG сканирования поверхности раздела содержит мультиплексор, который выбирает между тестовым вектором JTAG и нормальной схемотехникой, которая соединяется с выходными выводами интегральной схемы 110, при не использовании JTAG. Таким образом, как показано на фиг.3, каждая из ячеек битов в регистре фиксации данных соединяется с первыми входами соответственно мультиплексоров 330 через посредство соответствующих линий 333 связи. Выбранный вход 335 в каждый мультиплексор 330 позволяет выбор между обычным тестовым режимом JTAG и нормальным рабочим режимом через посредство декодированного выхода регистра 310 команд JTAG. Выходной сигнал каждого мультиплексора 330 входит в интерфейс 128 (периферийного межсоединения компонента), который содержит множество двунаправленных тристабильных буферов 340, 345. Как показано на фиг.3, выходные буферы 340 обеспечивают выходные пути к соответствующим внешним контактным площадкам 350, тогда как входные буферы 345 обеспечивают входные пути от контактных площадок 350 к схемотехнике внутри кристалла интегральной схемы 110.

Как показано на фиг. 3, линия 209 связи соединяется со всеми тристабильными буферами 340, так что, если сигнал разрешения выхода, передаваемый по линии 209 связи, является активным, то каждый из буферов 340 входит в режим высокого импеданса. В этом случае шины, соединенные с интегральной схемой 110, могут быть эффективно и избирательно переведены в режим высокого импеданса.

Хотя это и не существенно для настоящего изобретения, но необходимо отметить, что контактные площадки 350 дополнительно соединены с соответствующими элементами мультиплексора 226 через посредство входных буферов 345, так что данные на входных контактных площадках могут быть стробированы и зафиксированы в сдвиговом регистре 225.

Хотя настоящее изобретение было подробно описано выше, должно быть очевидным, что приведенное подробное описание является иллюстративным, а не ограничивающим. Квалифицированным в этой области техники специалистам должны быть очевидны модификации настоящего изобретения, которые могут быть сделаны без отклонения от его сущности или основных характеристик. В соответствии с этим, объем настоящего изобретения ограничивается приводимой ниже прилагаемой формулой изобретения.

Изобретение относится к схемам, которые используют структуру JTAG для сканирования поверхности раздела, в частности, к схемам, имеющим выход тракта передачи дискретных данных, управляемый посредством тестового регистра JTAG. Техническим результатом является повышение эффективности тестирования. Тестовая схема JTAG позволяет избирательно переводить множества соединений тракта передачи дискретных данных в интегральной схеме в состояние высокого импеданса. Тестовая схема содержит регистр фиксации данных сканирования поверхности раздела, соединенный с ним сдвиговый регистр данных сканирования поверхности раздела, причем ячейки разрешения выхода сдвигового регистра сгруппированы в тесной логической близости, и коммутационную схему, соединенную с указанным сдвиговым регистром. Способ описывает работу указанной тестовой схемы. 2 с. и 3 з.п. ф-лы, 3 ил.

| US 5084874 А, 28.01.1992 | |||

| СПОСОБ КОНТРОЛЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1990 |

|

RU2018148C1 |

| ТЕСТОВАЯ ИНТЕГРАЛЬНАЯ СТРУКТУРА | 1990 |

|

RU2034306C1 |

| US 515388 2А, 06.10.1992 | |||

| US 5210759 А, 11.05.1993. | |||

Авторы

Даты

2002-10-20—Публикация

1996-09-26—Подача