Изобретение относится к усовершенствованию тестирования интегральных схем. В частности, настоящее изобретение относится к способу и устройству для тестирования мегаэлемента в интегральной схеме частного применения на уровне кристалла.

Увеличивающаяся степень интеграции схем и новые технологии упаковки интегральных схем еще более увеличивают проблему тестирования интегральных схем и печатных плат. Программное обеспечение тестирования цифровой аппаратуры постоянно улучшается, однако степень интеграции схем делает тестирование более затруднительным, если эти компоненты не сформированы с предусмотренной тестируемостью.

Одним способом тестирования схемотехники, который привлек значительное внимание, является стандарт сканирования поверхности раздела 1149.1 IEEE, разработанный Международной рабочей группой по испытаниям соединений (JTAG), включенный в эту заявку ссылкой. Одно исполнение этого стандарта предусматривает конструирование компонентов (например, интегральных схем) для последовательного тестирования сканированием поверхности раздела посредством обеспечения элементов сдвигового регистра в виде цепи для образования дорожки по периферии компонента интегральной схемы. Концепция последовательного тестирования заключается в смещении последовательных данных в компоненты интегральной схемы и через них. Последовательные данные подают на входы известной схемотехники для обеспечения выходов, как определено функциями схемы. Задающая схема тестирования сравнивает данные возврата с ожидаемым результатом (то есть с результатом, который является зависимым от функций известной схемотехники). Другими словами, вводы последовательных данных в тестируемую схему обеспечивают известные выходы, если схема функционирует должным образом. Если поток данных, возвращаемых в задающую схему тестирования, не соответствует ожидаемому, то неисправность в схеме выявляется посредством схемы тестирования. Тщательный компьютерный анализ отклонений в потоке данных может локализовать любую неисправность схемы.

Тестирование компонентов сканированием поверхности раздела, как кратко описано выше, может быть также распространено на тестирование сверхбольших интегральных схем, например интегральных схем частного применения. Интегральная схема частного применения содержит логическую схемотехнику, которая обычно недосягаема через штырьковые выводы, обеспечиваемые на корпусе интегральной схемы. Такая внутренняя логическая схемотехника в интегральной схеме частного применения, как правило, является покупной и поступает от фирмы поставщика в виде модуля, имеющего определенные входы и выходы - стандартного функционального блока, и обычно называемого "мегаэлементом". В некоторых печатных платах тестовые входы и выходы покупного мегаэлемента в интегральной схеме частного применения соединяют с отдельными штырьковыми выводами на корпусе интегральной схемы. Однако дополнительные штырьковые выводы, требуемые для тестирования этого элемента, как правило, не используют в процессе производства и нормальной работы интегральной схемы. Кроме того, дополнительные тестовые штырьковые выводы иногда вынуждают изготовителя перейти на следующий больший размер кристалла и/или корпуса, вследствие увеличенного числа штырьковых выводов. Таким образом, корпус интегральной схемы занимает дополнительное место на печатной плате и стоимость интегральной схемы увеличивается, поскольку кристалл большего размера, как правило, стоит дороже.

Кроме того, стандартная спецификация JTAG позволяет окружить мегаэлемент внутри интегральной схемы частного применения элементами JTAG. Однако применение такой тестовой архитектуры не совместимо со способом, с помощью которого поставщик обычно тестирует мегаэлементы. Это объясняется тем, что поставщики мегаэлементов проводят стандартные испытания своих мегаэлементов. Хотя тестовые векторы и способы тестирования, предусматриваемые поставщиком для тестирования мегаэлемента, технологически являются достаточно гибкими, чтобы изменить порядок штырьковых выводов при тестировании своих мегаэлементов, для поставщика слишком дорого изменить функциональность стандартного теста. Например, стандартный тест поставщика может быть последовательно загружен через порт JTAG и подведен параллельно мегаэлементу, но это будет слишком дорого, поскольку в два раза увеличит длину цепи JTAG.

Для реализации изобретения предложено использовать устройство тестирования стандартного функционального блока в интегральной схеме с использованием JTAG, содержащее заказную цифровую логическую схему, причем указанная заказная цифровая логическая схема выполнена с возможностью принимать входные сигналы и генерировать выходные сигналы, функциональный блок смонтирован в указанной интегральной схеме с возможностью функционирования при взаимодействии с указанной заказной цифровой логической схемой, причем указанный функциональный блок имеет тестовые входы для приема тестовых входных сигналов и тестовые выходы для передачи тестовых выходных сигналов, предназначенные для тестирования работы указанного функционального блока, регистр данных сканирования поверхности раздела JTAG, выполненный с возможностью хранения тестового вектора, используемого при тестировании целостности входов и выходов указанного корпуса интегральной схемы, причем указанный регистр генерирует выходные сигналы, первую схему выборки, имеющую по меньшей мере один выход первой схемы выборки, который генерирует выходной сигнал первой схемы выборки, и имеющую входы первой системы выборки, причем по меньшей мере один из указанных входов первой схемы выборки соединен для приема по меньшей мере одного из указанных выходных сигналов от указанного регистра данных сканирования поверхности раздела, а другой из указанных входов первой системы выборки выполнен с возможностью приема по меньшей мере одного из указанных тестовых выходных сигналов от указанного функционального блока, причем указанная первая схема выборки выполнена с возможностью принятия первого сигнала выборки, а также с возможностью реагирования на соответствующее первое состояние указанного первого сигнала выборки с возможностью подключения указанного по меньшей мере одного из указанных тестовых выходных сигналов от указанного функционального блока к указанному первому выходу первой схемы выборки в качестве указанного выходного сигнала первой схемы выборки, указанная первая схема выборки выполнена с возможностью реагирования на второе состояние указанного первого сигнала выборки с подключением указанного по меньшей мере одного из указанных выходных сигналов от указанного регистра данных сканирования поверхности раздела к указанному выходу первой схемы выборки в качестве указанного выходного сигнала первой схемы выборки, вторую схему выборки, имеющую выход второй схемы выборки, который генерирует выходной сигнал второй выборки, и имеющую входы второй схемы выборки, причем один из указанных входов второй схемы выборки подключен для приема указанного выходного сигнала первой схемы выборки, а другой из указанных входов второй схемы выборки подключен для приема, по меньшей мере, одного из указанных выходных сигналов, генерируемых указанной заказной цифровой логической схемой.

Вторая схема выборки выполнена с возможностью второго сигнала выборки, причем указанная вторая схема выборки реагирует на соответствующее первое состояние указанного второго сигнала выборки для подключения указанного выходного сигнала первой схемы выборки к указанному выходу второй схемы выборки в качестве указанного выходного сигнала второй схемы выборки, при этом указанная вторая схема выборки реагирует на соответствующее второе состояние указанного второго сигнала выборки для подключения указанного по меньшей мере одного из указанных выходных сигналов от указанной заказной цифровой логической схемы к указанному выходу второй схемы выборки в качестве указанного выходного сигнала второй схемы выборки, регистр команд JTAG, выполненный с возможностью хранения информации о командах.

Причем указанная информация о командах в сочетании с состоянием подключения JTAG предназначены для определения указанного первого входа выборки и указанного второго входа выборки, а также по меньшей мере один внешний штырьковый вывод указанной интегральной схемы, подсоединенный к указанному выходу второй схемы выборки таким образом, что указанный выходной сигнал функционального блока поступает на указанный штырьковый вывод, в случае, когда указанный первый сигнал выборки имеет указанное соответствующее первое состояние и указанный второй сигнал выборки имеет указанное соответствующее первое состояние.

Устройство может дополнительно содержать переключательную коммутационную схему, имеющую первый вход, соединенный с внешним входным штырьковым выводом указанной интегральной схемы, второй вход, соединенный с выходом указанной заказной цифровой логической схемы, и выход, соединенный с входом указанного функционального блока, причем указанная переключательная коммутационная схема выполнена с возможностью реагирования на сигнал выборки переключательной коммутационной схемы для соединения указанного первого входа с указанным выходом или для соединения указанного второго входа с указанным выходом. В этом случае предпочтительно указанная переключательная коммутационная схема содержит мультиплексор. Устройство может также дополнительно содержать логический элемент И, выход которого соединен с внешним штырьковым выводом указанного корпуса интегральной микросхемы, и выход, соединенный с множеством тестовых входов указанного функционального блока для обеспечения общего тестового входного сигнала на указанном множестве тестовых входов, причем указанный общий тестовый входной сигнал управляется логическим состоянием, приложенным к указанному внешнему штырьковому выводу, и передается на указанный вход логического элемента И.

Также устройство может дополнительно содержать логический элемент ИЛИ, имеющий вход, соединенный с внешним штырьковым выходом указанного корпуса интегральной схемы, и выход, соединенный с множеством тестовых входов указанного функционального блока для обеспечения общего тестового входного сигнала на указанном множестве тестовых входов, причем указанный общий тестовый входной сигнал управляется логическим состоянием, приложенным к указанному внешнему штырьковому выводу, и передается на указанный вход логического элемента ИЛИ.

Изобретение реализовано использованием способа тестирования функционального элемента в интегральной схеме, содержащей указанный функциональный элемент в качестве компонента указанной схемы, причем указанный функциональный элемент способен генерировать по меньшей мере один тестовый выходной сигнал на выходе функционального блока, который не соединен с внешним штырьковым выводом указанной интегральной схемы в процессе обычной работы указанной интегральной схемы, при этом указанная интегральная схема выполнена с возможностью генерировать множество выходных сигналов, которые передаются на внешние штырьковые выводы указанной интегральной схемы в процессе ее обычной работы, указанная интегральная схема выполнена с возможностью приема множества входных сигналов, которые поступают на указанную интегральную схему с внешних штырьковых выводов указанной интегральной схемы в процессе ее обычной работы, причем подают команды указанной интегральной схеме посредством штырькового ввода JTAG для перевода указанной интегральной схемы в предварительно определенный режим тестирования, избирательно отключают по меньшей мере один из множества выходных сигналов указанной интегральной схемы посредством по меньшей мере первого штырькового вывода указанной интегральной схемы, избирательно направляют указанный тестовый выходной сигнал от указанного функционального блока к первому штырьковому выводу указанной интегральной схемы, подводят тестовый входной сигнал к указанному функциональному блоку посредством второго штырькового вывода указанной интегральной схемы для стимулирования указанного функционального блока в режим тестирования и проводят текущий контроль указанного тестового выходного сигнала указанного функционального блока через указанный первый штырьковый вывод указанной интегральной схемы.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - принципиальная блок-схема, которая иллюстрирует конфигурацию тестовой схемы JTAG.

Фиг.2 - принципиальная блок-схема, на которой показана интегральная схема, имеющая тестовые клеммы входа-выхода, соединенные с внешними штырьковыми выводами интегральной схемы.

Фиг. 3 - диаграмма состояний, показывающая работу контроллера программы анализа транзисторных схем, используемого для управления тестовой схемой JTAG.

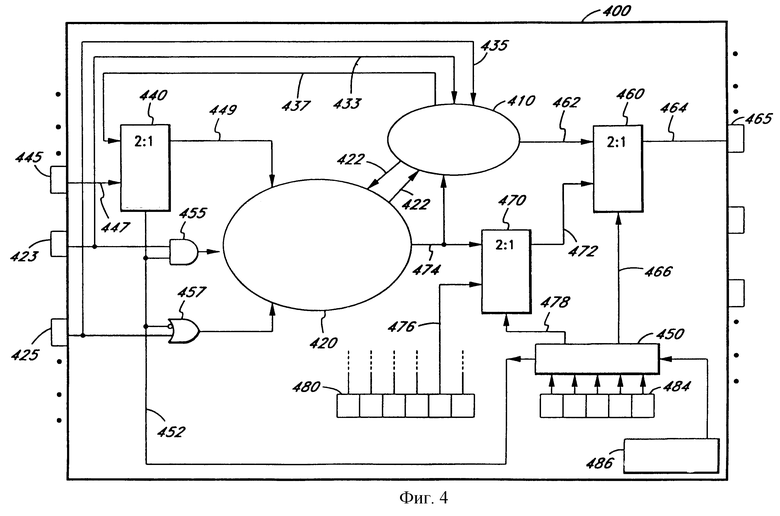

Фиг. 4 - принципиальная блок-схема, на которой показана усовершенствованная тестовая схема JTAG, обеспечивающая соединение внутреннего мегаэлемента с внешними штырьковыми выводами.

В дальнейшем изобретение будет подробно рассмотрено с использованием графического материала.

На фиг. 1 иллюстрируется принципиальная блок-схема, на которой показан кристалл 100 интегральной схемы, для которого предусмотрено тестирование при использовании системы для тестирования последовательным сканированием поверхности раздела JTAG в соответствии со стандартом IEEE 1149.1. Вариант системы JTAG, показанной на фиг. 1, содержит задающий генератор тестовых кодов/компаратор 102, который формирует сигнал данных/команды по линии 105, сигнал режима тестирования по линии 107 и синхронизирующий сигнал тестирования по линии 109. Как известно, в соответствии с обычной терминологией линию 105 передачи сигналов данных/команд называют также сигнальной линией TDI (входа данных тестирования), линию 107 передачи сигнала выбора режима - сигнальной линией TMS (выбора режима тестирования), а линию передачи синхронизирующего сигнала - сигнальной линией ТСК (синхронизирующего сигнала тестирования). Выходные линии 105, 107 и 109 генератора тестовых кодов/компаратора 102 соединены с внешними штырьковыми выводами, выходящими из кристалла 100 интегральной схемы так, чтобы конечный автомат 110 контроллера программы анализа транзисторных схем в кристалле 100 интегральной схемы принимал сигналы по линиям 105, 107 и 109.

Конечный автомат 110 контроллера программы анализа транзисторных схем соединен со сдвиговым регистром 115 данных посредством линии 117 передачи последовательных данных и линии 119 передачи разрешения подачи синхронизирующих импульсов. Конечный автомат 110 контроллера программы анализа транзисторных схем дополнительно соединен со сдвиговым регистром 120 команд по линии 122 передачи последовательных команд и линии 124 передачи разрешения подачи синхронизирующих импульсов. При этом следует отметить, что, как правило, линия 105 входа данных тестирования, линия 117 передачи последовательных данных и линия 122 передачи последовательных команд соединены с общим узлом, а линии 105, 117 и 122 отличаются только тем, что они считаются передающими данные, команды или то и другое.

Сдвиговый регистр 115 данных соединен параллельно с регистром 130 фиксированных данных в то время, как сдвиговый регистр 120 команд соединен параллельно регистру 140 фиксированных команд. Каждая из ячеек памяти двоичных разрядов в регистре 130 фиксированных данных соединена с первым входом мультиплексора в кристалле 100 интегральной схемы. Например, как показано на фиг. 1, одна из ячеек памяти регистра 130 фиксированных данных соединена с первым входом мультиплексора 145 два к одному посредством линии 147. Аналогичным образом, каждая из ячеек памяти в регистре 130 фиксированных данных соединена с входом мультиплексора в кристалле 100 интегральной схемы; однако, как показано на фиг.1, только один мультиплексор 145 для простоты иллюстрации соединен с регистром 130 фиксированных данных.

Регистр 140 фиксированных команд соединен параллельно декодеру 150, который используется для декодирования команд, хранимых в регистре 140 фиксированных команд. Декодер 150 обеспечивает селекторный выход к каждому мультиплексору JTAG в кристалле 100 интегральной схемы (то есть к мультиплексорам, используемым для обеспечения уровней усиленного выхода JTAG). Однако и в этом случае, для простоты иллюстрации декодер 150 показан на фиг. 1 для обеспечения только одного селекторного выхода к мультиплексору 145 посредством линии 152.

Второй вход мультиплексора 145 соединен с типовой интегральной схемотехникой 160 в кристалле 100 интегральной схемы посредством линии 162. Типовая интегральная схемотехника 160 в кристалле 100 интегральной схемы является схемотехникой, которая выполняет специальные функции, которые выполняет кристалл 100 интегральной схемы в процессе нормальной работы (то есть тогда, когда кристалл 100 интегральной схемы не тестируется). Выход мультиплексора 145 соединен со штырьковым выводом на поверхности кристалла 100 интегральной схемы посредством линии 165.

Сдвиговый регистр 115 данных и сдвиговый регистр 120 команд, соответственно, обеспечивают выход последовательных данных и команд по линиям 172, 174 в качестве первого и второго входов в мультиплексор 170, который, в свою очередь, обеспечивает выходы возврата последовательных данных по линии 175 к генератору тестовых кодов/компаратору 102.

В процессе работы генератор тестовых кодов/компаратор 102 генерирует конфигурацию данных и/или команд (как правило, называемую тестовым вектором), которые последовательно подаются по линии 105 к конечному автомату 110 контроллера программы анализа транзисторных схем. Генератор тестовых кодов/компаратор 102 дополнительно обеспечивает сигнал режима и синхросигнал к конечному автомату 110 контроллера программы анализа транзисторных схем по линиям 107 и 109, соответственно. Как будет более подробно описано ниже со ссылкой на фиг.3, конечный автомат 110 контроллера программы анализа транзисторных схем реагирует на сигналы режима и синхросигналы для смещения данных или команд, обеспечиваемого по линии 105 либо в сдвиговый регистр 115 данных (то есть, когда данные обеспечиваются по линии 105), или в сдвиговый регистр 120 команд (то есть, когда команды обеспечиваются по линии 105).

Данные, которые смещаются в сдвиговом регистре 150 данных, и команды, которые смещаются в сдвиговом регистре 120 команд, последовательно синхронизируются в соответствующих сдвиговых регистрах 115, 120 под управлением конечного автомата 110 контроллера программы анализа транзисторных схем. Таким образом, например, если 70 битов данных должны быть смещены в сдвиговом регистре 115 данных и 30 битов команд должны быть смещены в сдвиговом регистре 120 команд, то для смещения битов данных и команд в соответствующих сдвиговых регистрах потребуется в общем 100 периодов синхронизирующих импульсов. Безусловно, что, как будет более подробно описано ниже, дополнительные периоды синхронизирующих импульсов понадобятся для передачи данных из генератора тестовых кодов/компаратора 102 в конечный автомат 110 контроллера программы анализа транзисторных схем и для изменения режима конечного автомата 110 контроллера программы анализа транзисторных схем так, чтобы конечный автомат 110 контроллера программы анализа транзисторных схем обеспечивал соответствующие управляющие сигналы на линиях 119, 124 передачи разрешения подачи синхронизирующих импульсов.

Как только соответствующие данные для тестирования соответствующих входов и выходов кристалла 100 интегральной схемы смещены в сдвиговых регистрах 115, 120, сдвиговые регистры 115, 120 параллельно фиксируют данные и команды, содержащиеся в сдвиговых регистрах 115, 120, в соответствующих регистрах 130, 140. Команды, зафиксированные в регистре 140, декодируются посредством декодера 150 для выбора соответствующего выхода мультиплексора 145, а также любого другого из мультиплексоров JTAG (не показано) в кристалле 100 интегральной схемы. Как вкратце описано выше, каждый из мультиплексоров JTAG (например, мультиплексор 145, показанный на фиг.1) принимает вход JTAG, который соединен с регистром 130 фиксированных данных. Таким образом, например, мультиплексору 145 декодером 150 по линии 152 разрешено выбирать вход 147, соединяющийся с ячейкой памяти в регистре 130.

Таким образом, выход 165 мультиплексора 145 увеличивается на величину двоичного разряда, хранимого в регистре 130. В этом случае соединения выхода кристалла 100 интегральной схемы могут быть тестированы на наличие дефектов по линии 165. Например, если ячейка памяти, соединенная с мультиплексором 145 посредством линии 147, содержит двоичный разряд высокого уровня напряжения (то есть, соответствующий цифре 1), то выход мультиплексора 145 по линии 165 должен быть выявлен (на штырьковом выводе кристалла 100 интегральной схемы) соответствующим цифре 1. Если этот штырьковый вывод не формирует цифру 1, то тестовая схемотехника, с которой соединен кристалл 100 интегральной схемы, зарегистрирует сбой, так что кристалл 100 интегральной схемы может быть назван дефектным. Такой тест осуществляют для каждого из входов и выходов, указываемых декодером 150 в ответ на команды, загружаемые генератором тестовых кодов/компаратором 102.

Безусловно, хотя это и не показано на фиг.1, очевидно, что множество кристаллов интегральных схем могут быть последовательно соединены в цепь так, чтобы генератор тестовых кодов/компаратор 102 мог обеспечивать смещение данных и команд за один раз для множества кристаллов интегральных схем. Таким образом, кристалл 100 интегральной схемы содержит мультиплексор 170, который избирательно смещает данные, проходящие через регистр 115, или команды, проходящие через регистр 120, по линиям 172 или 174 под управлением конечного автомата 110 контроллера программы анализа транзисторных схем. Наконец, выходные данные из последней интегральной схемы передаются назад в генератор тестовых кодов/компаратор 102 по линии 175 последовательного возврата.

На фиг. 2 иллюстрируется принципиальная блок-схема, на которой показан кристалл 200 интегральной схемы, содержащий покупной мегаэлемент 210 помимо типовой интегральной схемотехники 220. Мегаэлемент 210 работает как функциональный модуль в кристалле 200 интегральной схемы, который принимает входы и обеспечивает входы к типовой схемотехнике 220 по линиям 225.

Покупной мегаэлемент 210 отличается от типовой схемотехники 220 в том отношении, что покупной мегаэлемент 210 имеет стандартную структуру и функцию, обеспечиваемые поставщиком в то время, как типовая схемотехника является заказной, разработанной конструктором интегральной схемы частного применения. Таким образом, модуль мегаэлемента имеет независимую функциональность (то есть мегаэлемент может быть использован для выполнения аналогичной функции во множестве различных окружающих схемных конфигураций, так что эта функциональность по существу не зависит от другой схемотехники в кристалле 200 интегральной схемы). Кроме того, отдельный набор тестовых векторов, которые используют для тестирования всего кристалла 200 интегральной схемы, как правило, используют для отдельного тестирования функциональности мегаэлемента 210.

Таким образом, например, конструктор интегральной схемы частного применения использует стандартные функциональные логические блоки, например универсальные асинхронные приемопередатчики, системы фазовой автоподстройки частоты и так далее, которые конструктор интегральной схемы частного применения включает в состав заказной интегральной схемы частного применения. Эти стандартные функциональные блоки называют мегаэлементами и поставщик мегаэлемента, как правило, предоставляет тестовые векторы, которые используют в процессе производства кристалла для тестирования мегаэлемента в интегральной схеме частного применения. Как правило, интегральная схема частного применения может тестироваться как единый модуль, но, если в нем обнаруживаются неисправности, то будет трудно определить, появились ли эти неисправности из-за заказной схемотехники, структура которой разработана конструктором интегральной схемы частного применения, или из-за схемотехники покупного мегаэлемента. По этой причине мегаэлементы тестируют независимо, используя тестовые векторы, обеспечиваемые поставщиком элемента. Кроме того, конструктору интегральной схемы частного применения не нужно затрачивать усилия на всесторонние испытания мегаэлемента, поскольку эти испытания будут сделаны посредством тестов, предоставляемых поставщиком.

Однако, как показано на фиг.2, для тестирования мегаэлемента, например мегаэлемента 210, тестовые выходы из мегаэлемента 210 требуют множества штырьковых выводов 235 на наружной поверхности кристалла 200 интегральной схемы частного применения. Передаваемые поставщиком тестовые векторы прикладываются к тестовым входам 230 и измеряется результирующая конфигурация на тестовых выходах 235 для определения, правильно ли функционирует мегаэлемент. Таким образом, штырьковые выводы 235 являются излишними в процессе нормальной работы кристалла интегральной схемы. Как будет более подробно описано ниже со ссылкой на фиг.4, настоящее изобретение обеспечивает уменьшение числа штырьковых выводов на корпусе интегральной схемы, в который заключена схема мегаэлемента. Экономии, обеспечиваемые с помощью настоящего изобретения, могут быть значительными (например, порядка от одного до двух десятков штырьковых выводов, которые могут быть исключены), так что могут быть использованы более дешевые кристалл (то есть кристалл меньшего размера) и корпус интегральной схемы.

На фиг.3 показана диаграмма состояний, которая иллюстрирует работу конечного автомата 110 контроллера программы анализа транзисторных схем в ответ на управляющие сигналы, обеспечиваемые по линиям 107, 109 передачи выбора режима тестирования и синхронизирующего сигнала тестирования. Конечный автомат 110 контроллера программы анализа транзисторных схем начинает с нерабочего состояния 300, в которое он возвращается между операциями сканирования. Будучи включенным, автомат 110 контроллера программы анализа транзисторных схем останется в нерабочем состоянии 300, пока низок уровень сигнала выбора режима тестирования. В нерабочем состоянии 300 активность в выбранной тестовой логике появляется только тогда, когда поступят некоторые команды, как хорошо понятно специалисту в этой области техники. Так как команды, загружаемые в регистр 140 команд, не побуждают конечный автомат 110 контроллера программы анализа транзисторных схем, находящийся в нерабочем состоянии 300, работать, он продолжит оставаться в прежнем состоянии (то есть в нерабочем состоянии). Кроме того, команды, загружаемые в регистр 140 команд, не изменяются в то время, как конечный автомат 110 контроллера программы анализа транзисторных схем находится в нерабочем состоянии 300.

Когда сигнал выбора режима тестирования (передаваемый по линии 107) велик и нарастающий фронт прикладывается к синхронизирующему сигналу тестирования (передаваемому по линии 109), конечный автомат 110 контроллера программы анализа транзисторных схем переходит в состояние 305 селекторного сканирования регистра данных. Состояние 305 селекторного сканирования регистра данных является временным состоянием контроллера, в котором все регистры тестовых данных, выбранные посредством текущей команды, удерживаются в их предшествующем состоянии. Если сигнал выбора режима тестирования удерживается низким в то время, как нарастающий фронт прикладывается к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем переходит в состояние 315 регистра собранных данных, хотя, если сигнал выбора режима тестирования удерживается высоким, а нарастающий фронт прикладывается к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем переходит в состояние 310 селекторного сканирования регистра команд.

Если конечный автомат 110 контроллера программы анализа транзисторных схем переходит в состояние 315 регистра собранных данных, то в этом состоянии данные могут быть параллельно загружены в регистр 130 данных из сдвигового регистра 115 данных при нарастающем фронте синхронизирующего сигнала тестирования. Если тестовая схемотехника JTAG не содержит параллельно загружаемого регистра 130 данных или если для выбора теста не требуется захвата, то регистр данных сохраняет свое предшествующее состояние неизменным. Кроме того, двоичные разряды, хранимые в регистрах 140, 120 команд, остаются неизменными в то время, как конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 315 регистра собранных данных.

Если конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 315 регистра собранных данных в то время, как сигнал выбора режима тестирования поддерживается низким, а нарастающий фронт приложен к синхронизирующему сигналу тестирования, то контроллер входит в состояние 320 сдвигового регистра данных. Однако, если сигнал выбора режима тестирования поддерживается высоким в то время, как нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем непосредственно из состояния 315 регистра собранных данных переходит в состояние 325 регистра данных вывода. В состоянии 320 сдвигового регистра данных данные по линии 105 смещаются в сдвиговый регистр 115 данных через линию 117. При приложении каждого нарастающего фронта синхронизирующего сигнала тестирования в то время, как сигнал выбора режима тестирования поддерживается низким, дополнительный бит данных смещается в сдвиговый регистр 115 данных по линии 117. Конечный автомат 110 контроллера программы анализа транзисторных схем продолжает находиться в состоянии 320 сдвигового регистра данных до тех пор, пока сигнал выбора режима тестирования поддерживается низким. Таким образом, столько битов данных, сколько необходимо для загрузки предварительно определенных тестовых векторов в сдвиговый регистр 115 данных, смещается в сдвиговый регистр 115 данных в то время, как сигнал выбора режима тестирования поддерживается низким в состоянии 320.

Если конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 320 сдвигового регистра данных, а нарастающий фронт приложен к синхронизирующему сигналу тестирования в то время, как сигнал выбора режима тестирования высок, то конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 325 регистра данных вывода. Состояние 325 регистра данных вывода является временным состоянием контроллера. Если сигнал выбора режима тестирования поддерживается высоким, то нарастающий фронт, приложенный к синхронизирующему сигналу тестирования, побуждает конечный автомат 110 контроллера программы анализа транзисторных схем войти в состояние 340 регистра обновленных данных, хотя, если сигнал выбора режима тестирования поддерживается низким в то время, как нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 330 регистра данных паузы.

Состояние 330 регистра данных паузы позволяет временно остановить смещение регистра 315 тестовых данных. Конечный автомат 110 контроллера программы анализа транзисторных схем остается в состоянии 330 регистра данных паузы, хотя сигнал выбора режима тестирования поддерживается низким. Если сигнал выбора режима тестирования поддерживается высоким, а нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 335 регистра данных вывода 2, которое также является временным состоянием контроллера. Если нарастающий фронт приложен к синхронизирующему сигналу тестирования, хотя сигнал выбора режима тестирования поддерживается низким, то конечный автомат 110 контроллера программы анализа транзисторных схем возвращается в состояние 320 сдвигового регистра данных. Однако, если сигнал выбора режима тестирования поддерживается высоким в то время, как нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем переходит из состояния 335 регистра данных вывода 2 в состояние 340 регистра обновленных данных.

Как показано на фиг.1, сдвиговый регистр 115 данных содержит фиксированный параллельный выход для предотвращения изменению данных в регистре 130 данных в то время, как данные смещаются в связанный с ним сдвиговый регистр 115 данных в ответ на некоторые команды совместно с регистром 140 команд. Таким образом, в состоянии 340 регистра обновленных данных данные фиксируются из сдвигового регистра 115 данных на параллельном выходе сдвигового регистра 115 данных на падающем фронте синхронизирующего сигнала тестирования. Таким образом, эти данные хранятся в регистре 130 фиксированных данных, так что данные в регистре 130 не изменяются иначе, чем в состоянии регистра обновленных данных, если не требуется работа в процессе осуществления самотестирования (например, в течение нерабочего состояния в ответ на соответствующую команду).

В каждом из состояний 305-335 команды, хранимые в сдвиговом регистре 120 команд и в регистре 140 фиксированных команд, не изменяются в то время, как конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 340 регистра обновленных данных. Если конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии регистра обновленных данных, а нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 305 селекторного сканирования регистра данных, если сигнал выбора режима тестирования поддерживается высоким, или в состояние 300, если сигнал выбора режима тестирования поддерживается низким.

Если сигнал выбора режима тестирования поддерживается высоким, а нарастающий фронт приложен к синхронизирующему сигналу тестирования в то время, как конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 305 селекторного сканирования регистра данных, то конечный автомат 110 контроллера программы анализа транзисторных схем переходит в состояние 310 селекторного сканирования регистра команд.

Если конечный автомат 110 контроллера программы анализа транзисторных схем переходит в состояние 345 регистра собранных команд, то в этом состоянии команды могут быть загружены параллельно в регистр 140 команд из сдвигового регистра 120 команд на нарастающем фронте синхронизирующего сигнала тестирования. Если тестовая схемотехника JTAG не содержит параллельно загружаемого регистра 140 команд или если не требуется сбора (команд) для выбранного теста, то сдвиговый регистр 120 команд удерживается в своем предшествующем состоянии неизмененным. Кроме того, биты (данных), хранимые в регистрах 130, 115 данных, остаются неизменными, хотя конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 345 регистра собранных команд. Если конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 345 регистра собранных команд, хотя сигнал выбора режима тестирования поддерживается низким, а нарастающий фронт приложен к синхронизирующему сигналу тестирования, то контроллер входит в состояние 350 сдвигового регистра команд. Однако, если сигнал выбора режима тестирования поддерживается высоким, хотя нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем непосредственно из состояния 345 регистра собранных команд переходит в состояние 355 регистра команд вывода.

В состоянии 350 сдвигового регистра команд команды по линии 105 смещаются в сдвиговый регистр 120 команд посредством линии 122. При приложении каждого нарастающего фронта синхронизирующего сигнала тестирования в то время, как сигнал выбора режима тестирования поддерживается низким, дополнительный бит команды смещается в сдвиговый регистр 120 команд по линии 122. Конечный автомат 110 контроллера программы анализа транзисторных схем продолжает находиться в состоянии 350 регистра команд пока сигнал выбора режима тестирования поддерживается низким. Таким образом, в регистр 120 смещается столько битов команды, сколько необходимо для загрузки предварительно определенных векторов команд в сдвиговый регистр 120, хотя сигнал выбора режима тестирования в состоянии 350 поддерживается низким.

Если конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 350 сдвигового регистра команд, а нарастающий фронт приложен к синхронизирующему сигналу тестирования в то время, как сигнал выбора режима тестирования поддерживается высоким, то конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 355 регистра команд вывода. Состояние 355 регистра команд вывода является временным состоянием контроллера. Если сигнал выбора режима тестирования поддерживается высоким, то нарастающий фронт, приложенный к синхронизирующему сигналу тестирования, побуждает конечный автомат 110 контроллера программы анализа транзисторных схем войти в состояние 370 регистра обновленных команд в то время, как, если сигнал выбора режима тестирования поддерживается низким, хотя нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 360 регистра команд паузы.

Состояние 360 регистра команд паузы позволяет временно остановить смещение регистра 345 собранных команд. Конечный автомат 110 контроллера программы анализа транзисторных схем остается в состоянии 360 регистра команд паузы в то время, как сигнал выбора режима тестирования поддерживается низким. Если сигнал выбора режима тестирования поддерживается высоким, а нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 365 регистра команд вывода 2, которое также является временным состоянием контроллера. Если нарастающий фронт приложен к синхронизирующему сигналу тестирования в то время, как сигнал выбора режима тестирования поддерживается низким, то конечный автомат 110 контроллера программы анализа транзисторных схем возвращается в состояние 350 сдвигового регистра команд. Однако, если сигнал выбора режима тестирования поддерживается высоким в то время, как нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем переходит из состояния 365 регистра команд вывода 2 в состояние 370 регистра обновленных команд.

Как показано на фиг.1, сдвиговый регистр 120 команд содержит зафиксированный параллельный выход для предотвращения изменений команды в регистре 140 команд в то время, как команда смещается в соответствующий сдвиговый регистр 120 команд в ответ на некоторые команды совместно с регистром 140 команд. Таким образом, в состоянии 370 регистра обновленных команд команды зафиксированы из сдвигового регистра 120 в параллельном выходе сдвигового регистра 120 на нарастающем фронте синхронизирующего сигнала тестирования. Таким образом, эти команды хранятся в регистре 140 фиксированных команд, так что команды в регистре 140 не изменяются иначе, чем в состоянии регистра обновленных команд, если не требуется работы в процессе выполнения самотестирования (например, в течение нерабочего состояния в ответ на специальную команду). В каждом из состояний 310 и 345-365 данные, хранимые в сдвиговом регистре 15 и регистре 130 фиксированных данных, не изменяются в то время, как конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 370 обновленных команд. Если конечный автомат 110 контроллера программы анализа транзисторных схем находится в состоянии 370 регистра обновленных команд, а нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 305 селекторного сканирования регистра данных, когда сигнал выбора режима тестирования поддерживается высоким, или в нерабочее состояние 300, когда сигнал выбора режима тестирования поддерживается низким.

Если в состоянии 310 селекторного сканирования регистра команд сигнал выбора режима тестирования поддерживается высоким в то время, как нарастающий фронт приложен к синхронизирующему сигналу тестирования, то конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 342 возврата тестовой логики в исходное состояние. Если конечный автомат 110 контроллера программы анализа транзисторных схем входит в состояние 342 возврата тестовой логики в исходное состояние, то тестовая логика отключается, так что нормальная работа логики системы на кристалле интегральной схемы (то есть в ответ на сигналы, принятые через системы штырьковых выводов) может беспрепятственно продолжаться. Конечный автомат 110 контроллера программы анализа транзисторных схем остается в состоянии 342 возврата тестовой логики в исходное состояние в то время, как сигнал выбора режима тестирования поддерживается высоким. Посредством сигнала выбора режима тестирования низким в течение нарастающего фронта на синхронизирующем сигнале тестирования конечный автомат 110 контроллера программы анализа транзисторных схем войдет в нерабочее состояние 300.

На фиг.4 показана принципиальная блок-схема, которая иллюстрирует пример внутренней тестовой схемы JTAG в кристалле 400 интегральной схемы. Для простоты пояснения настоящего изобретения, на фиг.4 не показаны конечный автомат 110 контроллера программы анализа транзисторных схем, сдвиговые регистры 115, 120 данных и команд и другая связанная с ними схемотехника JTAG. Однако специалисту в этой области техники будет очевидно, что кристалл 400 интегральной схемы содержит вышеупомянутую схемотехнику JTAG, работающую по существу так же, как описано выше. Кристалл 400 интегральной схемы может, например, содержать интегральную схему частного применения, которая содержит заказную схемотехнику, разработанную конструктором интегральных схем частного применения (показанную на фиг.4 как типовая схемотехника 410), и покупную структуру для мегаэлемента, которую конструктор интегральных схем частного применения внедряет в заказную интегральную схему частного применения (показанную на фиг.4 как схемотехника мегаэлемента 420). Типовая схемотехника 410 имеет связь через входные и выходные линии 422 со схемотехникой мегаэлемента 420. Например, схемотехника мегаэлемента 420 может содержать стандартный модуль арифметической логики, микропроцессор или другую схемотехнику, которая имеет стандартную конструкцию и может быть выполнена в виде независимого модуля в кристалле 400 интегральной схемы частного применения.

Типовая схемотехника 410 принимает входные сигналы из внешних штырьковых выводов, например штырьковых выводов 423, 425, по линиям 433, 435. Безусловно очевидно, что, как правило, типовая схемотехника 410 будет принимать порядка десятков или даже сотен входов, но с целью ясности иллюстрации настоящего изобретения для соединения с типовой схемотехникой показаны только входные клеммы 423, 425. Помимо выходных сигналов по линиям 422 к схемотехнике мегаэлемента 420 типовая схемотехника 410 может также иметь выход некоторых сигналов к схемотехнике мегаэлемента 420 по линии 437, которая соединяется с первым входом мультиплексора 440 два к одному. Мультиплексор 440 по линии 447 дополнительно принимает входной сигнал из внешнего штырькового вывода 445. Выход мультиплексора 440 подается на вход мегаэлемента 420 по линии 449, как показано на фиг.4.

Мультиплексор 400 по линии 452 принимает селекторный вход из декодера 450. Схемотехника мегаэлемента 420 дополнительно принимает тестовые входы из логического элемента 455 И и логического элемента 457 ИЛИ. Безусловно очевидно, что схемотехника мегаэлемента 420 будет иметь, как правило, несколько тестовых входов, а логический элемент 455 И и логический элемент 457 ИЛИ показаны в качестве примеров тестовых входов в схемотехнику мегаэлемента 420. Логический элемент 455 И принимает первый вход по линии 452, а второй вход - по линии 433 из штырькового вывода 423. Кроме того, логический элемент 457 ИЛИ принимает первый инвертирующий вход по линии 452, а второй вход - по линии 435 из штырькового вывода 425. Хотя для простоты иллюстрации на фиг.4 это не показано, но имеются штырьковый вывод и выходные буферы.

Типовая схемотехника 410 соединена с входом выходного мультиплексора 460 JTAG по линии 462. И в этом случае должно быть очевидно, что типовая схемотехника 410 будет, как правило, иметь порядка десятков или сотен выходов, однако для ясности иллюстрации на фиг.4 показан только выход 462. Выход мультиплексора 460 два к одному обеспечен к внешнему штырьковому выводу по линии 464. Селекторный вход мультиплексора 460 два к одному обеспечен посредством декодера 450 по линии 466. В соответствии со стандартной схемотехникой второй вход мультиплексора 460 два к одному будет соединен непосредственно к регистру фиксированных данных сканирования поверхности раздела так, чтобы величина стандартного входа JTAG заставляла бы выходную клемму 465 иметь двоичный разряд, равный двоичному разряду JTAG, когда соответствующий селекторный сигнал подается на вход мультиплексора 460 два к одному. Однако в соответствии с настоящим изобретением второй вход мультиплексора 460 может также принимать выход из схемотехники мегаэлемента 420 через мультиплексор 470 два к одному по линии 472.

Характерно то, что мультиплексор 470 два к одному принимает первый вход по линии 474 из схемотехники мегаэлемента 420. Мультиплексор 479 два к одному дополнительно принимает второй вход из регистра 480 фиксированных данных сканирования поверхности раздела по линии 476. Наконец, мультиплексор 470 два к одному принимает селекторный вход из декодера 450 по линии 478. Декодер 450 декодирует команды, содержащиеся в регистре 484 фиксированных команд.

В процессе нормальной (то есть не тестовой) работы типовая схемотехника 410 и схемотехника мегаэлемента 420 принимает входы через множество штырьковых выводов (например, через штырьковые выводы 423, 425 и 445) и обрабатывает эти входы в соответствии с конструкцией интегральной схемы частного применения для обеспечения множества выходных величин на множестве штырьковых выводов (например, на штырьковом выводе 465). В процессе нормальной работы типовая схемотехника 410 и схемотехника мегаэлемента 420 изменяют данные через внутренние схемные дорожки (например, схемные дорожки 422, 437 и 474), так что схемотехника мегаэлемента 420 действует как модуль, который выполняет предварительно определенную функцию, которая поддерживает общую работу кристалла 400 интегральной схемы частного применения.

Таким образом, для тестирования функциональности цепей мегаэлемента в интегральной схеме частного применения, как правило, необходимо вывести некоторые входные и выходные линии мегаэлемента на штырьковые выводы кристалла интегральной схемы частного применения так, чтобы в цехе изготовления кристаллов можно было бы независимо тестировать схемотехнику мегаэлемента, используя тестовые векторы, обеспечиваемые поставщиком мегаэлемента. Безусловно, как подробно описано выше, это приводит к некоторому числу лишних штырьковых выводов на поверхности кристалла интегральной схемы, которые не используются в процессе нормальной работы интегральной схемы. Таким образом, в соответствии с настоящим изобретением, схемотехника JTAG, образованная в кристалле 400 интегральной схемы частного применения, специально модифицирована для обеспечения выходных дорожек для схемотехники мегаэлемента 420 так, чтобы схемотехника мегаэлемента 420 могла быть протестирована в цехе изготовления кристаллов, не требуя дополнительных штырьковых выводов на кристалле 400 интегральной схемы частного применения.

Характерно, что дополнительный мультиплексор 470 дает возможность второго входа в мультиплексор 460, для поочередного использования выхода JTAG или в качестве выхода мегаэлемента в соответствии с тем, как определяется сигналом селекторной линии 478 из декодера 450. Таким образом, вместо соединения тестовой выходной линии 474 мегаэлемента 420 непосредственно к внешнему штырьковому выводу, аналогичная выходная линия 464, которая используется для поочередного обеспечения вывода стандартного выхода сканирования поверхности раздела JTAG или выхода типовой схемотехники, может быть также использована для вывода тестового сигнала из схемотехники мегаэлемента 420. Выбор выходного сигнала на линии 464 из одного из трех возможных выходов (то есть выход из типовой схемотехники 410, выход из схемотехники мегаэлемента 420 или выход сканирования поверхности раздела JTAG из регистра 480 фиксированных данных) координируется под управлением декодера 450, как определяется командами, находящимися в регистре 484 фиксированных команд. Таким образом, для обеспечения дополнительных управляющих сигналов, осуществление настоящего изобретения может потребовать дополнительных ячеек памяти или конфигураций декодирования в регистре 484 фиксированных команд. Однако современные регистры команд в тестовой схемотехнике JTAG, как правило, определяются пользователем, так что для обеспечения дополнительных данных управления могут быть использованы резервные состояния декодирования.

При тестировании схемотехники мегаэлемента 420 в соответствии со способами настоящего изобретения входы тестового вектора (предоставляемого поставщиком мегаэлемента) подают на внешние штырьковые выводы (например, штырьковые выводы 423, 425). Если сигнал на линии 452 поддерживается высоким, то входы тестового вектора, подаваемые на клеммы 423, 425, проходят через логический элемент 455 И и логический элемент 457 ИЛИ к тестовым входам схемотехники мегаэлемента 420. Специалисту в этой области техники будет очевидно, что, если сигнал режима тестирования на линии 452 будет низким, то выходы логического элемента 455 И и логического элемента 457 ИЛИ устанавливаются низким и высоким, соответственно так, чтобы предотвращать обеспечения тестовых входов в схемотехнику мегаэлемента 420 в процессе нормальной работы. Когда входы стандартного тестового вектора, поданные на входные клеммы 423, 425, пропускают к тестовым входам схемотехники мегаэлемента 420, в ответ на входы тестового вектора схемотехника мегаэлемента 420 формирует выходные сигналы по множеству выходных линий.

В примере, приведенном на фиг.4, для простоты иллюстрации показана только выходная линия 474; однако очевидно, что для полного тестирования функциональных характеристик схемотехники мегаэлемента 420 к множеству мультиплексоров два к одному (таких как мультиплексор 470) будет обеспечено множество выходных линий.

Выходной сигнал схемотехники мегаэлемента 420 в ответ на входы тестового вектора обеспечивается как первый вход в мультиплексор 470 по линии 474. В режиме тестирования мегаэлемента регистр 484 фиксированных команд дополнительно содержит биты команды, которые побуждают декодер 450 возбуждать селекторный сигнал на линии 478 для выбора тестового выхода мегаэлемента на линии 474. Таким образом, на линии 472 на выходе мультиплексора 470 обеспечивается выход схемотехники мегаэлемента 420 в ответ на входы тестового вектора. В ответ на команды в регистре 484 декодер 450 на линии 464 дополнительно обеспечивает сигнал для выбора входной линии 472 так, чтобы на линии 464 к штырьковому выводу 465 обеспечивался тестовый выход схемотехники мегаэлемента. Если схемотехника мегаэлемента 420 функционирует правильно, то входы тестового вектора вызовут формирование адекватной конфигурации выходов тестового вектора на штырьковых выводах, проводящая дорожка к которым обеспечена из схемотехники мегаэлемента 420. Таким образом, штырьковый вывод 465 станет показателем функциональности схемотехники мегаэлемента 420 при подаче входов тестового вектора на штырьковые выводы 423, 425. Таким образом, функциональность схемотехники мегаэлемента 420 может быть протестирована без обеспечения дополнительных штырьковых выводов на кристалле 400 интегральной схемы.

Когда функциональность схемотехники мегаэлемента 420 не тестируют, регистр 484 команд загружается соответствующими битами команд для побуждения декодера 450 выбирать либо режим нормальной работы, либо режим тестирования JTAG. Если выбран режим тестирования JTAG, то это побуждает декодер 450 обеспечить выход селекторного сигнала по линиям 478 для прохождения входа по линии 476 из регистра 480 фиксированных данных к выходу 472 мультиплексора 470. Кроме того, декодер 450 обеспечивает выход селекторного сигнала по линии 466, который побуждает вход на линии 472 (который представляет величину бита данных в регистре 480 фиксированных данных по линии 476) пройти на выход 464 мультиплексора 460 так, чтобы на штырьковом выводе 465 обеспечивался бит данных сканирования поверхности раздела JTAG, если имеет место целостность выходной дорожки.

С другой стороны, если кристалл 400 интегральной схемы частного применения должен работать в нормальном режиме, то контроллер 486 состояния JTAG побуждает декодер 450 выбирать первый вход 462 мультиплексора 460 так, чтобы сигнал на линии 462 был выходом на штырьковый вывод 465 через мультиплексор 460 и линию 464. Кроме того, декодер 450 обеспечивает выход небольшого сигнала на линии 452, так что тестовые входы в схемотехнику мегаэлемента 420 поддерживаются на определенной величине так, чтобы на работу схемотехники мегаэлемента 420 не оказывали влияние входы на штырьковых выводах 423, 425.

Хотя предпочтительные варианты осуществления настоящего изобретения были подробно описаны выше, специалисту в этой области техники будут очевидны модификации, которые могут быть сделаны без отклонения от сущности и объема изобретения. Таким образом, приведенное выше описание должно рассматриваться как иллюстративное, а не ограничительное. По этой причине объем настоящего изобретения должен приниматься, принимая во внимание прилагаемую формулу изобретения.

Изобретение относится к устройствам тестирования интегральных схем. Техническим результатом является уменьшение размера печатной платы и стоимости интегральной схемы. Для этого устройство содержит функциональный блок, заказную цифровую логическую схему, регистр данных, регистр команд, схемы выборки. Способ содержит следующие операции: избирательное отключение подачи одного из множества выходных сигналов от интегральной схемы, направление тестового выходного сигнала от функционального блока к первому внешнему штырьковому выводу интегральной схемы для выполнения функциональным блоком операции тестирования. 2 с. и 6 з.п.ф-лы, 4 ил.

| US 5150044 A, 22.09.1992 | |||

| ТЕСТОВАЯ ИНТЕГРАЛЬНАЯ СТРУКТУРА | 1990 |

|

RU2034306C1 |

| US 5115435 A, 19.05.1992 | |||

| US 4855669 A, 08.08.1989 | |||

| СПОСОБ КОНТРОЛЯ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 1986 |

|

SU1417613A1 |

Авторы

Даты

2003-02-10—Публикация

1996-06-06—Подача