Изобретение относится к электротехнике и может быть использовано в системах регулирования угловой скорости, в частности электроприводах с широким диапазоном ее стабилизации, где в качестве датчика обратной связи используется сельсин или аналогичное ему устройство, например синусно-косинусный вращающийся трансформатор.

Известен электропривод [1], включающий в себя замкнутый контур регулирования, состоящий из последовательно включенных формирователя прямоугольных импульсов, устройства коррекции, фазового дискриминатора, силового ключа, двигателя и сельсина, обмотки возбуждения которого через согласующее устройство и первый делитель частоты подключены к выходу генератора задающей частоты, который также соединен через второй делитель со вторым входом фазового дискриминатора. Такое устройство обеспечивает малую погрешность стабилизации угловой скорости, для изменения уровня которой используется согласованное управление первым и вторым делителем частоты. Однако так как в момент пуска положение импульсов частотных сигналов задания и обратной связи в общем случае произвольно, на выходе частотно-фазового дискриминатора появляется постоянный сигнал, соответствующий разгону или торможению двигателя. При этом процесс пуска сопровождается значительными (до 500% и более) бросками скорости или длительными (порядка нескольких секунд) промежутками времени между моментами подачи сигнала управления и начала движения. Такой эффект наиболее заметен в нижней части диапазона регулирования скорости двигателя

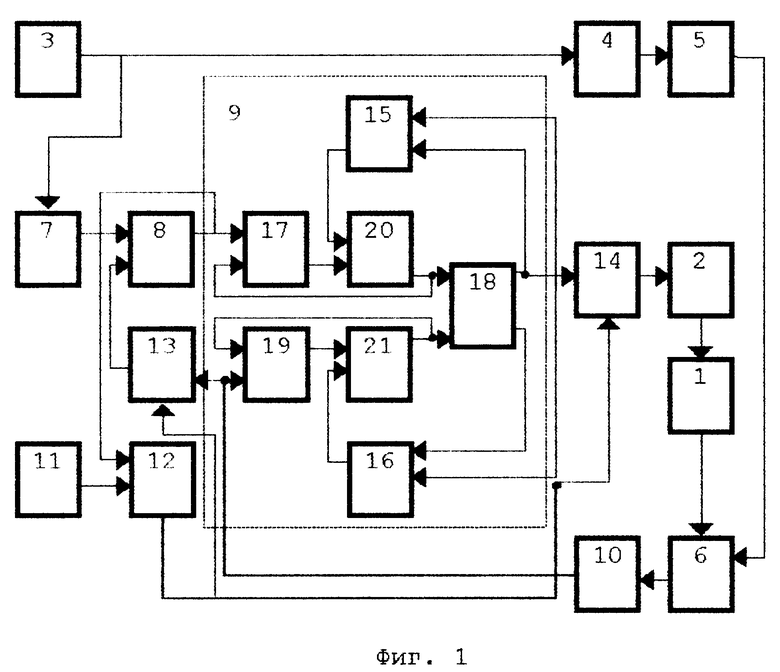

Наиболее близким к предлагаемому устройству является электропривод постоянного тока [2], функциональная схема которого приведена на фиг. 1.

Электропривод содержит двигатель 1, подключенный к выходу силового преобразователя 2, последовательно соединенные генератор 3 задающей частоты, первый делитель 4, согласующий элемент 5 и сельсин 6, установленный на валу двигателя 1. Генератор 3 через последовательно соединенные блок задания 7 и второй делитель 8 частоты соединен с первым входом частотно-фазового дискриминатора 9, второй вход которого через формирователь прямоугольных импульсов 10 подключен к выходу сельсина 6. Шина управления 11 соединена с информационным входом триггера 12, счетный вход которого связан с выходом второго делителя 8, а выход - с входом управления одновибратора 13, первым входом элемента ИЛИ-НЕ 14 и третьим входом дискриминатора 9, к которому подключены первые входы элементов ИЛИ 15,16. Выход одновибратора 13, запускаемого сигналом формирователя прямоугольных импульсов 10, соединен с входом сброса второго делителя 8, Частотно-фазовый дискриминатор 9 состоит из элементов ИЛИ 15,16, триггеров 17-19 и элементов И 20, 21. Первый вход дискриминатора 9 через последовательно соединенные триггер 17 и элемент И 20 связан с первым входом триггера 18, инверсный выход которого соединен через элемент ИЛИ 15 со вторым входом элемента И 20. Второй вход дискриминатора 9 через последовательно соединенные триггер 19 и элемент И 21 связан со вторым входом триггера 18, прямой выход которого соединен через элемент ИЛИ 16 со вторым входом элемента И 21. Второй выход триггера 18, являющегося выходом дискриминатора 9, через элемент ИЛИ-НЕ 14 соединен с входом силового преобразователя 2.

Такой электропривод обеспечивает плавный процесс пуска во всем диапазоне регулирования угловой скорости. В то же время при резких изменениях сигнала задания, когда частотно-фазовый дискриминатор 9 достигает состояния насыщения, затягиваются процессы выхода на задаваемое значение скорости. Это обусловлено алгоритмом работы частотно-фазового дискриминатора 9, выход которого из состояния насыщения происходит только при нарушении последовательности чередования импульсов входных частот, то есть при неизбежном появлении ошибки управляемой координаты. Кроме того, использование дискретной логики малой степени интеграции увеличивает габариты устройства и усложняет процесс его наладки.

Технический результат предлагаемого изобретения заключается в уменьшении ошибок стабилизации скорости в динамических режимах и снижении затрат оборудования на изготовление электропривода. Для этого в известном устройстве частотно-фазовый дискриминатор выполнен на базе восьмиразрядного регистра и БИС программируемого запоминающего устройства (ПЗУ), причем первый-восьмой выходы регистра соединены с четвертым-одиннадцатым адресными входами ПЗУ, восемь выходов данных которого подключены к информационным входам регистра. Первый, второй и третий адресные входы ПЗУ являются первым - третьим входами частотно-фазового дискриминатора соответственно. Первый вход частотно-фазового дискриминатора через формирователь прямоугольных импульсов подключен к выходу сельсина, а шина управления через триггер соединяется со вторым входом частотно-фазового дискриминатора. Третий вход дискриминатора связан с выходом второго делителя. Седьмой выход ПЗУ, представляющий собой первый выход дискриминатора, соединен с входом силового преобразователя и предназначен для управления скоростью двигателя. Для формирования переходных процессов ко второму входу второго делителя подключен второй выход дискриминатора, соединенный с восьмым выходом ПЗУ. Счетный вход регистра, являющийся четвертым входом частотно-фазового дискриминатора, подключен к выходу генератора задающей частоты. Частотно-фазовый дискриминатор обеспечивает выявления фазового рассогласования, поступающих с выходов второго делителя и формирователя прямоугольных импульсов, В режиме стабилизации скорости двигателя на выходе дискриминатора формируется широтно-импульсный сигнал, длительность которого пропорциональна разности фаз сравниваемых сигналов. При регулировании скорости нарушается последовательность чередования импульсов с выхода второго генератора и формирователя прямоугольных импульсов. При этом частотно-фазовый дискриминатор переходит в режим насыщения, при котором на его выходе появляется постоянный сигнал, величина которого определяется знаком разности частот сравниваемых импульсов. При этом на втором выходе дискриминатора формируются сигналы управления вторым делителем, синхронизирующие начало его счета с фронтами прямоугольных импульсов формирователя, что обеспечивает уменьшение перерегулирования скорости в переходных процессах.

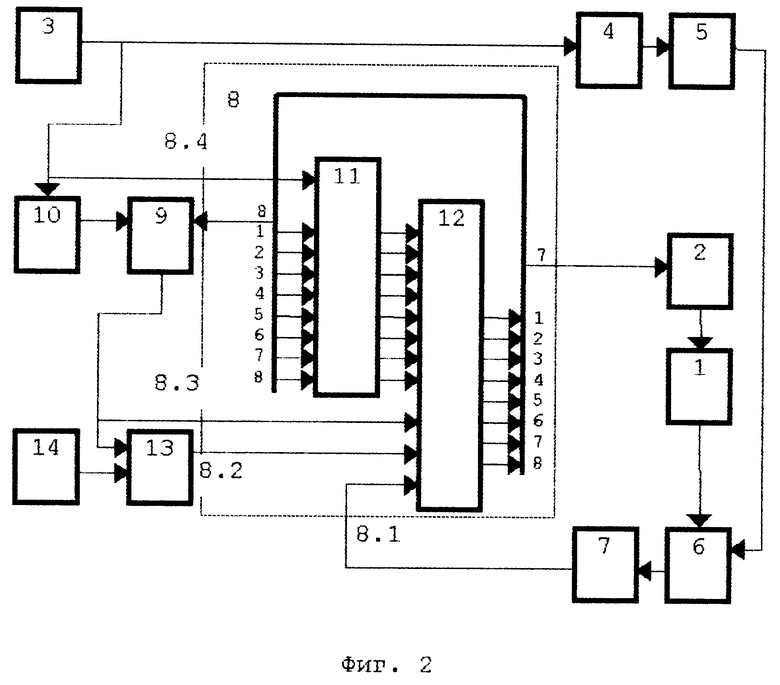

На фиг. 2 приведена функциональная схема электропривода.

Электропривод содержит двигатель 1, подключенный к выходу силового преобразователя 2. Генератор 3 задающей частоты через последовательно соединенные первый делитель 4 частоты и согласующий элемент 5, подключен к входу сельсина 6, выход которого через формирователь 7 прямоугольных импульсов подключен к первому входу 8.1 частотно-фазового дискриминатора 8, Дискриминатор 8 выполнен на базе регистра 11 и постоянного запоминающего устройства (ПЗУ) 12, один из адресных входов которого, являющийся вторым входом дискриминатора 8-8.2 связан с выходом триггера 13, счетный вход которого соединен с выходом второго делителя 9. Третий вход 8.3 дискриминатора 8 подключен к выходу второго делителя 9 частоты, первый вход которого соединен через блок задания 10 с выходом генератора 3. К информационному входу триггера 13 подключена шина управления 14. Выходы восьмиразрядного регистра 11 соединены с адресными входами ПЗУ 12 с номерами 4-11, а первый - третий адресные входы ПЗУ 12 являются соответствующими входами дискриминатора 8. Восемь выходов ПЗУ 12 соединены с соответствующими информационными входами регистра 11, счетный вход которого связан с четвертым входом дискриминатора 8 - 8.4 и подключен к выходу генератора 3 задающей частоты. К входу силового преобразователя 2 подключен седьмой выход ПЗУ 12, восьмой выход которого связан со вторым входом второго делителя частоты 9.

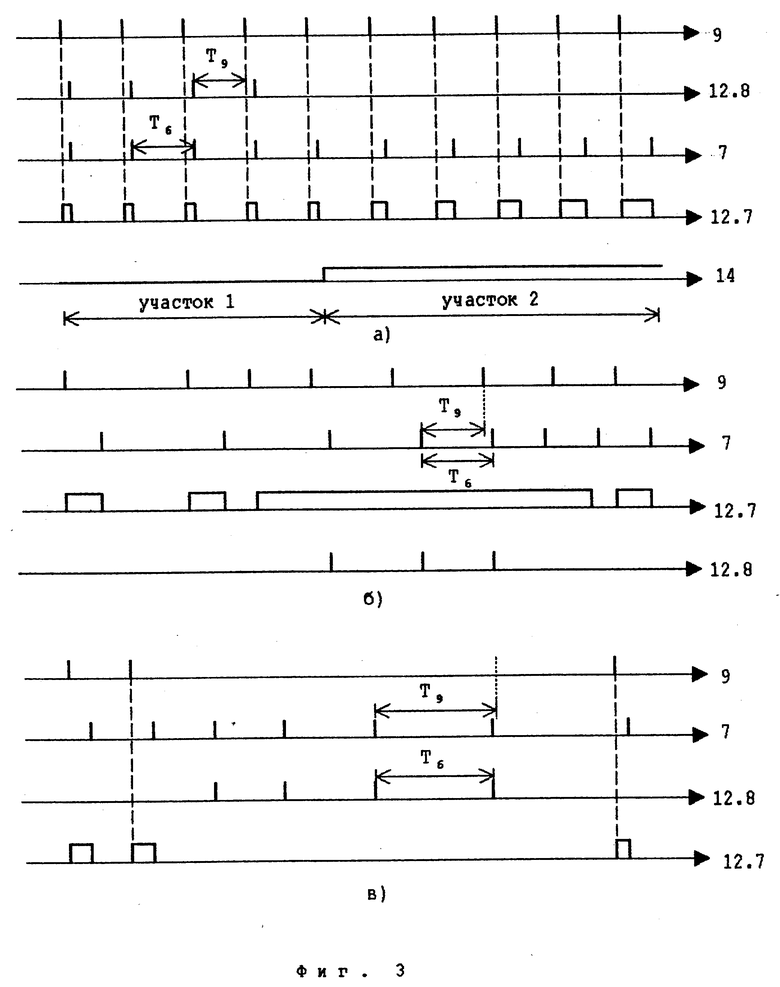

На фиг. 3 приведены временные диаграммы, поясняющие работу электропривода, где цифрами обозначены сигналы на выходах соответствующих элементов устройства.

Устройство работает следующим образом.

Электропривод представляет собой систему фазовой синхронизации, в которой управление скоростью двигателя 1 осуществляется в функции фазового рассогласования частотных сигналов задания, поступающих с делителя 9, и обратной связи с сельсина 6. Выявление величины фазового рассогласования осуществляется посредством частотно-фазового дискриминатора 8, выполненного на базе запоминающего регистра 11 и ПЗУ 12, в которое заносится графотопологическая схема работы дискриминатора. Эти элементы образуют синхронный конечный автомат [4], свободный от обусловленных разбросом параметров элементов ПЗУ "состязаний", появление которых возможно при изменении входных сигналов, что достигается фиксацией состояния ПЗУ 12 в регистре 11 импульсами с генератора 3 задающей частоты, поступающей на вход синхронизации 8.4 дискриминатора 8. На третий вход дискриминатора 8 (8.3) подаются импульсы частоты задания с выхода второго делителя 9. Прямоугольные импульсы с частотой f6 с выхода формирователя прямоугольных импульсов 7 поступают на первый вход фазового дискриминатора 8 - 8.1. Весь объем памяти ПЗУ 12 разделен на три взаимонезависимых банка данных, решающих следующие задачи.

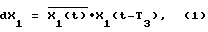

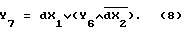

Банк 1 - формирование функции возбуждения dX1 сигнала задания скорости длительности, равной периоду генератора 3 задающей частоты Т3, привязанных к фронту импульсов с выхода второго делителя 9. Для этого используются 1 и 3 разряды данных ПЗУ 12, запрограммируемых таким образом, чтобы обеспечить реализацию разностного уравнения вида

где X1(τ) - значение сигнала на первом входе дискриминатора 8;

Т3 - период сигнала генератора 3.

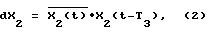

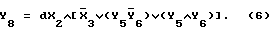

Банк 2 - формирование функции возбуждения dX2-сигнала обратной связи длительности, равной периоду генератора 3 задающей частоты, привязанных к фронту импульсов с выхода сельсина 6. Для этого используются 2 и 4 разряды данных ПЗУ 12, эапрограммируемых таким образом, чтобы обеспечить реализацию разностного уравнения вида

где X2(τ) - значение сигнала на третьем входе дискриминатора 8.

Банк 3 - реализация алгоритма работы частотно-фазового дискриминатора, состояние которого определяется 5 и 6 разрядами ПЗУ 12 Y5 и Y6 соответственно как

Q = col{Y5, Y6}.

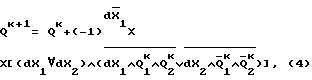

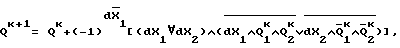

Алгоритм работы дискриминатора, обеспечивающего в режиме управления скоростью логическую защиту от опрокидывания регулирования [3], определяется разностным уравнением нахождения состояния дискриминатора QK=1 вида

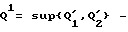

где QI= = sup {Q

Q

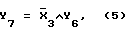

Кроме вышеуказанных банков данных в состав ПЗУ 12 входят комбинационные блоки данных, первый из которых обеспечивает формирование сигнала управления работой силового преобразователя Y7 в соответствии со следующим уравнением:

где X3 - сигнал на входе 8.2 дискриминатора 8, соединенного с выходом триггера 13.

Вторая комбинационная схема формирует сигнал сброса Y8 второго делителя 9 частоты по следующему алгоритму:

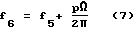

Во всех режимах работы электропривода вращение вала исполнительного двигателя 1 и механически связанного с ним ротора сельсина 6, обмотки возбуждения которого подключены к выходу согласующего элемента 5, приводит к появлению на измерительной обмотке сельсина сигнала с частотой f6, определяемой как

где f5 - частота питающего сигнала сельсина 6, получаемая после деления частоты генератора 3 первым делителем 4;

Ω - угловая скорость вала двигателя 1;

p - число пар полюсов сельсина 3.

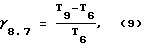

В режиме стабилизации скорости, когда сигналы на шине управления 14 и выходе триггера 13 равны логической "1" на седьмом выходе ПЗУ 12 имеет место широтно-импульсный сигнал, длительность которого γ8.7 определяется разностью фаз частотных сигналов с выходов второго делителя 9 частоты и сельсина 6. При этом каждый импульс с делителя 9 переводит дискриминатор 8 в состояние, для которого Q=2, что приводит к появлению сигнала логической "1" на выходе Y7 и обеспечивает подачу напряжения на двигатель 1. Импульс с сельсина 6 переводит дискриминатор 8 в состояние, для которого Q=1, что соответствует логическому "0" на выходе Y7 и снятию напряжения с двигателя 1. Длительность широтно-импульсного сигнала на выходе дискриминатора 8, как показано в [3], пропорциональна интегралу разности действительного и заданного значения скорости, что обеспечивает электроприводу высокую точность ее стабилизации.

В режиме блокировки силового преобразователя, когда сигнал на шине управления 14 равен логическому "0", каждый импульс сигнала сельсина 6, согласно (6), формирует сигнал сброса второго делителя 9. Дискриминатор 8 переключается в режим, алгоритм которого представляется разностным уравнением вида

Относительная длительность выходного сигнала дискриминатора 8 - γ8.7 определяется как

где Т6, T7 - периоды частот f6, f7 соответственно.

Так как в момент пуска f6=f7, получаем

или с учетом (7)

При этом согласно (5) сигнал управления двигателем 1 равен логическому "0", то есть напряжение на двигатель не подается.

При появлении сигнала логической "1" на шине управления 14 и выходе триггера 13 дискриминатор 8 переходит в режим фазового сравнения входных частотных сигналов (фиг. За участок 2). На двигатель 1, согласно (11), подается напряжение, средняя величина которого пропорциональна заданному значению скорости. Так же, как и в прототипе это обеспечивает малую длительность переходных процессов, особенно при пуске на минимальные скорости двигателя 1, однако в предлагаемом устройстве аппаратные затраты на реализацию такого режима работы электропривода много меньше, чем в известном устройстве.

В случае увеличения частоты задания с выхода второго делителя 9 при нарушении последовательности чередования импульсов частот f6 и f9, за один период T6 приходит более одного импульса f9. При этом согласно алгоритму работы дискриминатора 8 в момент появления фронта f6 формируется импульс сброса делителя 9 (фиг 36). При этом на выходе Y7 ПЗУ 12 все время присутствует сигнал логической "1", обеспечивающий максимальный темп разгона двигателя 1. Дискриминатор 8 осуществляет сравнение разности периодов частот входных сигналов до тех пор, пока выполняется условие

T9 < T6

При невыполнении условия (12) за один период Т9 приходят два импульса с сельсина 6, последний из которых уже не приводит к появлению импульса сброса делителя 9, так как согласно (4) состояние дискриминатора в момент его появления Q= 2. В то же время этот импульс приводит к появлению сигнала логического "0" на выходе Y7 ПЗУ 12, который остается постоянным до момента появления импульса с делителя 9. Дискриминатор 8 переходит в режим фазового сравнения входных сигналов. Так как это происходит при равенстве периодов частот f6 и f9, то есть при скорости двигателя, равной заданному значению, то величина динамической ошибки при регулировании скорости по сравнению с прототипом уменьшается.

При уменьшении скорости двигателя 1 (увеличении периода частоты f9) при последовательном появлении за время периода Т9 двух импульсов частоты обратной связи второй импульс этой частоты приводит, согласно (6), к появлению сигнала сброса второго делителя 9, то есть начало счета этим делителем синхронизируется импульсами с сельсина 6 (фиг 3в) Несмотря на то, что после каждого обнуления делителя 9 частоты ему разрешается счет импульсов, на выходе делителя 9 импульсы отсутствуют, так как скорость двигателя 1 еще не достигла нового значения, соответствующего периоду Т9. При этом выходной сигнал логического "0" дискриминатора 8 не изменяется.

При достижении двигателем 1 скорости, соответствующей периоду Т9, появляется импульс на выходе делителя 9, который приводит к возникновению логической "1" на выходе дискриминатора 8, что соответствует подаче напряжения на двигатель 1. Синхронизация импульсов частоты задания f9 импульсами с выхода сельсина обеспечивает малую длительность сигнала управления двигателем 1 в момент перехода в режим синхронизации скорости. Благодаря этому, по сравнению с прототипом, значительно уменьшается величина перерегулирования скорости. Как показали эксперименты, величина перерегулирования при переходе с номинальной скорости на (0,02-0,01) номинальной не превышает (3-5)%, что существенно меньше, чем у прототипа.

Благодаря синхронизации начала счета второго делителя 9 частоты в процессе изменения скорости двигателя, переход в установившийся режим работы происходит при строго определенном фазовом положении импульсов задания и обратной связи. Это обеспечивает улучшение качества регулирования при изменении скорости, а качество регулирования в режимах пуска по сравнению с прототипом не ухудшается. Реализация частотно-фазового дискриминатора на базе постоянного запоминающего устройства уменьшает затраты электронных компонент на изготовление устройства.

Уровень угловой скорости не зависит от напряжения питающей сети и колебаний температуры, а определяется только нестабильностью генератора 3 задающей частоты, которая при использовании кварцевых резонаторов не превышает 10-5%.

Источники информации, принятые во внимание при составлении заявки

1. Авт. cв. СССР 957400, кл. H 02 P 5/06, 1981.

2. Aвт. св. СССР 1786630, кл. H 02 P 5/06, 1993.

3. Трахтенберг P. M. Импульсные астатические системы электропривода с дискретным управлением. - М.: Энергоиздат, 1982.

4. Пухальский Г. И. , Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах. - М.: Радио и связь, 1990.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОПРИВОД | 1999 |

|

RU2161365C1 |

| ЭЛЕКТРОПРИВОД | 1996 |

|

RU2127940C1 |

| ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА | 1996 |

|

RU2138903C1 |

| Электропривод постоянного тока | 1991 |

|

SU1786630A1 |

| ЭЛЕКТРОПРИВОД | 2003 |

|

RU2260897C2 |

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2006 |

|

RU2310971C1 |

| Электропривод постоянного тока | 1985 |

|

SU1267575A1 |

| ЭЛЕКТРОПРИВОД | 2005 |

|

RU2302073C1 |

| ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА | 2003 |

|

RU2258297C2 |

| Электропривод постоянного тока | 1991 |

|

SU1775833A1 |

Изобретение относится к электротехнике, а именно к системам стабилизации угловой скорости, построенным на принципе контура фазовой синхронизации, в которых в качестве датчика обратной связи используется сельсин или многополюсный синусно-косинусный вращающийся трансформатор. Изобретение решает задачу расширения функциональных возможностей электропривода при одновременном снижении затрат компонент на изготовление устройства. Для достижения поставленной цели частотно-фазовый дискриминатор в предлагаемом устройстве выполнен на базе регистра и постоянного запоминающего устройства и используются новые взаимосвязи между известными элементами. 3 ил.

Электропривод, содержащий последовательно включенные генератор задающей частоты, первый делитель, согласующий элемент и сельсин, установленный на валу двигателя, подключенного к выходу силового преобразователя, причем измерительная обмотка сельсина через формирователь прямоугольных импульсов соединена с первым входом частотно-фазового дискриминатора, третий вход которого связан с первым выходом триггера и выходом второго делителя, первый вход которого через блок задания соединен с выходом генератора задающей частоты, а шина управления подключена ко второму входу триггера, выход которого соединен со вторым входом частотно-фазового дискриминатора, выход которого подключен к входу силового преобразователя, отличающийся тем, что частотно-фазовый дискриминатор с логической защитой от опрокидывания регулирования состоит из регистра и постоянного запоминающего устройства (ПЗУ) и реализует алгоритм переключения вида

где dx1 и dx2 - функции возбуждения первого и второго входов дискриминатора; состояние дискриминатора до (I = K) и после (I = K + I) появления импульсов на его первом или третьем входах;

состояние дискриминатора до (I = K) и после (I = K + I) появления импульсов на его первом или третьем входах;

Q

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Устройство для регулирования скорости электродвигателя постоянного тока | 1981 |

|

SU957400A1 |

| Стабилизированный электропривод | 1989 |

|

SU1624649A1 |

| Электропривод постоянного тока | 1981 |

|

SU989724A1 |

| Световое перо | 1982 |

|

SU1084840A1 |

Авторы

Даты

1999-05-20—Публикация

1997-07-02—Подача