Изобретение относится к области радиотехники, а именно к области диагностики технического состояния аппаратуры цифровых систем передачи, и, в частности, может использоваться для определения вида технического состояния аппаратуры цифровых систем передачи с локализацией поиска различных дефектов.

Известно устройство диагностики состояния аппаратуры цифровых систем передачи, состоящее из передающего и приемного трактов диагностируемой аппаратуры, каждый из которых включает в себя блоки преобразования сигналов, такие как кодер передающего тракта, модулятор передающего тракта, преобразователь частоты передающего тракта, усилитель мощности передающего тракта, блок входных цепей и усилитель высокой частоты приемного тракта, преобразователь частоты приемного тракта, демодулятор приемного тракта, декодер приемного тракта, генератора псевдослучайной последовательности, линии задержки, блока регистрации ошибок, блока подсчета ошибок, блока коммутации соединений, блока управляющих сигналов, генератора шума и аттенюатора [1].

Данное устройство не позволяет идентифицировать кратные отказы, так как оценка состояния диагностируемой аппаратуры цифровых систем передачи осуществляется только по одному параметру - коэффициенту ошибок, который не несет в себе информации о характере и кратности отказа, а свидетельствует только о наличии неисправности, что, в свою очередь, увеличивает время локализации неисправных элементов. Его надежность относительно невысока из-за необходимости введения между соответствующими блоками преобразования сигналов передающего и приемного трактов диагностируемой аппаратуры управляемых электронных ключей, низкой достоверности и больших затрат времени диагностирования. Наиболее близким по технической сущности (прототипом) является устройство диагностики состояния аппаратуры цифровых систем передачи, содержащее передающий и приемный тракты диагностируемой аппаратуры, которые включают блоки преобразования сигналов, генератор псевдослучайной последовательности, блоки управления, анализа, памяти, сравнения и отображения состояния, аттенюатор и генератор шума, выход которого подключен к выходу аттенюатора [2].

Выход генератора псевдослучайной последовательности подключен к входу передающего тракта диагностируемой аппаратуры цифровых систем передачи, выход которого через аттенюатор подключен к входу приемного тракта диагностируемой аппаратуры. Блок преобразования сигналов передающего тракта содержит последовательно соединенные кодер, модулятор, преобразователь частоты и усилитель мощности, блок преобразования сигналов приемного тракта содержит последовательно соединенные усилитель высокой частоты, преобразователь частоты, демодулятор и декодер, при этом вход передающего тракта является одновременно входом кодера, а выход передающего тракта является одновременно выходом усилителя мощности, вход приемного тракта является одновременно входом усилителя высокой частоты, а выходы кодера, модулятора, преобразователя частоты передающего тракта, усилителя мощности, усилителя высокой частоты, преобразователя частоты приемного тракта, демодулятора и декодера соединены с информационными входами блока анализа. К информационным входам блока памяти подключены информационные выходы блоков анализа, определения параметров и сравнения, а его информационный выход подключен к информационным входам блоков определения параметров, сравнения и отображения состояния. При этом управляющие входы генератора псевдослучайной последовательности, блоков анализа, определения параметров, памяти, сравнения и отображения состояния подключены к соответствующим выходам блока управления.

При такой схеме построения устройство-прототип позволяет обнаружить перемеживающиеся одиночные и кратные отказы.

К недостаткам устройства-прототипа относятся низкая достоверность определения вида технического состояния и большие затраты времени диагностирования.

Целью заявляемого изобретения является разработка устройства, обеспечивающего более широкие возможности диагностирования цифровых систем, позволяющего повысить достоверность измерений и сократить время диагностирования.

Поставленная цель достигается тем, что в известном устройстве-прототипе диагностики состояния аппаратуры цифровых систем передачи дополнительно введен блок определения числа N сегментов, информационный вход которого подключен к блоку определения параметров, а информационные выходы подключены к блокам отображения и управления.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественным всем признакам заявленного устройства для диагностирования цифровых систем, отсутствуют, поэтому изобретение соответствует условию патентоспособности "Новизна".

Результаты поиска известных решений в данной и смежной областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками каждого заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "Изобретательский уровень".

Заявленный объект изобретения поясняется чертежами, на которых показаны:

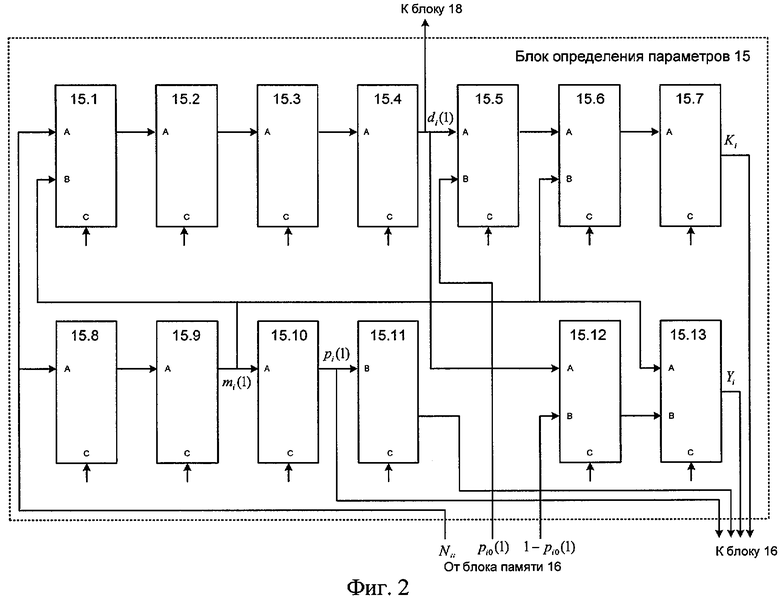

на Фиг.1 - структурная схема устройства диагностирования цифровых систем передачи;

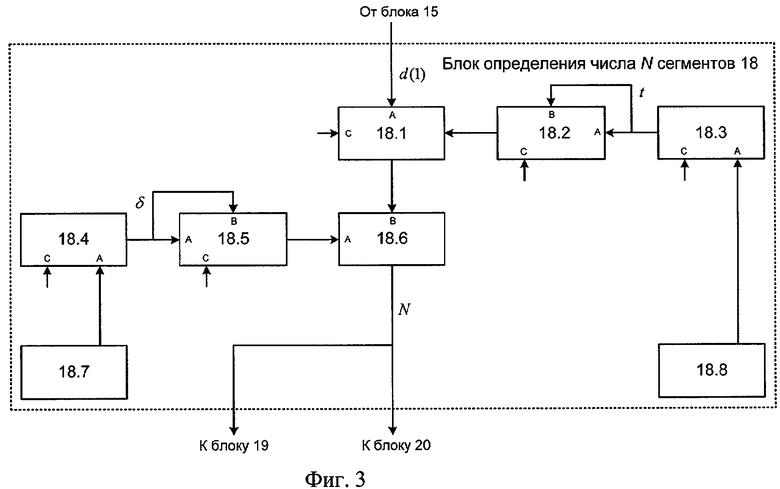

на Фиг.2 - структурная схема блока определения параметров;

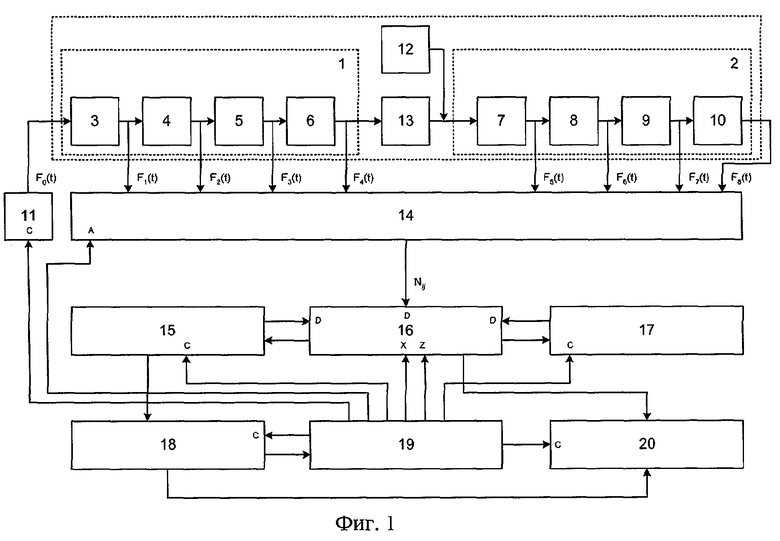

на Фиг.3 - структурная схема блока определения числа N сегментов.

Устройство диагностирования цифровых систем передачи, показанное на Фиг.1, состоит из передающего 1 и приемного 2 трактов, которые содержат блоки преобразования сигналов, такие как кодер 3, модулятор 4, преобразователь частоты 5, усилитель мощности 6 и усилитель высокой частоты 7, преобразователь частоты 8, демодулятор 9, декодер 10 соответственно, генератора псевдослучайной последовательности 11, генератора шума 12, аттенюатора 13, блока анализа 14, блока определения параметров 15, блока памяти 16, блока сравнения 17, блока определения числа N сегментов 18, блока управления 19, блока отображения состояния 20. Выход генератора псевдослучайной последовательности 11 подключен к входу передающего тракта 1 диагностируемой аппаратуры, выход которого через аттенюатор 13 подключен к входу приемного тракта 2 цифровых систем передачи, причем выход генератора шума 12 соединен с выходом аттенюатора 13.

Выходы блоков преобразования сигналов 3, 4, 5, 6, 7, 8, 9, 10 передающего и приемного трактов диагностируемой аппаратуры цифровых систем передачи подключены к информационным входам блока анализа 14, информационный выход которого подключен к одному из информационных входов блока памяти 16, а к остальным информационным входам подключены информационные выходы блоков определения параметров 15 и сравнения 17. Информационные выходы блока памяти 16 подключены к информационным входам блоков определения параметров 15, сравнения 17 и отображения состояния 20. Причем управляющие выходы блока управления 19 подключены к соответствующим управляющим входам генератора псевдослучайной последовательности 11, блоков анализа 14, определения параметров 15, памяти 16, сравнения 17, отображения состояния 20 и определения числа N сегментов 18. Информационные выходы блока определения числа N сегментов 18 подключены к соответствующим информационным входам блока управления 19 и блока отображения состояния 20, а информационный вход подключен к выходу блока определения параметров 15.

Генератор псевдослучайной последовательности, генератор шума, аттенюатор, блоки управления, анализа, памяти, сравнения, отображения состояния аналогичны соответствующим блокам из [2].

Генератор псевдослучайной последовательности 11 предназначен для генерирования тестовой псевдослучайной последовательности с параметрами Z и N.

Генератор шума 12 предназначен для вырабатывания шумовых радиотехнических сигналов для обеспечения требуемого соотношения сигнал/шум на входе приемного тракта диагностируемой аппаратуры цифровых систем передачи.

Аттенюатор 13 предназначен для уменьшения уровня мощности, поступающего на вход приемного тракта сигнала псевдослучайной последовательности.

Блок анализа 14 предназначен для выделения переданной псевдослучайной последовательности на выходах контролируемых блоков преобразования сигналов передающего и приемного трактов диагностируемой аппаратуры цифровых систем передачи: кодера 3, модулятора 4, преобразователя частоты 5, усилителя мощности 6, усилителя высокой частоты 7, преобразователя частоты 8, демодулятора 9, декодера 10.

Блок определения параметров 15 предназначен для определения значений статистических параметров выделенных псевдослучайных последовательностей: математического ожидания m(1), дисперсии d(1), вероятности появления единичного символа р(1), а также значений параметров усечения Y и К. Его структурная схема может быть представлена в нескольких вариантах. В частности, схема блока определения параметров 15, представленная на Фиг.2, состоит из сумматоров 15.3, 15.6, 15.8, умножителя 15.2, делителей 15.4, 15.5, 15.7, 15.9, 15.10, 15.12, вычитателей 15.1, 15.11, 15.13.

А-входы вычитателя 15.1 и сумматора 15.8 и В-входы делителей 15.5 и 15.12 подключены к выходу блока памяти 16. Выход вычитателя 15.1 подключен к А-входу перемножителя 15.2, выход которого подключен к А-входу сумматора 15.3. А-вход управляемого делителя частоты импульсов на N 15.4 подключен к выходу сумматора 15.3, а его выход подключен к А-входам делителей 15.5 и 15.12 и к A-входу умножителя 18.1 блока определения числа N сегментов. Выход делителя 15.5 подключен к А-входу сумматора 15.6, выход которого подключен к А-входу делителя на Z 15.7. Выход сумматора 15.8 подключен к А-входу управляемого делителя частоты импульсов на N 15.9, выход которого подключен к В-входам вычитателя 15.1, сумматора 15.6 и к А-входам вычитателя 15.13, делителя на Z 15.10, выход которого подключен к В-входу вычитателя 15.11. Выход делителя 15.12 подключен к В-входу вычитателя 15.13. Выходы делителей на Z 15.7, 15.10, вычитателей 15.11 и 15.13 подключены к информационному входу блока памяти 16.

Сумматоры 15.3, 15.6, 15.8 предназначены для суммирования чисел, представленных в двоичном коде.

Вычитатели 15.1, 15.11, 15.13 предназначены для получения значения разности чисел, представленных в двоичном коде.

Умножитель 15.2 предназначен для выполнения операции умножения чисел, представленных в двоичном коде.

Делители 15.4, 15.5, 15.7, 15.9, 15.10 и 15.12 предназначены для выполнения операции деления числа, представленного в двоичном коде, на известную константу или переменное число, также представленное в двоичном коде.

Схемы сумматоров 15.3, 15.6 и 15.8, вычитателей 15.1, 15.11, 15.13 известны [3] и могут быть реализованы, например, на микросхеме К155ИП4 [4].

Схема умножителя 15.2 известна [3] и может быть реализована на микросхеме К155ИП4 [4].

Схемы делителей 15.5, 15.7, 15.10 и 15.12 известны [5] и могут быть реализованы на микросхемах К155ИЕ8, К155ИЕ2 [6]. Схемы делителей 15.4, 15.9 описаны в изобретении Збинякова А.Н. "Управляемый делитель частоты импульсов" №2175167, МКИ Н03К 23/68, опубликованном 20.10.2001 г., бюллетень №29.

Блок памяти 16 предназначен для записи значений p(1), р0(1), 1-р0(1), Y, Y0, К, К0 и L, хранения их и выдачи требуемых значений в блок определения параметров 15, блок сравнения 17 и блок отображения состояния 20.

Блок сравнения 17 предназначен для сравнения измеренных значений вероятности появления единичных символов p(1), параметров усечения Y и К с известными значениями р0(1), Y0 и К0. На основе этого сравнения вычисляется значения кратности отказов L и принимается решения о характере неисправности.

Блок определения числа N сегментов 18 предназначен для определения числа N раз подаваемых на вход диагностируемой аппаратуры цифровой системы передачи Z-разрядных сегментов псевдослучайной последовательности с заданной точностью. Структурная схема блока определения числа N сегментов 18, представленная на Фиг.3, состоит из входных наборных панелей 18.7 и 18.8, шифраторов 18.3 и 18.4, умножителей 18.1, 18.2 и 18.5, делителя 18.6. Входные наборные панели 18.7 и 18.8 подключены соответственно к входам шифраторов 18.4 и 18.3, выходы которых подключены к входам умножителей 18.5 и 18.2 соответственно, выходы которых подключены к входам делителя 18.6 и умножителя 18.1 соответственно, на вход которого поступает значение дисперсии d(1) выделенных псевдослучайных последовательностей с выхода делителя 15.4 блока определения параметров 15. Выход умножителя 18.1 подключен к входу делителя 18.6, выход которого подключен к входам блока отображения 20 и блока управления 19.

Умножители 18.1, 18.2 и 18.5 предназначены для выполнения операции умножения чисел, представленных в двоичном коде.

Шифраторы 18.3 и 18.4 предназначены для перевода десятичных чисел в двоичные.

Делитель 18.6 предназначен для выполнения операции деления чисел, представленных в двоичном коде.

Входные наборные панели 18.7 и 18.8 предназначены для ввода информации, представленной в десятичной системе счисления.

Схемы умножителей 18.1, 18.2 и 18.5 известны [3] и могут быть реализованы на микросхеме К155ИП4 [4].

Схемы шифраторов 18.3 и 18.4 известны [3] и могут быть реализованы на микросхеме КР1564 ИВ3 [4].

Схема делителя 18.6 известна [5] и может быть реализована на микросхемах К155ИЕ8, К155ИЕ2 [6].

Блок управления 19 предназначен для выработки управляющих сигналов с целью реализации требуемого алгоритма преобразования сигнала.

Устройство отображения состояния 20 предназначено для индикации технического состояния диагностируемой аппаратуры цифровых систем передачи.

Заявленное устройство диагностирования цифровых систем передачи работает следующим образом.

На первом этапе производится определение значений вероятности появления единичных символов рi0(1) и параметров усечения Yi0 и Кi0 при работоспособном состоянии диагностируемой аппаратуры цифровых систем передачи и запоминание этих значений.

С поступлением управляющего сигнала из блока управления 19 "Разрешение передачи" генератор псевдослучайной последовательности 11 вырабатывает псевдослучайную последовательность F0(t), которая поступает на вход кодера 3 передающего тракта 1, при этом передача Z-разрядных сегментов псевдослучайной последовательности осуществляется N=10 раз. Значение N выбирается исходя из требований метрологической точности измерений математического ожидания и дисперсии числа единичных символов в Z-разрядных сегментах тестовой последовательности [7]. Для обеспечения требуемой точности N должно быть не менее 10.

Переданная псевдослучайная последовательность F0(t) подвергается ряду стандартных преобразований в кодере 3, модуляторе 4, преобразователе частоты 5 и усилителе мощности 6 передающего тракта 1, после чего ослабляется в аттенюаторе 13 и смешивается с сигналом шума, поступающем с выхода генератора шума 12. В усилителе высокой частоты 7, преобразователе частоты 8, демодуляторе 9 и декодере 10 приемного тракта 2 производятся обратные преобразования переданной псевдослучайной последовательности.

На выходе каждого контролируемого блока диагностируемой аппаратуры цифровых систем передачи производится выделение преобразованной псевдослучайной последовательности. Выделенные псевдослучайные последовательности F1(t), F2(t), F3(t), F4(t), F5(t), F6(t), F7(t), F8(t) поступают на соответствующие информационные входы блока анализа 14.

Последовательности сигналов, аналоговой формы с выходов модулятора 4, преобразователя частоты 5, усилителя мощности 6, усилителя высокой частоты 7 и преобразователя частоты 8 подаются на информационные входы D соответствующих аналого-цифровых преобразователей 14.1-14.5, где они приводятся к цифровому виду [2].

Псевдослучайные последовательности импульсов с выходов кодера 3, аналого-цифровых преобразователей 14.1-14.5, демодулятора 9 и декодера 10 подаются на соответствующие информационные D-входы счетчиков единичных символов (счетчиков "1") 14.6-14.13. По управляющим сигналам "Загрузка", поступающим на установочные С-входы счетчиков "1" 14.6-14.13, начинается подсчет числа единичных символов ("1") Nij(1) в каждом j-м Z-разрядном сегменте в каждой i-й выделенной псевдослучайной последовательности.

После поступления каждого Z-го символа сегмента в каждой i-й псевдослучайной последовательности производится считывание значений счетчиков "1" 14.6-14.13 путем подачи управляющих сигналов "Код адреса" на А-вход мультиплексора 14 и Х-вход блока памяти 16, при наличии сигнала "Запись" на входе выбора режима Z блока памяти 16. Значения чисел "1" Nij(1), представленных в двоичном коде, с выходов счетчиков "1" 14.6-14.13 поступают на информационные X1-X8-входы мультиплексора 14.14 и в соответствии с кодовой комбинацией на адресном А-входе, вырабатываемой блоком управления 19, поочередно коммутируются на Y-выход мультиплексора 14.14 [2].

С выхода мультиплексора 14.14 Nij(1) поступает на информационный D-вход блока памяти 16 и в соответствии с кодовой комбинацией на адресном Х-входе и управляющем Z-входе производится запись значений Nij(1) в соответствующие ячейки блока памяти 16 в следующей последовательности:

N11(1), N21(1), ..., Ni1(1), ..., NR1(1);

N12(1), N22(1), ..., Ni2(1), ..., NR2(1);

N1j(1), N2j(1), ..., Nij(1), ..., NRj(1);

N1N(1), N2N(1), ..., NiN(1), ..., NRN(1),

после чего происходит обнуление счетчиков "1" по сигналу "Очистка" на С-входах счетчиков 14.6-14.13.

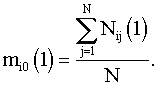

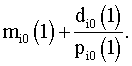

После занесения в блок памяти 16 значений всех чисел "1" Nij(1) в блоке определения параметров производится вычисление значений математического ожидания mi0(1), дисперсии di0(1) числа "1" в Z-разрядном сегменте и вероятности появления "1" рi0(1) в j-й позиции Z-разрядного сегмента и по результатам вычисления mi0(1), di0(1) и pi0(1) определяют значения параметров усечения Yi0 и Кi0.

С выхода блока памяти 16 в соответствии с сигналами "Код адреса" на адресном Х-входе и "Считывание" на управляющем Z-входе, вырабатываемыми блоком управления 19, производится последовательное считывание значения Nij(1), принадлежащей i-й последовательности, и подача этих значений на А-входы вычитателя 15.1 и сумматора 15.8 блока определения параметров 15, показанного на Фиг.2, при разрешающем сигнале "Загрузка" на С-входе. В сумматоре 15.8 производится суммирование всех j-x значений Nij(1) i-й последовательности, то есть производится вычисление суммы:

Сигнал с выхода сумматора 15.8 подается на А-вход управляемого делителя частоты импульсов 15.9 при разрешающем сигнале "Загрузка", вырабатываемом блоком управления 19, на управляющем С-входе. В делителе выполняется операция деления на число N, то есть производится вычисление среднего значения

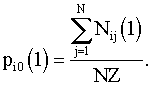

Среднее значение mi0(1) с выхода управляемого делителя частоты импульсов 15.9 подается на А-вход делителя 15.10, В-вход вычитателя 15.1, В-вход сумматора 15.6 и А-вход вычитателя 15.13. При разрешающем сигнале "Загрузка", вырабатываемом блоком управления 19, на управляющем С-входе, в делителе 15.10 выполняется операция деления на число Z, то есть производится вычисление по формуле:

После чего, при наличии сигнала "Считывание" на С-входе, производится подача ее на В-вход вычитателя 15.11 и информационный D-вход блока памяти 16, в котором, в соответствии с сигналами "Код адреса" на адресном Х-входе и "Заись" на управляющем Z-входе, вырабатываемыми блоком управления 19, производится запись значений pi0(1) в соответствующие ячейки памяти. В вычитателе 15.11, на А-входе которого присутствует двоичное значение "1", производится вычисление разности 1-pi0(1), при наличии сигнала "Загрузка" на С-входе.

Значение разности 1-рi0(1) по сигналу "Считывание" на С-входе считывается и подается на информационный D-вход блока памяти 16, в котором в соответствии с сигналами "Код адреса" на адресном входе Х и "Запись" на управляющем Z-входе, вырабатываемыми блоком управления 19, производится запись значений 1-рi0(1) в соответствующие ячейки памяти.

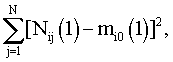

После вычисления среднего значения mi0(1) и подачи его на В-вход вычитателя 15.1 производится вычисление значения дисперсии di0(1). С выхода блока памяти 16 в соответствии с сигналами "Код адреса" на адресном Х-входе и "Считывание" на управляющем Z-входе, вырабатываемыми блоком управления 19, производится последовательное считывание значений Nij(1), принадлежащих i-й последовательности, и подача этих значений на А-вход вычитателя 15.1 при разрешающем сигнале "Загрузка" на С-входе. В вычитателе 15.1 производится вычисление по формуле:

Nij(1)-mi0(1).

Сигнал с выхода вычитателя 15.1 подается на А-вход умножителя 15.2, в котором производится вычисление вида:

[Nij(1)-mi0(1)]2,

результат которого подается на А-вход сумматора 15.3 при разрешающем сигнале "Загрузка" на его С-входе.

После этого производится обнуление вычитателя 15.1 и умножителя 15.2 по сигналу "Очистка" на управляющих С-входах.

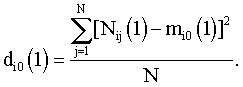

В сумматоре 15.3 производится вычисление суммы:

результат которого подается на А-вход управляемого делителя частоты импульсов 15.4 при разрешающем сигнале "Загрузка" на его С-входе.

В управляемом делителе частоты импульсов 15.4 производится вычисление дисперсии:

После вычисления di0(1) по сигналу "Считывание" на управляющем С-входе производится считывание значения di0(1).

Значение дисперсии di0(1) подается на А-входы делителей 15.5, 15.12 и вход умножителя 18.1 блока определения числа N сегментов 18. На В-вход делителя 15.5, при разрешающем сигнале "Загрузка" на С-входе, с выхода блока памяти 16, в соответствии с сигналами "Код адреса" на адресном Х-входе и "Считывание" на управляющем Z-входе, вырабатываемыми блоком управления 19, подается значение рi0(1). В делителе 15.5 производится вычисление отношения:

результат которого подается на А-вход сумматора 15.6.

В сумматоре 15.6, при разрешающем сигнале "Загрузка" на С-входе, на В-вход которого подано значение mi0(1), производится вычисление:

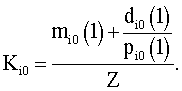

Результат суммирования подается на А-вход делителя на Z 15.7, в котором, при разрешающе сигнале "Загрузка" на С-входе, производится вычисление по формуле:

После вычисления Кi0 по сигналу "Считывание" на управляющем С-входе производится считывание значения Кi0 - подача значения Кi0 на информационный D-вход блока памяти 16, в котором в соответствии с сигналами "Код адреса" на адресном Х-входе и "Запись" на управляющем Z-входе, вырабатываемыми блоком управления 19, производится запись значений Кi0 в соответствующие ячейки памяти.

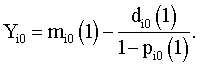

Параллельно с вычислением значения Кi0 производится вычисление значения Yi0. На В-вход делителя 15.12 с выхода блока памяти 16 в соответствии с сигналами "Код адреса" на адресном Х-входе и "Считывание" на управляющем Z-входе, вырабатываемыми блоком управления 19, подается значение разности 1-рi0(1), на А-вход которого подано значение di0(1). В делителе 15.12, при разрешающем сигнале "Загрузка" на С-входе, производится вычисление отношения:

результат которого подается на В-вход вычитателя 15.13. В вычитателе 15.13, при сигнале "Загрузка" на С-входе, на А-вход которого подано значение mi0(1), производится вычисление вида:

После вычисления Yi0 по сигналу "Считывание" на управляющем С-входе производится считывание значения Yi0 и подача значения Yi0 на информационный D-вход блока памяти 16, в котором в соответствии с сигналами "Код адреса" на адресном Х-входе и "Запись" на управляющем Z-входе, вырабатываемыми блоком управления 19, производится запись значений Yi0 в соответствующие ячейки памяти.

Вычисления, производимые в блоке определения параметров 15, производятся R раз и зависят от числа R контролируемых блоков приемного и передающего трактов для каждой i-й последовательности и все результаты вычислений заносятся в блок памяти 16.

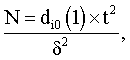

Одновременно с вычислением значений Yi и Кi производится вычисление значения числа N сегментов с заданной точностью и надежностью в блоке определения числа N сегментов 18.

При проведении измерений предварительно задают надежность оценки измерений, например, γ=0.95. Из соотношения 2Ф(t)=0.95 получаем Ф(t)=0.475 и по таблице (приложение 2) находим t=1.96 [8].

На входных панелях 18.7 и 18.8 блока определения числа N сегментов набираются требуемые значения точности измерения δ и параметра t. С выходов входных панелей 18.7 и 18.8 установленные значения точности измерения δ и параметра t в десятичной системе счисления поступают на А-входы шифраторов 18.4 и 18.3 соответственно, где производится преобразование этих сигналов в двоичную систему счисления при наличии сигнала "Загрузка" на С-входах. С выхода шифраторов 18.4 и 18.3 сигналы δ и t поступают на входы умножителей 18.5 и 18.2 соответственно, где производятся вычисления значений δ2 и t2 при разрешающем сигнале "Загрузка" на их С-входах, результаты которых поступают соответственно на А-вход делителя 18.6 и В-вход умножителя 18.1 при поступлении сигнала "Загрузка" на С - входы. В умножителе 18.1 производится вычисление значения di0(1)×t2 и производится считывание его при сигнале "Считывание" на С-входе. Значение di0(1)×t2 подается на В-вход делителя 18.6, где производится вычисление значения

результат которого подается на блоки отображения состояния 20 и управления 19. Из блока управления 19 выдается управляющий сигнал "Разрешение передачи" на генератор псевдослучайной последовательности 11, который вырабатывает псевдослучайную последовательность, при этом передача Z-разрядных сегментов осуществляется N раз. Значение N определяется блоком определения числа N сегментов 18.

На втором этапе, характеризующимся наступлением неработоспособного состояния диагностируемой аппаратуры цифровых систем передачи, производится вычисление значений mi(1), di(1), pi(1) и параметров усечения Yi, Ki, Li.

Вычисление значений mi(1), di(1), pi(1) и параметров усечения Yi, Кi производится по вышеизложенному алгоритму, за исключением некоторых операций:

- после вычисления pi(1) и записи ее значения в блок памяти 16 вычисление 1-рi(1) в вычитателе 15.11 не производится;

- при вычислении значений Yi и Кi в делителях 15.5, 15.12 используются значения pi0(1) и разности 1-рi0(1), вычисленные на первом этапе.

С выхода блока памяти 16 в соответствии с сигналами "Код адреса" на адресном Х-входе и "Считывание" на управляющем Z-входе, вырабатываемыми блоком управления 19, на А и В-входы компараторов 17.2, 17.3 и 17.4 и вычитателей 17.5 и 17.6 блока сравнения 17 подаются значения pi0(1) и pi(1), Yi0 и Yi, Кi0 и Кi соответственно. С G1(A<B), G2(A=B), G3(A>B)-выходов компараторов 17.2-17.4 результаты сравнения А и В, при разрешающих сигналах "Загрузка" на С-входах, подаются на информационные D1-D9-входы шифратора 17.1, при разрешающем сигнале "Загрузка" на его С-входе [2].

Значение кодовой комбинации на выходе шифратора 17.1 считывается по сигналу "Считывание", поступающему на управляющий С-вход, и подается на информационный D-вход блока памяти 16 в соответствии с сигналами "Код адреса" на адресном Х-входе и "Запись" на управляющем Z-входе, вырабатываемыми блоком управления 19. Кодовая комбинация на выходе шифратора 17.4 несет информацию о характере неисправности контролируемого блока преобразования сигналов передающего и приемного трактов диагностируемой аппаратуры цифровых систем передачи и является управляющим сигналом, который поступает на Х-входы выбора режима сумматоров - вычитателей 17.7 и 17.9, делителя 17.10 и на управляющий С-вход электронного коммутатора 17.11.

Вычисление кратности отказов Li производится по одному из трех вариантов [2].

Значение Li с выхода блока памяти 16 подается на вход В электронного коммутатора 17.11, а с его выхода - на вход D блока памяти 16 в соответствии с сигналами "Код адреса" на адресном входе Х и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19.

После этого из блока памяти 16 в соответствии с сигналом "Код адреса" на адресном Х-входе и сигналом "Считывание" на управляющем Z-входе считывается совокупность сигналов, представляющих собой кодовые комбинации, характеризующие техническое состояние (неисправный блок, характер неисправности и кратность отказа) диагностируемой аппаратуры цифровых систем передачи и подается на информационный вход блока отображения состояния 20, в котором, при наличии разрешающего сигнала "Загрузка" на С-входе, происходит дешифрация входных кодовых комбинаций и отображение технического состояния диагностируемой аппаратуры цифровых систем передачи с помощью семисегментных индикаторов.

Введение в устройство-прототип блока определения числа N сегментов в сочетании с управляемым делителем частоты импульсов в блоке определения параметров и новых связей между блоками позволяет значительно сократить время диагностики цифровых систем, повысить достоверность измерений и расширить возможности разработанного устройства.

Источники информации

1. Авторское свидетельство СССР №1734219, заявка 6.08.1992 г., бюллетень №18.

2. Изобретение №2132594 "Способ и устройство диагностики состояния аппаратуры цифровых систем передачи" 6 Н04В 3/46, 17/00, опубликованное 27.06.1999 г., бюллетень №18.

3. Р.Токхейм "Основы цифровой электроники": Пер. с англ. - М.: Мир, 1988, стр.231-232, рис.9.18, стр.236-240, рис.9.26, стр.119-121, рис.5.5.

4. В.А.Батушев, В.Н.Вениаминов и др. "Микросхемы и их применение. Справочное пособие". - М.: Радио и связь, 1983, стр.129-130.

5. B.C.Гутников, В.В.Лопатин и др. "Электронные устройства информационно-измерительной техники. Учебное пособие". - Л.: ЛПИ им. Калинина, 1980 г., стр.44-46, 48-50, рис.21, 24.

6. В.Л.Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987 г., стр.94-97, рис.1.69.

7. Б.А.Севастьянов "Теории вероятностей и математической статистики". - М.: Наука, 1982. - 256 с.

8. В.Е.Гмурман "Теория вероятностей и математическая статистика". - М.: "Высшая школа", 1972. - 368 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ АППАРАТУРЫ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ | 1998 |

|

RU2132594C1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| УСТРОЙСТВО ДИАГНОСТИРОВАНИЯ СОСТОЯНИЯ АППАРАТУРЫ СВЯЗИ | 2005 |

|

RU2289209C1 |

| УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ АППАРАТУРЫ СВЯЗИ | 1997 |

|

RU2124266C1 |

| СИСТЕМА ПЕРЕДАЧИ ДАННЫХ С МНОЖЕСТВЕННЫМ ДОСТУПОМ И ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2003 |

|

RU2240653C1 |

| СИСТЕМА ПЕРЕДАЧИ ЧЕТВЕРИЧНО-КОДИРОВАННЫХ РАДИОСИГНАЛОВ | 2004 |

|

RU2258313C1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2336670C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ДИАГНОСТИРОВАНИЯ ПЕРЕДАЮЩЕГО ТРАКТА КАНАЛА СВЯЗИ | 2020 |

|

RU2746261C1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182358C2 |

| СПОСОБ ДИАГНОСТИРОВАНИЯ И ОБЕСПЕЧЕНИЯ ТЕХНИЧЕСКОЙ ГОТОВНОСТИ ЭЛЕМЕНТОВ СЕТЕЙ СВЯЗИ | 2006 |

|

RU2325031C2 |

Изобретение может быть использовано при определении вида технического состояния аппаратуры цифровых систем передачи с обнаружением и локализацией различных дефектов. Целью изобретения заявленных технических решений является разработка устройства, обладающего более широкими возможностями диагностирования цифровых систем и позволяющего повысить достоверность измерений и сократить время диагностики. Устройство состоит из генератора псевдослучайной последовательности, генератора шума, аттенюатора, блока анализа, блока определения параметров, блока памяти, блока сравнения, блока определения числа N сегментов, блока управления, блока отображения состояния, применяемых для диагностирования передающего и приемного трактов цифровых систем передачи, которые включают в себя кодер, модулятор, преобразователь частоты, усилитель мощности и усилитель высокой частоты, преобразователь частоты, демодулятор, декодер, соответственно. 3 ил.

Устройство диагностирования цифровых систем передачи, содержащее передающий и приемный тракты диагностируемой цифровой системы передачи с блоками преобразования сигналов, генератор псевдослучайной последовательности, подключенный к входу передающего тракта, выход которого через аттенюатор соединен с входом приемного тракта, генератор шума, выходом подключенный к выходу аттенюатора, блоки определения параметров, анализа, сравнения и отображения состояния, блок преобразования сигналов передающего тракта содержит последовательно соединенные кодер, модулятор, преобразователь частоты и усилитель мощности, блок преобразования сигналов приемного тракта содержит последовательно соединенные усилитель высокой частоты, преобразователь частоты, демодулятор и декодер, при этом вход передающего тракта является одновременно входом кодера, а выход передающего тракта является одновременно выходом усилителя мощности, вход приемного тракта является одновременно входом усилителя высокой частоты, а выходы кодера, модулятора, преобразователя частоты передающего тракта, усилителя мощности, усилителя высокой частоты, преобразователя частоты приемного тракта, демодулятора и декодера соединены с информационными входами блока анализа, информационный выход которого подключен к одному из информационных входов блока памяти, а к остальным информационным входам подключены информационные выходы блоков определения параметров и сравнения, информационные выходы блока памяти подключены к информационным входам блоков определения параметров, сравнения и отображения состояния, причем управляющие входы генератора псевдослучайной последовательности, блоков анализа, определения параметров, памяти, сравнения и отображения состояния подключены к соответствующим выходам блока управления, отличающееся тем, что дополнительно введен блок определения числа N сегментов, информационный вход которого подключен к блоку определения параметров, а информационные выходы подключены к блокам отображения состояния.

| СПОСОБ И УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ АППАРАТУРЫ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ | 1998 |

|

RU2132594C1 |

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Экономайзер | 0 |

|

SU94A1 |

| JP 2000295142 A, 20.10.2000 | |||

| US 6269082 A, 31.07.2001. | |||

Авторы

Даты

2007-05-20—Публикация

2005-07-04—Подача