Настоящее изобретение относится к перемежающему устройству или перемежителю для системы мобильной телесвязи с многостанционного доступа с кодовым разделением (МДКР), и в частности к перемежителю в групповом спектре для каналов прямой передачи и пейджинга, предпочтительно применимых к варианту IS-95 МДКР системы телесвязи.

Перемежитель для канала прямой передачи и пейджингового канала в полосе частот, определяемой в соответствии со стандартом IS-95 МДКР, снабжается набором источников данных, отличающихся друг от друга в соответствии с различными скоростями передачи, такими как 14400 байт/сек, 9600 байт/с, 7200 байт/с, 3600 байт/с и 1800 байт/с, а также 4800 байт/с, 2400 байт/с и 1200 байт/с; эти источники данных, однако, обеспечивают некое общее свойство, то есть регулярность. Таким образом, эта регулярность использовалась для перемежителей известного уровня техники так, чтобы быть применимой ко всем типам скоростей передачи в обычном использовании.

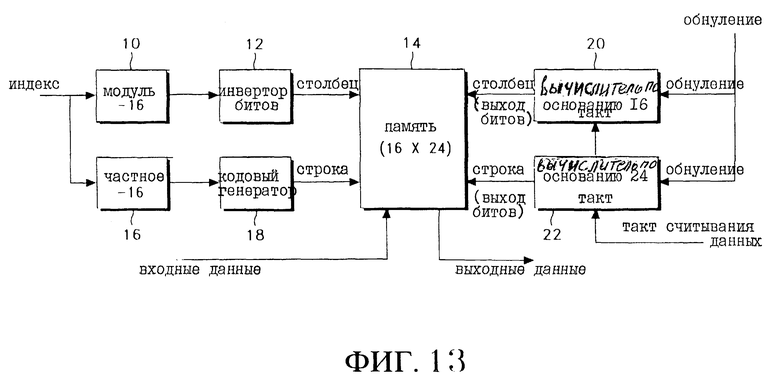

Фиг. 1 показывает примерную таблицу ввода вышеупомянутого перемежителя каналов прямой передачи и пейджинга на скоростях 14400 байт/с, 9600 байт/с, 7200 байт/с, 3600 байт/с и 1800 байт/с. Таблица ввода состоит из 24 рядов и 16 колонок в матрице, фиксируя скорость передачи данных, введенную в таблицу ввода на 9600 байт/с. Поэтому последующий ввод данных на скорости передачи 9600 байт/с выполняется с первой позиции, ряд 1 и колонка 1, матрицы до ее последней позиции, ряд 24, колонка 16, в которой соответствующий индекс присвоен в соответствии с порядком входных данных. Например, индекс 1 представляет первые входные данные, а индекс 2 представляет вторые входные данные. Аналогично в таблице ввода отмечено, что адрес индекса 1 соответствует ряду 1 и колонке 1, а адрес индекса 2 - ряду 2 и колонке 1, адрес индекса 3 - ряду 3 и колонке 1 и адрес индекса 4 - ряду 4 и колонке 1.

Данные, записанные по вышеупомянутым адресам, направляются на перемежитель в соответствии с порядком индексов, в котором перемежитель чередует входные данные, подлежащие записи в память.

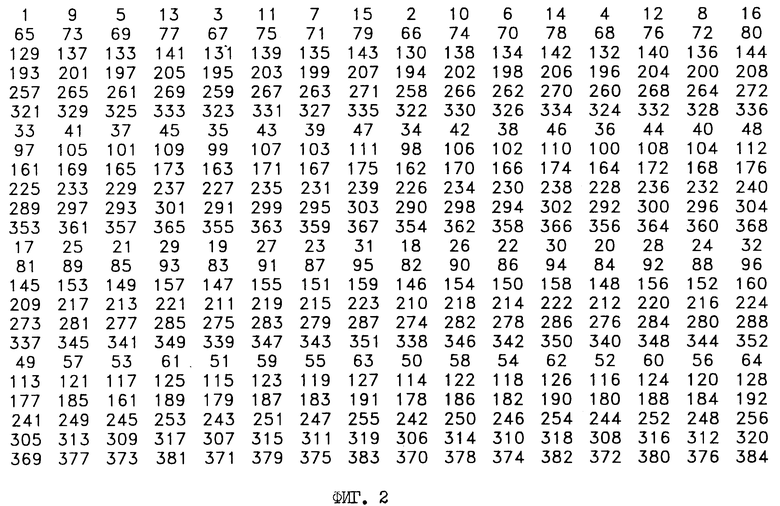

Фиг. 2 показывает примерную таблицу перемежения, записанную в памяти, скоростей 14400 байт/с, 9600 байт/с, 7200 байт/ с, 3600 байт/с и 1800 байт/с для перемежителя каналов прямой передачи и пейджингового каналов. Вышеупомянутая таблица перемежения имеет одинаковую структуру с таблицей ввода по фиг. 1 и содержит 24 строки и 16 столбцов в матричной таблице, устанавливая ее скорость передачи данных на 9600 байт/с. Согласно таблице перемежения, индекс данных размещен так, что индекс 1 расположен в строке 1 и столбце 1, индекс 2 - в строке 2 и столбце 9, а индекс - 3 в строке 1 и столбце 5, и в этом расположении индексирование данных таблицы перемежения проводится дисперсно, а не последовательно.

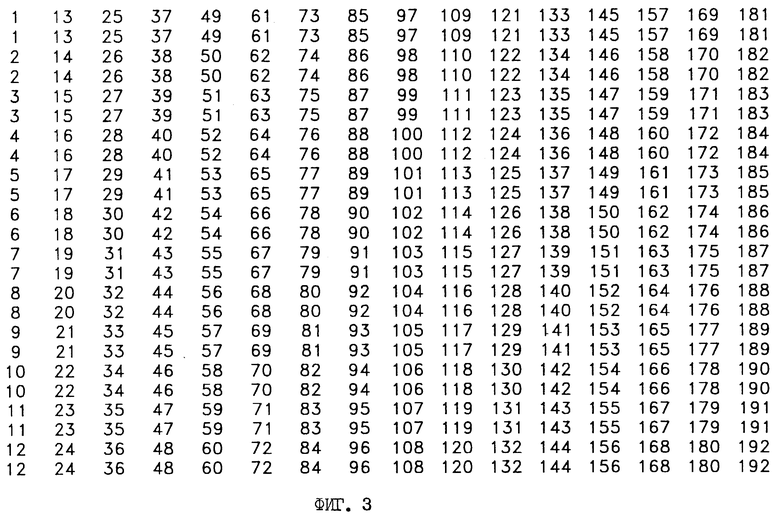

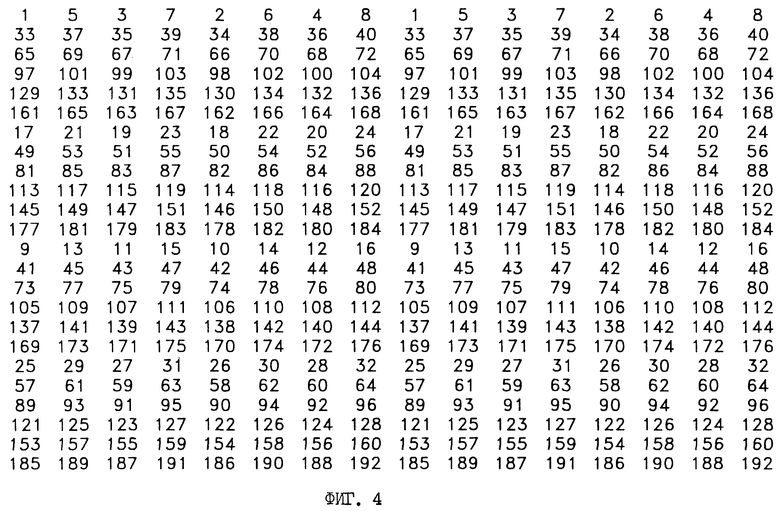

Фиг. 3 показывает примерную таблицу ввода скорости 4800 байт/с для перемежителя каналов прямой передачи и пейджинга, у которого скорость передачи данных в два раза ниже, чем у перемежителя на 9600 байт/с, но который разработан так, чтобы быть применимым для данных со скоростью передачи данных 9600 байт/с. Таким образом, одни данные на 4800 байт/с расположены по двум последовательным адресам в таблице ввода, так что эти два индекса дают один индекс данных. Например, как видно из фиг. 3, индекс первых данных представлен в двух индексах "1". Следовательно, перемежитель производит чередование данных, расположенных в таблице ввода, на скорости передачи данных 9600 байт/с, и в течение этого времени перемежитель раздельно распознает два этих последовательных индекса, представляющих одни данные. Фиг. 4 показывает примерную таблицу перемежения на 4800 байт/с для перемежителя каналов прямой передачи и пейджинга как выход перемежения перемежителя по фиг. 3. Как показано на фиг. 4, два удаленных друг от друга индекса чередуются раздельно. Например, первый индекс 1 чередуется перемежителем в позицию строки 1 и столбца 1, а второй индекс затем чередуется в другую позицию строки 1 и столбца 9.

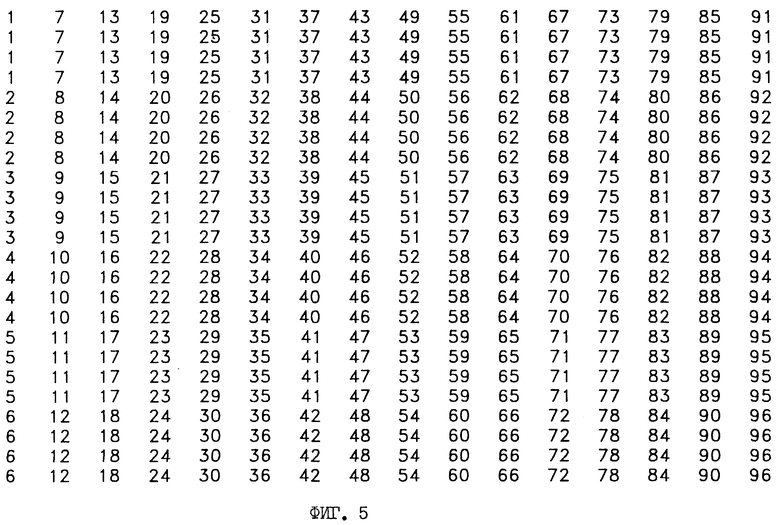

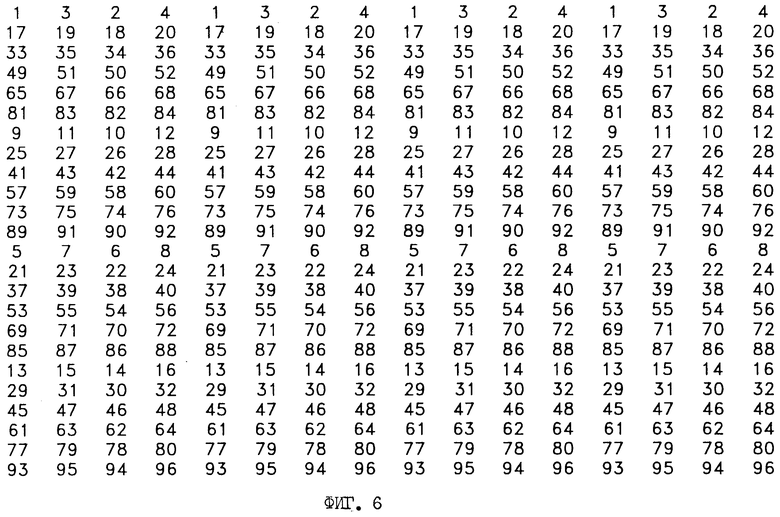

Фиг. 5 показывает примерную таблицу ввода скорости 2400 байт/с для перемежителя каналов прямой передачи и пейджинга, у которого скорость передачи данных в четыре раза ниже, чем у перемежителя на 9600 байт/с, но который разработан так, чтобы быть применимым для данных со скоростью передачи данных 9600 байт/с. Таким образом, одни данные на 2400 байт/с размещены по четырем последовательным адресам в таблице ввода, так что эти четыре последовательных индекса дают один индекс данных. Например, как видно из фиг. 5, индекс первых данных представлен в четырех индексах "1". Следовательно, перемежитель производит чередование данных, расположенных в таблице ввода, на скорости передачи данных 9600 байт/с, и в течение этого времени перемежитель раздельно распознает четыре этих последовательных индекса, представляющих одни данные. Фиг. 6 показывает примерную таблицу перемежения на 2400 байт/с для перемежителя каналов прямой передачи и пейджинга как выход перемежения перемежителя по фиг. 5. Как показано на фиг. 6, четыре удаленных друг от друга индекса чередуются раздельно. Например, первый индекс 1 чередуется в позицию строки 1 и столбца 1, а второй индекс 1 затем чередуется в позицию строки 1 и столбца 9, третий индекс 1 - в позицию строки 1 и столбца 5, а четвертый индекс 1 - в позицию строки 1 и столбца 13 с помощью перемежителя.

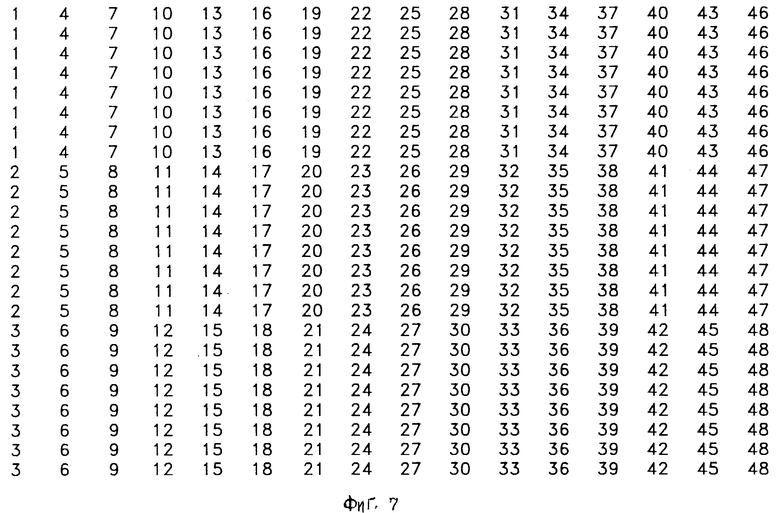

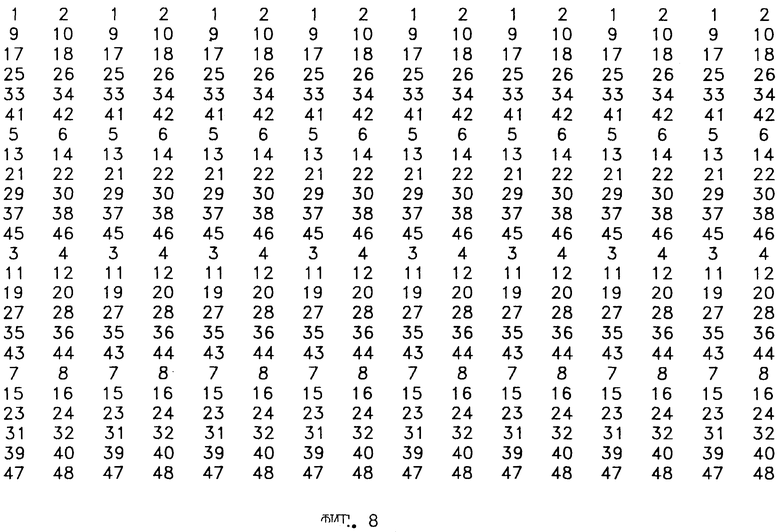

На фиг. 7 показана примерная таблица ввода скорости 1200 байт/с для перемежителя каналов прямой передачи и пейджинга, у которого скорость передачи данных в восемь раз ниже, чем у перемежителя на 9600 байт/с, но который разработан так, чтобы быть применимым для данных со скоростью передачи данных 9600 байт/с. Таким образом, одни данные на 1200 байт/с размещены по восьми последовательным адресам в таблице ввода, так что эти восемь последовательных индексов дают один индекс данных. Следовательно, например, как видно из фиг. 7, индекс первых данных может быть представлен в восьми индексах "1". Следовательно, перемежитель производит чередование данных, расположенных в таблице ввода, на скорости передачи данных 9600 байт/с, и в течение этого времени перемежитель раздельно распознает восемь этих последовательных индексов, представляющих одни данные. Фиг. 8 показывает примерную таблицу перемежения на 1200 байт/с для перемежителя каналов прямой передачи и пейджинга как выход перемежения перемежителя по фиг. 7. Как показано на фиг. 8, восемь удаленных друг от друга индексов чередуются раздельно. Например, первый индекс 1 чередуется в позицию строки 1 и столбца 1, а второй индекс 1 затем чередуется в позицию строки 1 и столбца 9, третий индекс 1 - в позицию строки 1 и столбца 5, четвертый индекс 1 - в позицию строки 1 и столбца 13, пятый индекс 1 - в позицию строки 1 и столбца 3, шестой индекс 1 - в позицию строки 1 столбца 11, седьмой индекс 1 - в позицию строки 1 и столбца 7, а восьмой индекс - 1 в позицию строки 1 и столбца 15 с помощью перемежителя.

Как указано выше, операция перемежения выполняется на фиксированной скорости передачи 9600 байт/с, несмотря на разницу в скоростях передачи данных. Поэтому отмечено, что индекс не вырабатывается в блоке данных, но вырабатывается в блоке данных при 9600 байт/с для всех данных. Если ввод данных, имеющий упомянутые индексы, вводится в перемежитель, способный перемежать на скорости передачи 9600 байт/с, то различные скорости передачи данных могут чередоваться путем использования единственного перемежителя.

Один из перемежителей известного уровня техники использует таблицу преобразования памяти, которая является исходной таблицей, по который каждый индекс входных данных чередуется на свой соответствующий адрес в таблице перемежения. Следовательно, поскольку индекс одних входных данных для перемежения обеспечивается перемежителем, он считывает соответствующий адрес в таблице перемежения, чтобы этим сохранить считанные данные по адресу. Например, если введены данные индекса 1, то позиция строки 1 и столбца 1 таблицы перемежения, соответствующая индексу 1, считывается для того, чтобы этим сохранить данные индекса 1 на той же позиции. Такой тип способа перемежения обычно не требует использования никаких сложных операций, но требует память для хранения в ней такой таблицы преобразования для перемежения.

Более того, большинство из таких существующих перемежителей предпочтительно снабжены памятью общего назначения на 512 байт для таблицы преобразования. Однако, поскольку вышеописанная таблица преобразования обычно требует только 384 байта из 512 - байтов микросхемы памяти, остающиеся 128 байт памяти могут быть бесполезными.

Таким образом, технической задачей настоящего изобретения является обеспечение улучшенного перемежителя в групповом спектре для каналов прямой передачи и пейджинга с уменьшенной емкостью памяти перемежения и более простой конструкцией.

Вышеупомянутая техническая задача достигается в соответствии с принципами настоящего изобретения, включающими в себя полосовой перемежитель, снабженный схемой по модулю 16 для деления индекса на число 16, каковой индекс выбирается из следующих друг за другом индексов от 0 до 383, соответствующих входным данным, и для обеспечения остатка от деления индекса; преобразователь разрядов для преобразования выхода схемы по модулю 16 и определения положения в столбце для записи данных с выполненным чередованием; схема частного по модулю 16 для приема индекса для выработки частного от деления индекса на число 16; кодовый преобразователь, имеющий таблицу строк, по которой частное соответственно сопрягается с позицией в строке, подлежащей записи с выполненным чередованием, для выработки положения в строке, соответствующего частному; вычислитель по основанию 24 для вычисления такта считывания данных и для обеспечения этим вычисленного значения по основанию 24, соответствующего выбранной строке выходных данных для считывания, чтобы выборочно выводить перемеженные записанные данные; вычислитель по основанию 16, принимающий перенос от вычислителя по основанию 24, для обеспечения вычисленного по основанию 16 значения, соответствующего выбранному столбцу выходных данных для считывания; и память с таблицей перемежения, включающей 32 строки и 16 столбцов, входные данные записываются на выбранную позицию в таблице перемежения в соответствии с выходом преобразователя разрядов и с выходом кодового преобразователя, выходные данные являются данными, считанными из позиции, соответствующей выходу вычислителя по основанию 16 и выходу вычислителя по основанию 24.

Более полное понимание этого изобретения и многие его сопутствующие преимущества будут более ясны, равно как и станут более понятными при ссылке на нижеследующее подробное описание, при рассмотрении его совместно с приложенными чертежами, в которых одинаковые ссылочные символы означают одинаковые или сходные компоненты.

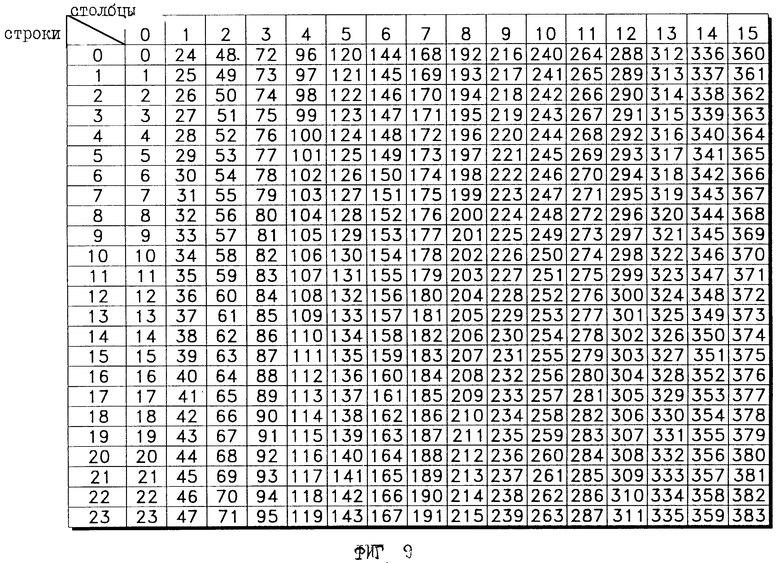

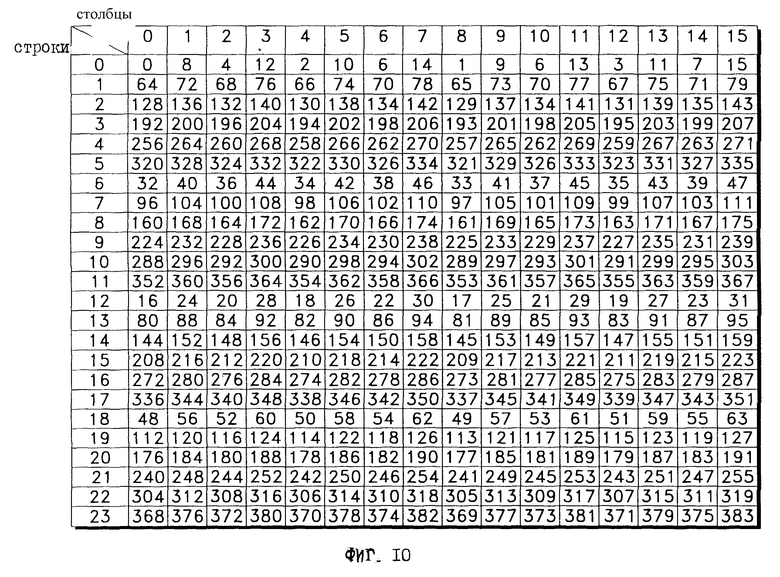

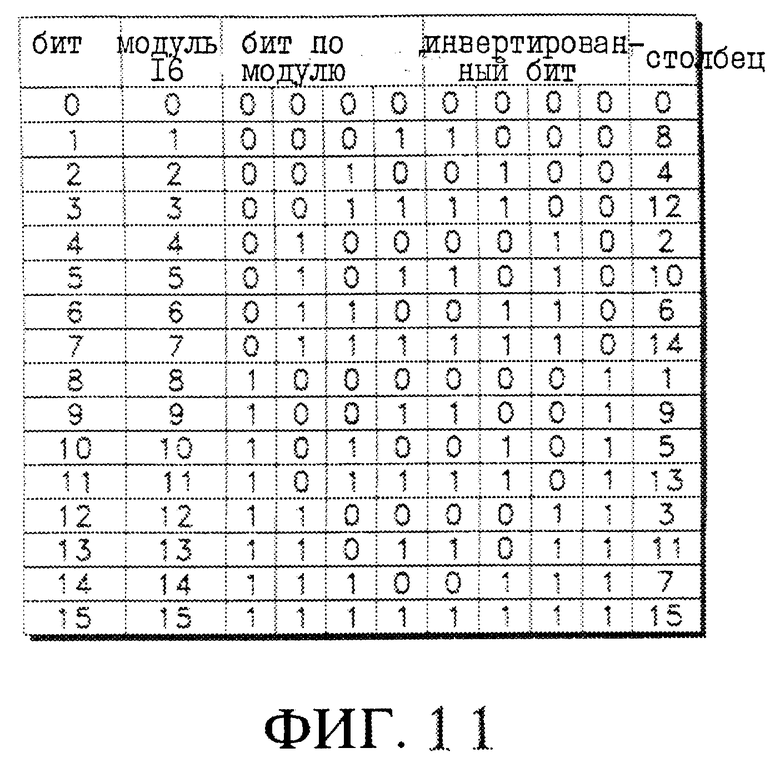

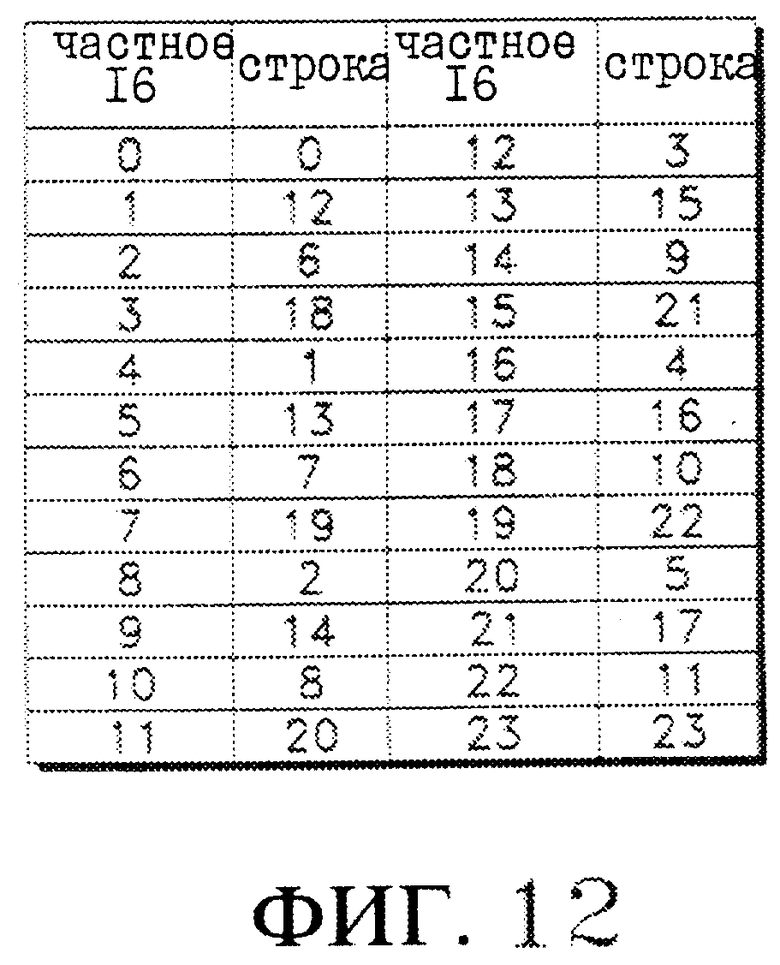

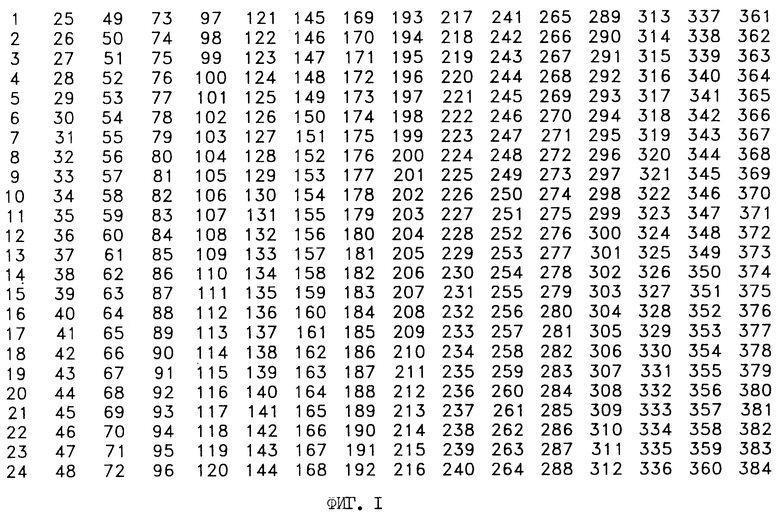

Фиг. 1 показывает примерную таблицу ввода для перемежителя каналов прямой передачи и пейджинга на скоростях 14400 байт/с, 9600 байт/с, 7200 байт/с, 3600 байт/с и 1800 байт/с; фиг. 2 показывает примерную таблицу перемежения для перемежителя каналов прямой передачи и пейджинга на скоростях 14400 байт/с, 9600 байт/с, 7200 байт/с, 3600 байт/с и 1800 байт/с; фиг. 3 показывает примерную таблицу ввода на скорости 4800 байт/с для перемежителя каналов прямой передачи и пейджинга; фиг. 4 показывает примерную таблицу перемежения на 4800 байт/с для перемежителя каналов прямой передачи и пейджинга; фиг. 5 показывает примерную таблицу ввода на скорости 2400 байт/с для перемежителя каналов прямой передачи и пейджинга; фиг. 6 показывает примерную таблицу перемежения на 2400 байт/с для перемежителя каналов прямой передачи и пейджинга; фиг. 7 показывает примерную таблицу ввода на скорости 1200 байт/с для перемежителя каналов прямой передачи и пейджинга; фиг. 8 показывает примерную таблицу перемежения на 1200 байт/с для перемежителя каналов прямой передачи и пейджинга; фиг. 9 показывает таблицу ввода входных данных в соответствии с предпочтительным выполнением настоящего изобретения; фиг. 10 показывает таблицу перемежения в соответствии с предпочтительным выполнением настоящего изобретения; фиг. 11 показывает таблицу, представляющую связи между столбцами на фиг. 9 и 10; фиг. 12 показывает таблицу, представляющую связи между строками на фиг. 9 и 10; фиг. 13 показывает блок-схему перемежителя в групповом спектре в соответствии с предпочтительным выполнением настоящего изобретения.

Ниже будет подробно описано предпочтительное выполнение настоящего изобретения со ссылками на приложенные чертежи, в которых .различные подробности, включая биты или байты и т.д., могут быть проиллюстрированы для лучшего понимания настоящего изобретения. Однако следует отметить, что настоящее изобретение не ограничивается этими особенностями, сформулированными только в качестве примера в нижеследующем выполнении. Далее, подробное описание известных функций и конструкций, которое может излишне затруднять лучшее понимание предмета изобретения, будет опущено в настоящем изобретении.

Говоря в целом, перемежитель выполняет чередование на основе входных данных на 9600 байт/с. Таким образом, перемежитель по предпочтительному выполнению настоящего изобретения использует таблицу ввода и таблицу перемежения, выработанные на основе упомянутого сигнала 9600 байт/с. Фиг. 9 показывает таблицу ввода входных данных в соответствии с предпочтительным выполнением настоящего изобретения, тогда как фиг. 10 показывает таблицу перемежения в соответствии с предпочтительным выполнением. Вышеупомянутые таблицы ввода и перемежения снабжены 384 битами, индексы которых именуются как на индексы 0 - 383. Далее, строки и столбцы таблиц ввода и перемежения именуются как строки 0-23 и столбцы 0 - 15 соответственно. Таблица ввода снабжена 384 индексами, которые расположены последовательно от индекса 0 строки 0 и столбца 0 до индекса 383 строки 23 и столбца 15, как показано на фиг. 9. Аналогично таблица перемежения снабжена 384 индексами, которые расположены последовательно от индекса 0 строки 0 и столбца 0 до индекса 383 строки 23 и столбца 15, как показано на фиг. 10.

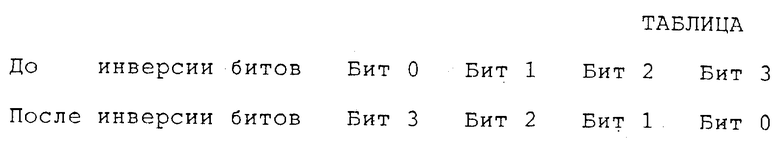

По упомянутым таблицам ввода и перемежения можно оценить следующее отношение. Имеется в виду, что если любой индекс таблицы вывода подлежит делению на число 16, то его остаток затем представляется в четырех битах, и над этими четырьмя битами проводится инверсия битов, затем этот остаток соотносится конкретному столбцу, где упомянутый индекс расположен в таблице перемежения. Здесь инверсия битов может быть обычно обеспечена путем преобразования, позиции бита, как указано в следующей таблице.

Согласно этой таблице инверсия битов выполняется так, чтобы бит 0 заменялся битом 3, бит 1 битом 2, бит 2 битом 1 и бит 3 битом 0.

Фиг. 11 показывает примерный путь получения столбцов таблицы перемежения путем использования вышеупомянутого индекса, в котором устанавливаются полученные столбцы индексов 0-15. Когда этот индекс делится на число 16, его остаток может быть взят как число по модулю 16, которое затем может быть представлено в четырехбитном формате, получая тем самым биты по модулю. Биты по модулю затем инвертируются в соответствии с вышеприведенной таблицей для проведения инверсии битов, по которой столбец, указываемый инвертированным битом, соответствует выбранному столбцу в таблице преобразования. Например, если числом по модулю 16 индекса 0 является ноль, то тогда бит по модулю равен 0000, инверсия битов - 0000 и столбец в таблице перемежения - 0. Это означает, что когда данные индекса 0 таблицы ввода чередуются, данные индекса 0 расположены в столбце 0 таблицы перемежения. Аналогично следует понять, что число по модулю 16 индекса 1 равно 1, бит по модулю равен 0001, инверсия битов - 1000 и столбец индекса 1 в таблице перемежения - 8. Таким образом, это означает, что когда данные индекса 1 таблицы ввода чередуются, то данные индекса 1 расположены в столбце 8 таблицы перемежения. В результате отмечено, что соответствующие столбцы этих индексов таблицы ввода и таблицы перемежения сопрягаются друг с другом один за одним простой операцией.

Далее, отношение между индексами таблицы ввода и строками таблицы перемежения описано ниже со ссылками на фиг. 9 и 10. Когда индекс делится на 16, его частное берется как частное по модулю 16. Чтобы получить строку из этого частного по модулю 16, настоящее изобретение использует таблицу строк, как установлено на фиг. 12, поскольку невозможно найти никакой связи между частным по модулю 16 и строками путем использования любой простой операции. Например, таблица строк на фиг. 12 устроена так, что если частное по модулю 16 равно нулю, то строка становится строкой 0, если частное по модулю 16 равно 1, то строка становится строкой 12, если частное по модулю 16 равно 2, то строка становится строкой 6, и аналогично, если частное по модулю 16 равно 23, то строка становится строкой 23.

Соответственно в случае, когда частное по модулю 16 равно нулю, индексы, которые расположены в строке 0, будут 0, 1, 2 ... 14, 15, как показано в таблице перемежения на фиг. 10. Далее, в случае, если частное по модулю 16 равно 1, индексы будут 16, 17, 18, ... 30, 31. Как описано выше, эти строки таблицы строк на фиг. 12 и строки, соответствующие частному по модулю 16, идентичны. Здесь таблица строк может быть выполнена в памяти гораздо меньшего размера, например 24 байта, по сравнению с памятью большего размера, например 512 байт, необходимых при использовании памяти общего назначения.

Фиг. 13 показывает блок-схему перемежителя в групповом спектре в соответствии с предпочтительным выполнением настоящего изобретения и в соответствии с вышеописанной взаимосвязью индексов. Схема 10 по модулю 16 перемежителя принимает индекс, который делится на 16, и затем снабжает инвертор 12 битов его остатком. Инвертор битов проводит инверсию битов значения входного остатка по модулю 16 из схемы по модулю 16, и значение инвертированного бита соответствует заданному столбцу таблицы перемежения. Этот столбец вводится в память 14, имеющую внутри таблицы перемежения, как показано на фиг. 10.

Схема 16 частного по модулю 16 перемежителя также принимает индекс, который поделен на 16, и затем снабжает частным от его деления кодовый преобразователь 18, имеющий таблицу столбцов, как показано на фиг. 11. Соответственно кодовый преобразователь 18 считывает столбец, соответствующий упомянутому частному из таблицы столбцов, и затем снабжает считанным столбцом память 14. Таким образом, память получает и столбец, и строку, по которым память записывает выходные данные в конкретную позицию в соответствии с этими строкой и столбцом.

В то же время основная система (не показана) обеспечивает такты считывания данных, которые подаются на вычислитель 22 по основанию 24, когда ему требуется выдать данные, записанные в память по вышеописанной операции перемежения. Вычислитель 22 по основанию 24 вычисляет такт входных данных, чтобы обеспечить вычисленное значение, которое показывает выбранную строку таблицы перемежения в памяти 14.

Далее, перенос, подаваемый из вычислителя по основанию 24, затем подается на вычислитель по основанию 20, который вычисляет перенос и подает вычисленное значение в память 14. Это вычисленное значение представляет собой столбец таблицы перемежения. Следовательно, память 14 принимает упомянутые строку и столбец и в ответ на них выдает данные соответствующей позиции как выходные.

Как ясно из вышеприведенного описания, настоящее изобретение обеспечивает перемежитель в групповом спектре, использующий корреляцию между позициями индексов таблицы перемежения в случае, когда индексы данных записываются с перемежением. Далее, в случае записи с перемежением индексов данных, не имеющих корреляции, позиция в таблице перемежения ищется путем использования простого малоемкого кодового преобразователя.

В результате настоящее изобретение требует гораздо меньшую емкость памяти, например только 24 байта или около того, для перемежителя в групповом спектре по сравнению с существующим перемежителем, который обычно требует по меньшей мере 384 байта емкости памяти. Следовательно, перемежитель в групповом спектре может быть выполнен с меньшей стоимостью, чем любой существующий перемежитель.

Хотя здесь было проиллюстрировано и описано то, что считается предпочтительными выполнениями настоящего изобретения, специалистам должно быть понятно, что могут производиться различные изменения и модификации и эквиваленты могут заменять имеющиеся элементы без отклонения от истинного объема настоящего изобретения. Кроме того, могут производиться многие модификации для приспосабливания конкретной ситуации к предмету настоящего изобретения без отклонения от его основного объема. Поэтому имеется в виду, что настоящее изобретение не ограничено конкретным выполнением, описанным как наилучший режим, предполагаемый для осуществления настоящего изобретения, но что настоящее изобретение включает в себя все выполнения, попадающие в объем прилагаемой формулы изобретения.

Изобретение относится к перемежающему средству или перемежителю для системы мобильной телесвязи с многостанционным доступом с кодовым разделением (МДКР), и в частности к перемежителю в групповом спектре для каналов прямой передачи и пейджинга. Технический результат - обеспечение улучшенного перемежителя в групповом спектре для каналов прямой передачи и пейджинга с уменьшенной емкостью памяти перемежения и более простой конструкцией. В перемежителе схема по модулю 16 делит индекс на число 16, причем индекс выбирается из множества последовательных индексов 0-383, соответствующих входным данным, и обеспечивает остаток от деления этого индекса. Инвертор битов проводит инверсию битов на выходе схемы по модулю 16 и определяет позицию столбца для записи в данных с проведенным перемежением. Схема частного по модулю 16 вырабатывает частное от деления индекса на число 16. Кодовый преобразователь имеет таблицу строк, по которой частное соответственно соотносится с позицией строки, чтобы записать его с проведенным перемежением, для выработки позиции строки, соответствующей частному. Вычислитель по основанию 24 вычисляет такты считывания данных и обеспечивает вычисленное по основанию 24 значение, соответствующее выбранной строке выходных данных для считывания. Вычислитель по основанию 16 обеспечивает вычисленное по основанию 24 значение, соответствующее выбранному столбцу выходных данных для считывания. Память имеет в себе таблицу перемежения, включающую в себя 32 строки и 16 столбцов, при этом входные данные записываются в выбранную позицию таблицы перемежения в соответствии с выходом инвертора битов и выходом кодового преобразователя, а выходные данные являются данными, считанными из позиции, соответствующей выходу вычислителя по основанию 16 и выходу вычислителя по основанию 24. 1 табл., 13 ил.

Перемежитель в групповом спектре, содержащий кодовый преобразователь, память и два вычислителя, отличающийся тем, что содержит схему по модулю 16 для деления индекса на число 16, причем упомянутый индекс выбирается из множества последовательных индексов 0-383, соответствующих входным данным, и для получения остатка от деления этого индекса, инвертор битов, осуществляющий инверсию битов на выходе схемы по модулю 16, а инвертированное значение битов вводится в память, при этом инвертированное значение соответствует столбцу, который является одним из информации, указывающей положение таблицы перемежения для записи входных данных, причем входные данные относятся к данным, вводимым для перемежения, схему частного по модулю 16 для приема индекса для выработки частного от деления индекса на число 16, при этом кодовый преобразователь, имеющий таблицу строк, по которой упомянутое частное соответственно соотносится с позицией строки, чтобы записать его с проведенным перемежением для выработки позиции строки, соответствующей частному, при этом первый вычислитель является вычислителем по основанию 24 для вычисления тактов считывания данных и для обеспечения вычисленного по основанию 24 значения, соответствующего выбранной строке выходных данных для считывания, чтобы выборочно выводить перемеженные записанные данные, второй вычислитель является вычислителем по основанию 16, принимающий перенос вычислителя по основанию 24, для обеспечения вычисленного по основанию 16 значения, соответствующего выбранному столбцу выходных данных для считывания, и блок памяти, имеющий в себе таблицу перемежения, включающую в себя 32 строки и 16 столбцов, причем упомянутые входные данные записываются в выбранную позицию упомянутой таблицы перемежения в соответствии с выходом инвертора битов и выходом кодового преобразователя, упомянутые выходные данные являются данными, считанными из позиции, соответствующей выходу упомянутого вычислителя по основанию 16 и выходу вычислителя по основанию 24.

| US 5535220 A, 09.07.96 | |||

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| US 4559625 A, 17.12.85 | |||

| US 5056112 A, 08.10.91 | |||

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

Авторы

Даты

1999-09-10—Публикация

1997-09-19—Подача