Настоящее изобретение относится к перемежителю для применения в мобильной станции PCS (Персональных коммуникационных услуг) типа CDMA (множественного доступа с кодовым разделением каналов), более конкретно - к генератору адреса считывания с чередованием для генерации адреса считывания с чередованием для считывания данных, записанных в память с чередованием.

Уровень техники.

В соответствии со Стандартом SP-3384 для CDMA PCS мобильной станции определяется, что CDMA PCS мобильная станция должна выполнять перемежение для предотвращения импульсной ошибки или реверса канала. Перемежение (чередование) достигается с помощью последовательной записи данных передачи в память при чередовании, а затем последовательным считыванием данных из памяти с чередованием.

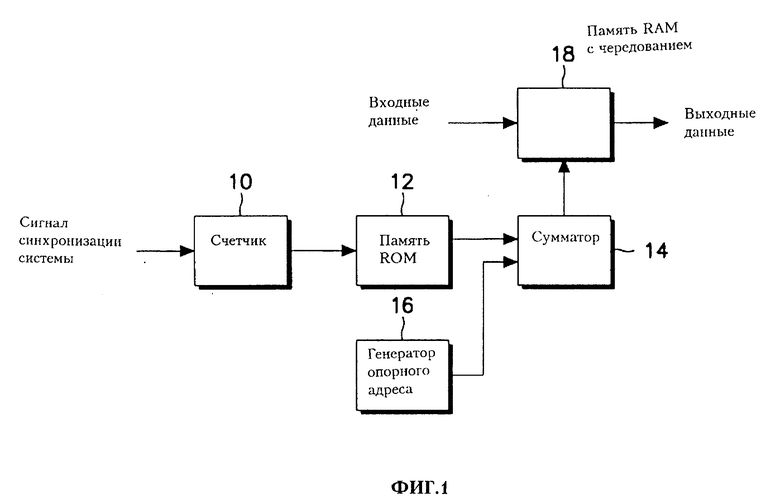

Известный перемежитель (фиг. 1) для получения перемежения включает в себя счетчик 10, память типа ROM (постоянное ЗУ) 12, сумматор 14, генератор 16 опорного адреса и память типа RAM (оперативное ЗУ) 18. Счетчик 10 подсчитывает синхронизирующие импульсы системы и подает подсчитанное значение в ROM 12, в которую записывается адрес считывания при чередовании, соответствующее подсчитанному значению. После приема подсчитанного значения ROM 12 генерирует адрес считывания с чередованием, соответствующий подсчитанному значению. Генератор 16 опорного адреса формирует опорный адрес для считывания и записи данных из/в RAM 18 при чередовании. Сумматор 14 суммирует адрес считывания при чередовании, выданный из ROM 12, с опорным адресом, выданным из генератора 16 опорного адреса, для формирования адреса считывания при чередовании, по которому RAM 18 с чередованием считывает записанные в него данные. Память RAM 18 с чередованием записывает данные, подаваемые извне, и считывает данные, записанные в нее, в соответствии с адресом считывания при чередовании, выданным из сумматора 14.

Как видно из предшествующего описания, известный перемежитель обязательно включает дорогую память ROM, в которую записывается адрес считывания с чередованием, таким образом увеличивая стоимость изготовления перемежителя.

Между тем, в соответствии с вышеупомянутым Стандартом SP-3384 перемежитель имеет переменную скорость данных. Другими словами Стандарт SP-3384 определяет скорость данных 9600 бит/сек и 14400 бит/сек, скорость данных 4800 бит/сек и 7200 бит/сек, скорость данных 2400 бит/сек и 3600 бит/сек и скорость данных 1200 бит/сек и 1800 бит/сек. Перемежитель должен по-разному выполнять перемежение по отношению к соответствующим скоростям данных. Соответственно, система CDMA с переменной скоростью данных должна включать в себя ROM, в которую записывается адрес считывания с перемежением для соответствующих скоростей данных для того, чтобы выполнить перемежение. В случае, когда скорость данных является переменной, как указано выше, ROM имеет увеличенный объем для записи в нее данных, так что ROM должна увеличиваться по объему.

Как описано выше, известный перемежитель использует ROM, в которую записывается адрес считывания при перемежении в соответствии для каждой скорости данных, приводя к увеличению стоимости. В частности, в случае мобильной станции типа CDMA PCS, работающей в Стандарте SP-3384, ROM будет увеличиваться по стоимости, вызывая проблемы с увеличением стоимости.

Сущность изобретения.

Задачей настоящего изобретения является создание простого генератора адреса считывания при перемежении, состоящего из счетчиков и логических вентилей.

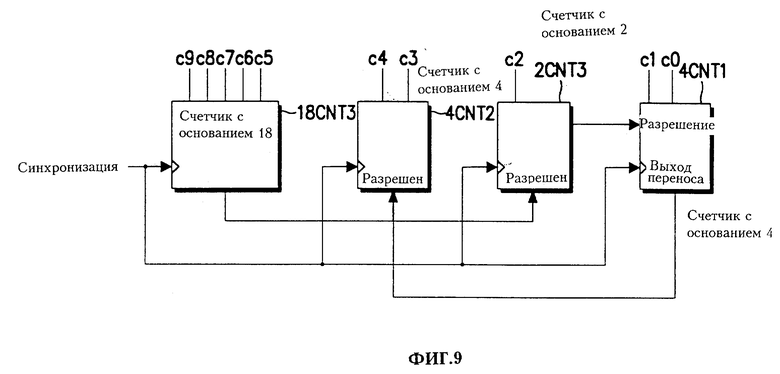

Согласно аспекту настоящего изобретения генератор адреса считывания с перемежением включает в себя счетчик с основанием 18 для подсчета входных синхронизирующих сигналов по модулю 18 для формирования битов адреса колонки, счетчик с основанием 32, работающий по выходному сигналу переноса от счетчика с основанием 18, для подсчета входных синхронизирующих сигналов по модулю 32 для формирования битов адреса строки и мультиплексор для изменения положения выходных битов счетчика с основанием 32 в соответствии с сигналами выбора скорости данных для переменного формирования адресных битов строки.

Краткое описание чертежей.

Указанные выше и другие задачи, признаки и преимущества настоящего изобретения станут более ясными в свете последующего подробного описания наилучшего его воплощения вместе с сопроводительными чертежами.

Фиг. 1 - диаграмма перемежителя в соответствии с предшествующим уровнем техники,

фиг. 2 - диаграмма, изображающая организацию данных при записи данных в память с чередованием при скорости данных 9600 бит/сек и 14400 бит/сек,

фиг. 3 - диаграмма, изображающая организацию данных при записи данных в память с чередованием при скорости данных 4800 бит/сек и 7200 бит/сек,

фиг. 4 - диаграмма, изображающая организацию данных при записи данных в память с чередованием при скорости данных 2400 бит/сек и 3600 бит/сек,

фиг. 5 - диаграмма, изображающая организацию данных при записи данных в память с чередованием при скорости данных 1200 бит/сек и 1800 бит/сек,

фиг. 6 - диаграмма, изображающая последовательность считывания строк для считывания данных, записанных в память при чередовании, согласно соответствующим скоростям данных,

фиг. 7 - схема генератора адреса считывания при чередовании для формирования адреса считывания при чередовании для считывания данных при скорости данных 9600 бит/сек и 14400 бит/сек согласно варианту осуществления настоящего изобретения,

фиг. 8 - схема генератора адреса считывания при чередовании для формирования адреса считывания при чередовании для считывания данных при скорости данных 4800 бит/сек и 7200 бит/сек согласно варианту осуществления настоящего изобретения,

фиг. 9 - схема генератора адреса считывания при чередовании для формирования адреса считывания при чередовании для считывания данных при скорости данных 2400 бит/сек и 3600 бит/сек согласно варианту осуществления настоящего изобретения,

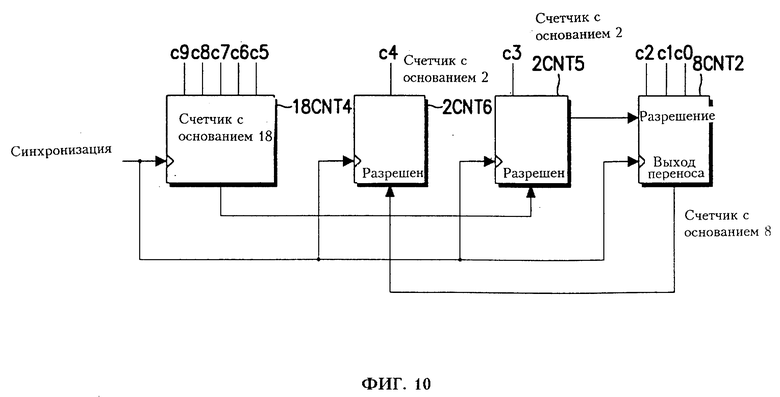

фиг.10 - схема генератора адреса считывания при чередовании для формирования адреса считывания при чередовании для считывания данных при скорости данных 1200 бит/сек и 1800 бит/сек согласно варианту осуществления настоящего изобретения,

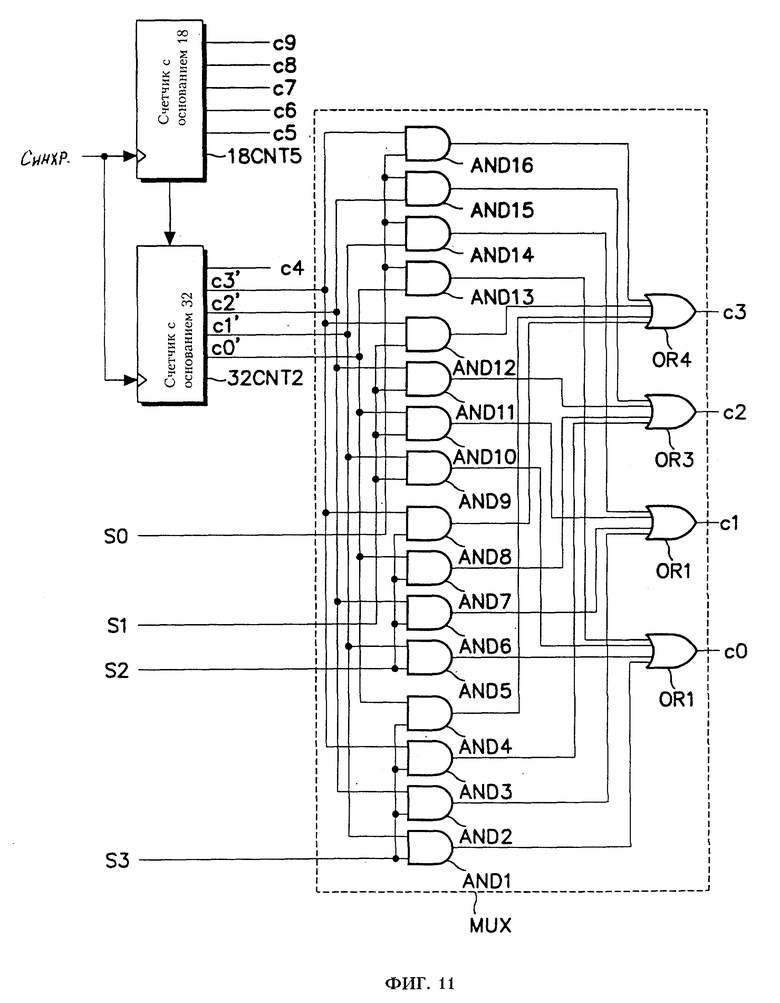

фиг. 11 - схема генератора адреса считывания при переменном чередовании для формирования адреса считывания при чередовании для считывания данных при переменной скорости данных согласно другому варианту осуществления настоящего изобретения.

Подробное описание предпочтительного варианта осуществления изобретения.

Ниже будет подробно описан предпочтительный вариант осуществления настоящего изобретения со ссылками на сопроводительные чертежи, на которых одинаковые цифровые обозначения соответствуют одинаковым элементам. Далее, должно быть понятно, что многие подробности, такие как подробные элементы схемы, изображены только в качестве примера для лучшего понимания настоящего изобретения, и настоящее изобретение может быть реализовано без этих подробностей. Кроме того, следует отметить, что подробные описания соответствующего предшествующего уровня техники могут быть намеренно опущены, если предполагается, что нет необходимости в их описании в концепции настоящего изобретения.

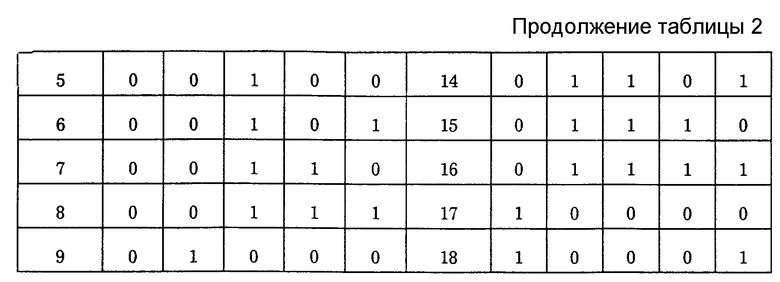

Фиг. 2 изображает организацию данных в памяти при чередовании, такой как RAM (со случайным доступом), когда данные записываются со скоростью 9600 бит/сек и 14400 бит/сек в соответствии со стандартом SP-3384 для CDMA PSC мобильных станций. Так как количество записываемых данных является тем же самым, что и количество адресов, то номера, изображенные на фиг.2, являются одинаковыми с адресами памяти с чередованием. Другими словами, номер "1" представляет собой первые данные и адрес первой строки и первой колонки, а номер "2" представляет собой вторые данные и адрес во второй строке и первой колонке. Аналогично номер "3" представляет собой третьи данные и адрес в третьей строке и первой колонке. Другие номера представляют собой соответствующие данные и адреса, как описано выше. Следует заметить, что такая адресная организация одинаково применима к другим скоростям данных.

Данные записываются последовательно (фиг.2) в порядке адресов со скоростями 9600 бит/сек и 14400 бит/сек, а записанные данные считываются в соответствии с адресом считывания при чередовании во время перемежения. Фиг. 6 иллюстрирует последовательность считывания адресов строк по адресам считывания при чередовании. Как изображено, последовательность считывания строк при скорости данных 9600 бит/сек и 14400 бит/сек составляет 1, 2, 3, 4, ..., 32. Так как последовательность считывания строк определена, то данные, записанные во все 18 колонок определенных строк, последовательно считываются.

То есть, в соответствии с фиг.2 последовательность считывания данных при скорости данных 9600 бит/сек и 14400 бит/сек составляет 1, 33, 65, 97, 129,. .. 545, 2, 34,... и 576. Фиг. 7 иллюстрирует генератор адреса считывания при перемежении для формирования адреса считывания при перемежении в соответствии с отмеченной выше последовательностью считывания данных. Генератор адреса считывания при перемежении включает в себя первый счетчик 18CNT1 с основанием 18 (восемнадцатеричный) и первый счетчик 32CNT1 с основанием 32.

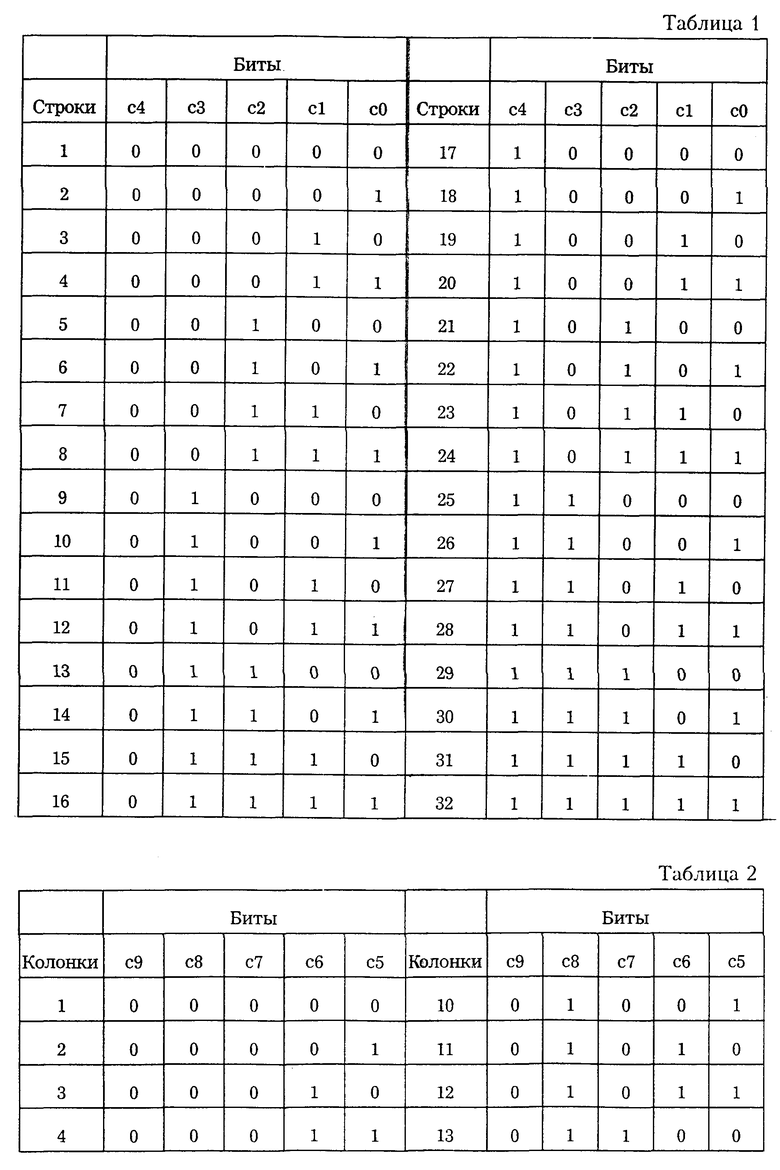

Адреса считывания с перемежением представлены пятью адресными битами c9, c8, c7, c6 и c5 колонки и пятью адресными битами c4, c3, c2, c1 и c0 строки соответственно. Как показано в таблице 1 (см. таблицу в конце описания), 32 строки представлены адресными битами строки c4, c3, c2, c1 и c0. Следует отметить, что строки могут быть одинаково представлены адресными битами строки c4, c3, c2, c1 и c0 при других скоростях данных.

Далее, как показано в таблицы 2 (см. табл. в конце описания), 18 колонок представлены адресными битами колонок c9, c8, c7, c6 и c5. Следует отметить, что колонки могут быть идентично представлены адресными битами колонки c9, c8, c7, c6 и c5 при других скоростях данных.

То есть, 576 адресов, показанных на фиг. 2, представляются комбинацией адресных битов колонки c9, c8, c7, c6 и c5 и адресных битов строки c4, c3, c2, c1 и c0. Например, адрес первой колонки и первой строки представляется комбинацией адресных битов колонки 00000 и адресных битов строки 00000.

Фиг. 7 иллюстрирует генератор адресов считывания при чередовании для формирования адресов считывания при чередовании в последовательности адреса считывания при чередовании для скорости данных 9600 бит/сек и 14400 бит/сек.

Во время работы первый счетчик 18CNT1 с основанием 18 подсчитывает входные синхронизирующие сигналы для формирования подсчитанного значения (т.е. адресных битов колонки c9, c8, c7, c6 и c5, в которых адресный бит колонки c5 является младшим значащим битом (LSB), а адресный бит колонки c9 является старшим значащим битом (MSB). В данном случае подсчитанное значение представляет собой адрес колонки и увеличивается от 00000, соответствующего первой колонке, до 10001, соответствующего восемнадцатой колонке.

Первый счетчик 18CNT1 с основанием 18 формирует перенос на своем выходе переноса, когда подсчитанное значение изменяется с 10001 на 00000. Выходной сигнал переноса от первого счетчика 18CNT1 с основанием 18 подается на разрешающий вывод первого счетчика 32CNT1 с основанием 32. После приема выходного сигнала переноса от первого счетчика 18CNT1 с основанием 18 первому счетчику 32CNTI с основанием 32 разрешается подсчитывать синхросигналы и формировать подсчитанное значение адресных битов строки c4, c3, c2, c1 и c0, в которых адресный бит строки с0 является младшим значащим битом (LSB), а адресный бит строки с4 является старшим значащим битом (MSB). В данном случае подсчитанное значение представляет собой адрес строки и последовательно увеличивается от 00000, соответствующего первой строке, до 11111, соответствующего тридцать второй строке.

Как описано выше, первый счетчик 18CNT1 с основанием 18 подсчитывает синхросигналы от 00000 до 10001 для формирования адресов колонки 1, 33, 65, 129, 161, ... и 545, как изображено на фиг.2. Первый счетчик 18CNT1 с основанием 18 формирует перенос, когда подсчитанное значение изменяется с 10001 на 00000. Затем, после приема выходного сигнала переноса от первого счетчика 18CNT1 с основанием 18 первый счетчик 32CNT1 с основанием 32 подсчитывает синхросигнал для формирования подсчитанного значения, равного 00001. В этот момент первый счетчик 18CNT1 с основанием 18 снова подсчитывает синхросигналы от 00000 до 10001 для формирования адресов колонки 2, 34, 66, 98, 130,. .. и 546. Таким же образом генератор адреса считывания с перемежением, изображенный на фиг.7, формирует адреса считывания до 576 с чередованием.

Фиг. 3 изображает организацию данных, когда данные записываются в память с чередованием со скоростью 4800 бит/сек и 7200 бит/сек в соответствии со Стандартом SP-3384 для CDMA PCS мобильных станций. Хотя адреса в памяти с чередованием являются теми же самыми, что и в случае 9600 бит/сек и 14400 бит/сек, скорости данных 4800 бит/сек и 7200 бит/сек в два раза медленнее, чем скорости данных 9600 бит/сек и 14400 бит/сек. Соответственно данные, которые должны быть записаны в память с перемежением со скоростью 4800 бит/сек и 7200 бит/сек, записываются по двум последовательным адресам. Поэтому одинаковые данные появляются дважды по отношению ко всем данным, как изображено на фиг. 3. Однако данные перемежаются посредством адресного устройства во время чередования.

Данные, записываемые по двум адресам, считываются согласно адресу считывания при чередовании, и последовательность считывания строк адресов считывания при чередовании изображена на фиг.6. А именно, фиг.6 иллюстрирует последовательность адресов строк из адресов считывания при чередовании. Как показано, последовательность считывания строк при скорости данных 4800 бит/сек и 7200 бит/сек составляет 1, 3, 2, 4, 5,... и 32.

То есть последовательность считывания при скорости данных 4800 бит/сек и 7200 бит/сек составляет 1, 33, 65, 129, 545, 2, 34,... и 576. Отметим, что последовательность колонок является той же, что и в случае скорости данных 9600 бит/сек и 14400 бит/сек, но последовательность строк изменяется. Адресные биты c4, c3, c2, c1 и c0 строки в соответствии с последовательностью считывания строк представляются 00000, 00010, 00001, 00011, 00100, 00110,... и 11111.

Вообще, счетчик переключает младший значащий бит (например, бит c0) между 0 и 1 и переключает следующий бит в соответствии с младшим значащим битом (т.е. бит c1), когда младший значащий бит c0 переключается из 1 в 0. Однако при скорости данных 4800 бит/сек и 7200 бит/сек адресный бит строки c1 переключается первым, а затем переключаются последовательно адресные биты строки c0, c2, c3 и c4. Поэтому генератор адреса считывания с чередованием для скорости данных 4800 бит/сек и 7200 бит/сек может быть реализован с помощью изменения выходного сигнала генератора адреса считывания с чередованием для скорости данных 9600 бит/сек и 14400 бит/сек. А именно, выходные биты c0 и c1 генератора адреса считывания с чередованием для скорости данных 9600 бит/сек и 14400 бит/сек меняются друг с другом для реализации генератора адреса считывания с чередованием для скорости данных 4800 бит/сек и 7200 бит/сек.

Фиг. 8 иллюстрирует генератор адреса считывания с чередованием для скорости данных 4800 бит/сек и 7200 бит/сек. Генератор адреса считывания с чередованием формирует адрес считывания с чередованием из последовательности адреса считывания с чередованием. Генератор адреса считывания с чередованием включает в себя второй счетчик 18CNT2 с основанием 18, первый восьмеричный (с основанием 8) счетчик 8CNT1 и первый и второй двоичные (с основанием 2) счетчики 2CNT1 и 2CNT2. Второй счетчик 18CNT2 с основанием 18 формирует адресные биты колонки c9, c8, c7, c6 и c5 и сигнал переноса таким же образом, как изображенный на фиг.7 первый счетчик 18CNT1 с основанием 18 генератора адреса считывания с чередованием для 9600 бит/сек и 14400 бит/сек. Выходной сигнал переноса из второго счетчика 18CNT2 с основанием 18 подается на разрешающий вывод первого двоичного счетчика 2CNT1, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, всякий раз, когда выходной сигнал переноса принимается из второго счетчика 18CNT2 с основанием 18, первый двоичный счетчик 2CNT1 подсчитывает синхронизирующие сигналы для формирования адресного бита c1 строки. Первый двоичный счетчик 2CNT1 формирует перенос, когда адресный бит c1 строки изменяется с 1 на 0. Выходной сигнал переноса от первого двоичного счетчика 2CNT1 подается на разрешающий вывод второго двоичного счетчика 2CNT2, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, второй двоичный счетчик 2CNT2 подсчитывает синхронизирующие сигналы для формирования адресного бита c0 строки всякий раз, когда первый двоичный счетчик 2CNT1 формирует перенос. Второй двоичный счетчик 2CNT2 формирует перенос, когда адресный бит c0 строки изменяется с 1 на 0. Выходной сигнал переноса второго двоичного счетчика 2CNT2 подается на разрешающий вывод первого восьмеричного счетчика 8CNT1, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, всякий раз, когда второй двоичный счетчик 2CNT2 формирует выходной сигнал переноса, первый восьмеричный счетчик 8CNT1 подсчитывает синхронизирующие сигналы для формирования адресных битов c4, c3 и c2 строки. Поэтому адрес считывания с чередованием формируется в комбинации адресных битов колонки c9, c8, c7, c6 и c5 второго счетчика 18CNT2 с основанием 18, адресных битов c4, c3 и c2 строки восьмеричного счетчика 8CNT1, адресного бита c1 первого двоичного счетчика 2CNT1 и адресного бита c0 второго двоичного счетчика 2CNT2.

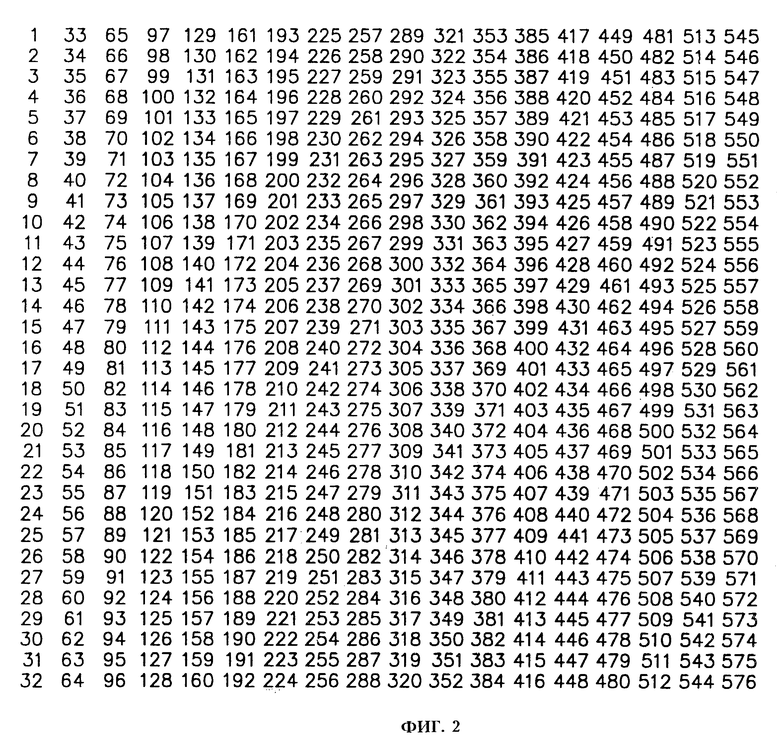

Фиг.4 иллюстрирует организацию данных, когда данные записываются в память с перемежением со скоростью 2400 бит/сек и 3600 бит/сек в соответствии со стандартом SP-3384 для CDMA PSC мобильной станции. Хотя адреса в памяти с перемежением являются теми же, что и при скорости 9600 бит/сек и 14400 бит/сек, скорость данных 2400 бит/сек и 3600 бит/сек в 4 раза медленнее, чем скорость 9600 бит/сек и 14400 бит/сек. Соответственно данные, которые должны быть записаны в память с перемежением со скоростью 2400 бит/сек и 3600 бит/сек, записываются по четырем последовательным адресам. Поэтому одинаковые данные появляются 4 раза по сравнению со всеми данными, как изображено на фиг.4. Однако данные чередуются с помощью адресного устройства во время чередования.

Данные, записанные последовательно по четырем адресам, считываются в соответствии с адресом считывания при чередовании во время перемежения, и последовательность строк адресов считывания при чередовании иллюстрируется на фиг. 6. А именно, фиг.6 иллюстрирует последовательность строчных адресов считывания при чередовании. Как показано, последовательность считывания строк при скоростях данных 2400 бит/сек и 3600 бит/сек составляет 1, 5, 2, 6, 3, 7, 4, 8, 9, 13, ... и 32.

То есть, последовательность считывания при скоростях данных 2400 бит/сек и 3600 бит/сек должна заключаться в считывании 18 колонок первой строки, а затем 18 колонок пятой строки и т.д. Следует отметить, что последовательность колонок является той же, что и в случае скорости данных 9600 бит/сек и 14400 бит/сек, но последовательность считывания изменена. Адресные биты строки c4, c3, c2, c1 и c0 согласно последовательности считывания строк представляются 00000, 00100, 00001, 00101, 00010, 00110,... и 11111.

Из предыдущего описания видно, что при скорости данных 2400 бит/сек и 3600 бит/сек адресный бит c2 строки переключается первым, а затем переключаются последовательно адресные биты c0, c1, c3 и c4. Поэтому генератор адреса считывания с чередованием для скорости данных 2400 бит/сек и 3600 бит/сек может быть реализован с помощью изменения выходного сигнала генератора адреса считывания с чередованием для скорости данных 9600 бит/сек и 14400 бит/сек. А именно, выходные биты c0, c1 и c2 генератора адреса считывания с чередованием для скорости данных 9600 бит/сек и 14400 бит/сек изменяются соответственно на биты c2, c0 и c1 для реализации генератора адреса считывания с чередованием для скорости данных 2400 бит/сек и 3600 бит/сек.

Фиг.9 иллюстрирует генератор адреса считывания с чередованием для скорости данных 2400 бит/сек и 3600 бит/сек. Генератор адреса считывания с чередованием формирует адрес считывания с чередованием в последовательности адреса считывания с чередованием. Генератор адреса считывания с чередованием включает в себя третий счетчик 18CNT3 с основанием 18, первый и второй счетчики 4CNT1 и 4CNT2 с основанием 4 и третий двоичный (с основанием 2) счетчик 2CNT3. Третий счетчик 18CNT3 с основанием 18 формирует адресные биты колонки c9, c8, c7, c6 и c5 и сигнал переноса таким же образом, как изображенный на фиг. 7 первый счетчик 18CNT1 с основанием 18 генератора адреса считывания с чередованием для 9600 бит/сек и 14400 бит/сек. Выходной сигнал переноса из третьего счетчика 18CNT3 с основанием 18 подается на разрешающий вывод третьего двоичного счетчика 2CNT3, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, всякий раз, когда третий счетчик 18CNT3 с основанием 18 формирует выходной сигнал переноса, третий двоичный счетчик 2CNT3 подсчитывает синхронизирующие сигналы для формирования адресного бита c2 строки. Третий двоичный счетчик 2CNT3 формирует перенос, когда адресный бит c2 строки изменяется с 1 на 0. Выходной сигнал переноса от третьего двоичного счетчика 2CNT3 подается на разрешающий вывод первого счетчика 4CNT1 с основанием 4, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, первый счетчик 4CNT1 с основанием 4 подсчитывает синхронизирующие сигналы для формирования адресных битов c1 и c0 строки всякий раз, когда третий двоичный счетчик 2CNT3 формирует перенос. Первый счетчик 4CNT1 с основанием 4 формирует перенос всякий раз, когда адресные биты c1 и c0 строки изменяются с 11 на 00. Выходной сигнал переноса первого счетчика 4CNT1 с основанием 4 подается на разрешающий вывод второго счетчика 4CNT2 с основанием 4, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, всякий раз, когда первый счетчик 4CNT1 с основанием 4 формирует выходной сигнал переноса, второй счетчик 4CNT2 с основанием 4 подсчитывает синхронизирующие сигналы для формирования адресных битов c4 и c3 строки. Поэтому адрес считывания с чередованием формируется в комбинации адресных битов c9, c8, c7, c6 и c5 третьего счетчика 18CNT3 с основанием 18, адресных битов c4 и c3 второго счетчика 4CNT2 с основанием 4, адресного бита c2 третьего двоичного счетчика 2CNT3 и адресных битов c1 и c0 первого счетчика 4CNT1 с основанием 4.

Фиг. 5 иллюстрирует организацию данных, когда данные записываются в память с перемежением со скоростью 1200 бит/сек и 1800 бит/сек в соответствии со стандартом SP-3384 для CDMA PSC мобильной станции. Хотя адреса в памяти с перемежением являются теми же, что и при скорости 9600 бит/сек и 14400 бит/сек, скорость данных 1200 бит/сек и 1800 бит/сек в 8 раза медленнее, чем скорость 9600 бит/сек и 14400 бит/сек. Соответственно данные, которые должны быть записаны в память с перемежением со скоростью 1200 бит/сек и 1800 бит/сек, записываются по восьми последовательным адресам. Поэтому одинаковые данные появляются 8 раз по сравнению со всеми данными, как изображено на фиг. 5. Однако данные чередуются с помощью адресного устройства во время чередования.

Данные, записанные последовательно по восьми адресам, считываются в соответствии с адресом считывания при чередовании во время перемежения, и последовательность строк адресов считывания при чередовании иллюстрируется на фиг. 6. А именно, фиг.6 иллюстрирует последовательность строчных адресов из адресов считывания при чередовании. Как показано, последовательность считывания строк при скоростях данных 1200 бит/сек и 1800 бит/сек составляет 1, 9, 2, 10, 3, 11, 4, 12, 5,... и 32.

То есть, последовательность считывания при скоростях данных 1200 бит/сек и 1800 бит/сек заключается в считывании 18 колонок первой строки, а затем 18 колонок девятой строки и т.д. Следует отметить, что последовательность колонок является той же, что и в случае скорости данных 9600 бит/сек и 14400 бит/сек, но последовательность считывания изменена. Адресные биты c4, c3, c2, c1 и c0 строки согласно последовательности считывания строк представляются 00000, 01000, 00001, 01001, 00010, 01011,... и 11111.

Из предыдущего описания видно, что при скорости данных 1200 бит/сек и 1800 бит/сек адресный бит c3 строки переключается первым, а затем переключаются последовательно адресные биты строки c0, c1, c2 и c4. Поэтому генератор адреса считывания с чередованием для скорости данных 1200 бит/сек и 1800 бит/сек может быть реализован с помощью изменения выходного сигнала генератора адреса считывания с чередованием для скорости данных 9600 бит/сек и 14400 бит/сек. А именно, выходные биты c0, c1, c2 и c3 генератора адреса считывания с чередованием для скорости данных 9600 бит/сек и 14400 бит/сек изменяются соответственно на биты c3, c0, c1 и c2 для реализации генератора адреса считывания с чередованием для скорости данных 1200 бит/сек и 1800 бит/сек.

Фиг.10 иллюстрирует генератор адреса считывания с чередованием для скорости данных 1200 бит/сек и 1800 бит/сек. Генератор адреса считывания с чередованием формирует адрес считывания с чередованием в последовательность адреса считывания с чередованием. Генератор адреса считывания с чередованием включает в себя четвертый счетчик 18CNT4 с основанием 18, пятый и шестой двоичные счетчики 2CNT5 и 2CNT6 и второй восьмеричный (с основанием 8) счетчик 8CNT2. Четвертый счетчик 18CNT4 с основанием 18 формирует адресные биты колонки c9, c8, c7, c6 и c5 и сигнал переноса таким же образом, как изображенный на фиг. 7 первый счетчик 18CNT1 с основанием 18 генератора адреса считывания с чередованием для 9600 бит/сек и 14400 бит/сек. Выходной сигнал переноса из четвертого счетчика 18CNT4 с основанием 18 подается на разрешающий вывод пятого двоичного счетчика 2CNT5, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, всякий раз, когда четвертый счетчик 18CNT4 с основанием 18 формирует выходной сигнал переноса, пятый двоичный счетчик 2CNT5 подсчитывает синхронизирующие сигналы для формирования адресного бита c3 строки. Пятый двоичный счетчик 2CNT5 формирует перенос, когда адресный бит c3 строки изменяется с 1 на 0. Выходной сигнал переноса пятого двоичного счетчика 2CNT5 подается на разрешающий вывод второго восьмеричного счетчика 8CNT2, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, второй восьмеричный счетчик 8CNT2 подсчитывает синхронизирующие сигналы для формирования адресных битов c2, c1 и c0 всякий раз, когда пятый двоичный счетчик 2CNT5 формирует перенос. Второй восьмеричный счетчик 8CNT2 формирует перенос всякий раз, когда адресные биты c2, c1 и c0 изменяются с 111 на 000. Выходной сигнал переноса второго восьмеричного счетчика 8CNT2 подается на разрешающий вывод шестого двоичного счетчика 2CNT6, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, всякий раз, когда второй восьмеричный счетчик 8CNT2 формирует выходной сигнал переноса, шестой двоичный счетчик 2CNT6 подсчитывает синхронизирующие сигналы для формирования адресного бита c4. Поэтому адрес считывания с чередованием формируется в комбинации адресных битов c9, c8, c7, c6 и c5 четвертого счетчика 18CNT4 с основанием 18, адресного бита c4 шестого двоичного счетчика 2CNT6, адресного бита c3 пятого двоичного счетчика 2CNT5 и адресных битов c2, c1 и c0 второго восьмеричного счетчика 8CNT2.

Как описано выше, адрес считывания при чередовании может быть свободно сформирован в соответствии со скоростями данных посредством простого изменения выходных сигналов генератора адресов считывания с чередованием при 9600 бит/сек и 14400 бит/сек, изображенном на фиг.7. Поэтому возможно реализовать генератор адресов считывания при чередовании для каждой скорости данных посредством простого изменения входных сигналов изображенного на фиг. 7 генератора адресов считывания при чередовании при 9600 бит/сек и 14400 бит/сек в соответствии со скоростями данных.

Фиг. 11 иллюстрирует генератор адреса считывания с переменным чередованием для формирования адреса считывания с чередованием согласно другому воплощению настоящего изобретения. Как изображено, генератор адреса считывания с переменным чередованием включает в себя пятый счетчик 18CNT5 с основанием 18, второй счетчик 32CNT2 с основанием 32 и мультиплексор MUX. Пятый счетчик 18CNT5 с основанием 18 формирует адресные биты колонки c9, c8, c7, c6 и c5 и сигнал переноса таким же образом, как изображенный на фиг. 7 первый счетчик 18CNT1 с основанием 18 генератора адреса считывания с чередованием для 9600 бит/сек и 14400 бит/сек. Выходной сигнал переноса из пятого счетчика 18CNT5 с основанием 18 подается на разрешающий вывод второго счетчика 32CNT2 с основанием 32, который принимает сигнал синхронизации на свой синхронизирующий вход. Таким образом, всякий раз, когда пятый счетчик 18CNT5 с основанием 18 формирует выходной сигнал переноса, второй счетчик 32CNT2 с основанием 32 подсчитывает синхронизирующие сигналы для формирования адресных битов c4, c3', c2', c1' и c0'. Мультиплексор MUX принимает адресные биты c3', c2', c1' и c0' от второго счетчика 32CNT2 с основанием 32 для формирования адресных битов c3, c2, c1 и c0 в соответствии с сигналами S3, S2, S1, S0 выбора скорости данных. Таблица 3 (см. в конце описания) представляет таблицу истинности для мультиплексора MUX.

Как видно из таблицы 1, мультиплексор MUX формирует различные адресные биты c3, c2, c1 и c0 в соответствии с сигналами S3, S2, S1 и S0 выбора скорости данных. Например, в случае скорости данных 9600 бит/сек и 14400 бит/сек мультиплексор MUX формирует биты данных c3', c2' c1' и c0' на выходах c3, c2, c1 и c0 соответственно. В этот момент генератор адреса считывания с чередованием реализует ту же функцию, что и генератор адреса считывания с чередованием, изображенный на фиг. 7. Адрес считывания с чередованием для 9600 бит/сек и 14400 бит/сек формируется в комбинации адресных битов c9, c8, c7, c6 и c5 пятого счетчика 18CNT5 с основанием 18, адресного бита c4 второго счетчика 32CNT2 с основанием 32 и адресных битов c3, c2, c1 и c0 мультиплексора MUX.

Далее, в случае скорости данных 4800 бит/сек и 7200 бит/сек мультиплексор MUX формирует биты данных c3', c2' c0' и c1' на выходах c3, c2, c1 и c0 соответственно. В этот момент генератор адреса считывания с чередованием реализует ту же функцию, что и генератор адреса считывания с чередованием, изображенный на фиг. 8. Адрес считывания с чередованием для 4800 бит/сек и 7200 бит/сек формируется в комбинации адресных битов c9, c8, c7, c6 и c5 пятого счетчика 18CNT5 с основанием 18, адресного бита c4 второго счетчика 32CNT2 с основанием 32 и адресных битов c3, c2, c1 и c0 мультиплексора MUX.

В случае скорости данных 2400 бит/сек и 3600 бит/сек мультиплексор MUX формирует биты данных c3', c0' c2' и c1' на выходах c3, c2, c1 и c0 соответственно. В этот момент генератор адреса считывания с чередованием реализует ту же функцию, что и генератор адреса считывания с чередованием, изображенный на фиг. 9. Адрес считывания с чередованием для 2400 бит/сек и 3600 бит/сек формируется в комбинации адресных битов c9, c8, c7, c6 и c5 пятого счетчика 18CNT5 с основанием 18, адресного бита c4 второго счетчика 32CNT2 с основанием 32 и адресных битов c3, c2, c1 и c0 мультиплексора MUX.

Кроме того, в случае скорости данных 1200 бит/сек и 1800 бит/сек мультиплексор MUX формирует биты данных c0', c3' c2' и c1' на выходах c3, c2, c1 и c0 соответственно. В этот момент генератор адреса считывания с чередованием реализует ту же функцию, что и генератор адреса считывания с чередованием, изображенный на фиг. 10. Адрес считывания с чередованием для 1200 бит/сек и 1800 бит/сек формируется в комбинации адресных битов c9, c8, c7, c6 и c5 пятого счетчика 18CNT5 с основанием 18, адресного бита c4 второго счетчика 32CNT2 с основанием 32 и адресных битов c3, c2, c1 и c0 мультиплексора MUX.

Между тем, мультиплексор MUX содержит с первого по шестнадцатый вентили И AND1 - AND16 и с первого по четвертый вентили ИЛИ OR1 - OR4. Адресный бит c0' второго счетчика 32CNT2 с основанием 32 подается на 4-й, 7-й 10-й и 13-й вентили AND4, AND7, AND10 и AND13. Адресный бит c1' второго счетчика 32CNT2 с основанием 32 подается на 1-й, 5-й 9-й и 14-й вентили AND1, AND5, AND9 и AND14. Адресный бит c2' второго счетчика 32CNT2 с основанием 32 подается на 2-й, 6-й 11-й и 15-й вентили AND2, AND6, AND11 и AND15. Кроме того, адресный бит c3' второго счетчика 32CNT2 с основанием 32 подается на 3-й, 8-й 12-й и 16-й вентили AND3, AND8, AND12 и AND16.

Сигнал S3 выбора скорости данных подается на первый - четвертый вентили И AND1 - AND4. Таким образом, набор с первого по четвертый вентилей И AND1 - AND4 формирует адресные биты c0', c3' c2' и c1' на выходах c3, c2, c1 и c0 соответственно в ответ на сигнал S3 скорости данных с высоким логическим уровнем так, чтобы сформировать адрес считывания с чередованием для 1200 бит/сек и 1800 бит/сек.

Аналогично, сигнал S2 выбора скорости данных подается на пятый - восьмой вентили И AND5 - AND8. Таким образом, набор с пятого по восьмой вентилей И AND5 - AND8 формирует адресные биты c3', c0' c2' и c1' на выходах c3, c2, c1 и c0 соответственно в ответ на сигнал S2 выбора скорости данных с высоким логическим уровнем так, чтобы сформировать адрес считывания с чередованием для 2400 бит/сек и 3600 бит/сек.

Сигнал S1 выбора скорости данных подается на девятый - двенадцатый вентили И AND9 - AND12. Таким образом, набор с девятого по двенадцатый вентилей И AND9 - AND12 формирует адресные биты c3', c2', c0' и c1' на выходах c3, c2, c1 и c0 соответственно в ответ на сигнал S1 выбора скорости данных с высоким логическим уровнем так, чтобы сформировать адрес считывания с чередованием для 4800 бит/сек и 7200 бит/сек.

Далее, сигнал S0 выбора скорости данных подается на 13 - 16 вентили и AND13 - AND16. Таким образом, набор с 13 по 16 вентилей И AND13 - AND16 формирует адресные биты c3', c2' c1' и c0' на выходах c3, c2, c1 и c0 соответственно в ответ на сигнал S0 выбора скорости данных с высоким логическим уровнем так, чтобы сформировать адрес считывания с чередованием для 9600 бит/сек и 14400 бит/сек.

Первый вентиль ИЛИ OR1 принимает выходные сигналы от 1, 5, 9 и 13 вентилей И AND1, AND5, AND9 и AND13 для формирования адресного бита c3. Второй вентиль ИЛИ OR2 принимает выходные сигналы от 2, 6, 10 и 14 вентилей И AND2, AND6, AND10 и AND14 для формирования адресного бита c2. Третий вентиль ИЛИ OR3 принимает выходные сигналы от 3, 7, 11 и 15 вентилей И AND3, AND7, AND11 и AND15 для формирования адресного бита c1. Четвертый вентиль ИЛИ OR4 принимает выходные сигналы от 4, 8, 12 и 16 вентилей И AND4, AND8, AND12 и AND16 для формирования адресного бита c0.

Как описано выше, генератор адреса считывания с чередованием реализуется с помощью недорогих счетчиков. Далее, генератор адреса считывания с переменным чередованием согласно изобретению включает в себя мультиплексор для формирования адреса считывания с переменным чередованием для различных скоростей данных. Поэтому возможно создать генератор адреса считывания с чередованием с низкой стоимостью.

Хотя предпочтительное воплощение настоящего изобретения описано выше подробно, должно быть понятно, что многие изменения и модификации основных концепций изобретения могут быть сделаны специалистами в объеме и форме настоящего изобретения, которое определяется прилагаемой формулой изобретения.

Изобретение относится к генератору адреса считывания с чередованием для считывания данных, записанных в память с чередованием, для использования в мобильном терминале связи типа СDМА. Техническим результатом является создание простого генератора адреса считывания при перемежении. Технический результат достигается за счет того, что генератор адреса считывания с чередованием включает в себя счетчик с основанием 18 для подсчета входных синхронизирующих импульсов по модулю 18 для формирования адресных битов колонки, счетчик с основанием 32, работающий от сигнала переноса от счетчика с основанием 18, для подсчета входных синхронизирующих импульсов по модулю 32 для формирования подсчитанного значения и мультиплексор для изменения положения выходных битов счетчика с основанием 32 в соответствии с сигналами выбора скорости данных для переменной генерации адресных битов строки. 2 c. и 8 з. п.ф-лы, 11 ил., 3 табл.

| Устройство для управления игрушечным автомобилем | 1975 |

|

SU552979A1 |

| RU 94014268 A1, 20.06.96 | |||

| РЕНТГЕНОВСКИЙ МИКРОАНАЛИЗАТОР | 0 |

|

SU202571A1 |

| Тепловая труба | 1972 |

|

SU449213A1 |

| US 4394642 A, 19.07.83. | |||

Авторы

Даты

1999-07-27—Публикация

1997-10-01—Подача