Изобретение относится к области вычислительной техники и может быть использовано при решении задач информационно-поисковой обработки данных, логической обработки данных в составе векторных ЭВМ и систем, форматирования данных.

Известно устройство для решения задач сжатия, расширения, сплетения, перегруппировки, форматирования единичного вектора (а. с. N 1314332 G 06 F 7/00). Устройство содержит две треугольные матрицы, группу элементов ИЛИ, НЕ, коммутационные ячейки, содержащие элементы НЕ, ИЛИ, И.

Недостатком этого устройства является невозможность выполнения произвольной операции побитной перестановки элементов двоичного вектора.

Наиболее близким техническим решением к изобретению является многокаскадная сеть Бенеса (Р. Хокни, К. Джессхоуп. Параллельные ЭВМ - М., Радио и связь, 1986, с. 389 - стр. 171 рис. 3.25), содержащая сеть из двухвходовых коммутационных элементов, связанных между собой каналами приема-передачи данных. Недостатком данного устройства является применение в конструкции постоянной топологии межкоммутаторных соединений, что ограничивает область применения устройства.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности динамического управления коммутаторами коммутационной сети с данными, поступающими на обработку.

Указанная цель достигается тем, что в устройство коммутации, содержащее коммутационную сеть из четырех столбцов коммутаторов по четыре коммутатора в столбце, причем, каждый из коммутаторов каждого столбца имеет два информационных входа, два информационных выхода и один вход управления, каждый коммутатор коммутационной сети обеспечивает передачу сигналов с информационных входов на информационные выходы без изменения их значений, причем, при единичном значении сигнала управления на управляющем входе коммутатора обеспечивается передача сигнала с первого информационного входа коммутатора на первый информационный выход коммутатора и сигнала со второго информационного входа коммутатора на второй информационный выход коммутатора, а при нулевом значении управляющего сигнала на управляющем входе коммутатора обеспечивается передача сигнала с первого информационного входа коммутатора на второй информационный выход коммутатора и сигнала со второго информационного входа коммутатора на первый информационный выход коммутатора, дополнительно введены в каждый столбец и каждую строку коммутационной сети по (n/2-4) коммутаторов с двумя информационными одним управляющим входами и двумя информационными выходами, причем, n=2(m-1) и m ≥ 6, каждый коммутатор из столбца коммутационной сети обеспечивает передачу сигналов с информационных входов на информационные выходы без изменения их значений, причем, при единичном значении сигнала управления на управляющем входе коммутатора обеспечивается передача сигнала с первого информационного входа коммутатора на первый информационный выход коммутатора и сигнала со второго информационного входа коммутатора на второй информационный выход коммутатора, а при нулевом значении управляющего сигнала на управляющем входе коммутатора обеспечивается передача сигнала с первого информационного входа коммутатора на второй информационный выход коммутатора и сигнала со второго информационного входа коммутатора на первый информационный выход коммутатора, первый 2n-разрядный регистр входного кода с первым входом управления записью данных, вторым входом установки в 0 и двумя группами n-разрядных информационных входов и группой 2n-разрядных информационных выходов, второй n-разрядный регистр входных данных с первым входом управления записью данных и вторым входом установки в 0, группой n-разрядных информационных входов и группой n-разрядных информационных выходов, третий n-разрядный регистр выходных данных с первым входом управления записью данных и вторым входом установки в 0, первая группа из n-разрядных информационных входов коммутационной сети, вторая группа из (2n) управляющих входов коммутационной сети и третья группа из n-разрядных информационных выходов коммутационной сети, мультиплексор с первой группой n-разрядных информационных входов, второй группой n-разрядных информационных входов, третьей группой n-разрядных информационных входов, первой группой n-разрядных информационных выходов, второй группой n-разрядных информационных выходов и первым, вторым, третьим управляющими входами, n-разрядное постоянное запоминающее устройство емкостью h ячеек с первым входом управления чтением данных из ячеек памяти, вторым входом установки в начальное состояние, n(h)-разрядной группой адресных входов и группой n-разрядных информационных выходов, (k=ln h)-разрядный счетчик адреса с первым счетным входом, вторым входом установки в 0 и группой из n-разрядных информационных выходов устройство управления с (0/t) адресными входами, шестью внешними управляющими входами и тринадцатью управляющими выходами, группу информационных входов данных устройства (0)-(n), группу (0)-(t) внешних адресных входов устройства, управляющий вход устройства, управляющий вход "готовность устройства" устройства, управляющий вход "режим установки" устройства, управляющий вход "режим обработки" устройства, управляющий выход "прием данных" устройства, управляющий выход "запрос данных" устройства, управляющий выход "конец обработки" устройства, группу информационных выходов устройства (0)-(n), управляющий вход устройства "конец работы", управляющий вход устройства "режим обратной обработки", управляющий выход устройства "режим установки начального кода", управляющий выход устройства "выбор режима обработки", причем, n-разрядные информационные входы коммутаторов первого столбца являются первой группой из n информационных входов коммутационной сети, информационные выходы коммутаторов последнего столбца являются информационными выходами коммутационной сети, а управляющие входы всех коммутаторов коммутационной сети являются управляющими входами коммутационной сети, вторая группа внешних информационных входов устройства подключена к (0-t)-разрядной группе адресных входов устройства управления, первый, второй, -, восьмой внешние управляющие входы устройства подключены соответственно к первому, второму, -, восьмому управляющим входам устройства управления, первый управляющий выход устройства управления подключен к третьему управляющему входу мультиплексора, второй управляющий выход устройства управления подключен к второму управляющему входу мультиплексора, третий управляющий выход устройства управления подключен к первому управляющему входу мультиплексора, четвертый управляющий выход устройства управления модуля подключен к первому управляющему входу второго n-разрядного регистра входных данных, пятый управляющий выход устройства управления подключен к первому управляющему входу первого 2n-разрядного регистра входного кода, шестой управляющий выход устройства управления подключен к второму управляющему входу второго n-разрядного регистра входных данных, седьмой управляющий выход устройства управления подключен к первому внешнему управляющему выходу устройства, восьмой управляющий выход устройства управления подключен к второму внешнему управляющему выходу устройства, девятый управляющий выход устройства управления подключен к первому управляющему входу третьего n-разрядного регистра выходных данных, десятый управляющий выход устройства управления подключен к первому управляющему входу n-разрядного постоянного запоминающего устройства, одиннадцатый управляющий выход устройства управления подключен к второму управляющему входу n-разрядного постоянного запоминающего устройства, второму управляющему входу первого 2n-разрядного регистра входного кода и второму управляющему входу третьего n-разрядного регистра выходных данных, двенадцатый управляющий выход устройства управления подключен к второму управляющему входу (k=ln h)-разрядного счетчика, тринадцатый управляющий выход устройства подключен к первому управляющему входу счетчика, четырнадцатый управляющий выход устройства управления подключен к третьему внешнему управляющему выходу устройства, первый, второй, -, последний n-разрядные информационные выходы (k=Ln h)-разрядного счетчика соответственно подключены к первому, второму, -, последнему адресным входам n-разрядного постоянного запоминающего устройства, n-разрядная группа информационных выходов n-разрядного постоянного запоминающего устройства соответственно подключена к третьей n-разрядной группе информационных входов мультиплексора, первая n-разрядная группа информационных входов устройства соответственно подключена к группе n-разрядных информационных входов второго n-разрядного регистра входных данных, группа n-разрядных информационных выходов которого соответственно подключена к первой группе из n информационных входов коммутационной сети и первой n-разрядной группе информационных входов мультиплексора, (n) информационных выходов коммутационной сети подключены соответственно к группе n-разрядных информационных входов третьего n-разрядного регистра, группа n-разрядных информационных выходов которого соответственно подключены к второй n-разрядной группе информационных входов мультиплексора и n-разрядной группе внешних информационных выходов устройства, первая группа n-разрядных информационных выходов мультиплексора соответственно подключена к первой группе (n)-разрядных информационных входов первого 2n-разрядного регистра входного кода, вторая группа n-разрядных информационных выходов мультиплексора соответственно подключена к второй группе из (n)-разрядных информационных входов первого 2n-разрядного регистра входного кода, группа из (2n)-разрядных информационных выходов первого 2n-разрядного регистра входного кода соответственно подключены к 2n-разрядной группе управляющих входов коммутационной сети, первая группа из n информационных входов коммутационной сети подключены соответственно к (n) информационным входам (n/2) коммутаторов первого столбца коммутационной сети, группа (2n) разрядных информационных выходов первого 2n-разрядного регистра соответственно подключены к (2n) управляющим входам коммутационной сети, причем, внутри коммутационной сети первый выход группы n-разрядных информационных выходов второго n-разрядного регистра входных данных подключен к любому (j-му) входу любого (i-го) коммутатора первого столбца, а информационный (j-й) выход (i-го) коммутатора последнего столбца подключен к первому информационному входу n-разрядной группе информационных входов третьего n-разрядного регистра выходных данных, второй выход n-разрядной группы информационных выходов второго n-разрядного регистра входных данных подключен к любому свободному (j-му) входу любого (k-го) коммутатора первого столбца, а информационный (j-й) выход (k-го) коммутатора последнего столбца подключен к второму информационному входу n-разрядной группе информационных входов третьего n-разрядного регистра выходных данных, -, n-информационный выход группы n-разрядных информационных выходов второго n-разрядного регистра входных данных подключен к последнему свободному информационному входу (m-го) коммутатора, а последний свободный информационный выход (m-го) коммутатора последнего столбца подключен к последнему информационному входу n-разрядной группе информационных входов третьего n-разрядного регистра выходных данных, первый информационный выход (i-го) коммутатора первого столбца подключен к любому (j-му) свободному информационному входу (k-го) коммутатора второго столбца, а (j-й) информационный вход (k-го) коммутатора последнего столбца подключен к первому информационному выходу (i-го) коммутатора второго столбца, второй информационный выход (i-го) коммутатора первого столбца подключен к любому (l-му) свободному информационному входу (f-го) коммутатора второго столбца, а (l-й) информационный вход (f-го) коммутатора последнего столбца подключен к второму информационному выходу (i-го) коммутатора второго столбца, -, последний свободный информационный выход (i-го) коммутатора первого столбца подключен к последнему (j-му) свободному информационному входу (k-го) коммутатора второго столбца, а последний свободный (j-й) информационный вход (k-го) коммутатора последнего столбца подключен к последнему свободному информационному выходу (i-го) коммутатора второго столбца, где j = 1,2, k = 1,2...,n i = 1,2, l = 1,2, f = 1,2,...,n, первый информационный выход первого коммутатора второго столбца подключен к первому информационному входу первого коммутатора третьего столбца, второй информационный выход первого коммутатора второго столбца подключен к второму информационному входу первого коммутатора третьего столбца, первый информационный выход второго коммутатора второго столбца подключен к первому информационному входу второго коммутатора третьего столбца, второй информационный выход второго коммутатора второго столбца подключен к второму информационному входу второго коммутатора третьего столбца, первый информационный выход последнего коммутатора второго столбца подключен к первому информационному входу последнего коммутатора третьего столбца, второй информационный выход последнего коммутатора второго столбца подключен к второму информационному входу последнего коммутатора третьего столбца, первый информационный выход из 2n-разрядной группы информационных выходов первого 2n-разрядного регистра входного кода подключен к любому свободному управляющему входу любого (i-го) коммутатора первого столбца, а (2n) информационный выход из 2n-разрядной группы информационных выходов первого 2n-разрядного регистра входного кода подключен к управляющему входу (i-го) коммутатора последнего столбца, второй информационный выход из 2n-разрядной группы информационных выходов первого 2n-разрядного регистра входного кода подключен к любому свободному управляющему входу любого (j-го) коммутатора первого столбца, а 2n-1 информационный выход из 2n-разрядной группы информационных выходов первого 2n-разрядного регистра входного кода подключен к управляющему входу (j-го) коммутатора последнего столбца, -, (n-й) информационный выход из 2n-разрядной группы информационных выходов первого 2n-разрядного регистра входного кода подключен к последнему свободному управляющему входу коммутатора первого столбца, а n+1 информационный выход из 2n-разрядной группы информационных выходов 2n-разрядного регистра входного кода подключен к последнему свободному управляющему входу коммутатора последнего столбца.

Устройство, показанное на фиг. 1, содержит первый 2n-разрядный регистр входного кода 1 с первым входом управления записью данных, вторым входом установки в 0 и двумя группами n-разрядных информационных входов и группой 2n-разрядных информационных выходов, второй n-разрядный регистр входных данных 2 с первым входом управления записью данных и вторым входом установки в 0, группой n-разрядных информационных входов и группой n-разрядных информационных выходов, третий n-разрядный регистр выходных данных 3 с первым входом управления записью данных и вторым входом установки в 0, коммутационную сеть 4 с первой группой n-информационных входов, второй группой (2n)-управляющих входов и третьей группой n-информационных выходов, состоящую из (2n)-управляемых коммутаторов с двумя информационными входами, двумя информационными выходами и одним входом управления, мультиплексор 5 с первой группой n-разрядных информационных входов, второй группой n-разрядных информационных входов, третьей группой n-разрядных информационных входов, первой группой n-разрядных информационных выходов, второй группой n-разрядных информационных выходов и первым, вторым, третьим управляющими входами, n-разрядное ПЗУ 6 емкостью h ячеек с первым входом управления чтения, вторым входом установки в начальное состояние и n-разрядной группой информационных выходов, k-разрядный счетчик 7 адреса ПЗУ (ST) с первым счетным входом и вторым входом установки в 0 и группой n-разрядным информационным выходом, устройство управления 8 с (0/t) адресными входами, шестью внешними управляющими входами и тринадцатью управляющими выходами, группу информационных входов данных устройств 9(0) - 9(n), группу 10(0) - 10(t) внешних адресных входов устройства, управляющий вход устройства 11, управляющий вход "готовность устройства" устройства 12, управляющий вход "режим установки" устройства 13, управляющий вход "режим обработки" устройства 14, управляющий выход "прием данных" устройства 15, управляющий выход "запрос данных" устройства 16, управляющий выход "конец обработки" устройства 17, группу информационных выходов устройства 18(0) - 18(n), управляющий вход устройства 19 "конец работы", управляющий вход устройства 21 "режим обратной обработки", управляющий выход устройства 22 "режим установки начального кода", управляющий выход устройства 23 "выбор режима обработки", группа 10 входов устройства подключена к группе внешних адресных входов модуля 8, 11 вход устройства подключен к первому входу устройства управления 8, 19 вход устройства подключен к второму входу устройства управления 8, 21 вход устройства подключен к 3 входу устройства управления 8, 14 вход устройства подключен к 4 входу устройства управления 8, 13 вход устройства подключен к 5 входу устройства управления 8 и 17 вход устройства подключен к 6 входу модуля 8, управляющий выход 1 модуля 8 подключен к 3 первому управляющему входу мультиплексора 5, второй выход модуля 8 подключен к второму управляющему входу мультиплексора 5, третий выход модуля 8 подключен к первому управляющему входу мультиплексора 5, четвертый выход модуля 8 подключен к первому управляющему входу второго n-разрядного регистра входных данных, пятый выход модуля 8 подключен к первому управляющему входу первого 2n-разрядного регистра входного кода 1, шестой управляющий выход модуля 8 подключен к второму управляющему входу второго n-разрядного регистра входного кода, седьмой управляющий выход модуля 8 подключен к выходу 15 устройства, восьмой управляющий выход модуля 8 подключен к выходу 16 устройства, девятый управляющий выход модуля 8 подключен к первому управляющему входу третьего n-разрядного регистра 3 выходных данных, десятый управляющий выход модуля 8 подключен к первому управляющему входу ПЗУ 6, одиннадцатый управляющий выход модуля 8 подключен к второму управляющему входу ПЗУ 6, второму управляющему входу регистра 1 и второму управляющему входу n-разрядного третьего регистра 3 выходного кода, двенадцатый управляющий выход модуля 8 подключен к второму управляющему входу счетчика 7, тринадцатый управляющий выход модуля 8 подключен к первому управляющему входу счетчика 7, k-информационных выходов счетчика 7 соответственно подключены к k-адресным входам ПЗУ 6, n-информационных выходов ПЗУ 6 соответственно подключены к третьей n-разрядной группе информационных входов мультиплексора 5, группа 9 информационных входов устройства соответственно подключена к группе n-разрядных информационных входов второго n-разрядного регистра 2 входных данных, группа n-разрядных информационных выходов которого соответственно подключены к первой группе из n-информационных входов коммутационной сети 4 и первой группе n-разрядных информационных входов мультиплексора 5, третья группа из n информационных выходов коммутационной сети 4 соответственно подключены к группе n-разрядных информационных входов третьего n-разрядного регистра выходного кода 3, информационные выходы которого соответственно подключены к второй группе n-разрядных информационных входов мультиплексора 5 и группе информационных выходов 18 устройства, первая n-разрядная группа информационных выходов мультиплексора 5 соответственно подключена к первой группе n-разрядных информационных входов первого 2n-разрядного регистра 1 входного кода, вторая n-разрядная группа информационных выходов мультиплексора 5 соответственно подключена к второй группе n-разрядных информационных входов первого 2n-разрядного регистра 1 входного кода, группа n-разрядных информационных выходов регистра 1 соответственно подключены к второй группе из (2n) управляющих входов коммутационной сети 4, информационные выходы n/2 коммутаторов первого столбца подключены к информационным входам n/2 коммутаторов второго столбца, информационные выходы n/2 коммутаторов второго столбца подключены к информационным входам n/2 коммутаторов третьего столбца, информационные выходы n/2 коммутаторов третьего столбца подключены к информационным входам n/2 коммутаторов четвертого столбца, информационные выходы n/2 коммутаторов четвертого столбца подключены к информационным входам третьего n-разрядного регистра 3 выходного кода, группа n-разрядных информационных выходов регистра 1 соответственно подключены к второй группе из (2n) управляющих входов коммутационной сети 4, причем, внутри коммутационной сети первый выход n-разрядной группы информационных выходов второго n-разрядного регистра входных данных 2 подключен к любому (j-му) входу любого (i-го) коммутатора первого столбца, а информационный (j-й) выход (i-го) коммутатора последнего столбца подключен к первому информационному входу n-разрядного регистра 3 выходного кода, второй выход n-разрядной группы информационных выходов второго n-разрядного регистра входных данных 2 подключен к любому свободному (j-му) входу любого (k-го) коммутатора первого столбца, а информационный (j-й) выход (k-го) коммутатора последнего столбца подключен к второму информационному входу n-разрядной группы информационных входов n-разрядного регистра 3 выходного кода, -, n-информационный выход n-разрядной группы информационных выходов второго n-разрядного регистра входных данных подключен к последнему свободному информационному входу (m-го) коммутатора, а последний свободный информационный выход (m-го) коммутатора последнего столбца подключен к последнему информационному входу n-разрядной группы информационных входов n-разрядного регистра 3 выходного кода, (j-й) информационный вход (k-го) коммутатора последнего столбца подключен к первому информационному выходу (i-го) коммутатора второго столбца, второй информационный выход (i-го) коммутатора первого столбца подключен к любому (l-му) свободному информационному входу (f-го) коммутатора второго столбца, а (l-й) информационный вход (f-го) коммутатора последнего столбца подключен к второму информационному выходу (i-го) коммутатора второго столбца, -, последний свободный (j-й) информационный вход (k-го) коммутатора последнего столбца подключен к последнему свободному информационному выходу (i-го) коммутатора второго столбца, первый информационный выход первого коммутатора второго столбца подключен к первому информационному входу первого коммутатора третьего столбца, второй информационный выход первого коммутатора второго столбца подключен к второму информационному входу первого коммутатора третьего столбца, первый информационный выход второго коммутатора второго столбца подключен к первому информационному входу второго коммутатора третьего столбца, второй информационный выход второго коммутатора второго столбца подключен к второму информационному входу второго коммутатора третьего столбца, первый информационный выход последнего коммутатора второго столбца подключен к первому информационному входу последнего коммутатора третьего столбца, второй информационный выход последнего коммутатора второго столбца подключен к второму информационному входу последнего коммутатора третьего столбца, первый информационный выход регистра 1 подключен к любому свободному управляющему входу любого (i-го) коммутатора первого столбца, а 2n информационный выход второго n-разрядного регистра 2 входных данных подключен к управляющему входу (i-го) коммутатора последнего столбца, второй информационный выход регистра 1 подключен к любому свободному управляющему входу любого (j-го) коммутатора первого столбца, а 2n-1 информационный выход второго n-разрядного регистра 2 входных данных подключен к управляющему входу (j-го) коммутатора последнего столбца, -, (n-й) информационный выход регистра 1 подключен к последнему свободному управляющему входу коммутатора первого столбца, а n+1 информационный выход второго n-разрядного регистра 2 входных данных подключен к последнему свободному управляющему входу коммутатора последнего столбца.

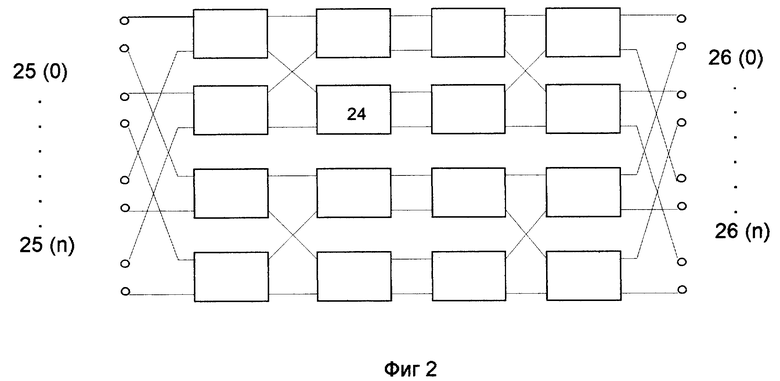

На фиг. 2 показан вариант организации коммутационной сети из коммутационных элементов, показанных на фиг. 3. На фиг. 2 группа входов 25 является первой группой из (n) информационных входов коммутационной сети, а группа выходов 26 - третья группа из (n) информационных выходов коммутационной сети. Управляющие входы коммутационных элементов сети на фиг. 2 не показаны. По умолчанию считается, что каждый элемент коммутационной сети имеет один управляющий вход, набор которых является группой управляющих входов коммутационной сети.

Используемое в данном устройстве ПЗУ и система его программирования являются стандартными устройствами, подробно описаны в современной научно-технической литературе и широко применяются сегодня в инженерной практике. Поэтому данный узел ПЗУ заявляемого устройства далее детально не рассматривается из-за тривиальности технического решения.

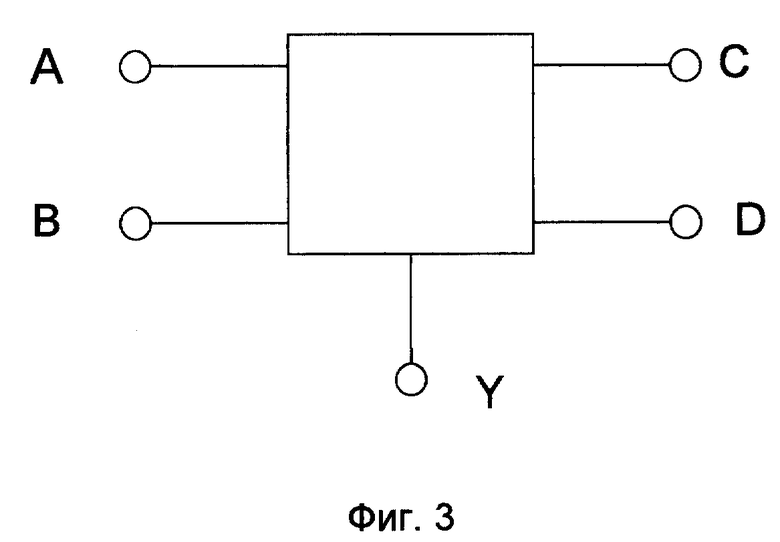

Коммутационный элемент (фиг. 3) обеспечивает функции коммутации, описываемые следующими булевыми функциями:

C=AY ∨ BY, D=AY ∨ BY, где A, B - однобитные n-разрядные информационные входы, C, D - однобитные информационные выходы, Y - управляющий вход коммутационного элемента. Ввиду тривиальности технического решения коммутационного элемента более подробная схема не приводится.

Устройство работает следующим образом.

Устройство имеет три режима работы: начальной установки, режим статический обработки данных, режим динамической обработки данных. При статическом режиме работы управляющий код схемы коммутации коммутационной сети устанавливается из ПЗУ. Этот режим служит для обработки первого пакета данных при прямой и обратной обработки. Динамический режим обработки информации выполняется после обработки первого пакета данных. При этом режиме код схемы коммутации коммутационной сети формируется на основе поступающих данных.

1. Режим начальной установки.

Данный режим включается при поступлении сигнала "режим установки" 13 на блок управления 8. По сигналу 13 блок управления 8 формирует сигналы сброса модулей 1, 2, 3, 7 в "0". Установка начальной схемы коммутации в коммутационной сети выполняется следующим образом. При поступлении сигнала 11, который разрешает начать установку счетчика 7 устройством управления 8, на группе адресных входов 10 устройства управления 8 предварительно должен быть установлен k-разрядный двоичный код адреса ячейки ПЗУ, в котором находится код начальной установки схемы коммутации.

Исходя из значения кода на входах 10 блок управления 8 устанавливает в счетчик 7 требуемый адрес ячейки ПЗУ, содержащий начальный код установки коммутаторов в сети 4. Эта установка выполняется путем подачи на счетный управляющий вход модуля 7 соответствующей серии счетных импульсов. Далее блок управления 8 устанавливает сигнал "чтение", по которому производится считывание данных из ячейки ПЗУ по адресу, который содержится в счетчике 7, одновременно с этим выдается сигнал настройки на модуль 5, чем обеспечивается коммутация информационных выходов ПЗУ через модуль 5 на (0-n) входы первого 2n разрядного регистра входного кода 1. По окончанию переходных процессов в ПЗУ и модуля 5 и записи данных в первый 2n разрядный регистр входного кода 1 на вторую n-разрядную группу информационных входов из (2n) управляющих входов коммутационной сети 4 поступит 2n разрядный код управления коммутации, который изменяет схему коммутации информационных каналов в сети 4. После этого, блок управления 8 формирует сигнал сброса регистра ST 7. После сброса регистра ST 7, блок управления 8 формирует сигнал 12 для сообщения о переводе работы устройства в режим готовности к обработки информации.

2. Режим статической обработки данных:

Выбор режима производится при отсутствии сигнала 23. Затем происходит перевод устройства в режим готовности при поступлении в блок управления 8 сигнала 14. При отсутствии сигнала 14 устройство находится в состоянии ожидания. При наличии сигнала 14 блок управления 8 разрешает запись входных данных, поступивших на n-разрядные информационные входы 9(0)-9(n) в второй n-разрядный регистр входных данных. Затем с выходов [O/n] группы n-разрядных информационных входов второго n-разрядного регистра входных данных данные поступают на обработку в коммутационную сеть 4 на входы [O/n]. После обработки данных в коммутационной сети 4 на выходы [O/n] сети формируется [O/n] разрядный результат, который поступают на вход регистра RG3. Устройство управления вырабатывает сигнал записи данных в RG3. Данные после обработки в коммутационной сети 4 не изменяют свое начальное значение, а изменяется только позиционная организация данных.

Если необходимо изменить схему коммутации в коммутационной сети 4, следует выбрать новый код коммутации из ПЗУ 6. По сигналу 13 блок управления 8 формирует сигналы сброса модулей 1, 2, 3, 7 в "O". Установка новой схемы коммутации в коммутационной сети выполняется следующим образом. При поступлении сигнала 11, который разрешает начать установку счетчика 7 устройством управления 8, на группе адресных входов 10 устройства управления 8 предварительно должен быть установлен k-разрядный двоичный код адреса ячейки ПЗУ, в котором находится код начальной установки схемы коммутации.

Исходя из значения кода на входах 10 блок управления 8 устанавливает в счетчик 7 требуемый адрес ячейки ПЗУ, содержащий новый код установки коммутаторов в сети 4. Эта установка выполняется путем подачи на счетный управляющий вход модуля 7 соответствующей серии счетных импульсов. Далее блок управления 8 устанавливает сигнал "чтение", по которому производится считывание данных из ячейки ПЗУ по адресу, который содержится в счетчике 7, одновременно с этим выдается сигнал настройки на модуль 5, чем обеспечения коммутация информационных выходов ПЗУ через модуль 5 на (0-n) входы регистра 1.

В итоге происходит смена значений в регистре 1 и, соответственно, происходит смена схемы коммутации в коммутационной сети 4.

После установки новой схемы коммутации в коммутационной сети 4 блок управления 8 выдает сигнал 16. Если данные не поступили на n-разрядные информационные входы 9(0)-9(n) устройства, то блок управления 8 формирует сигналы 16 и 19 и производится сброс всей системы в исходное состояние. Если данные поступили на n-разрядные информационные входы 9(0)-9(n), то блок управления 8 устанавливает сигнал 14 и происходит обработка следующего пакета данных.

3. Режим динамической обработки данных:

Выбор режима производится формированием сигнала 23 блоком управления 8. Затем происходит перевод устройства в режим готовности при поступлении в блок управления 8 сигнала 14. При отсутствии сигнала 14 устройство находится в состоянии ожидания. При наличии сигнала 14 блок управления 8 разрешает запись входных данных, поступивших на n-разрядные информационные входы 9(0)-9(n) во второй n-разрядный регистр входных данных. Одновременно с записью входных данных в второй n-разрядный регистр входных данных выполняется запись этих же данных с выхода второй n-разрядный регистр входных данных в (0/n) разряды регистра 1 через модуль 5. Затем с выходов [0/n] второго n-разрядного регистра входных данных данные поступают на обработку в коммутационную сеть 6 на входы [0/n]. После обработки данных в коммутационной сети 6 на выходы [0/n] сети формируется [0/n] разрядный результат, который поступает на вход регистра RG3. Устройство управления вырабатывает сигнал записи данных в RG3. Данные после обработки в коммутационной сети 6 не изменяют свое начальное значение, а изменяется только позиционная организация данных.

После записи данных в регистр 3 эти данные с его информационных выходов поступают на 18(0)-18(n) информационные выходы устройства и одновременно через модуль 5 на (n+1/m) входы регистра 1 и по сигналу записи данных выполняется их запись в регистр 1. В итоге происходит смена значений в регистре 1 и, соответственно, происходит смена схемы коммутации в коммутационной сети 4.

После установки новой схемы коммутации в коммутационной сети 4 блок управления 8 выдает сигнал 16. Если данные не поступили на n-разрядные информационные входы 9(0)-9(n) устройства, то блок управления 8 формирует сигналы 16 и 19 и производится сброс всей системы в исходное состояние. Если данные поступили на n-разрядные информационные входы 9(0)-9(n), то блок управления 8 устанавливается сигнал 14 и происходит обработка следующего пакета данных.

Таким образом, в режиме статической обработки данных обеспечивается перестановка элементов входного вектора на новые позиционные места в соответствии с топологией внутренних связей в коммутационной сети и заданным кодом управления коммутацией, чем поддерживается реализация различных типов операций конкатенации. В режиме динамической обработки управление коммутационной сетью обеспечивается данными - код управления коммутацией формируется из входного данного и результата предыдущего шага обработки. Тем самым обеспечиваются более широкие функциональные возможности устройства по сравнению с аналогом.

На фиг. 2 приведен частный случай выполнения коммутационной сети.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2000 |

|

RU2173934C1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ | 2000 |

|

RU2173933C1 |

| Многофункциональная ячейка однородной структуры | 1989 |

|

SU1663609A1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ С ЦИФРОВОЙ ПЕРЕСТРОЙКОЙ ПЕРИОДА | 2000 |

|

RU2170490C1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ С ПЕРЕМЕННЫМ МОДУЛЕМ СЧЕТА | 2000 |

|

RU2179784C2 |

| ЦИФРОВАЯ КОММУТАЦИОННАЯ СИСТЕМА | 1998 |

|

RU2147160C1 |

Изобретение относится к вычислительной технике и может быть использовано при решении задач информационно-поисковой и логической обработки данных в составе векторных ЭВМ и систем и форматирования данных. Техническим результатом является расширение функциональных возможностей устройства за счет обеспечения возможности динамического управления коммутаторами коммутационной сети с данными, поступающими на обработку. Для этого устройство коммутации содержит коммутационную сеть, разрядные регистры, мультиплексор, устройство управления и разрядное постоянное запоминающее устройство с ячейками памяти. 3 ил.

Устройство коммутации, содержащее коммутационную сеть, состоящую из коммутаторов, отличающееся тем, что в устройство коммутации введены первый разрядный регистр входного кода с первым входом установки в нуль и двумя группами разрядных информационных входов, второй разрядный регистр входных данных с информационными входами, с первым входом управления записью данных и вторым входом установки в нуль, третий разрядный регистр выходных данных с первым входом управления записью данных и вторым входом установки в нуль, мультиплексор с тремя группами разрядных информационных входов, двумя группами информационных разрядных выходов и тремя управляющими входами, разрядное постоянное запоминающее устройство с ячейками памяти, с первым входом управления чтения данных из ячеек памяти, вторым входом установки в начальное состояние и разрядной группой адресных входов, разрядный счетчик адреса с первым счетным входом и вторым входом установки в нуль, устройство управления с разрядной группой адресных входов, восемью управляющими входами и четырнадцатью управляющими выходами, вторая группа информационных входов устройства коммутации подключена к разрядной группе адресных входов устройства управления, с первого по восьмой управляющие входы устройства коммутации подключены соответственно к первому - восьмому управляющим входам устройства управления, первый управляющий выход устройства управления подключен к третьему управляющему входу мультиплексора, второй управляющий выход устройства управления подключен к второму управляющему входу мультиплексора, третий управляющий выход устройства управления подключен к первому управляющему входу мультиплексора, четвертый управляющий выход устройства управления подключен к первому управляющему входу второго разрядного регистра входных данных, пятый управляющий выход устройства управления подключен к первому входу управления записью данных первого разрядного регистра входного кода, шестой управляющий выход устройства управления подключен ко второму входу установки в нуль второго разрядного регистра входных данных, седьмой управляющий выход устройства управления подключен к первому управляющему выходу устройства коммутации, восьмой управляющий выход устройства управления подключен ко второму управляющему выходу устройства коммутации, девятый управляющий выход устройства управления подключен к первому входу управления записью данных третьего разрядного регистра выходных данных, десятый управляющий выход устройства управления подключен к первому входу управления чтения данных из ячеек памяти постоянного запоминающего устройства, одиннадцатый управляющий выход устройства управления подключен ко второму входу установки в начальное состояние постоянного запоминающего устройства, второму входу установки в нуль первого разрядного регистра входного кода и второму входу установки в нуль третьего разрядного регистра выходных данных, двенадцатый управляющий выход устройства управления подключен ко второму входу установки в нуль разрядного счетчика адреса, тринадцатый управляющий выход устройства управления подключен к первому счетному входу разрядного счетчика адреса, четырнадцатый управляющий выход устройства управления подключен к третьему управляющему выходу устройства коммутации, с первого по последний выходы разрядного счетчика адреса подключены соответственно к разрядной группе адресных входов постоянного запоминающего устройства, разрядная группа информационных выходов упомянутого постоянного запоминающего устройства подключена к третьей группе разрядных информационных входов мультиплексора, первая разрядная группа информационных входов устройства коммутации подключена соответственно к информационным входам второго разрядного регистра входных данных, информационные выходы которого подключены соответственно к информационным входам коммутационной сети и первой разрядной группе информационных входов мультиплексора, информационные выходы коммутационной сети подключены соответственно к информационным входам третьего разрядного регистра выходных данных, информационные входы которого соответственно подключены ко второй группе разрядных информационных входов мультиплексора и разрядной группе информационных выходов устройства коммутации, первая группа информационных разрядных выходов мультиплексора соответственно подключена к первой группе разрядных информационных входов первого разрядного регистра входного кода, вторая группа информационных разрядных выходов мультиплексора соответственно подключена ко второй группе разрядных информационных входов первого разрядного регистра входного кода, информационные выходы которого подключены к управляющим входам коммутационной сети.

| Р.Хокни и др | |||

| Параллельные ЭВМ | |||

| - М.: Радио и связь, 1986, с.171, рис.3.25 | |||

| Коммутатор | 1986 |

|

SU1314332A2 |

| УСТРОЙСТВО КОММУТАЦИИ ДЛЯ МНОГОПРОЦЕССОРНОЙ СИСТЕМЫ | 1989 |

|

RU2027220C1 |

| RU 94029855 A1, 10.06.96. | |||

Авторы

Даты

1999-10-10—Публикация

1997-06-11—Подача