Изобретение относится к области цифровой и импульсной техники и предназначено для подавления влияния помех в линиях передачи цифровой информации.

Известны кабельные приемные усилители [1], предназначенные для подавления помех в проводных линиях передачи информации, содержащие инвертор на передающей стороне, трехпроводную линию связи и сравнивающее устройство на приемной стороне. Недостатком подобных устройств является то, что при приеме полезного сигнала с помехой, помеха подавляется не полностью из-за свойств дифференциального каскада, входящего в состав приемного усилителя. Недостаток такого рода устройств иллюстрируется временными диаграммами, представленными в данной заявке на фиг. 3, где показано, что при приближении амплитуды напряжения помехи (Uп) к значению питающего напряжения (Eп), помеха не подавляется из-за того, что: помеха является синфазным сигналом для дифференциального каскада, при приближении синфазного сигнала к значению питающего напряжения (Eп) дифференциального каскада коэффициент ослабления синфазного сигнала уменьшается и помеха усиливается усилителем. В производственных условиях помеха может превышать значение питающего напряжения дифференциального усилителя, что еще больше усиливает действие рассмотренного недостатка. Таким образом недостатком аналога является наличие приемного усилителя.

Наиболее близким к предлагаемому техническому решению является выбранный в качестве прототипа приемник биимпульсного сигнала с обнаружением ошибок [2] , содержащий два D-триггера, два элемента И и сумматор по модулю два. Входы D и С первого триггера являются информационным и тактовым входами устройства соответственно. Первый вход сумматора по модулю два подключен ко входу D первого триггера, а второй вход - к инверсному выходу первого триггера. Выход сумматора по модулю два подключен ко входам первого и второго элементов И. Первый элемент И является детектором ошибок и его второй вход подключен к тактовому входу, а его выход является выходом сигнала ошибок устройства. Второй элемент И является детектором нулей, второй его вход подключен к инверсному тактовому входу устройства, а выход - ко входу S второго триггера.

Данное устройство осуществляет лишь регистрацию ошибок и не осуществляет их коррекцию. Для передачи информации кроме информационной линии необходимы две взаимно инверсные тактовые линии, которые тоже в свою очередь подвержены влиянию помех. Поэтому это устройство не может быть использовано в условиях действия сильных помех (например, в производственных цехах). Кроме того, прототип требует для своей работы синхронизацию информационного сигнала с тактовыми импульсами, а при использовании информационного сигнала от датчика перемещения информационный сигнал затруднительно синхронизировать с тактовыми импульсами. Таким образом, недостатками прототипа являются: отсутствие элементов и соединений, осуществляющих коррекцию ошибок; отсутствие элементов и соединений, обеспечивающих помехозащиту в цепях передачи тактовых сигналов; невозможность работы с датчиками (например, перемещения), не имеющими тактового выхода.

Поставлена задача - повысить помехозащищенность линии передачи. Поставленная задача решается за счет того, что в устройство для подавления помех в линии передачи бинарных сигналов, содержащее два триггера, согласно изобретению дополнительно введены два диода и инвертор, триггеры выполнены в виде RS-триггеров, а линия передачи информации между передающей и приемной частями устройства выполнена в виде трехпроводной линии, причем выходы первого триггера соединены со входами второго триггера, входы первого триггера соединены с прямым и инверсным проводами линии передачи информации и каждый из этих входов соединен с положительной шиной источника питания через диод, подключенный анодом ко входу триггера, а катодом к шине источника питания, а выходами устройства являются выходы второго триггера.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается тем, что два триггера выполнены в виде RS-триггеров, причем входы первого RS-триггера непосредственно соединены с прямым и инверсным проводами линии передачи информации, а выходы первого RS-триггера непосредственно соединены со входами второго RS-триггера, кроме того в заявляемом устройстве дополнительно введены два диода, а также инвертор на передающей стороне. Таким образом, заявляемое устройство соответствует критерию изобретения "новизна".

Сравнение заявляемого решения с другими техническими решениями показывает, что в известных устройствах отсутствует непосредственное соединение двух триггеров, что позволяет сделать вывод о соответствии технического решения критерию "изобретательский уровень".

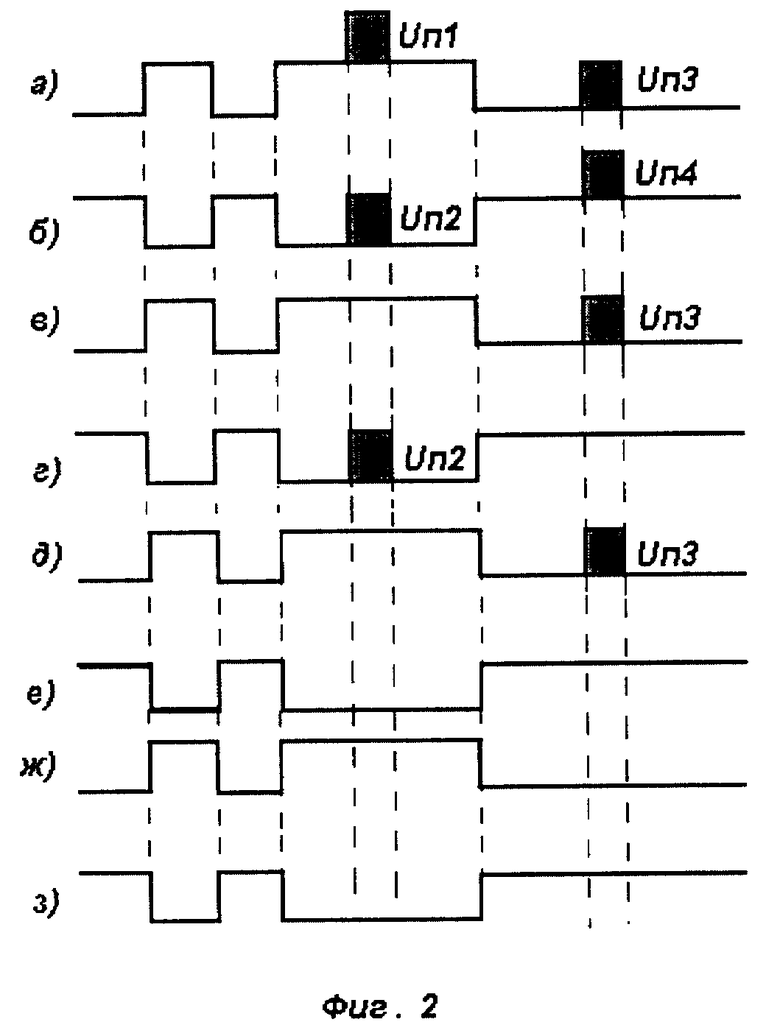

Сущность изобретения поясняется чертежами, где на фиг. 1 показана принципиальная схема устройства, на фиг. 2 - графики, поясняющие работу устройства, на фиг. 3 показано, каким образом помеха проходит на выход аналога изобретения, а на фиг. 4 представлена принципиальная схема прототипа.

Устройство для подавления помех в линии передачи бинарных сигналов (фиг. 1) содержит инвертор 1 на передающей стороне, трехпроводную линию связи, два непосредственно последовательно соединенных RS-триггера 2, 3 и два диода 4, 5 на приемной стороне. Выходы первого триггера 2 соединены со входами второго триггера 3. Входы первого триггера 2 соединены с прямым и инверсным проводами линии передачи информации. Каждый из входов первого триггера 2 соединен с положительной шиной источника питания через соответствующий диод 4, 5. Каждый диод подключен анодом ко входу первого триггера 2, а катодом к положительной шине источника питания. Выходами устройства являются выходы второго триггера 3.

Заявляемое устройство работает следующим образом: пусть в линии передачи информации действует помеха Uп1, Uп2 (фиг. 2), тогда сигнал помехи Uп1 шунтируется диодом 4 (фиг. 2 в), а сигнал помехи Uп2 переводит первый триггер 2 в режим хранения информации, при котором на выходе этого триггера сохраняется информация о полезном сигнале, который предшествовал появлению помехи Uп1, Uп2 (фиг. 2 ж, з). Пусть в линии передачи действует другая помеха Uп3, Uп4 (фиг. 2), тогда сигнал помехи Uп4 шунтируется диодом 5 (фиг. 2 г), а сигнал помехи Uп3 создает на входах первого триггера 2 запрещенную комбинацию, что ведет к появлению на обоих его выходах высокого логического уровня, что переводит второй триггер 3 в режим хранения информации, при котором на выходе этого триггера сохраняется информация о полезном сигнале, который предшествовал появлению помехи Uп3, Uп4 (фиг. 2 ж, з), таким образом предлагаемое устройство исключает прохождение сигналов помехи Uп1, Uп2, Uп3, Uп4 на выход предлагаемого устройства.

Экспериментальные исследования заявляемого устройства для подавления помех в линии передачи бинарных сигналов показали, что по сравнению с прототипом заявляемое устройство обеспечивает более надежное подавление помех в линии передачи бинарных сигналов и позволяет за счет непосредственно последовательно включенных RS-триггеров намного снизить влияние помех в линии. Например, при длительности фронта срабатывания триггера tф= 20 нс и максимальной частоте передачи tmax=300 Гц, а также при длительности помехи (0,01 - 0,3 мс), влияние помехи ослабляется не менее чем в 10000 раз.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ТЕМПЕРАТУРЫ ВРАЩАЮЩИХСЯ ОБЪЕКТОВ | 1996 |

|

RU2142121C1 |

| СПОСОБ ОБНАРУЖЕНИЯ И АНАЛИЗА РАДИОСИГНАЛОВ | 2005 |

|

RU2296349C9 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ТЕМПЕРАТУРЫ ВРАЩАЮЩИХСЯ ОБЪЕКТОВ | 1995 |

|

RU2110050C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЛЕБАНИЙ ЛОПАТОК ТУРБОМАШИН | 2000 |

|

RU2189567C1 |

| СПОСОБ ИЗМЕРЕНИЯ ПЕРЕМЕЩЕНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2082076C1 |

| СИГНАЛИЗАТОР ПРЕДАВАРИЙНЫХ ДЕФОРМАЦИЙ ЛОПАТОК ТУРБОМАШИН | 2000 |

|

RU2177145C1 |

| СЛЕДЯЩИЙ ИНВЕРТОР С ДВУХПОЛЯРНОЙ ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 2001 |

|

RU2202144C2 |

| УСИЛИТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1998 |

|

RU2172060C2 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 2007 |

|

RU2331098C1 |

| ПЫЛЕУДАРНЫЙ МАСС-СПЕКТРОМЕТР | 1996 |

|

RU2122257C1 |

Изобретение относится к области цифровой и импульсной техники. Устройство для подавления помех в линии передачи бинарных сигналов содержит инвертор 1 на передающей стороне, трехпроводную линию связи, два последовательно соединенных RS-триггера 2 и 3 и два диода 4 и 5 на приемной стороне, причем входы RS-триггера 2 непосредственно соединены с прямым и инверсным проводами линии передачи информации и каждый из этих выводов соединен с положительной шиной источника питания через диод, подключенный анодом к входу триггера 2, а катодом - к положительной шине источника питания. Прямой и инверсный выходы RS-триггера 2 соединены соответственно с R- и S-входами RS-триггера 3, а выходами устройства являются выходы RS-триггера 3. Достигаемым техническим результатом является снижение влияния помех в линиях передачи цифровой информации. 4 ил.

Устройство для подавления помех в линии передачи бинарных сигналов, содержащее два триггера, отличающееся тем, что в него дополнительно введены два диода и инвертор, триггеры выполнены в виде RS-триггеров, а линия передачи информации между передающей и приемной частями устройства выполнена в виде трехпроводной линии, причем выходы первого триггера соединены с входами второго триггера, входы первого триггера - с прямым и инверсным проводами линии передачи информации и каждый из этих входов соединен с положительной шиной источника питания через диод, подключенный анодом к входу триггера, а катодом - к шине источника питания, а выходами устройства являются выходы второго триггера.

| Приемник биимпульсного сигнала с обнаружением ошибок | 1989 |

|

SU1658401A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВОГО СИГНАЛА В ДВУХПРОВОДНУЮ ЛИНИЮ СВЯЗИ | 1992 |

|

RU2019035C1 |

| RU 2002367 C1, 30.10.93 | |||

| US 4475214 A, 02.10.84 | |||

| EP 0902547 A2, 17.03.99. | |||

Авторы

Даты

1999-11-27—Публикация

1998-06-08—Подача