Изобретение относится к вычислительной технике и предназначено для сбора информации от внешних источников и последующей ее обработки для выработки сигналов управления различным корабельным оборудованием, в частности корабельным оружием.

В настоящее время для эффективного использования объектов управления от корабельной управляющей вычислительной системы требуется реализация сложных алгоритмов, для чего необходимо выполнить большое количество вычислений за ограниченное время.

Известна вычислительная система для обработки данных [1], содержащая центральные процессоры, блоки памяти, периферийные процессоры, образующие группу устройств с высокой общей производительностью и внешние унифицированные устройства обмена информацией с внешним исполнительным оборудованием.

Недостатком этой системы является отсутствие возможности обмена информацией между всеми процессорами, что снижает эффективную производительность системы, кроме того, невозможно производить одновременный обмен с внешними абонентами.

Известна также микропроцессорная система [2], состоящая из нескольких микропроцессоров, соединенных посредством системной шины с общей памятью, через которую осуществляется обмен информацией между всеми процессорами. Управление обменом осуществляется распределителем системной шины.

Недостатком этой системы является низкая пропускная способность обмена информацией через общую память, а также отсутствие контроля за состоянием каждого микропроцессора, что ограничивает функциональные возможности и надежность рассмотренной системы.

Известна также микропроцессорная система [3], содержащая микропроцессорные модули, внешнее оперативное запоминающее оперативное (ОЗУ) устройство связи с памятью, блок коммутации и генератор импульсов для синхронизации работы всей системы.

Система имеет ограниченные функциональные возможности и недостаточную надежность в случае отказа отдельных элементов системы.

Известна также многопроцессорная вычислительная система [4], состоящая из нескольких процессоров со своими резидентными ОЗУ и постоянными запоминающими устройствами (ПЗУ), портами ввода-вывода, подключенными к единой системной шине, к которой подключены системное устройство ввода-вывода, системное ОЗУ и ПЗУ.

Недостатком указанной системы является отсутствие средств обеспечения логико-временных диаграмм управления исполнительными устройствами, средств блокировки несанкционированного запуска объектов управления.

Наиболее близкой по технической сущности к предлагаемой корабельной управляющей вычислительной системе является многопроцессорная корабельная система обработки данных [5] , содержащая микропроцессоры, устройства обмена информацией, блоки ввода-вывода, внешние запоминающие устройства, первую и вторую интерфейсные магистрали обмена, адаптер межмагистрального обмена, пульт управления, блоки ввода данных от корабельных источников информации, при этом к первой магистрали подключены через устройства обмена информацией микропроцессоры, вторые входы-выходы которых через блоки ввода-вывода образуют m групп выходов системы на m исполнительных устройств, ко второй магистрали подключены через блок сопряжения два внешних запоминающих устройства, через соответствующие адаптеры дисплей, пульт управления, а также таймер - системный контроллер через третий вход-выход адаптера межмагистрального обмена, к первому входу-выходу которого подключена магистраль, а ко второму входу адаптер ввода данных.

Система-прототип имеет недостаточную надежность в случае отказа отдельных элементов системы (например, адаптера межмагистрального обмена).

Задачей изобретения является создание многопроцессорной корабельной управляющей вычислительной системы с более широкими функциональными возможностями, пространственно-функциональной живучестью и высокой безопасностью управления.

Сущность изобретения заключается в том, что в многопроцессорную корабельную управляющую систему, содержащую блоки ввода данных от корабельных источников информации, блоки ввода-вывода данных в объекты управления, системную интерфейсную магистраль межпроцессорного обмена, а также пульт управления, содержащий блок клавиатуры, введены девять микропроцессорных вычислительных устройств (МПВУ), системная пультовая интерфейсная магистраль, интерфейсные магистрали управления объектами индивидуального наведения (ОИН) левого и правого бортов, интерфейсные магистрали управления объектами группового наведения (ОГН) левого и правого бортов, блоки цифровых следящих устройств (ЦСУ) ОИН левого и правого бортов, блоки ЦСУ для ОГН левого и правого бортов, блоки блокировки цепей стрельбы и аварийного выброса ОИН левого и правого бортов, блоки блокировки цепей стрельбы и аварийного выброса ОГН левого и правого бортов, два дополнительных пульта управления, аналогичных упомянутому пульту управления.

При этом:

первые входы-выходы всех МПВУ соединены с системной интерфейсной магистралью межпроцессорного обмена,

вторые входы-выходы первого, второго и третьего МПВУ, а также входы-выходы всех пультов управления соединены с системной пультовой интерфейсной магистралью,

третьи входы первого, второго и третьего МПВУ образуют соответственно первую, вторую и третью группы входов системы,

вторые входы-выходы четвертого и пятого МПВУ объединены и соединены с интерфейсной магистралью управления ОИН левого борта и входами-выходами блоков ЦСУ ОИН левого борта,

третьи входы-выходы четвертого и пятого МПВУ объединены и соединены с первыми входами-выходами блока блокировки цепей стрельбы и аварийного выброса ОИН левого борта,

вторые входы-выходы шестого и седьмого МПВУ объединены и соединены с интерфейсной магистралью ОИН правого борта и входами-выходами блоков ЦСУ ОИН правого борта,

третьи входы-выходы шестого и седьмого МПВУ объединены и соединены с первыми входами-выходами блока блокировки цепей стрельбы и аварийного выброса ОИН правого борта,

вторые входы-выходы восьмого и девятого МПВУ объединены и соединены с интерфейсными магистралями управления ОГН левого и правого бортов и входами-выходами блоков ЦСУ ОГН левого и правого бортов,

третьи входы-выходы восьмого и девятого МПВУ объединены и соединены с первыми входами-выходами блоков блокировки цепей стрельбы и аварийного выброса ОГН левого и правого бортов,

каждое МПВУ с первого по девятое содержит свои первую и вторую внутренние интерфейсные магистрали, свой микропроцессор, подключенный первым входом-выходом к соответствующей первой внутренней интерфейсной магистрали, а вторым входом-выходом - к соответствующей второй внутренней интерфейсной магистрали, к которой подключен свой блок контроля и автономного управления, свое внешнее ПЗУ, подключенное к входу соответствующего микропроцессора, свое ОЗУ, подключенное к соответствующей первой внутренней интерфейсной магистрали, свой контроллер интерфейсной магистрали межпроцессорного обмена, первый из входов-выходов которого подключен к соответствующей первой внутренней интерфейсной магистрали, а второй является первым входом-выходом соответствующего МПВУ,

каждое МПВУ с первого по третье содержит также свой блок обмена через системную пультовую интерфейсную магистраль, первый из входов-выходов которого подключен к соответствующей второй внутренней интерфейсной магистрали, а второй вход-выход является вторым входом-выходом соответствующего МПВУ, блоки ввода данных от корабельных источников информации, первые входы-выходы которых подключены к соответствующей первой внутренней магистрали, а вторые входы являются третьими входами соответствующего МПВУ,

каждое МПВУ с четвертого по девятое содержит также свой контроллер интерфейсной магистрали управления объектами, первый из входов-выходов которого подключен к соответствующей первой внутренней интерфейсной магистрали, а второй вход-выход является вторым входом-выходом МПВУ с четвертого по девятое, блоки ввода-вывода данных в объекты управления, первые входы-выходы которых подключены к соответствующей первой внутренней магистрали, а вторые входы-выходы являются третьими входами-выходами МПВУ с четвертого по девятый.

Каждый пульт управления в предлагаемой системе содержит первую и вторую группы индикаторов, ключ блокировки цепей старта и ключ блокировки цепи питания, соединенные с блоком клавиатуры, а также два МПВУ пульта управления, каждое из которых содержит свои первую и вторую внутренние интерфейсные магистрали, свой микропроцессор, подключенный первым входом-выходом к соответствующей первой внутренней интерфейсной магистрали, а вторым входом-выходом - к соответствующей второй внутренней интерфейсной магистрали, к которой своим первым входом-выходом подключен свой блок контроля и автономного управления, второй вход-выход которого является вторым входом-выходом соответствующего МПВУ, свое внешнее ПЗУ ко входу соответствующего микропроцессора, свой блок обмена через системную пультовую интерфейсную магистраль, первый из входов-выходов которого подключен к соответствующей первой внутренней интерфейсной магистрали, а второй является первым входом-выходом МПВУ пульта управления, при этом блок клавиатуры одним из входов-выходов подключен к входам соответствующих индикаторов первой группы и второму входу-выходу одного МПВУ данного пульта управления, а другим входом-выходом блок клавиатуры подключен к входам соответствующих индикаторов второй группы и второму входу-выходу другого МПВУ данного пульта управления.

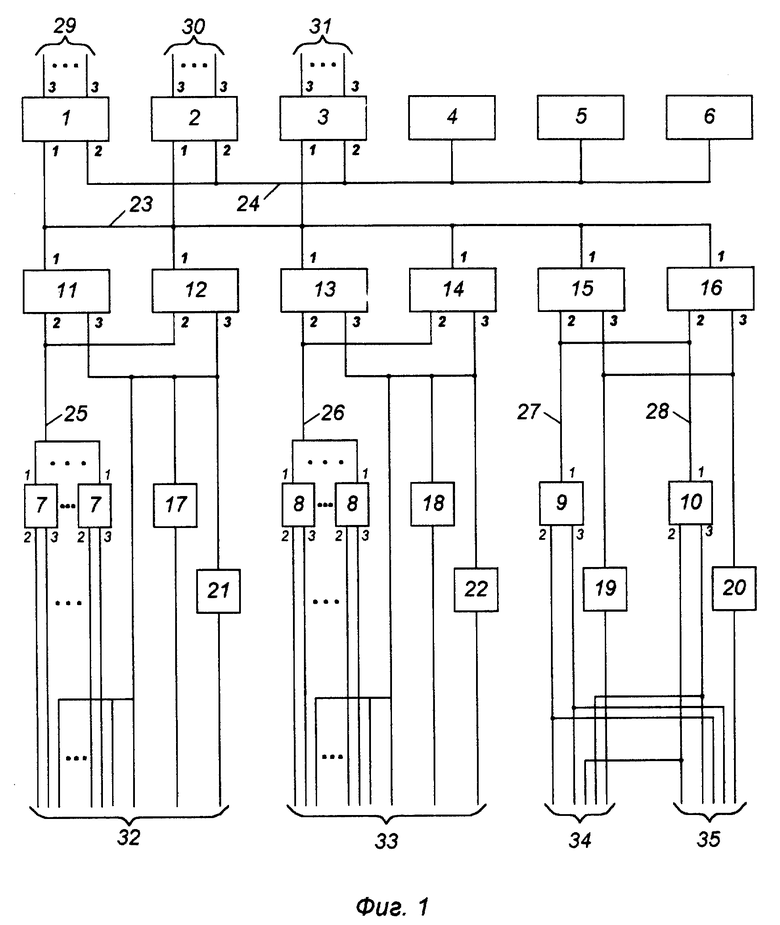

Сущность изобретения поясняется чертежами, на которых изображены:

на фиг. 1 - структурная схема системы;

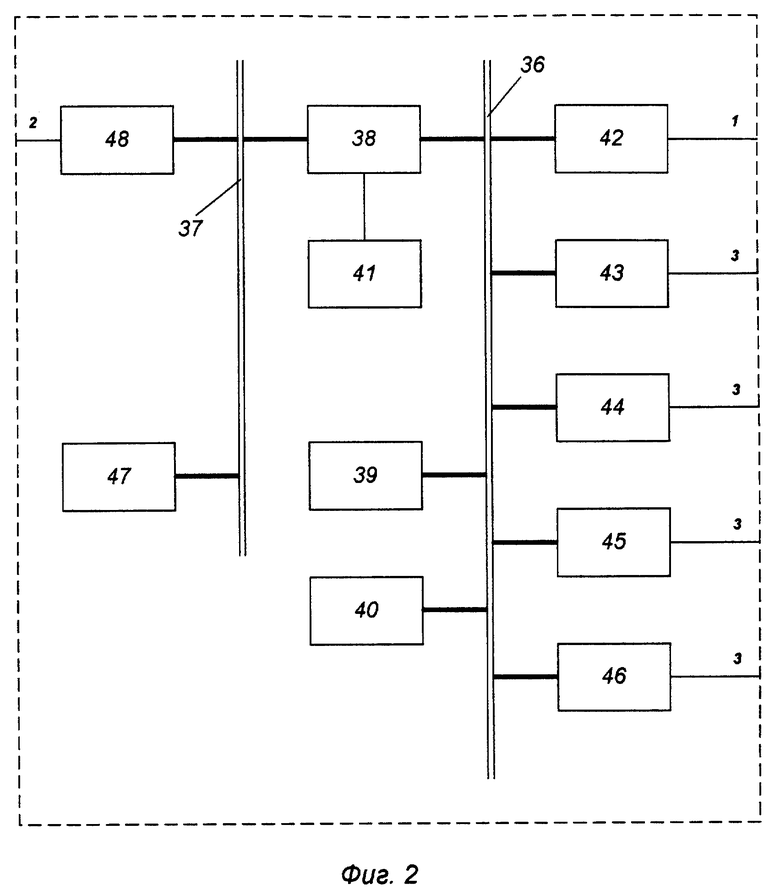

на фиг. 2 - функциональная схема первого-третьего МПВУ;

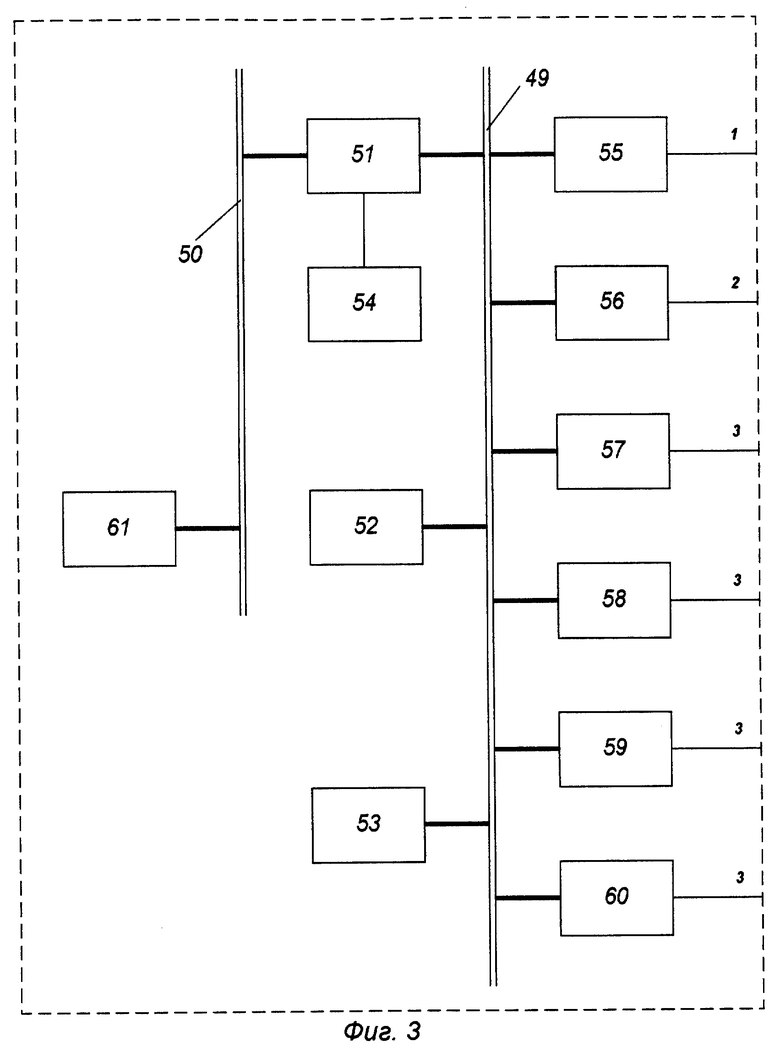

на фиг. 3 - функциональная схема четвертого-девятого МПВУ;

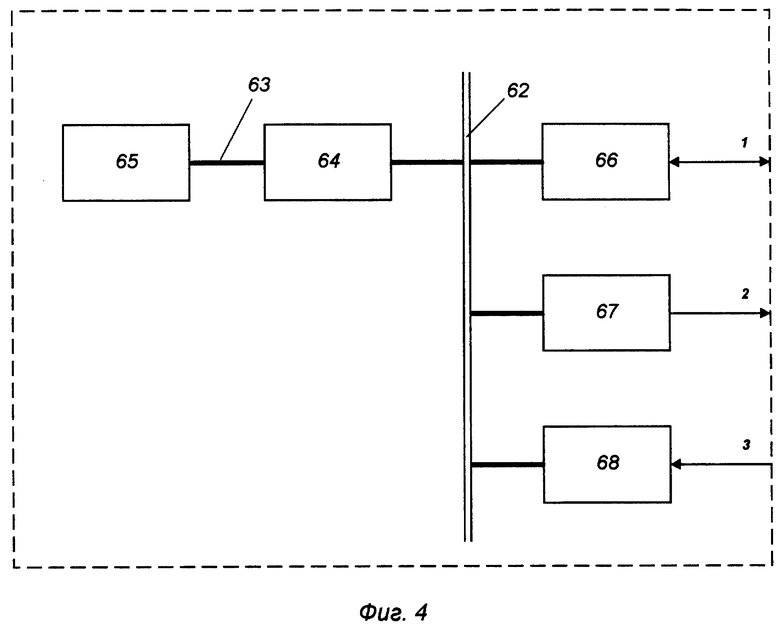

на фиг. 4 - функциональная схема блока ЦСУ;

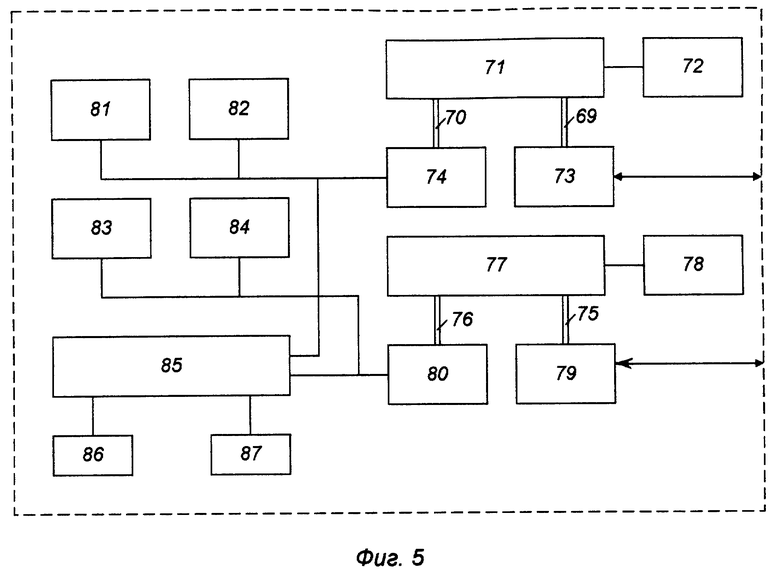

на фиг. 5 - функциональная схема пульта управления.

На фиг. 1 обозначены:

1-3 - первое, второе и третье МПВУ;

4-6 - пульты управления;

7 - блок ЦСУ для ОИН левого борта;

8 - блок ЦСУ для ОИН правого борта;

9 - блок ЦСУ для ОГН левого борта;

10 - блок ЦСУ для ОГН правого борта;

11 - четвертое (основное) МПВУ управления ОИН левого борта;

12 - пятое (резервное) МПВУ управления ОИН левого борта;

13 - шестое (основное) МПВУ управления ОИН правого борта;

14 - седьмое (резервное) МПВУ управления ОИН правого борта;

15 - восьмое (основное) МПВУ управления ОГН левого борта;

16 - девятое (резервное) МПВУ управления ОГН правого борта;

17 - блок блокировки цепей стрельбы и аварийного выброса ОИН левого борта;

18 - блок блокировки цепей стрельбы и аварийного выброса ОИН правого борта;

19 - блок блокировки цепей стрельбы и аварийного выброса ОГН левого борта;

20 - блок блокировки цепей стрельбы и аварийного выброса ОГН правого борта;

21 - блок установки типа ОИН левого борта;

22 - блок установки типа ОИН правого борта;

23 - системная интерфейсная магистраль межпроцессорного обмена;

24 - системная пультовая интерфейсная магистраль;

25 - интерфейсная магистраль управления ОИН левого борта;

26 - интерфейсная магистраль управления ОИН правого борта;

27 - интерфейсная магистраль управления ОГН левого борта;

28 - интерфейсная магистраль управления ОГН правого борта;

29 - первая группа информационных входов системы;

30 - вторая группа информационных входов системы;

31 - третья группа информационных входов системы;

32 - первая группа входов-выходов в ОИН левого борта;

33 - вторая группа входов-выходов в ОИН правого борта;

34 - третья группа входов-выходов в ОГН левого борта;

35 - четвертая группа входов-выходов в ОГН правого борта.

На фиг. 2 обозначены:

36 - первая внутренняя интерфейсная магистраль;

37 - вторая внутренняя интерфейсная магистраль;

38 - микропроцессор;

39 - арифметический сопроцессор;

40 - ОЗУ;

41 - внешнее ПЗУ;

42 - контроллер интерфейсной магистрали 23;

43-46 - блоки ввода данных от корабельных источников информации;

47 - блок контроля и автономного управления;

48 - блок обмена через интерфейсную магистраль 24;

На фиг. 3 обозначены:

49 - первая внутренняя интерфейсная магистраль;

50 - вторая внутренняя интерфейсная магистраль;

51 - микропроцессор;

52 - арифметический сопроцессор;

53 - ОЗУ;

54 - внешнее ПЗУ;

55 - контроллер интерфейсной магистрали 23;

56 - контроллер интерфейсной магистрали 25 (26, 27, 28);

57-60 - блоки ввода-вывода данных в объекты управления;

61 - блок контроля и автономного управления.

На фиг. 4 обозначены:

62 - первая внутренняя интерфейсная магистраль;

63 - вторая внутренняя интерфейсная магистраль;

64 - микропроцессор;

65 - блок контроля и автономного управления;

66 - блок оконечного устройства интерфейсной магистрали 25 (26, 27, 28);

67 - блок управления двигателем;

68 - преобразователь фаза-код.

На фиг. 5 обозначены:

69 - первая внутренняя интерфейсная магистраль;

70 - вторая внутренняя интерфейсная магистраль;

71 - микропроцессор;

72 - внешнее ПЗУ;

73 - блок обмена через интерфейсную магистраль 24;

74 - блок контроля и автономного управления;

75 - первая внутренняя интерфейсная магистраль;

76 - вторая внутренняя интерфейсная магистраль;

77 - микропроцессор;

78 - внешнее ПЗУ;

79 - блок обмена через интерфейсную магистраль 24;

80 - блок контроля и автономного управления;

81, 82 - индикаторы первой группы;

83, 84 - индикаторы второй группы;

85 - блок клавиатуры;

86 - ключ блокировки цепей старта;

87 - ключ блокировки цепи питания.

Предлагаемая многопроцессорная корабельная управляющая вычислительная система (фиг. 1) содержит девять МПВУ 1-3, 11-16, интерфейсные магистрали 25 и 26 управления ОИН левого и правого бортов, интерфейсные магистрали 27 и 28 управления ОГН левого и правого бортов, блоки 7 и 8 ЦСУ для ОИН левого и правого бортов, блоки 9 и 10 ЦСУ для ОГН левого и правого бортов, блоки 17 и 18 блокировки цепей стрельбы и аварийного выброса ОИН левого и правого бортов, блоки 19 и 20 блокировки цепей стрельбы и аварийного выброса ОГН левого и правого бортов, три пульта 4-6 управления, блоки 21 и 22 установки типа ОИН левого и правого бортов.

При этом:

первые входы-выходы МПВУ 1-3 и 11-16 соединены с системной интерфейсной магистралью межпроцессорного обмена;

вторые входы-выходы первого-третьего МПВУ 1-3, а также входы-выходы всех пультов 4-5 управления соединены с системной пультовой интерфейсной магистралью 24;

третьи входы первого-третьего МПВУ 1-3 образуют соответственно первую, вторую и третью группы входов 29, 30, 31 системы;

вторые входы-выходы четвертого и пятого МПВУ 11 и 12 объединены и соединены с интерфейсной магистралью 25 управления ОИН левого борта и входами-выходами блоков 7 ЦСУ ОИН левого борта;

третьи входы-выходы четвертого и пятого МПВУ 11 и 12 объединены и соединены с первыми входами-выходами блока 17 блокировки цепей стрельбы и аварийного выброса ОИН левого борта и первыми входами-выходами блока 21 установки типа ОИН левого борта;

вторые входы-выходы шестого и седьмого МПВУ 13 и 14 объединены и соединены с интерфейсной магистралью управления 26 ОИН правого борта и входами-выходами блоков 8 ЦСУ ОИН правого борта;

третьи входы-выходы шестого и седьмого МПВУ 13 и 14 объединены и соединены с первыми входами-выходами блока 18 блокировки цепей стрельбы и аварийного выброса ОИН правого борта и первыми входами-выходами блока 22 установки типа ОИН правого борта;

вторые входы-выходы восьмого и девятого МПВУ 15 и 16 объединены и соединены с интерфейсными магистралями 27 и 28 управления ОГН левого и правого бортов и первыми входами-выходами блоков 9 и 10 ЦСУ ОГН левого и правого бортов;

третьи входы-выходы восьмого и девятого МПВУ 15 и 16 объединены и соединены с первыми входами-выходами блоков 19 и 20 блокировки цепей стрельбы и аварийного выброса ОГН левого и правого бортов.

Каждое МПВУ 1-3 (фиг. 2) содержит первую и вторую внутренние интерфейсные магистрали 36 и 37, микропроцессоры 38, подключенный первым входом-выходом к первой внутренней интерфейсной магистрали 36, а вторым входом-выходом - ко второй внутренней интерфейсной магистрали 37, к которой подключен блок 47 контроля и автономного управления, свое внешнее ПЗУ 41, подключенное к входу микропроцессора 38, свое ОЗУ 40, подключенное к первой внутренней интерфейсной магистрали 36, контроллер 42 интерфейсной магистрали 23, первый из входов-выходов которого подключен к первой внутренней интерфейсной магистрали 36, а второй вход-выход является первым входом-выходом МПВУ 1-3, блок 48 обмена через системную пультовую интерфейсную магистраль 24, первый из входов-выходов которого подключен к соответствующей второй внутренней интерфейсной магистрали 37, а второй вход-выход является вторым входом-выходом МПВУ 1-3, блоки 43-46 ввода данных от корабельных источников информации, первые входы-выходы которых подключены к соответствующей первой внутренней магистрали 36, а вторые входы являются третьими входами МПВУ 1-3. Блоки 43-46 могут быть выполнены, например, в виде преобразователя последовательного кода в параллельный (43), преобразователя фаза-код (44), преобразователя параллельного кода в параллельный код (45), аналого-цифрового преобразователя (46).

Каждое МПВУ 11-16 (фиг. 3) содержит первую и вторую внутренние интерфейсные магистрали 49 и 50, микропроцессор 51, подключенный первым входом-выходом к первой внутренней интерфейсной магистрали 49, а вторым входом-выходом - ко второй внутренней интерфейсной магистрали 50, к которой подключен блок 61 контроля и автономного управления, свое внешнее ПЗУ 54, подключенное к входу микропроцессора 50, свое ОЗУ 53, подключенное к первой внутренней интерфейсной магистрали 49, контроллер 55 системной интерфейсной магистрали 23, первый из входов-выходов которого подключен к первой внутренней интерфейсной магистрали 49, а второй вход-выход является первым входом-выходом МПВУ 11-16, контроллер 56 интерфейсной магистрали управления объектами, первый из входов-выходов которого подключен к соответствующей первой внутренней интерфейсной магистрали 49, а второй вход-выход является вторым входом-выходом МПВУ 11-16, блоки 57-60 ввода-вывода данных в объекты управления, первые входы-выходы которых подключены к соответствующей первой внутренней магистрали 49, а вторые входы-выходы являются третьими входами-выходами соответствующего МПВУ с четвертого по девятый. Блоки 57-60 могут быть выполнены, например, в виде преобразователя последовательного кода в параллельный (57), преобразователя параллельного кода в параллельный код (58), преобразователя параллельного кода в последовательный (59), цифроаналогового преобразователя (60).

Каждый блок 7-10 ЦСУ (фиг. 4) содержит свои первую и вторую внутренние интерфейсные магистрали 62 и 63, свой микропроцессор 64, подключенный первым входом-выходом к соответствующей первой внутренней интерфейсной магистрали 62, а вторым входом-выходом - к соответствующей второй внутренней интерфейсной магистрали 63, к которой своим входом-выходом подключен свой блок 65 контроля и автономного управления, свой блок 66 оконечного устройства интерфейсной магистрали, первый из входов-выходов которого подключен к соответствующей первой внутренней интерфейсной магистрали 62, а второй вход-выход является входом-выходом блока 7 (8, 9, 10) ЦСУ, блок 67 управления двигателем, вход-выход которого подключен к соответствующей первой интерфейсной магистрали 62, а выход является выходом блока 7 (8, 9, 10) ЦСУ, преобразователь фаза-код, вход-выход которого подключен к соответствующей первой интерфейсной магистрали 62, а вход является входом блока 7 (8, 9, 10) ЦСУ.

Каждый пульт 4-6 управления (фиг. 5) содержит первую и вторую группы индикаторов 81, 82 и 83, 84, ключ 86 блокировки цепей старта и ключ 87 блокировки цепи питания, соединенные с блоком 85 клавиатуры. Каждый пульт 4-6 содержит также два МПВУ. Первое (второе) МПВУ каждого пульта 4-6 содержит свои первую и вторую внутренние интерфейсные магистрали 69 (75) и 70 (76), свой микропроцессор 71 (77), подключенный первым входом-выходом к соответствующей первой внутренней интерфейсной магистрали 69 (75), а вторым входом-выходом - к соответствующей второй внутренней интерфейсной магистрали 70 (76), к которой своим первым входом-выходом подключен свой блок 74 (80) контроля и автономного управления, второй вход-выход которого является вторым входом-выходом соответствующего МПВУ пульта управления, свое внешнее ПЗУ 72 (78), подключенное к входу соответствующего микропроцессора 71 (77), свой блок 73 (79) обмена через системную пультовую интерфейсную магистраль 24, первый из входов-выходов которого подключен к соответствующей первой внутренней интерфейсной магистрали 69 (75), а второй является первым входом-выходом МПВУ пульта управления, при этом блок 85 клавиатуры одним из входов-выходов подключен к входам индикаторов 81 и 82 первой группы и второму входу-выходу одного МПВУ данного пульта управления, а другим входом-выходом 85 блок клавиатуры подключен к входам индикаторов 83 и 84 второй группы и второму входу-выходу другого МПВУ данного пульта управления.

В предлагаемой многопроцессорной корабельной управляющей вычислительной системе МПВУ 1-3, 11-16 образуют вычислительное ядро с распределенными функциями (задачами):

- МПВУ 1-3 осуществляют прием данных от внешних корабельных информационных систем и команд от пультов 4-6 управления, вывод информации в пульты 4-6 и для документирования;

- МПВУ 11 и 12, 13 и 14 решают функциональные задачи управления ОИН отдельно левого и правого бортов;

- МПВУ 15 и 16 решают функциональные задачи управления ОГН левого и правого бортов;

Предлагаемая многопроцессорная корабельная управляющая система работает следующим образом.

При включении питания системы микропроцессоры 38, 51, 64, 71, 77 всех устройств автоматически включаются в режим тестового самоконтроля.

В случае исправности микропроцессоры 38, 51, 71, 77 автоматически загружают программы из своих внешних ПЗУ 41 (54, 72, 78) в системные ОЗУ 40, 53, резидентное ОЗУ микропроцессора 38 (51, 71, 77), ОЗУ арифметического сопроцессора 39 (52).

После загрузки программы в МПВУ 1-3, 11-16, а также в МПВУ пультов 4, 5, 6 запускается тест исправности. В процессе тестирования проверяются программно-доступные средства всех блоков, подключенных к внутренним магистралям 36 (49, 62, 69, 75) и 37 (50, 63, 70, 76) микропроцессоров 38, 51, 64, 71, 77.

В случае исправности МПВУ 11, 13 и 15 производится загрузка программы из ПЗУ 54 МПВУ 11 по магистрали 25 в резидентные ОЗУ микропроцессоров 64 блоков 7 ЦСУ, из ПЗУ 54 МПВУ 13 по магистрали 26 в резидентные ОЗУ микропроцессоров 64 блоков 8 ЦСУ, из внешнего ПЗУ 54 МПВУ 15, 16 по магистралям 27 и 28 в резидентные ОЗУ микропроцессора 64 блоков 9 и 10 ЦСУ.

После загрузки программ автоматически запускаются тесты исправности всех МПВУ, входящих в состав блоков 7, 8, 9 и 10 ЦСУ. Информацию о прохождении исправности МПВУ 11-16, МПВУ пультов 4, 5, 6, блоков 7, 8, 9, 10 ЦСУ собирает МПВУ 1, которое в дальнейшем выполняет функцию диспетчера вычислительных процессов во всех МПВУ через системные магистрали 23, 24.

В резидентном ОЗУ микропроцессора 38 МПВУ 1 формируется информация об исправной конфигурации всей управляющей системы, которая выводится на индикаторы 81-84 пультов управления 4 для ОИН левого и правого бортов, 5 - для OГН левого и правого бортов. Пульты управления 4 и 5 равноправны и независимы, опрос органов управления режимами работы осуществляется циклически с частотой 1 ГЦ, информация о положении органов управления хранится в резидентном ОЗУ микропроцессора 38.

Возможна независимая работа, например с пульта 4 управления в основном режиме, а с пульта 5 - в режиме тренировки оператора.

При наличии исправной конфигурации по управлению ОИН или ОГН МПВУ 1 управляет вводом данных от источников информации, вычисляет элементы движения цели, формирует текущее время. МПВУ 1 распределяет информацию по МПВУ 2, 3, 11-16 и в пульты 4 и 5. При неисправном МПВУ 1 функцию диспетчера вычислительного процесса выполняет МПВУ 2. МПВУ 11-16 вырабатывают управляющие воздействия для ОИН и ОГН левого и правого бортов.

Кодовая информация в ОИН передается МПВУ 11 (12) и МПВУ 13 (14) через контроллеры 56 интерфейсных магистралей 25 и 26, релейные команды выдаются блоком 58, ответные сигналы из объектов управления принимаются также блоком 58 отдельно по левому и правому бортам.

Релейные команды в ОГН левого и правого бортов выдаются блоком 58, находящимся в МПВУ 15 (16), прием ответных сигналов от ОГН двух бортов осуществляется также блоком 58 из этих МПВУ.

Все блоки 7, 8, 9, 10 ЦСУ получают по магистралям 25-26 в кодовом виде углы разворота и через блоки 67 под управлением микропроцессоров 64 выдают их на исполнительные двигатели. Информация об отработке заданных углов разворота поступает из объектов управления в виде углов разворота датчиков на преобразователи 68 фаза-код.

Даже в случае отказа двух пультов 4 и 5 управления МПВУ 1, 11, 13, 15 (или 2, 12, 14, 16), блоков 7, 9 (или 8, 10) ЦСУ система обеспечивает управление с полным набором объектов управления одного борта.

Несанкционированное управление объектами блокируется специальными блоками 86 и 87 ключей и блоками 17-20, представляющими собой механические ключи, которые замыкают соответствующие электрические цепи при разрешении проведения стрельбы. Если операторы работают на пультах 4 и 5, то управление с пульта 6 заблокировано. Если работает оператор пульта 6, то блокируется управление с пультов 4 и 5.

В аварийной ситуации выброс аварийных объектов управления осуществляется только с помощью органов блоков 17-20.

Таким образом, предлагаемая система обладает большими функциональными возможностями, более высокой живучестью и безопасностью управления.

Представленные чертежи и описание системы позволяют, используя существующие элементную базу и технологию, изготовить ее промышленным способом и использовать в качестве корабельной системы управления, что характеризует предлагаемое изобретение как промышленно применимое.

Источники информации

1. А.с. СССР N 424148, кл. G 06 F 15/16, 1974.

2. Патент США N 3959775, кл. G 06 F 15/16, 1976.

3. А.с. СССР N 907551, кл. G 06 F 15/16, 1982.

4. Торгов Ю. И. Использование нескольких микропроцессоров в микроЭВМ.- Микропроцессорные средства и системы, N 1, 1985 г., с. 74, рис. 6.

5. Свид. РФ N 4395 на ПМ, кл. G 06 F 15/16, 1997 г. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОПРОЦЕССОРНАЯ КОРАБЕЛЬНАЯ УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2169943C1 |

| МНОГОПРОЦЕССОРНАЯ КОРАБЕЛЬНАЯ УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2174704C1 |

| СИСТЕМА ЭЛЕКТРОПИТАНИЯ КОРАБЕЛЬНОГО ИНФОРМАЦИОННО-УПРАВЛЯЮЩЕГО КОМПЛЕКСА | 2004 |

|

RU2267849C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА КОРАБЕЛЬНОГО КОМПЛЕКСА РАДИОЭЛЕКТРОННОГО ПРОТИВОДЕЙСТВИЯ | 2001 |

|

RU2209463C2 |

| КОРАБЕЛЬНАЯ БОЕВАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА | 2000 |

|

RU2163392C1 |

| КОРАБЕЛЬНАЯ БОЕВАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА | 2001 |

|

RU2186421C1 |

| АВТОМАТИЗИРОВАННОЕ РАБОЧЕЕ МЕСТО ОПЕРАТОРА КОРАБЕЛЬНОЙ БОЕВОЙ ИНФОРМАЦИОННО-УПРАВЛЯЮЩЕЙ СИСТЕМЫ ИЛИ БОЕВОЙ ИНФОРМАЦИОННО-УПРАВЛЯЮЩЕЙ СИСТЕМЫ БЕРЕГОВОГО БАЗИРОВАНИЯ | 2001 |

|

RU2183856C1 |

| КОМАНДНО-СТРЕЛЬБОВАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА БЕРЕГОВОГО БАЗИРОВАНИЯ | 2000 |

|

RU2176818C1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА РАДИОЛОКАЦИОННОЙ СТАНЦИИ ЦЕЛЕУКАЗАНИЯ | 2000 |

|

RU2177171C1 |

| КОМАНДНО-СТРЕЛЬБОВАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА | 2001 |

|

RU2191430C1 |

Изобретение относится к вычислительной технике и предназначено для сбора информации от внешних источников и последующей ее обработки для выработки сигналов управления различным корабельным оборудованием, в частности корабельным оружием. Техническим результатом является создание многопроцессорной управляющей вычислительной системы с более широкими функциональными возможностями и высокой безопасностью управления. Система содержит блоки ввода данных от корабельных источников информации, блоки ввода-вывода данных в объекты управления, системную интерфейсную магистраль межпроцессорного обмена, три пульта управления, девять микропроцессорных вычислительных устройств, системную пультовую интерфейсную магистраль, интерфейсные магистрали управления объектами индивидуального и объектами группового наведения левого и правого бортов, блоки цифровых следящих устройств для объектов индивидуального и для объектов группового наведения левого и правого бортов, блоки блокировки цепей стрельбы и аварийного выброса объектов индивидуального и объектов группового наведения левого и правого бортов. 1 з.п. ф-лы, 5 ил.

| ПРИСПОСОБЛЕНИЕ ДЛЯ ВОСПЛАМЕНЕНИЯ В ДВИГАТЕЛЯХ ВНУТРЕННЕГО ГОРЕНИЯ | 1925 |

|

SU4395A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Мультимикропроцессорная система | 1980 |

|

SU907551A1 |

| МНОГОПРОЦЕССОРНАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 1993 |

|

RU2054710C1 |

| US 3959775 A, 25.05.1976 | |||

| СПОСОБ И УСТАНОВКА ДЛЯ УЛУЧШЕНИЯ ЭКСПЛУАТАЦИОННЫХ ХАРАКТЕРИСТИК И ПЕРЕМЕШИВАНИЯ ПАРА В ЯДЕРНОЙ ЭНЕРГЕТИЧЕСКОЙ СИСТЕМЕ | 1995 |

|

RU2140589C1 |

Авторы

Даты

2000-04-10—Публикация

1998-10-13—Подача