Изобретение относится к вычислительной технике и технике связи и может быть использовано для построения локальных сетей, обеспечивающих возможность передачи и приема дискретной информации.

Известна система для передачи и приема дискретной информации, содержащая на передающей стороне информационный канал из последовательно соединенных вычитающего счетчика, дешифратора, инвертора, блока совпадения, регистра сдвига и элемента задержки, а на приемной стороне - последовательно соединенные блок выделения псевдослучайной последовательности, сумматор по модулю два и инвертор, связанный со счетчиком выбора каналов, в каждом из которых установлены генератор псевдослучайной последовательности, блок сравнения, суммирующий счетчик и накопитель (см., например, описание изобретения к авторскому свидетельству СССР N 886296, кл. H 03 М 7/04, 1980).

Недостатком такой системы является ее сложность, обуславливающую сравнительно невысокую надежность в эксплуатации и низкую достоверность передачи информации.

Известна адаптивная система для приема дискретной информации, закодированной корректирующим кодом, имеющая накопитель с блоком памяти, регистры, блок ключей и сумматоры (см., например, описание изобретения к авторскому свидетельству СССР N 1674384, кл. H 03 М 13/00, 1988).

Недостатками системы являются ее сложность реализации, а также необходимость коррекции кодовой комбинации путем передачи ее в накопитель и исправления ошибочных разрядов.

Наиболее близкой из известных по своей технической сущности и достигаемому результату является выбранная в качестве прототипа адаптивная система для передачи и приема дискретной информации, содержащая на передающей стороне информационный канал, включающий буферный регистр, присоединенный к линии связи, на принимающей стороне - сумматор по модулю два, первый вход которого через сдвиговый регистр подключен к линии связи, элементы И и узел управления, имеющий первый и второй буферные регистры, генератор тактовых импульсов и элемент задержки (см., например, описание изобретения к авторскому свидетельству СССР N 1691965, кл. H 03 М 13/00, 1989).

К недостаткам системы следует отнести передачу ответного вектора ошибок по линии связи в обратном направлении.

Сущность заявляемого изобретения выражается в совокупности существенных признаков, достаточных для достижения обеспечиваемого предлагаемым изобретением технического результата, который выражается в повышении достоверности передачи цифровой информации по прямому каналу передачи цифровой информации путем обнаружения ошибок декодирования на приемной стороне системы.

Заявленная совокупность существенных признаков находится в прямой причинно-следственной связи к достигаемому результату.

Новизна предложенной системы усматривается в том, что в нее дополнительно введены кодер и декодер передаваемой информации с соответствующими первым и вторым процессорами, два дополнительных сдвиговых регистра и второй элемент задержки, а также дополнительный сумматор по модулю два, причем первый буферный регистр, кодер и первый процессор подключены последовательно, образуя прямой канал передачи дискретной информации, второй буферный регистр, декодер и второй процессор подключены последовательно, образуя обратный канал передачи дискретной информации, второй буферный регистр посредством дополнительных сдвиговых регистров связан соответственно с первым и вторым сумматорами по модулю два, подключенными через введенный в обратный канал передачи дискретной информации первый и второй элементы И, последний из которых присоединен через первый процессор к первому буферному регистру прямого канала передачи дискретной информации, при этом сдвиговый регистр подключен к дополнительному сумматору по модулю два, а генератор тактовых импульсов через элемент задержки подключен ко второму элементу И, в нее дополнительно введены кодер и декодер передаваемой информации с соответствующими первым и вторым процессорами, два дополнительных сдвиговых регистра и второй элемент задержки, а также дополнительный сумматор по модулю два, причем первый буферный регистр, кодер и первый процессор подключены последовательно, образуя прямой канал передачи дискретной информации, второй буферный регистр, декодер и второй процессор подключены последовательно, образуя обратный канал передачи дискретной информации, второй буферный регистр посредством дополнительных сдвиговых регистров связан соответственно с первым и вторым сумматорами по модулю два, подключенными через введенный в обратный канал передачи дискретной информации первый и второй элементы И, последний из которых присоединен через первый процессор к первому буферному регистру прямого канала передачи дискретной информации, при этом сдвиговый регистр подключен к дополнительному сумматору по модулю два, а генератор тактовых импульсов через элемент задержки подключен ко второму элементу И.

Сравнение заявленного технического решения с прототипом позволило установить соответствие его критерию "новизна", так как оно не известно из уровня техники.

Предложенная система является промышленно применимой существующими средствами и соответствует критерию "изобретательский уровень", т. к. он явным образом не следует из уровня техники, при этом из последнего не выявлено каких-либо преобразований, характеризуемых отличительными от прототипа существенными признаками, на достижение указанного технического результата.

Таким образом, предложенное техническое решение соответствует установленным условиям патентоспособности изобретения.

Других известных технических решений аналогичного назначения с подобными существенными признаками заявителем не обнаружено.

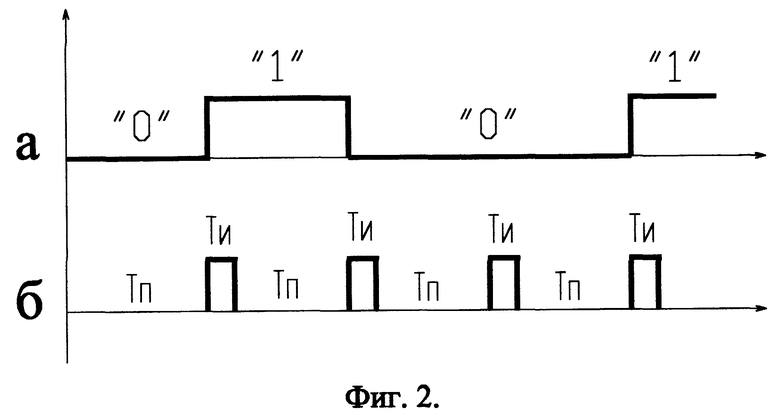

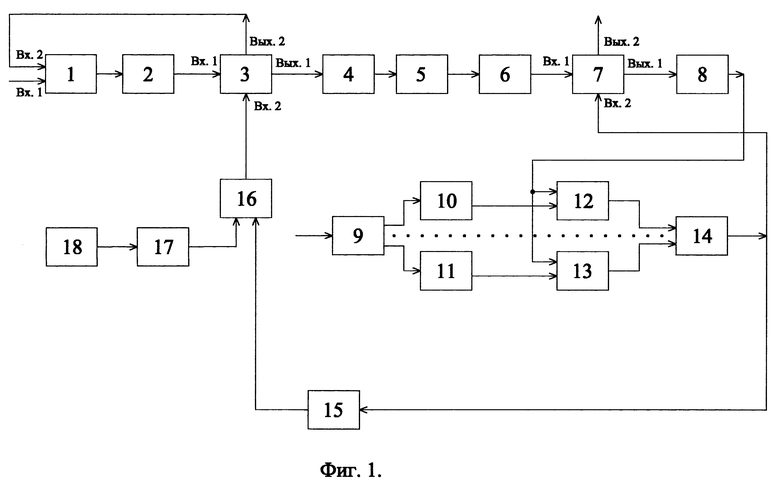

На фиг. 1 изображена структурная электрическая схема предлагаемой системы, на фиг. 2 - временные диаграммы работы системы.

Адаптивная система для передачи и приема дискретной информации содержит на передающей стороне первый буферный регистр 1, кодер 2, первый процессор 3, прямой канал 4 передачи дискретной цифровой информации, на приемной стороне второй буферный регистр 5, декодер 6, второй процессор 7, регистр сдвига 8, буферный регистр 9, дополнительные регистры сдвига 10 и 11, сумматоры по модулю два 12 и 13, первый элемент И 14, обратный канал 15 передачи цифровой информации, второй элемент И 16, элемент задержки 17, генератор 18 тактовых импульсов.

Предлагаемая система работает следующим образом.

По команде с управляющего устройства (не показано) на передающей стороне на вход первого буферного регистра 1 поступает управляющий сигнал, под воздействием которого из первого буферного регистра 1 на вход кодера 2 поступает дискретная (двоичная) информация в виде k - разрядного сообщения Aj,  (каждый разряд которого является "0" или "1"). K - разрядное сообщение Aj кодируется системой кодирования CKi;,

(каждый разряд которого является "0" или "1"). K - разрядное сообщение Aj кодируется системой кодирования CKi;,  , (n≠N) в m-разрядный кодовый вектор (где k - информационные разряды, a m-k избыточные разряды, вводимые в k - разрядное сообщение Aj с целью повышения достоверности передаваемой информации). Алгоритм кодирования системы кодирования CKi, работает таким образом, что всего кодером 2 (который реализует алгоритм кодирования CKi) может быть сгенерировано n m-разрядных кодовых векторов (X1, X2,...Xn), для каждого из которых справедливо условие

, (n≠N) в m-разрядный кодовый вектор (где k - информационные разряды, a m-k избыточные разряды, вводимые в k - разрядное сообщение Aj с целью повышения достоверности передаваемой информации). Алгоритм кодирования системы кодирования CKi, работает таким образом, что всего кодером 2 (который реализует алгоритм кодирования CKi) может быть сгенерировано n m-разрядных кодовых векторов (X1, X2,...Xn), для каждого из которых справедливо условие  (где Xi произвольный i-й кодовый вектор из множества кодовых векторов, входящих в CKi). Количество m-разрядных кодовых векторов (n), генерируемых кодером 2, реализующих алгоритм кодирования CKi, меньше общего количества m-разрядных кодовых векторов, и справедливо условие n < 2m.

(где Xi произвольный i-й кодовый вектор из множества кодовых векторов, входящих в CKi). Количество m-разрядных кодовых векторов (n), генерируемых кодером 2, реализующих алгоритм кодирования CKi, меньше общего количества m-разрядных кодовых векторов, и справедливо условие n < 2m.

В результате работы кодера 2, k-разрядное сообщение Aj кодируется в один из m-разрядных кодовых векторов  , который поступает на вход 1 первого процессора 3, в котором запоминается. C выхода 1 первого процессора 3 кодовый вектор Xi поступает на вход прямого канала 4 передачи цифровой информации.

, который поступает на вход 1 первого процессора 3, в котором запоминается. C выхода 1 первого процессора 3 кодовый вектор Xi поступает на вход прямого канала 4 передачи цифровой информации.

В канале 4 на кодовый вектор Xi воздействуют помехи (F), которые могут внести ошибки (под воздействием помех F в произвольном из m-разрядов кодового вектора Xi, может произойти замена содержимого двоичного разряда на противоположное значение, например 0 ---> 1, 1 ---> 0), в результате чего кодовый вектор Xi преобразуется в кодовый вектор Xi .

.

На приемной стороне системы, с выхода канала 4 кодовый вектор X'i поступает на вход второго буферного регистра 5, с выхода которого кодовый вектор X'i поступает на вход декодера 6, где он (кодовый вектор X'i) декодируется в кодовый вектор Yi.

В результате работы декодера 6 кодовый вектор X'i, преобразуется в кодовый вектор Yi (X'i ---> Yi), при этом возможны три состояния:

Xi = Yi,  - состояние "правильное декодирование";

- состояние "правильное декодирование";

Xi ≠ Yi,  - состояние "ошибка декодирования";

- состояние "ошибка декодирования";

Xi ≠ Yi,  - состояние "отказ от декодирования".

- состояние "отказ от декодирования".

На приемной стороне системы состояния: "правильное декодирование" и "ошибка декодирования" не различимы. Состояние "ошибка декодирования" на приемной стороне системы не обнаруживается (всякая CKi имеет определенную вероятность ошибки декодирования  .

.

Кодовый вектор Yi с выхода декодера 6 поступает на вход 1 второго процессора 7. С выхода 1 второго процессора 7 кодовый вектор Yi поступает на вход m-разрядного сдвигового регистра.

По команде с управляющего устройства (не показано) на приемной стороне из буферного регистра 9 на входы m-разрядных дополнительных сдвиговых регистров 10 и 11 поступают эталонные кодовые вектора X1, X2,...Xn (количество m-разрядных сдвиговых регистров 10,...11 равно количеству кодовых векторов (n) системы кодирования CKi). Эталонные кодовые вектора X1, X2,...Xn (системы кодирования CKi) с выходов m-разрядных сдвиговых регистров 10 и 11 поступают на один из входов m-разрядных сумматоров по модуля два 12 и 13, соответственно (количество m-разрядных сумматоров по модулю два (12,...13) равно количеству m-разрядных сдвиговых регистров (10,...11) и равно количеству кодовых векторов n). На другой вход m-разрядных сумматоров по модулю два 12 и 13, с выхода m-разрядного сдвигового регистра 8, поступает кодовый вектор Yi.

Если для кодового вектора Yi выполняются условия (случай I):

Xi = Yi,  - состояние "правильное декодирование";

- состояние "правильное декодирование";

или Xi ≠ Yi,  - состояние "ошибка декодирования",

- состояние "ошибка декодирования",

где Xi произвольный эталонный кодовый вектор из множества векторов X1, X2,...Xn, то на выходе одного из m-разрядных сумматоров по модулю два (12,.. 13) будет сигнал "0", а на выходах остальных m-разрядных сумматоров по модулю два (12,...13) будет сигнал "1". В результате поступления сигнала "0" с выхода одного из m-разрядных сумматоров по модулю два (12,...13) на один из входов элемента И 14 и поступления сигналов "1" с выходов остальных m-разрядных сумматоров по модулю два (12,...13) на остальные входы элемента И 14, на выходе элемента И 14 образуется сигнал "0" (количество входов элемента И 14 равно количеству m- разрядных сумматоров по модулю два и равно количеству эталонных кодовых векторов n).

Появление сигнала "0" на выходе элемента И 14 означает ситуации: "правильное декодирование" или "ошибка декодирования". На приемной стороне системы состояния: "правильное декодирование" или "ошибка декодирования" (случай I) не различимы. Состояние "ошибка декодирования" на приемной стороне системы не обнаруживается (всякая CKi имеет определенную вероятность ошибки декодирования  . Поэтому на приемной стороне системы случай I воспринимается как сигнал правильной передачи и приема кодового вектора Xi. С выхода элемента И 14 сигнал "0" поступает на вход 2 процессора 7. В результате этого кодовый вектор Yi считывается с выхода 2 процессора 7 в устройство обработки (не показано), где из него выделяется k информационных разрядов (избыточные m-k разрядов при этом отбрасываются). Сформированное, таким образом из кодового вектора Yi, k-разрядное информационное сообщение A'j поступает далее на обработку.

. Поэтому на приемной стороне системы случай I воспринимается как сигнал правильной передачи и приема кодового вектора Xi. С выхода элемента И 14 сигнал "0" поступает на вход 2 процессора 7. В результате этого кодовый вектор Yi считывается с выхода 2 процессора 7 в устройство обработки (не показано), где из него выделяется k информационных разрядов (избыточные m-k разрядов при этом отбрасываются). Сформированное, таким образом из кодового вектора Yi, k-разрядное информационное сообщение A'j поступает далее на обработку.

Сигнал "0" (случай I) с выхода элемента И 14 поступает на вход обратного канала 15 цифровой информации, с выхода которого сигнал "0" поступает на один из двух входов элемента И 16, на другой вход которого поступает тактовый импульс (имеющий значение "1") с выхода элемента задержки 17, на вход которого поступает сигнал с генератора 18 тактовых импульсов.

На фиг. 2 обозначены следующие сигналы:

а - сигналы "0" или "1" с выхода элемента И 14;

б - тактовые импульсы (имеющие значения "1") с генератора 18 тактовых импульсов. Временной интервал Тп между тактовыми импульсами равен времени передачи кодового вектора Xi по прямому каналу 4, плюс время обработки цифровой информации на приемной стороне системы, плюс время передачи по обратному каналу 15.

С выхода элемента И 16 сигнал "0" поступает на вход 2 первого процессора 3. С выхода 2 первого процессора 3 поступает управляющий сигнал на вход 2 первого буферного регистра 1, в результате чего с выхода первого буферного регистра 1 на вход кодера 2 поступает следующая дискретная информация Aj+1.

Если для кодового вектора Yi выполняется условие (случай II):

Xi ≠ Yi,  - состояние "отказ от декодирования",

- состояние "отказ от декодирования",

то на выходе всех m-разрядных сумматоров по модулю два (12,...13) будет сигнал "1". В результате поступления сигналов "1" с выходов всех m-разрядных сумматоров по модулю два (12,...13) на все входы элемента И 14, на выходе элемента И 14 образуется сигнал "1".

Появление сигнала "1" на выходе элемента И 14 означает ситуацию "отказ от декодирования". На приемной стороне системы ситуация "отказ от декодирования" обнаруживается в процессе проверки условия Xi ≠ Yi,  . Если с выхода элемента И 14 поступает сигнал "1" на вход 2 процессора 7, то кодовый вектор Yi не считывается (так как на приемной стороне случай II обнаруживается как состояние "отказ от декодирования"). Сигнал "1" с выхода элемента И 14 поступает одновременно на вход обратного канала 15 передачи цифровой информации, с выхода которого сигнал "1" поступает на один из двух входов элемента И 16, на другой вход которого поступает тактовый импульс с выхода элемента задержки 17, на вход которого поступает сигнал с генератора 18 тактовых импульсов. С выхода элемента И 16 сигнал "1", в момент поступления тактового импульса (имеющего значение "1") поступает на вход 2 первого процессора 3. В этом случае, с выхода 1 первого процессора 3 на вход прямого канала 4 передачи цифровой информации, повторно поступает кодовый вектор Xi (ранее запомненный в первом процессоре 3), с целью обеспечения достоверной передачи информации в системе. Одновременно (в случае II) с выхода 2 первого процессора 3 поступает управляющий сигнал на вход 2 первого буферного регистра 1, в результате чего с выхода первого буферного регистра 1 на вход кодера 2 не поступает следующая дискретная информация Aj+1.

. Если с выхода элемента И 14 поступает сигнал "1" на вход 2 процессора 7, то кодовый вектор Yi не считывается (так как на приемной стороне случай II обнаруживается как состояние "отказ от декодирования"). Сигнал "1" с выхода элемента И 14 поступает одновременно на вход обратного канала 15 передачи цифровой информации, с выхода которого сигнал "1" поступает на один из двух входов элемента И 16, на другой вход которого поступает тактовый импульс с выхода элемента задержки 17, на вход которого поступает сигнал с генератора 18 тактовых импульсов. С выхода элемента И 16 сигнал "1", в момент поступления тактового импульса (имеющего значение "1") поступает на вход 2 первого процессора 3. В этом случае, с выхода 1 первого процессора 3 на вход прямого канала 4 передачи цифровой информации, повторно поступает кодовый вектор Xi (ранее запомненный в первом процессоре 3), с целью обеспечения достоверной передачи информации в системе. Одновременно (в случае II) с выхода 2 первого процессора 3 поступает управляющий сигнал на вход 2 первого буферного регистра 1, в результате чего с выхода первого буферного регистра 1 на вход кодера 2 не поступает следующая дискретная информация Aj+1.

Далее цикл работы повторяется.

Применение предложенной системы позволяет повысить достоверность передачи цифровой информации по каналам связи, подверженным воздействию импульсных и других помех при обеспечении высокой скорости передачи информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Декодер кода Рида-Маллера первого порядка по максимуму правдоподобия | 1990 |

|

SU1775857A1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОГО СООБЩЕНИЯ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2179365C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОГО СООБЩЕНИЯ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2179366C1 |

| УСТРОЙСТВО МНОГОКАНАЛЬНОЙ РАДИОСВЯЗИ | 2023 |

|

RU2809552C1 |

| Система передачи информации с решающей обратной связью | 1984 |

|

SU1167746A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Устройство кодирования и декодирования факсимильных сигналов | 1980 |

|

SU1043834A1 |

| ПРОСТРАНСТВЕННО-ВРЕМЕННОЕ БЛОЧНОЕ КОДИРОВАНИЕ В СИСТЕМАХ СВЯЗИ С ОРТОГОНАЛЬНЫМ ЧАСТОТНЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2005 |

|

RU2344555C2 |

Использование: в технике связи и вычислительной технике. Сущность изобретения: адаптивная система для передачи и приема дискретной информации содержит на передающей стороне буферный регистр, а на приемной стороне - сумматор по модулю два, сдвиговый регистр, элемент И и узел управления, имеющий первый и второй буферные регистры, генератор тактовых импульсов и элемент задержки. Новизна системы состоит в том, что в нее дополнительно введены кодер и декодер передаваемой информации с соответствующими процессорами, два дополнительных сдвиговых регистра, второй элемент задержки, а также дополнительный сумматор по модулю два. Техническим результатом является повышение достоверности передачи цифровой информации по прямому каналу, путем обнаружения ошибок декодирования на приемной стороне. 2 ил.

Адаптивная система для передачи и приема дискретной информации, содержащая на передающей стороне буферный регистр, на приемной стороне - сумматор по модулю два, первый вход которого подключен к выходу сдвигового регистра, а также первый и второй элементы И, узел управления, содержащий дополнительный буферный регистр, генератор тактовых импульсов и элемент задержки, отличающаяся тем, что введены на передающей стороне кодер и процессор, а на приемной стороне буферный регистр, декодер, процессор, два дополнительных регистра сдвига и дополнительный сумматор по модулю два, причем буферный регистр, кодер и процессор на передающей стороне соединены последовательно, с первого выхода процессора на передающей стороне кодовый вектор поступает на вход прямого канала передачи цифровой информации, с выхода которого поступает на вход буферного регистра приемной стороны, на которой буферный регистр, декодер и процессор соединены последовательно, с первого выхода процессора на приемной стороне кодовый вектор поступает на вход сдвигового регистра, дополнительный буферный регистр посредством дополнительных регистров сдвига связан с соответствующими входами сумматора по модулю два, другой вход дополнительного сумматора по модулю два соединен с выходом сдвигового регистра с второго выхода процессора на приемной стороне считывается правильно принятый кодовый вектор, выходы сумматоров по модулю два соединены с входами первого элемента И, с выхода которого сигнал поступает на второй вход процессора и на вход обратного канала передачи цифровой информации, с выхода которого сигнал поступает на один вход второго элемента И, выход которого через процессор на передающей стороне присоединен ко второму входу буферного регистра, на первый вход которого поступает управляющий сигнал, а выход генератора таковых импульсов через элемент задержки подключен к другому входу второго элемента И.

| Устройство для передачи информации | 1989 |

|

SU1691965A1 |

| Адаптивное устройство разделения неортогональных сигналов двоичной фазовой манипуляции | 1991 |

|

SU1786682A2 |

| US 4592075 A, 27.05.1986 | |||

| БИБЛИОТЕКА | 0 |

|

SU390351A1 |

Авторы

Даты

2000-06-10—Публикация

1999-04-19—Подача